# UNIVERSIDAD NACIONAL AUTÓNOMA DE MÉXICO

# FACULTAD DE ESTUDIOS SUPERIORES ACATLÁN

Estructuras de datos multi-dimensionales para cálculo numérico en CUDA C

# **TESIS**

QUE PARA OBTENER EL TÍTULO DE:

LIC. EN MATEMÁTICAS APLICADAS Y COMPUTACIÓN

PRESENTA:

JOSEFINA SÁNCHEZ NOGUEZ

ASESOR: DR. CARLOS COUDER CASTAÑEDA

SANTA CRUZ ACATLÁN, NAUCALPAN, EDO. DE MÉXIC, OCTUBRE 2021

UNAM – Dirección General de Bibliotecas Tesis Digitales Restricciones de uso

### DERECHOS RESERVADOS © PROHIBIDA SU REPRODUCCIÓN TOTAL O PARCIAL

Todo el material contenido en esta tesis esta protegido por la Ley Federal del Derecho de Autor (LFDA) de los Estados Unidos Mexicanos (México).

El uso de imágenes, fragmentos de videos, y demás material que sea objeto de protección de los derechos de autor, será exclusivamente para fines educativos e informativos y deberá citar la fuente donde la obtuvo mencionando el autor o autores. Cualquier uso distinto como el lucro, reproducción, edición o modificación, será perseguido y sancionado por el respectivo titular de los Derechos de Autor.

#### Dedicatoria.

La culminación de una carrera no sería posible sin la colaboración de un conjunto de personas que nos guían y acompañan durante todo el proceso.

El esfuerzo realizado dentro de este trabajo de investigación va principalmente dedicado a mi asesor el Doctor Carlos Couder Castañeda, por el apoyo y herramientas brindadas.

De igual manera, a mis sínidos, profesores de la carrera y personal educativo que fueron los que me acompañaron en cada paso que di.

Por último pero no menos importante a mi esposo Rubicel por su apoyo incondicional en todo momento.

#### AGRADECIMIENTOS

A la Universidad Nacional Autónoma de México, Facultad de Estudios Superiores Acatlán y a la carrera de Matemáticas Aplicadas y Computación por la oportunidad que me dieron para mi formación.

A mi asesor el Doctor Carlos Couder Castañena por el apoyo y herramientas brindadas.

A los señores miembros del sínodo:

Mtra. Sara Camacho Cancino.

Mtra. Socorro Martínez José.

Mtra. Teresa Carrillo Ramírez.

Lic. Oscar Gabriel Caballero Martínez.

Por su tiempo y dedicación.

Al Centro de Desarrollo Aeroespacial del Instituto Politécnico Nacional, por el acceso a las tarjetas gráficas para poder llevar a cabo los experimentos requeridos en este trabajo.

En años recientes, la necesidad de incrementar la velocidad de procesamiento de los algoritmos numéricos, ha conducido al uso de tarjetas gráficas conocidas como Unidades de Procesamiento Gráfico o GPUs por sus siglas en inglés (Graphic Procesing Units). En el 2007 NVIDIA a través de la plataforma CUDA (Compute Unified Device Architecture) permitió el acceso global a los GPUs con la finalidad de desarrollar aplicaciones de propósito general, que inicialmente estaban orientadas únicamente a tareas de visualización. CUDA es una de las interfaces de programación de aplicaciones más populares para acelerar una variedad de funciones en el GPU.

CUDA son las siglas en inglés Compute Unified Device Architecture (Arquitectura Unificada de Dispositivos de Cómputo) que hace referencia a una plataforma de computación en paralelo incluyendo un compilador y un conjunto de herramientas de desarrollo creadas por Nvidia que permiten a los programadores usar una variación del lenguaje de programación C (CUDA C) para codificar algoritmos en GPU de Nvidia. (Ref. Wikipedia).

CUDA puede permitir que el código escrito en C o C++ se ejecute de manera eficiente en una GPU con un esfuerzo de programación relativamente razonable. Logra un equilibrio entre la necesidad de conocer la arquitectura para explotarla bien, y la necesidad de tener una interfaz de programación que sea fácil de uso y resultados en programas legibles.

Las extensiones al lenguaje C que introduce CUDA facilita enormemente la programación de los GPUs, no obstante, la creación de arreglos multidimensionales no es tan simple como en lenguaje C, lo que implica que los códigos que utilizan arreglos bidimensionales o tridimensionales deben ser trabajados como unidimensionales requiriéndose un mapeo de los índices bidimensionales o tridimensionales a un índice unidimensional, lo cual puede ser propenso a errores, sobre todo cuando se implementan moléculas computaciones que representan diferencias finitas o elementos finitos, donde los índices juegan un papel crucial.

La implementación de arreglos multidimensionales en CUDA C, no es análogo a C estándar, por lo que es una pregunta recurrente en los foros de programación, por lo que en este trabajo presentamos una solución práctica para crear arreglos 2D y 3D en CUDA C, de la forma más parecida a estándar C, dando una posible solución para generar un código más legible a comparación de los que solo están basados en arreglos unidimensionales.

Para demostrar la capacidad de la estructura de datos propuesta, se resuelve la ecuación de transferencia de conducción de calor en una placa (2D) y en un cubo (3D), los resultados de rendimiento muestran que no existe una sobre carga significativa en el rendimiento y si una mejor lectura del código, además de que se prueba el acceso a memoria compartida. Para verificar los resultados se programó la contraparte serial en estándar C.

# ÍNDICE GENERAL

| In | TROD              | ucción 1                                               |  |  |  |

|----|-------------------|--------------------------------------------------------|--|--|--|

| 1  | ARC               | ARQUITECTURAS PARALELAS 5                              |  |  |  |

|    | 1.1               | Antecedentes 5                                         |  |  |  |

|    | 1.2               | Taxonomía de Flynn 6                                   |  |  |  |

|    | 1.3               | Arquitecturas de memoria compartida 8                  |  |  |  |

|    | 1.4               | Arquitecturas de memoria distribuida 9                 |  |  |  |

|    |                   | Granularidad del código y niveles de paralelismo 9     |  |  |  |

|    | 1.0               | 1.5.1 Arquitectura de los GPUs 11                      |  |  |  |

|    | 1.6               | Programación paralela 13                               |  |  |  |

|    | 1.0               | 1.6.1 Descomposición de programas 13                   |  |  |  |

|    |                   | 1.6.2 Modelos de programación paralela 15              |  |  |  |

|    |                   | 1.6.2.1 OpenMP 16                                      |  |  |  |

|    |                   | 1.6.2.1 OpenMi 10<br>1.6.2.2 Paso de Mensajes (MPI) 17 |  |  |  |

|    |                   | 1.6.2.3 CUDA 18                                        |  |  |  |

|    |                   | 1.6.3 La Arquitectura CUDA 19                          |  |  |  |

|    |                   | 1.6.3.1 Programación Híbrida MPI+OpenMP 20             |  |  |  |

|    |                   | 1.6.3.2 MPI+OpenMP+CUDA 22                             |  |  |  |

|    | 1.7               | Estrategias para desarrollar aplicaciones paralelas 22 |  |  |  |

|    | 1.1               | 1.7.1 Paralelización automática 23                     |  |  |  |

|    |                   | 1.7.2 Librerías paralelas 24                           |  |  |  |

|    |                   | 1.7.3 Generación total de la aplicación paralela 24    |  |  |  |

| 2  | тлі               | PLATAFORMA CUDA Y SU PARADIGMA DE PROGRAMACIÓN 25      |  |  |  |

| 4  | 2.1               | La arquitectura CUDA 25                                |  |  |  |

|    | 2.1               | Computación Heterogénea 27                             |  |  |  |

|    | 2.3               | Paradigma de la Computación Heterogénea 29             |  |  |  |

|    | ۷.۵               | 2.3.1 Hilos CPU vs Hilos CUDA 29                       |  |  |  |

|    | 2.4               | Modelo de programación CUDA 30                         |  |  |  |

|    | $\frac{2.4}{2.5}$ | Estructura de programación CUDA 31                     |  |  |  |

|    | 2.5               | 2.5.1 Manejo de memoria 33                             |  |  |  |

|    | 2.6               | Organización de los Hilos 35                           |  |  |  |

|    |                   | CUDA como una plataforma heterogénea de cálculo 37     |  |  |  |

|    |                   |                                                        |  |  |  |

|    |                   | 1                                                      |  |  |  |

| 2  | 2.9               | Modelo de programación CUDA 40                         |  |  |  |

| 3  |                   | EÑO E IMPLEMENTACIÓN DE ESTRUCTURAS DE DATOS BIDI-     |  |  |  |

|    |                   | USIONALES Y TRIDIMENSIONALES EN CUDA C 43              |  |  |  |

|    | 3.1               | Estructura bidimensional 43                            |  |  |  |

| 3.2 Estructura tridimensional 46                     |                                          |  |  |

|------------------------------------------------------|------------------------------------------|--|--|

| 4 APLICACIÓN A LA ECUACIÓN DE TRANSFEREN             | CIA DE CALOR 51                          |  |  |

| 4.1 La ecuación de transferencia de calor 51         | La ecuación de transferencia de calor 51 |  |  |

| 4.2 La ecuación de transferencia de calor en diferer | ncias finitas 52                         |  |  |

| 4.3 Casos de Aplicación 55                           |                                          |  |  |

| 4.3.1 Suma de Matrices 55                            |                                          |  |  |

| 4.3.2 Solución a la ecuación de transferencia        | de calor 2D no esta-                     |  |  |

| cionaria. 59                                         |                                          |  |  |

| 4.3.3 Solución a la ecuación de transferencia        | de calor 3D no esta-                     |  |  |

| cionaria. 67                                         |                                          |  |  |

| 4.3.4 Consideraciones de rendimiento, el uso o       | de memoria comparti-                     |  |  |

| da = 74                                              |                                          |  |  |

| 4.3.5 Pruebas de Rendimiento 78                      |                                          |  |  |

| Conclusiones 85                                      |                                          |  |  |

| A CÓDIGOS FUENTE 87                                  |                                          |  |  |

| A.1 Código fuente serial 2D 87                       |                                          |  |  |

| A.2 Código Fuente serial 3D 92                       |                                          |  |  |

| A.3 kernels 2D 97                                    |                                          |  |  |

| A.3.1 Kernel 2D-1-1 97                               |                                          |  |  |

| A.3.2 Kernel 2D-1-2 103                              |                                          |  |  |

| A.3.3 Kernel 2D-2-2 111                              |                                          |  |  |

| A.4 Kernels 3D 120                                   |                                          |  |  |

| A.4.1 Kernel 3D-1-1 120                              |                                          |  |  |

| A.4.2 Kernel 3D-1-3 128                              |                                          |  |  |

| A.4.3 Kernel 3D-3-3 139                              |                                          |  |  |

| B PRESENTACIONES EN CONGRESOS 151                    |                                          |  |  |

| BIBLIOGRAFÍA 171                                     |                                          |  |  |

$\mathbf{x}$

# ÍNDICE DE FIGURAS

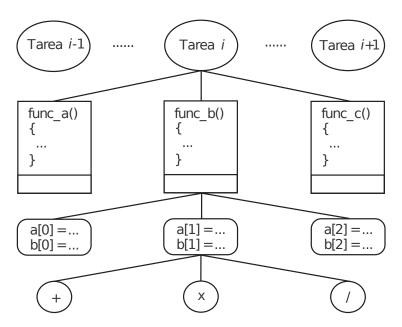

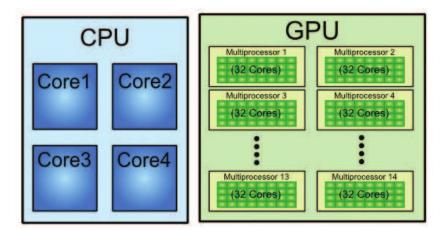

| Figura 1.1<br>Figura 1.2 | Niveles de paralelismo. 11<br>Número de núcleos, CPU vs GPU. Los núcleos en el GPU                                                                                                                                                                                                                                                                                                                  |

|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                          | están organizados en multiprocesadores. 12                                                                                                                                                                                                                                                                                                                                                          |

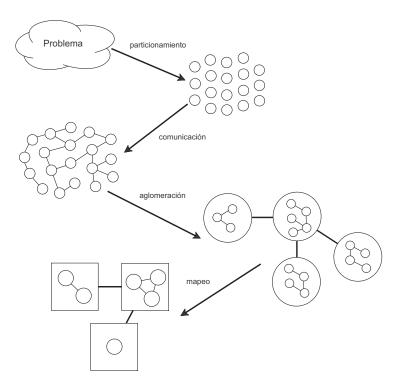

| Figura 1.3               | Metodología PCAM (Foster, 2020). 14                                                                                                                                                                                                                                                                                                                                                                 |

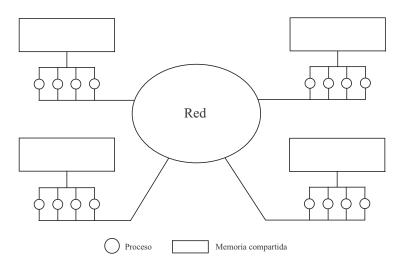

| Figura 1.4               | Topología MPI (Foster, 2020). 17                                                                                                                                                                                                                                                                                                                                                                    |

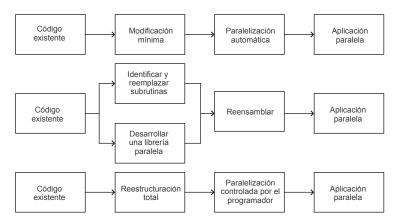

| Figura 1.5               | Estrategias para paralelizar aplicaciones paralelas. 23                                                                                                                                                                                                                                                                                                                                             |

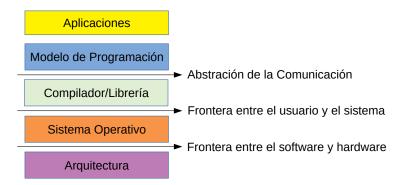

| Figura 2.6               | Capas de la plataforma. 30                                                                                                                                                                                                                                                                                                                                                                          |

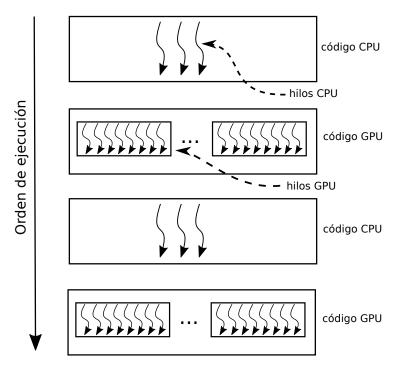

| Figura 2.7               | Secuencia de ejecución de un programa CUDA. 33                                                                                                                                                                                                                                                                                                                                                      |

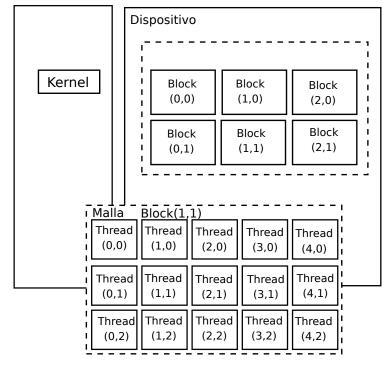

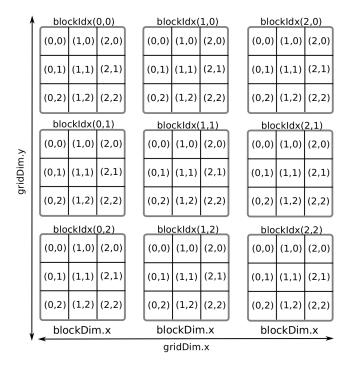

| Figura 2.8               | Estructura jerárquica de una malla 2D que contiene bloques 2D. 36                                                                                                                                                                                                                                                                                                                                   |

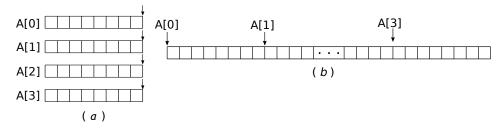

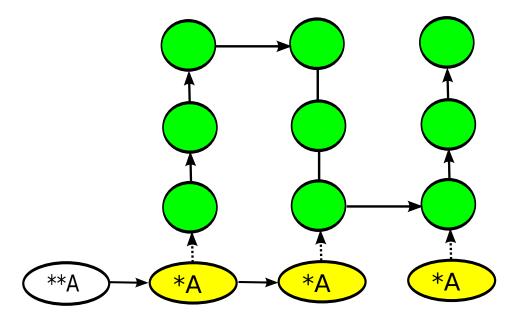

| Figura 3.9               | Estructura de memoria continua bidimensional en la CPU. (a) Arreglo 2D sin continuidad, (b) Arreglo 2D contiguo. 44                                                                                                                                                                                                                                                                                 |

| Figura 3.10              | Asignación de memoria continua para un arreglo 2D 46                                                                                                                                                                                                                                                                                                                                                |

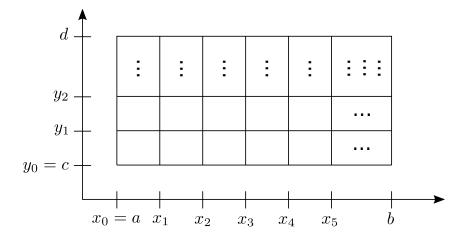

| Figura 4.11              | Dominio discreto en 2D. 53                                                                                                                                                                                                                                                                                                                                                                          |

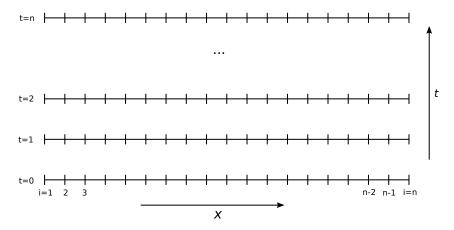

| Figura 4.12              | Solución discreta de la ecuación 1D. 54                                                                                                                                                                                                                                                                                                                                                             |

| Figura 4.13              | Malla utilizada para la suma de matrices. 59                                                                                                                                                                                                                                                                                                                                                        |

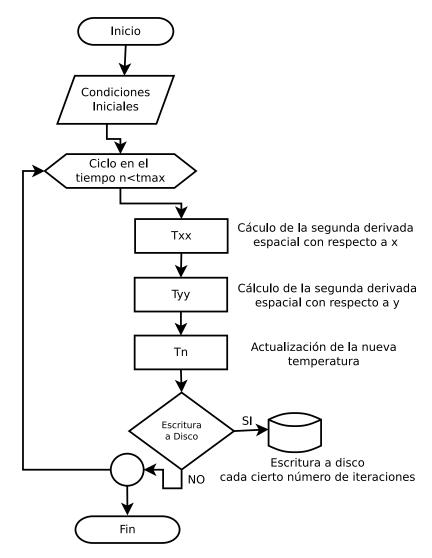

| Figura 4.14              | Diagrama de flujo correspondiente al código serial para resolver el caso 2D de la ecuación de calor. 61                                                                                                                                                                                                                                                                                             |

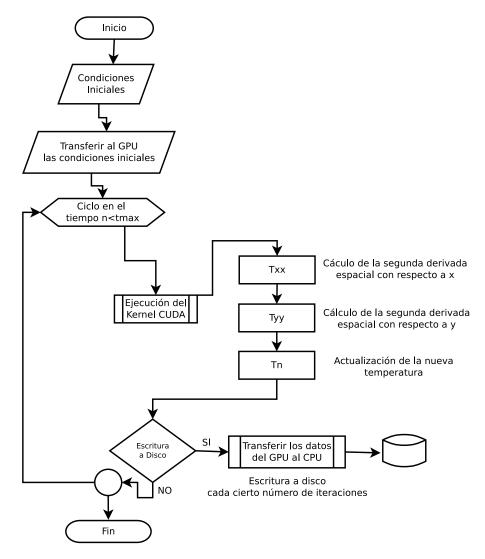

| Figura 4.15              | Diagrama de flujo correspondiente a la estructura CUDA                                                                                                                                                                                                                                                                                                                                              |

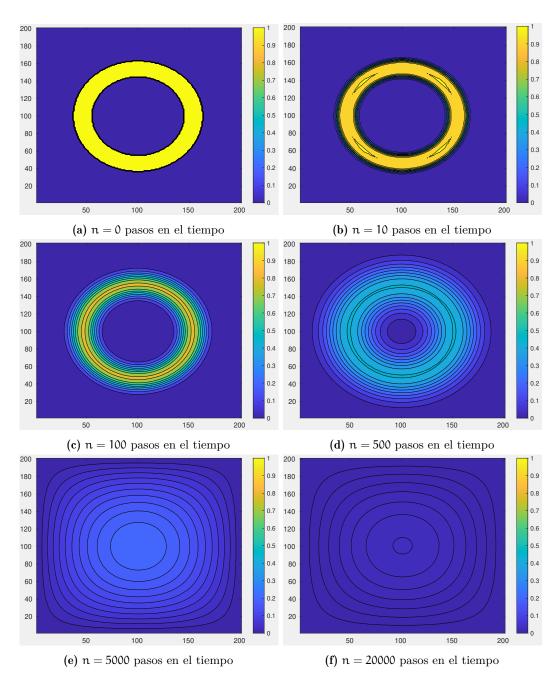

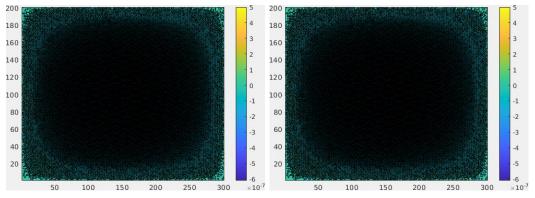

| Figura 4.16              | para resolver la ecuación de calor en 2D. 62<br>Difusión de calor no estacionaria en 2D sobre la placa unitaria generada con la versión en lenguaje C (solución de referencia), las condiciones iniciales se muestran cuando $n=0$ .<br>La malla esta conformada por $201 \times 201$ puntos, por lo tanto, $\Delta x = 0.005$ y $\Delta y = 0.005$ , $\Delta t$ se calcula con el criterio CFL. 66 |

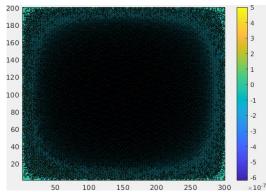

| Figura 4.17              | Error absoluto con respecto a la solución de referencia después de $20,000$ pasos en el tiempo ( $n=20,000$ ), el error máximo encontrado es del orden de $10^-7$ , lo cual es aceptable para la precisión de tipo float. $67$                                                                                                                                                                      |

| Figura 4.18              | Error absoluto con respecto a la solución de referencia después de $20,000$ pasos en el tiempo ( $n=20,000$ ), el error máximo encontrado es del orden de $10^-15$ , lo cual es aceptable para la precisión de tipo double.                                                                                                                                                                         |

| Figura 4.19              | . 70                                                                                                                                                                                                                                                                                                                                                                                                |

| T: 4.00        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

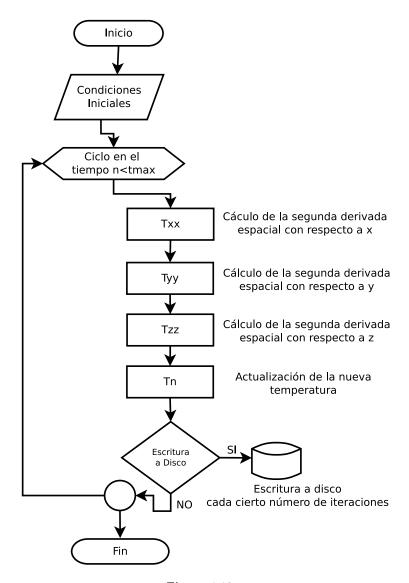

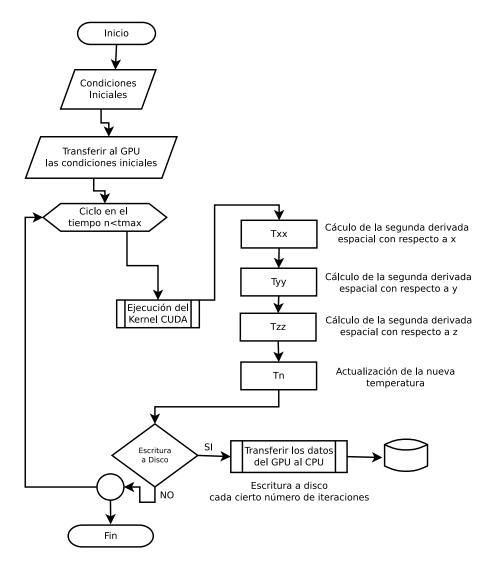

| Figura 4.20    | Diagrama de flujo correspondiente a la estructura CUDA para resolver la ecuación de calor en 3D. 71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| D: 4.01        | Police Control of the |

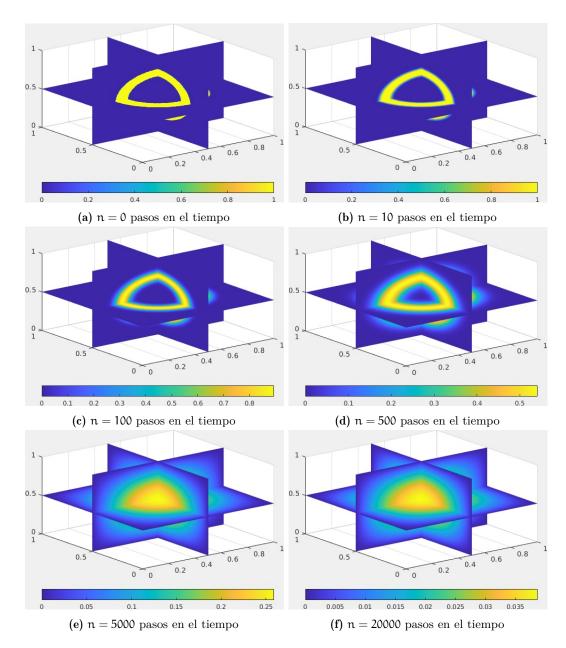

| Figura 4.21    | Difusión de calor no estacionaria en 3D sobre el cubo unitario                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                | generado con la versión en lenguaje C (solución de referen                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                | cia), las condiciones iniciales se muestran cuando $\mathfrak{n}=0.$ La                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                | malla esta conformada por $201 \times 201 \times 201$ puntos, por lo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                | tanto, $\Delta x = 0.005$ , $\Delta y = 0.005$ y $\Delta z = 0.005$ . 75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

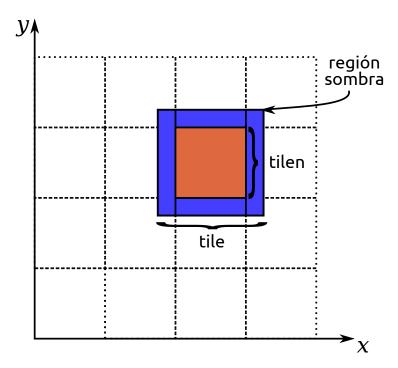

| Figura 4.22    | Uso de memoria compartida en una malla 2D, la zona azu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                | representa la región aumentada o región sombra que permite                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                | completar los cálculos en la parte interior. 77                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

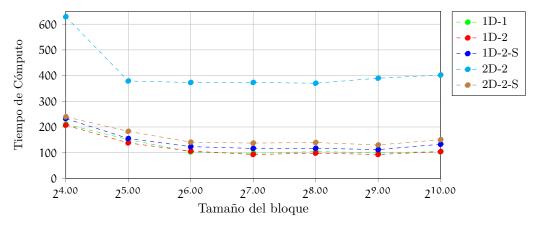

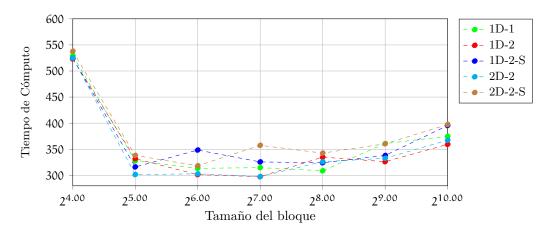

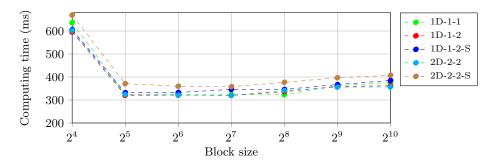

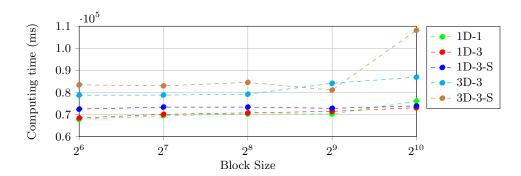

| Figura 4.23    | Comportamiento del tiempo de cómputo en milisegundos                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                | obtenidos probando diferentes configuraciones de los kernels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                | 2D en precisión sencilla mostrados en la Tabla 4.5. 82                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

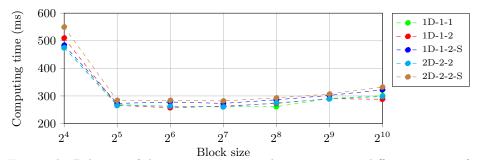

| Figura 4.24    | Comportamiento del tiempo de cómputo en milisegundos                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| _              | obtenidos probando diferentes configuraciones de los kernels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                | 2D en precisión doble, mostrados en la Tabla 4.6. 82                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

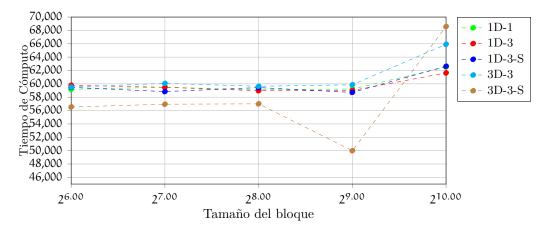

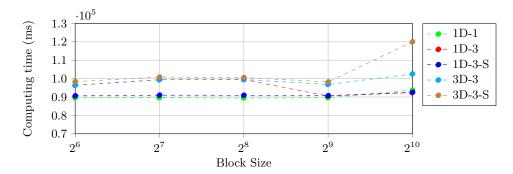

| Figura 4.25    | Comportamiento del tiempo de cómputo en milisegundos                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                | obtenidos probando diferentes configuraciones de los kernels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                | 3D en precisión sencilla mostrados en la Tabla 4.7. 83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

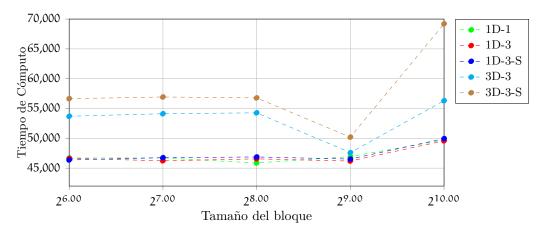

| Figura 4.26    | Comportamiento del tiempo de cómputo en milisegundos                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| O              | obtenidos probando diferentes configuraciones de los kernels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                | 3D en precisión doble mostrados en la Tabla 4.8 83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

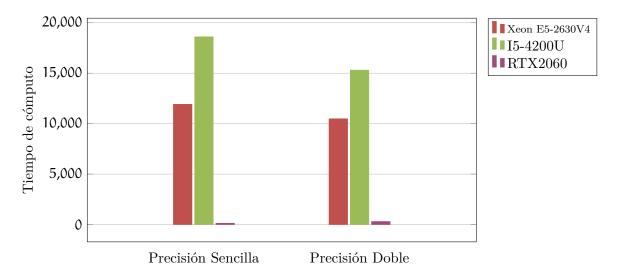

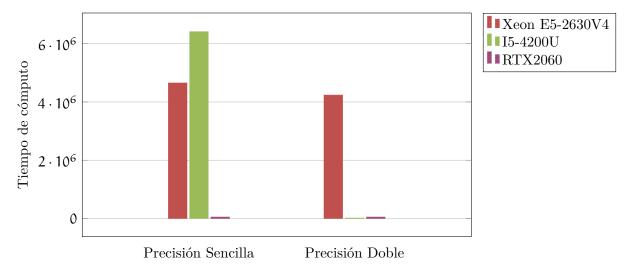

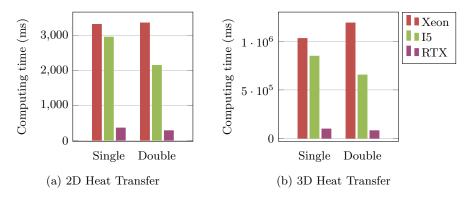

| Figura 4.27    | Comparación entre los tiempos de cómputo obtenidos en pre-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 8              | cisión sencilla, entre un Intel Xeon E52630V, un Intel 515                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                | 4200U y la tarjeta RTX2060, para el caso 2D. 84                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Figura 4.28    | Tiempos de cómputo obtenidos en precisión sencilla, entre                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 1 15 dr d 1.20 | un Intel Xeon E52630V, un Intel 5I5-4200U y la tarjeta                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |