# UNIVERSIDAD NACIONAL AUTÓNOMA DE MÉXICO

#### FACULTAD DE ESTUDIOS SUPERIORES CUAUTITLÁN

# DESARROLLO E IMPLEMENTACIÓN DE UN SISTEMA PARA PROCESAMIENTO DE IMÁGENES MEDIANTE EL USO DE UN DISPOSITIVO FPGA

#### **TESIS**

Que para obtener el título de

## INGENIERO EN TELECOMUNICACIONES SISTEMAS Y ELECTRÓNICA

#### PRESENTAN:

José Alejandro Maya Camacho

Rodrigo Santiago Rocha Varela

#### **ASESOR:**

Ing. José Luis Barbosa Pacheco

CUAUTITLÁN IZCALLI, ESTADO DE MÉXICO, 2020

UNAM – Dirección General de Bibliotecas Tesis Digitales Restricciones de uso

#### DERECHOS RESERVADOS © PROHIBIDA SU REPRODUCCIÓN TOTAL O PARCIAL

Todo el material contenido en esta tesis esta protegido por la Ley Federal del Derecho de Autor (LFDA) de los Estados Unidos Mexicanos (México).

El uso de imágenes, fragmentos de videos, y demás material que sea objeto de protección de los derechos de autor, será exclusivamente para fines educativos e informativos y deberá citar la fuente donde la obtuvo mencionando el autor o autores. Cualquier uso distinto como el lucro, reproducción, edición o modificación, será perseguido y sancionado por el respectivo titular de los Derechos de Autor.

MEXICO

#### FACULTAD DE ESTUDIOS SUPERIORES CUAUTITLÁN SECRETARÍA GENERAL DEPARTAMENTO DE EXÁMENES PROFESIONALES

ASUNTO: VOTO APROBATORIO

ACULTAD DE ESTODIOS

M. en C. JORGE ALFREDO CUÉLLAR ORDAZ DIRECTOR DE LA FES CUAUTITLAN PRESENTE

> ATN: I.A. LAURA MARGARITA CORTAZAR FIGUEROA Jefa del Departamento de Exámenes Profesionales de la FES Cuautitlán.

Con base en el Reglamento General de Exámenes, y la Dirección de la Facultad, nos permitimos comunicar a usted que revisamos el: Trabajo de Tesis

Desarrollo e implementación de un sistema para procesamiento de imágenes mediante el uso de un dispositivo FPGA.

Que presenta el pasante: JOSÉ ALEJANDRO MAYA CAMACHO

Con número de cuenta: 31201567-7 para obtener el Título de la carrera: Ingeniería en Telecomunicaciones,

Sistemas y Electrónica

Considerando que dicho trabajo reúne los requisitos necesarios para ser discutido en el EXAMEN PROFESIONAL correspondiente, otorgamos nuestro VOTO APROBATORIO.

#### ATENTAMENTE

"POR MI RAZA HABLARÁ EL ESPÍRITU"

Cuautitlán Izcalli, Méx. a 12 de marzo de 2020.

#### PROFESORES QUE INTEGRAN EL JURADO

|               | NOMBRE                                  | FIRMA      |

|---------------|-----------------------------------------|------------|

| PRESIDENTE    | Mtro. Jorge Buendía Gómez               |            |

| VOCAL         | Ing. José Luis Barbosa Pacheco          | fling E.   |

| SECRETARIO    | Ing. Noemi Hernández Dominguez          |            |

| 1er. SUPLENTE | Mtro. Leopoldo Martín del Campo Ramírez | - LA       |

| 2do. SUPLENTE | Ing. Jorge Alberto Vázquez Maldonado    | factorial. |

NOTA: los sinodales suplentes están obligados a presentarse el día y hora del Examen Profesional (art. 127).

LMCF/ntm\*

MEXICO

#### FACULTAD DE ESTUDIOS SUPERIORES CUAUTITLÁN SECRETARÍA GENERAL DEPARTAMENTO DE EXÁMENES PROFESIONALES

ASUNTO: VOTO APROBATORIO

M. en C. JORGE ALFREDO CUÉLLAR ORDAZ DIRECTOR DE LA FES CUAUTITLAN PRESENTE

> ATN: I.A. LAURA MARGARITA CORTAZAR FIGUEROA Jefa del Departamento de Exámenes Profesionales de la FES Cuantitlán.

Con base en el Reglamento General de Exámenes, y la Dirección de la Facultad, nos permitimos comunicar a usted que revisamos el: <u>Trabajo de Tesis</u>

Desarrollo e implementación de un sistema para procesamiento de imágenes mediante el uso de un dispositivo FPGA.

Que presenta el pasante: RODRIGO SANTIAGO ROCHA VARELA

Con número de cuenta: 31218871-7 para obtener el Título de la carrera: <u>Ingeniería en Telecomunicaciones</u>, <u>Sistemas y Electrónica</u>

Considerando que dicho trabajo reúne los requisitos necesarios para ser discutido en el **EXAMEN PROFESIONAL** correspondiente, otorgamos nuestro **VOTO APROBATORIO**.

#### **ATENTAMENTE**

"POR MI RAZA HABLARÁ EL ESPÍRITU"

Cuautitlán Izcalli, Méx. a 21 de enero de 2020.

#### PROFESORES QUE INTEGRAN EL JURADO

|                               | NOMBRE                                                                         | FIRMA       |

|-------------------------------|--------------------------------------------------------------------------------|-------------|

| PRESIDENTE                    | Mtro. Jorge Buendía Gómez                                                      | Jes.        |

| VOCAL                         | Ing. José Luis Barbosa Pacheco                                                 | firs?       |

| SECRETARIO                    | Ing. Noemi Hernández Dominguez                                                 | Phu'        |

| 1er. SUPLENTE                 | Mtro. Leopoldo Martin del Campo Ramirez                                        | 姬           |

| 2do. SUPLENTE                 | Ing. Jorge Alberto Vázquez Maldonado                                           | Australia . |

| NOTA: los sinodales suplentes | están obligados a presentarse el día y hora del Examen Profesional (art. 127). |             |

LMCF/ntm\*

#### **AGRADECIMIENTOS**

A mis padres Ma. Soledad Varela y José Pablo Rocha Jiménez:

Les agradezco por todo el amor incondicional y la confianza que me otorgaron. Gracias ustedes, soy la persona que hoy en día puede enfrentar todo tipo de problemas que se llegaran a presentar.

Espero que puedan observar a primera fila, todos los planes que se tienen para el futuro. Porque esos logros no solo serán míos, sino también suyos. Yo sé que aún me falta mucho por aprender. Pero sus enseñanzas, me guiarán por el buen camino.

A Humberto Rocha Varela y José Pablo Rocha Varela:

A mis hermanos, que han sido mis compañeros de toda la vida. Les agradezco por su cariño, experiencias y su protección que siempre me compartieron. Les tengo mucho respeto y admiración.

A mi profesor José Luis Barbosa Pacheco:

Siempre nos mostró el camino del conocimiento, de la curiosidad y de ir más allá de lo que nos ofrecen en el colegio. Alimentando nuestras ideas con sus sabios consejos que nos guiaron por la senda del estudio.

A mis compañeros:

Junto a los que emprendí el feliz camino de la vocación y a los cuales agradezco la estimación que me brindaron.

A mi Facultad de Estudios Superiores Cuautitlán:

Para todas aquellas personas que de alguna manera participaron en la elaboración de este trabajo.

Rodrigo Santiago Rocha Varela

Primeramente, quiero agradecer a mi familia, ya que sin ellos este trabajo no hubiera sido posible. A mi madre quien siempre ha estado allí cuando la he necesitado, por haber trabajado arduamente para que no me faltara nada, por todos esos consejos y el tiempo que dedicó para hacerme sentir mejor en mis peores momentos. A mi padre que siempre ha sido mi guía y un ejemplo que seguir, por inculcarme el gusto a estudiar y por todos los regaños que en su momento no entendía, pero hoy, cobran sentido al ver lo que he logrado. Por supuesto a mi abuelita, por haberme cuidado mientras mis padres trabajaban, por enseñarme modales y valores, además de siempre haberme mostrado un cariño incondicional. No hay palabras para agradecer todo lo que han hecho por mí y por hacerme el hombre que soy hoy.

A mis amigos, ya que puedo decir que estoy rodeado de personas increíbles, he aprendido mucho de todos ustedes, les agradezco por apoyarme cuando tuve algún problema, por darme un consejo cuando no tenía la más mínima idea de que hacer, por impulsarme y por creer en mí, estoy seguro de que el camino habría sido muy distinto si no hubiesen estado ahí. Gracias por todo.

A mi asesor el Ingeniero José Luis Barbosa por todo su apoyo, paciencia y sobre todo sus enseñanzas, que no solo se limitaron al ámbito académico, gracias por su dedicación a la enseñanza y por transmitirme ese gusto por la investigación y el desarrollo que me ayudaron a crecer como ingeniero.

Por último, quiero agradecer a la Universidad Nacional Autónoma de México y a la Facultad de Estudios Superiores Cuautitlán por todo lo aprendido en sus aulas y por todas esas experiencias vividas en sus instalaciones que me ayudaron a desarrollarme tanto en el ámbito profesional como en el personal, es un orgullo y un honor ser parte de la UNAM. "Por mi raza hablará el espíritu".

## CONTENIDO

| Índice de figuras                                                                | II   |

|----------------------------------------------------------------------------------|------|

| Índice de tablas                                                                 | V    |

| Índice de Pseudocódigos                                                          | V    |

| Introducción                                                                     | Vl   |

| Justificación                                                                    | VIII |

| Objetivo                                                                         | XI   |

| Objetivos particulares                                                           | XI   |

| Capítulo 1 Marco teórico                                                         | 1    |

| 1.1 Breve historia del lenguaje de descripción de hardware                       | 1    |

| 1.1.1 Diseño en VHDL                                                             | 3    |

| 1.1.2 Elementos básicos de VHDL                                                  | 4    |

| 1.2 Antecedentes.                                                                | 5    |

| 1.2.1 Memorias programables de solo lectura (PROM).                              | 6    |

| 1.2.2 Dispositivos Lógicos Programables (PLD)                                    |      |

| 1.2.3 Arreglos Lógicos Programables (PLA)                                        |      |

| 1.2.4 Lógica de Arreglos Programables (PAL)                                      | 8    |

| 1.2.5 Arreglos Lógicos Genéricos (GAL)                                           | 9    |

| 1.2.5 Dispositivos Lógicos Programables Complejos (CPLD)                         | 9    |

| 1.2.6 Arreglo de Compuertas Programables en Campo (FPGA)                         | 11   |

| 1.3 Procesamiento de imágenes en FPGA                                            | 11   |

| 1.3.1 Videojuegos en un dispositivo FPGA                                         | 13   |

| 1.4 Diseño con FPGA                                                              | 15   |

| Capítulo 2 Conceptos para el diseño del sistema de procesamiento de imágenes     | 19   |

| 2.1 Diagrama general de la solución                                              | 19   |

| 2.2 Imágenes digitales y audio.                                                  | 21   |

| 2.2.1 Las imágenes digitales                                                     | 21   |

| 2.2.2 El sonido                                                                  | 23   |

| 2.2.3 Conversión Analógico-Digital                                               | 23   |

| 2.3 Estándares y protocolos de comunicación para los puertos de entrada y salida | 25   |

| 2.3.1 Estándar VGA                                                               | 25   |

| 2.3.2 Protocolo I2S.                                                             | 28   |

| Canítulo 3 Diseño de una anlicación nara videojuegos                             | 32   |

| 3.1 Planteamiento de la aplicación                                 | 32  |

|--------------------------------------------------------------------|-----|

| 3.2 Diseño de la aplicación.                                       | 33  |

| 3.2.1 Definición de los módulos del sistema                        | 35  |

| 3.2.1 Diseño conceptual (Top Level Design)                         | 36  |

| 3.3 Núcleo de la aplicación                                        | 39  |

| 3.4 Controles                                                      | 41  |

| 3.5 Audio                                                          | 44  |

| 3.6 Control de las imágenes                                        | 45  |

| Capítulo 4 Implementación en la tarjeta de desarrollo              | 50  |

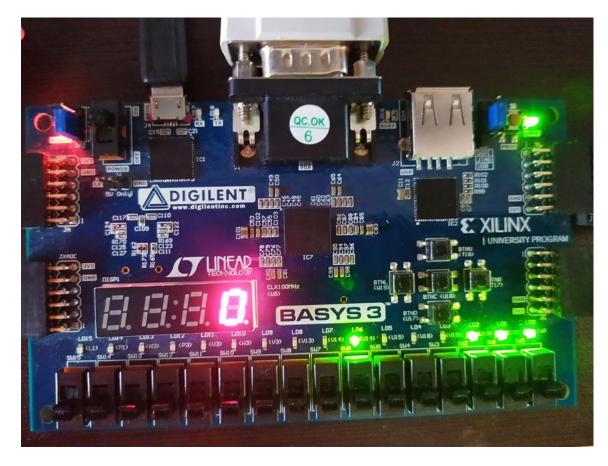

| 4.1 Tarjeta de desarrollo BASYS 3.                                 | 50  |

| 4.2 Implementación y desarrollo.                                   | 52  |

| 4.2.1 Módulo Divisor de frecuencia                                 | 52  |

| 4.2.2 Módulo VGA 640x480                                           | 55  |

| 4.2.3 Despliegue de figuras en pantalla (Módulo Laberinto)         | 58  |

| 4.2.4 Efecto del movimiento de imágenes (Módulo de los Personajes) | 62  |

| 4.2.5 Mandos de control                                            | 65  |

| 4.2.6 Despliegue de Imágenes                                       | 66  |

| 4.2.7 Implementación del audio                                     | 70  |

| 4.2.8 Interacción con el Puerto VGA (Módulo de control VGA)        | 72  |

| Capítulo 5 Resultados                                              | 76  |

| Conclusiones                                                       | 84  |

| Apéndice                                                           | 86  |

| Apéndice 1 Código del sistema - Divisor de frecuencia.             | 86  |

| Apéndice 2 Código del sistema - VGA640x480                         | 90  |

| Apéndice 3 Código del sistema - Laberinto                          | 92  |

| Apéndice 4 Código del sistema - ArticaleDisplay.                   | 97  |

| Apéndice 5 Código del sistema - Acceso a la ROM de Articale.       | 108 |

| Apéndice 6 Código del sistema - Control VGA.                       | 109 |

| Apéndice 7 Código del sistema - Núcleo del sistema.                | 112 |

| Apéndice 8 Código del sistema - Controlador del Audio              | 115 |

| Apéndice 9 Código del sistema - Controlador de los mandos.         | 119 |

| Bibliografía                                                       | 123 |

## ÍNDICE DE FIGURAS

| Capítulo 1                                                                              |    |

|-----------------------------------------------------------------------------------------|----|

| Figura 1. 1 Proceso de diseño en VHDL                                                   | 4  |

| Figura 1. 2 Entidad en VHDL.                                                            | 5  |

| Figura 1. 3 Configuración de una PROM.                                                  |    |

| Figura 1. 4 Configuración de un PLA.                                                    | 8  |

| Figura 1. 5 Configuración de un PAL.                                                    | 9  |

| Figura 1. 6 Macrocelda de una GAL.[3]                                                   | 10 |

| Figura 1. 7 Estructura básica de un CPLD.                                               | 11 |

| Figura 1. 8 Estructura de una FPGA                                                      | 12 |

| Figura 1. 9 Tabla de patrones                                                           | 14 |

| Capítulo 2                                                                              |    |

| Figura 2. 1 Diagrama general del sistema de procesamiento de imágenes                   |    |

| Figura 2. 2 Ejemplo de baja (Imagen 1) y alta resolución (Imagen 2) en una misma imagen |    |

| Figura 2. 3 Muestreo de una señal de audio.                                             |    |

| Figura 2. 4 Flujo de conversión Analógico-Digital                                       |    |

| Figura 2. 5 Diagrama de conexiones del puerto VGA con la FPGA.[18]                      |    |

| Figura 2. 6 Diagrama de señales síncronas en pantalla                                   |    |

| Figura 2. 7 Diagrama general de tiempos para las señales síncronas                      |    |

| Figura 2. 8 Señales de sincronización horizontal y vertical.                            |    |

| Figura 2. 9 Diagrama básico de conexión por medio del protocolo I2S                     |    |

| Figura 2. 10 Diagrama de tiempos de transmisión I2S.                                    |    |

| Figura 2. 11 Transmisión I2S justificada a la izquierda                                 | 31 |

| Capítulo 3                                                                              |    |

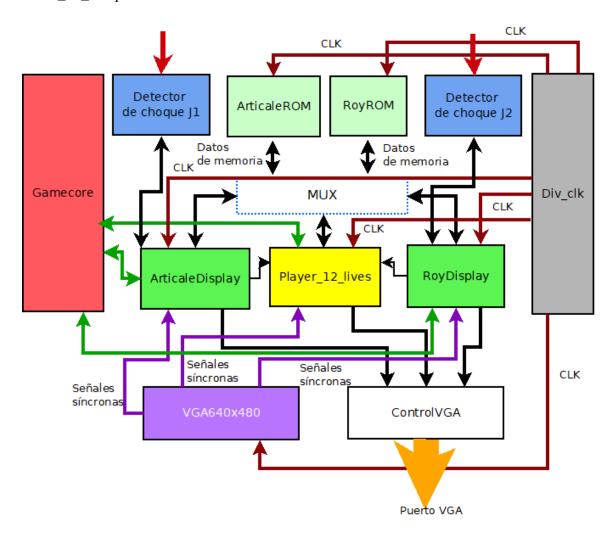

| Figura 3. 1 Modelo general del sistema completo.                                        |    |

| Figura 3. 2 Diagrama de flujo general del proceso de la aplicación                      |    |

| Figura 3. 3 Diseño de alto nivel (Top level design).                                    |    |

| Figura 3. 4 Integración por punto a punto e integración por sistema centralizado        |    |

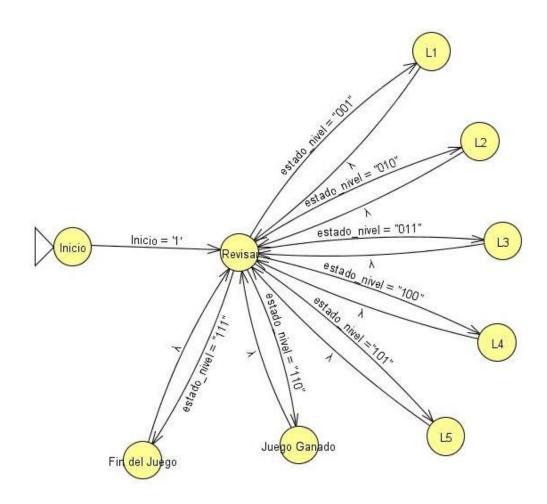

| Figura 3. 5 Máquina de estados para el sistema integrador central                       |    |

| Figura 3. 6 Mando para puerto de entrada de datos.                                      |    |

| Figura 3. 7 Diagrama de tiempos para el envío de datos por los mandos                   |    |

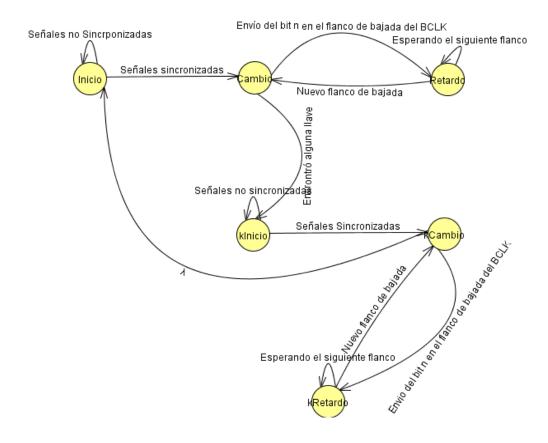

| Figura 3. 8 Máquina de estados de los mandos de entrada                                 |    |

| Figura 3. 9 Máquina de estados para reproducir sonido                                   |    |

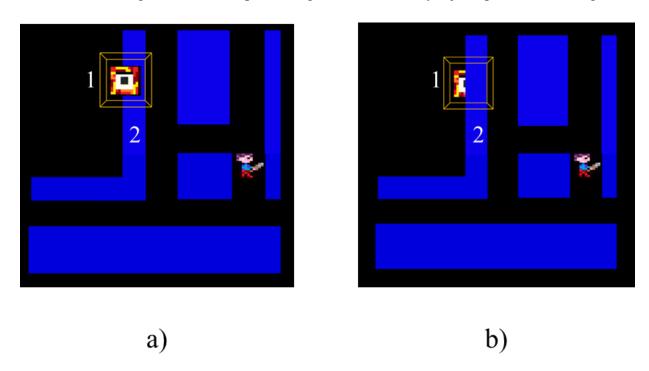

| Figura 3. 10 Visualización en pantalla de los tipos de imágenes                         |    |

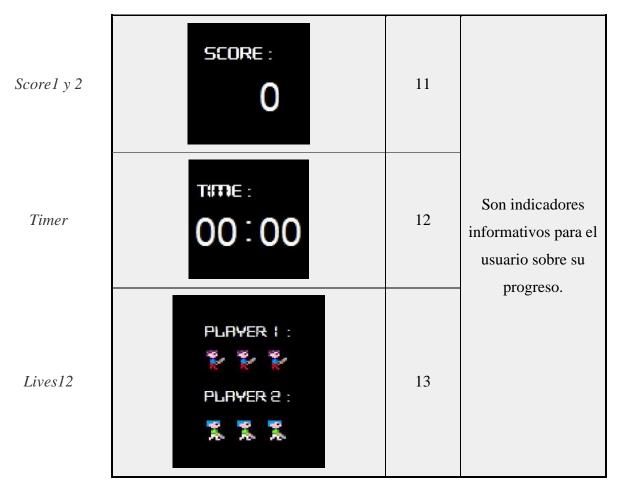

| Figura 3. 11 Jerarquía de imágenes.                                                     | 46 |

| Figura 3, 12 Privilegios de imágenes de presentación y de finalización                  | 47 |

| Capítulo 4                                                                                          |    |

|-----------------------------------------------------------------------------------------------------|----|

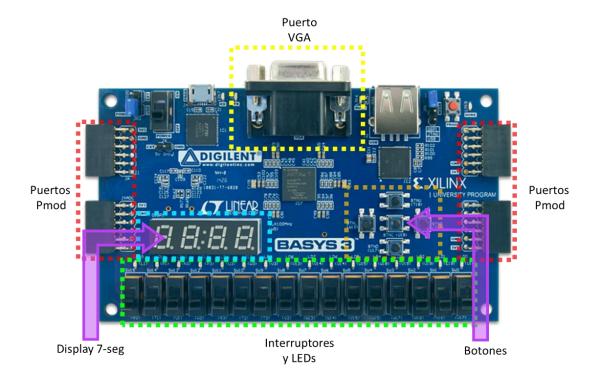

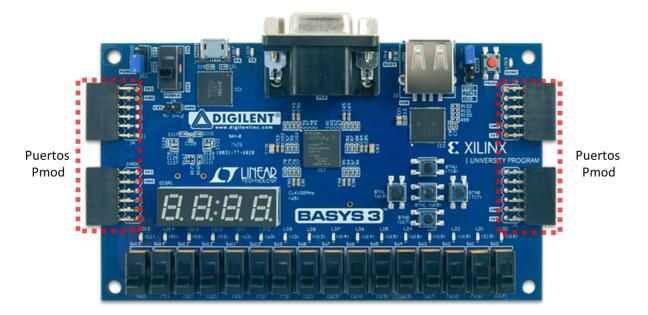

| Figura 4. 1 Tarjeta BASYS 3 indicando los puertos utilizados.[22]                                   | 51 |

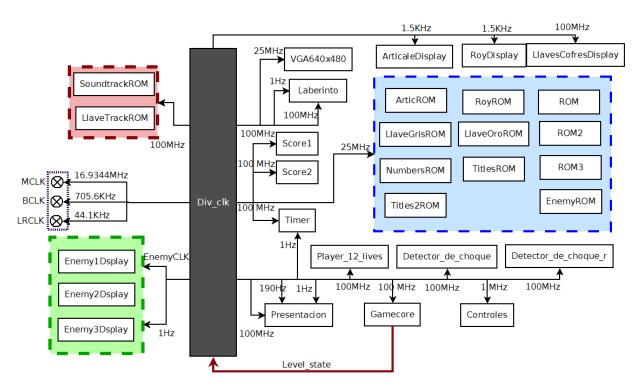

| Figura 4. 2 Interacción con el módulo de divisor de frecuencia                                      | 54 |

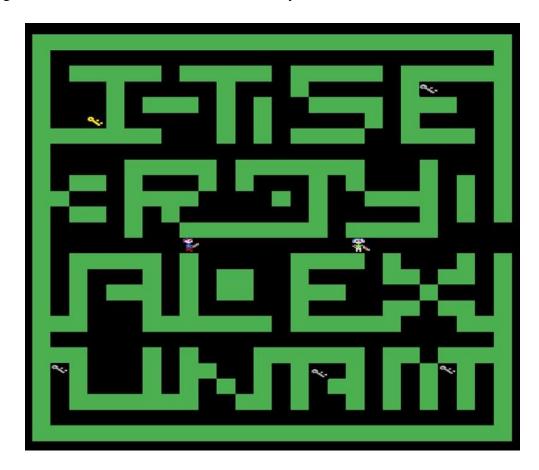

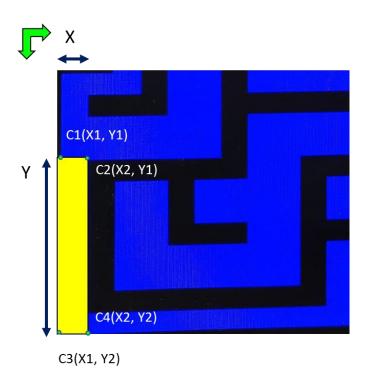

| Figura 4. 3 Despliegue en pantalla del laberinto.                                                   | 58 |

| Figura 4. 4 Interacción entre el módulo Laberinto                                                   | 59 |

| Figura 4. 5 Despliegue del laberinto en pantalla                                                    | 60 |

| Figura 4. 6 Máquina de estados del módulo Laberinto.                                                | 61 |

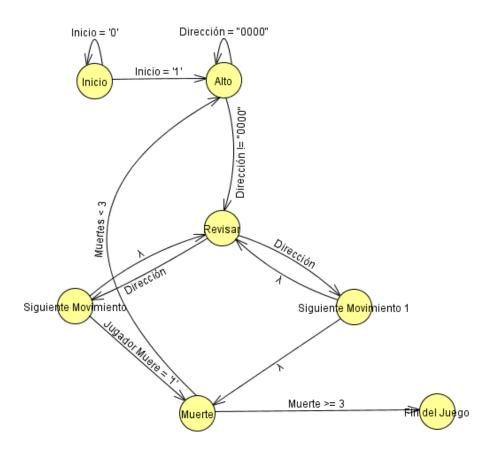

| Figura 4. 7 Máquina de estados del personaje principal                                              |    |

| Figura 4. 8 Máquina de estados del personaje principal                                              | 63 |

| Figura 4. 9 Máquina de estados del personaje principal                                              | 64 |

| Figura 4. 10 Módulos involucrados con Controles.                                                    | 65 |

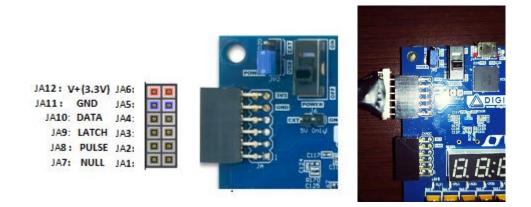

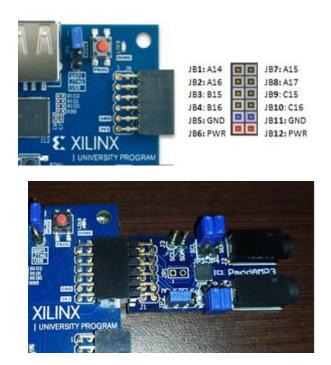

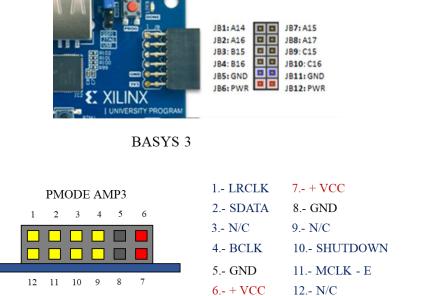

| Figura 4. 11 Puertos disponibles de la tarjeta. [22]                                                | 66 |

| Figura 4. 12 Diseño de pines de entrada para los mandos                                             | 66 |

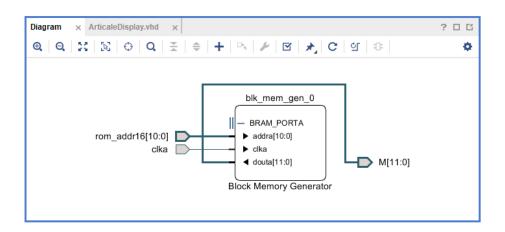

| Figura 4. 13 Bloque de memoria para el resguardo de las imágenes                                    | 67 |

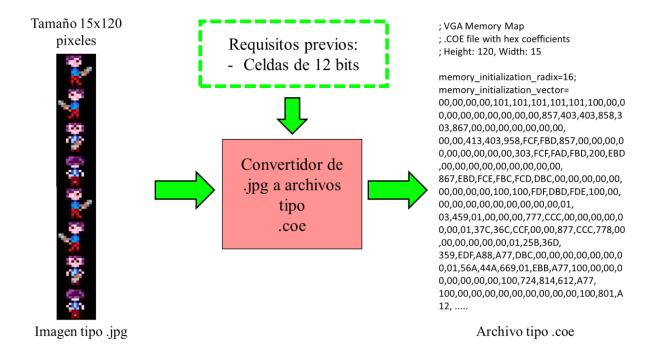

| Figura 4. 14 Generación de los archivos tipo. coe con herramientas de uso libre para almacenamiento |    |

| imágenes                                                                                            | 68 |

| Figura 4. 15 Entidad generada para el bloque de memoria.                                            | 69 |

| Figura 4. 16 Definición del puerto de salida y conexión con del dispositivo                         | 71 |

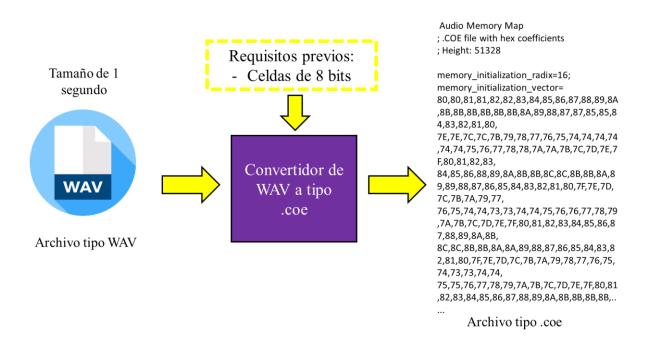

| Figura 4. 17 Generación de los archivos tipo .coe.                                                  | 71 |

| Figura 4. 18 Pines definidos por la tarjeta y por el dispositivo PMODE AMP3                         | 72 |

| Figura 4. 19 Controlador de señales hacia el puerto VGA                                             | 73 |

| Figura 4. 20 Conexiones entre el puerto VGA y el FPGA                                               | 75 |

| Capítulo 5                                                                                          |    |

| Figura 5. 1 Recursos utilizados en la Tarjeta BASYS 3.                                              | 76 |

| Figura 5. 2 Indicadores de las señales enviadas por el núcleo del sistema                           | 77 |

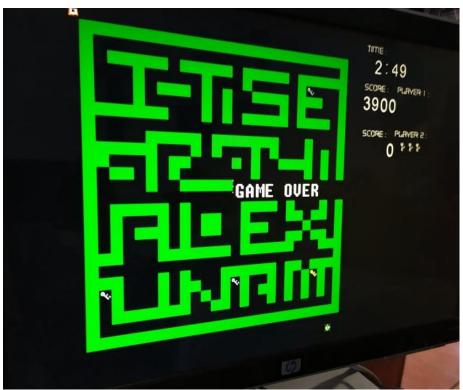

| Figura 5. 3 Indicadores del estado "fin de juego"                                                   | 79 |

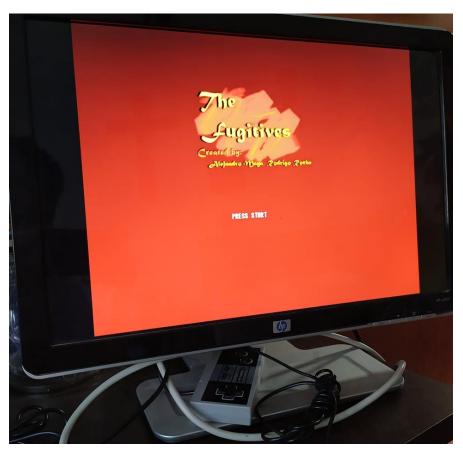

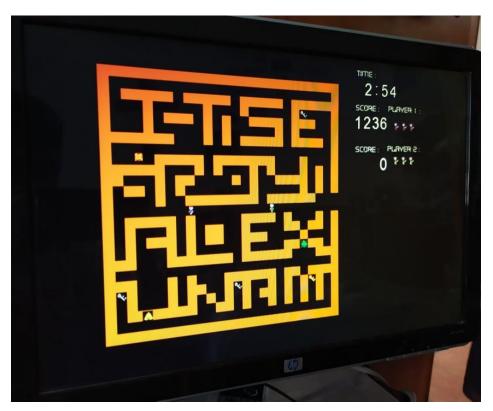

| Figura 5. 4 Estado de presentación y Nivel 1                                                        | 80 |

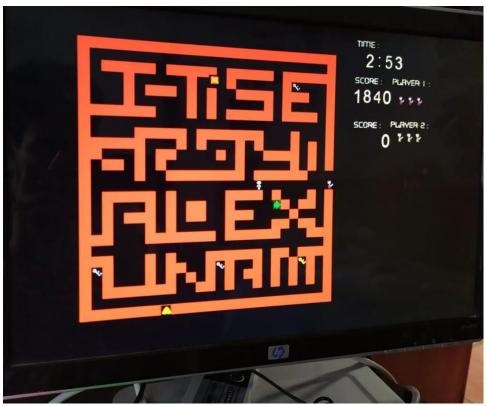

| Figura 5. 5 Estado Nivel 2 y Nivel 3.                                                               | 81 |

| Figura 5. 6 Estado Nivel 4 y Nivel 5.                                                               | 82 |

| Figura 5. 7 Estado Fin del juego y Juego Ganado.                                                    | 83 |

## ÍNDICE DE TABLAS

| Tabla 1 Comparación entre dispositivos de diseño digital         | VII |

|------------------------------------------------------------------|-----|

| Tabla 2 Jerarquía de las imágenes                                | 49  |

| Tabla 3 Tabla comparativa de dispositivos con FPGA en el mercado | 50  |

| Tabla 4 Frecuencias de movimiento de los enemigos                | 54  |

| Tabla 5 Colores a 12 bits para cada nivel del juego              | 61  |

| Tabla 6 Tamaño y gestión de datos para los bloques de memoria    | 78  |

## ÍNDICE DE PSEUDOCÓDIGOS

| Pseudocódigo 1 - Divisor de frecuencia de 100 MHz a 25 MHz que requiere el módulo VGA640x480 | 53 |

|----------------------------------------------------------------------------------------------|----|

| Pseudocódigo 2 - Señal síncrona horizontal.                                                  | 56 |

| Pseudocódigo 3 - Señal síncrona vertical.                                                    | 57 |

| Pseudocódigo 4 - Señal de habilitación en pantalla                                           | 57 |

| Pseudocódigo 5 - Algoritmo para obtener la dirección de memoria                              | 70 |

| Pseudocódigo 6 - Algoritmo para definición de la jerarquía                                   |    |

#### INTRODUCCIÓN

Durante la década del 2010, se han realizado investigaciones por parte de las empresas dedicadas al diseño de microprocesadores para dispositivos electrónicos, buscando desarrollar e innovar nuevos modelos arquitectónicos para la implementación en nuevas áreas de la electrónica. Una de las empresas que ha estado trabajando en ello es Microsoft©, la cual lanzó una iniciativa para realizar investigaciones, desarrollos e innovaciones combinando las nuevas tecnologías (en especial el uso de dispositivos de silicio como son los Arreglos Genéricos Programables en Campo o también conocidos como FPGA) ciertas áreas de desarrollo como son: la manipulación del proceso paralelo en la utilización de *big data*<sup>1</sup>, desarrollo y utilización de la nube como lo es Bing®, aplicaciones de inteligencia artificial, desarrollo en conjunto de aplicaciones con los procesadores Intel® para aumento de velocidad y flexibilidad con reducción de costos y para aplicaciones de tipo *machine learning*<sup>2</sup>.

Varias de estas investigaciones han desarrollado formas de aprendizaje sobre las nuevas tecnologías como son los dispositivos de lógica programable (como los FPGA por mencionar alguna de ellas), donde se realizan desarrollos de sistemas de procesamiento basados en videojuegos[1], aportando un mejor entendimiento de los sistemas basados en lógica programable de descripción de hardware. Dando como resultado una mejora en el entendimiento de los lenguajes basados en descripción de hardware, diseños, delimitaciones y conceptualizaciones que se pudieran llegar durante el desarrollo. Además del apoyo en la búsqueda de nuevas herramientas que pudiesen complementar los proyectos como son dispositivos de entrada y salida (el comprender e implementar protocolos y estándares necesarios para la utilización de éstos).

La utilización de dispositivos de entrada y salida conlleva la búsqueda de información referente a éstos, la visualización en pantalla a través del puerto VGA es una buena opción para la implementación de aplicaciones basadas en dispositivos FPGA. Varios artículos presentan implementaciones y desarrollos sobre diversas tarjetas con dispositivos FPGA para el procesamiento de imágenes desplegadas en pantallas a través del puerto VGA[2], obteniendo buenos resultados en rendimientos y ventajas sobre el espacio en memoria y el tamaño en pantalla de las imágenes desplegadas por medio del estándar VGA con resolución 640x480.

Dado el interés generado por lo anterior, este trabajo buscará desarrollar y evaluar una aplicación de procesamiento de imágenes, a través de un sistema simple basado en un videojuego diseñado e implementado con varios sistemas interactuando al mismo tiempo sobre una misma tarjeta de desarrollo. El diseño propuesto hace uso de varios recursos, por ejemplo:

<sup>&</sup>lt;sup>1</sup> Big data se refiere a la utilización manipulación de grandes cantidades de datos. Lo caracteriza por el volumen, variabilidad, velocidad, captura y análisis de datos.

<sup>&</sup>lt;sup>2</sup> Machine learning es considerada un área de la inteligencia artificial donde los sistemas aprenden los patrones para realización de predicciones de comportamientos futuros.

desplegar imágenes, reproducir audio y administrar registros, por lo que un FPGA podría realizar todas esas tareas de forma independiente y agruparlas en un solo diseño, además de ofrecer flexibilidad para implementar sobre este dispositivo varios de los protocolos de comunicación y estándares en forma de lenguaje descriptivo.

Para implementar dicho sistema es necesario utilizar algunas herramientas para el desarrollo de la aplicación como son: lógica programable (una forma de expresar circuitos lógicos por medio de un lenguaje de programación) ofreciendo un procesamiento paralelo aplicado en un FPGA entre los módulos internos del sistema, bloques de memoria (celdas independientes que tienen el propósito de guardar datos) que serán utilizados para almacenar las imágenes de la aplicación y por último los puertos de entrada y salidas (túneles que interactúan con el exterior del sistema) con el fin de ofrecerle al usuario una interacción que pueda comprender durante la ejecución de la aplicación.

Dichos dispositivos se tornan ideales y flexibles en el proceso de diseño porque permiten ser desarrollados por medio de un lenguaje de descripción de hardware, de esta manera se pueden dividir las tareas entre cada uno de los sistemas involucrados en el procesamiento de imágenes.

Este trabajo consta de 5 capítulos, el primer capítulo explica el marco teórico para poner en contexto el tema de la lógica programable, abordando de forma general su funcionamiento, componentes y características que lo hacen destacar para cumplir el objeto de estudio en el procesamiento de imágenes y sus aplicaciones en los videojuegos; en el segundo capítulo se explicarán los conceptos necesarios para el diseño de la aplicación de procesamiento de imágenes, tanto los sistemas involucrados, la forma de interpretar los datos de entrada, la manipulación de los datos y el procesamiento de la salida de datos requeridos para el diseño, abarcando los protocolos de comunicación y algunos estándares; el tercer capítulo se describirá el diseño de la aplicación del sistema de procesamiento de imágenes aplicado en un sistema de videojuegos; en el cuarto capítulo se mostrará la implementación de los sistemas descritos sobre la tarjeta de desarrollo; y en el quinto capítulo se mostrarán los resultados obtenidos de la implementación del sistema.

## JUSTIFICACIÓN

El desarrollo de este trabajo es derivado por el interés de conocer y evaluar las características de los dispositivos FPGA que están evolucionando junto con las nuevas tecnologías y cómo es el impacto que tienen en la manipulación de estos en sistemas aplicados, entre ellos el procesamiento de imágenes.

A nivel académico se busca comprobar las ventajas que tiene el trabajar con estos dispositivos en el área de la electrónica y su viabilidad en el manejo de imágenes con dispositivos con FPGA evaluando los recursos que disponen.

A nivel institución se muestra este trabajo basado en estudios con FPGA para destacar la importancia de estos dispositivos, debido a que cambiarán la forma de diseñar nuevas aplicaciones para las diferentes áreas de la ingeniería como son: bioingeniería, ingeniería aeroespacial, telecomunicaciones, etc.

El hecho de usar un dispositivo FPGA tiene ventajas frente a otro tipo de sistemas, por ejemplo, el procesamiento de algoritmos de forma concurrente ha acelerado los tiempos de ejecución respecto a una programación secuencial, también resulta ser más económicos respecto a otros dispositivos como se muestra en la tabla 1.

|            | Rendimiento | Costo            | Flexibilidad |

|------------|-------------|------------------|--------------|

| ASIC       | Alto        | \$482.41 USD [3] | Baja         |

| Procesador | Bajo        | \$20.00 USD [4]  | Alta         |

| FPGA       | Medio       | \$149.00 USD [5] | Alta         |

Tabla 1 Comparación entre dispositivos de diseño digital.

De la tabla 1 se puede observar que los FPGA son una alternativa muy atractiva para el desarrollo de proyectos al no ser tan costosas como un ASIC (circuitos integrados diseñados a la medida) y ser igual de flexibles como un microprocesador, pero con un mayor rendimiento.

Una de las características que puede ofrecer los dispositivos FPGA con respecto a un CPU es la baja latencia<sup>3</sup>. Con un FPGA es factible obtener una latencia aproximadamente de 1

<sup>&</sup>lt;sup>3</sup> Latencia es la velocidad de respuesta que se tiene cuando el emisor transmite un dato y el remitente lo responde.

microsegundo a comparación de un CPU con 50 microsegundos[6], con estos tiempos se puede hacer la diferencia en la respuesta para un sistema programado del piloto automático de un avión de combate. Además, la latencia de un FPGA es mucho más determinista porque no depende de un sistema operativo para poder realizar algún envío de datos entre otros dispositivos, como lo podría ser la comunicación por medio de los buses de entrada y salida (el puerto USB por mencionar alguno).

La conectividad que ofrece los FPGA es mucho más diversa. Esto se debe a que puede conectarse con cualquier fuente de datos directamente a través de los pines del dispositivo. Contrastando contra los CPU que deben realizar sus conexiones a través de los buses estandarizados y depender directamente de la respuesta del sistema operativo (ofrece un mayor ancho de banda para el envío de datos). Un ejemplo de este caso es el sistema LOFAR<sup>4</sup> que genera una gran cantidad de datos y que deben ser reducidos para poder ser enviados de tal forma que sean manejables. Por lo que el instituto ASTRON<sup>5</sup> diseñó un tablero con 4 dispositivos FPGA que manipulan más datos por segundo que el intercambio de internet. [6]

Otra característica de los FPGA es la eficiencia energética, eso se debe a que las tarjetas con FPGA tienen sus propios puertos de entrada y salida y no requieren una computadora de tipo Host para funcionar, ahorrando así energía y dinero.

Se debe observar cuales son las medidas que las empresas toman para ir actualizando y mejorando los nuevos sistemas como lo son: el desarrollo de información en la nube (o Cloud); implementación de nuevas tecnologías de IoT (Internet de las cosas o *Internet of Things*); la mejora de procesadores (como lo es el dispositivo *Intel Stratix 10 DX*[7] por mencionar alguna), donde ofrecen un procesador con un dispositivo FPGA que aumenta la aceleración de las cargas de trabajo.

Un ejemplo de lo anterior, es la empresa INTEL® con la compra de ALTERA®[8], donde tiene una visión en el futuro utilizando dispositivos FPGA para desarrollar nuevos productos con mejores características y rendimientos. Otra de ellas fue Microsoft©, lanzando

IX

<sup>&</sup>lt;sup>4</sup> LOFAR (por sus siglas en inglés Low Frecuency Array) es una red distribuida de sensores multipropósito utilizado principalmente como radiotelescopio para las áreas de la astronomía, geofísica y agronomía.

<sup>&</sup>lt;sup>5</sup>ASTRON es un Instituto para la radio astronomía en Países Bajos (Netherlands).

| ra mejorar áreas me | ncionadas anteri | ormente. |  |  |

|---------------------|------------------|----------|--|--|

|                     |                  |          |  |  |

|                     |                  |          |  |  |

|                     |                  |          |  |  |

|                     |                  |          |  |  |

|                     |                  |          |  |  |

|                     |                  |          |  |  |

|                     |                  |          |  |  |

|                     |                  |          |  |  |

|                     |                  |          |  |  |

|                     |                  |          |  |  |

|                     |                  |          |  |  |

|                     |                  |          |  |  |

|                     |                  |          |  |  |

|                     |                  |          |  |  |

|                     |                  |          |  |  |

|                     |                  |          |  |  |

|                     |                  |          |  |  |

|                     |                  |          |  |  |

|                     |                  |          |  |  |

|                     |                  |          |  |  |

## OBJETIVO

Diseñar e implementar un sistema de procesamiento de imágenes con un sistema embebido en FPGA, utilizando el lenguaje de descripción de hardware VHDL.

### **OBJETIVOS PARTICULARES**

- Desarrollar una plataforma de procesamiento de imágenes haciendo uso eficiente de los recursos de hardware de una FPGA.

- Implementar sobre la tarjeta FPGA los protocolos de comunicación necesarios para el sistema.

- Implementar el diseño del sistema de procesamiento de imágenes usando lenguaje VHDL por medio de una tarjeta FPGA BASYS 3.

## CAPÍTULO 1 MARCO TEÓRICO

En este capítulo se fundamentarán los conceptos teóricos necesarios para la comprensión y desarrollo del presente trabajo de tesis. Se dará una idea general de los conceptos principales utilizados y sus características más importantes. Primero se va a definir el lenguaje de descripción de hardware con el que se realizará el código del proyecto, más adelante se abordarán las características de un FPGA y las ventajas de utilizarlas para el diseño de sistemas digitales.

#### 1.1 BREVE HISTORIA DEL LENGUAJE DE DESCRIPCIÓN DE HARDWARE

El desarrollo de circuitos integrados digitales programables y la necesidad de desarrollar aplicaciones cada vez más complejas hizo que las herramientas tradicionales se volvieran ineficientes. Como consecuencia, las empresas desarrollaron los lenguajes de descripción de hardware (HDL por sus siglas en inglés *Hardware Description Languaje*).

Hay diferentes formas de describir en HDL:

- a) Funcional: en esta forma se pueden representar los circuitos combinacionales como pueden ser sumadores, multiplicadores, codificadores, decodificadores o conversores de código utilizando funciones elementales como AND, OR, NOT, XOR, XNOR.

- b) Procedimental: los valores asignados se describen mediante un procedimiento, el cual se ejecuta ante el cambio de señales, mismos que pueden representar circuitos combinacionales o secuenciales utilizando sentencias o instrucciones como if-else, case, for o while.

- c) Estructural: en este modelo se realiza el diseño de todos los módulos y conexiones que se utilizarán obteniendo al final un diagrama que contiene los componentes, procesos y

lazos de los que se compone el sistema conocido como diagrama de alto-nivel (Top-Level).

Algunos tipos de HDL que existen son:

- ABEL-HDL que es un tipo de lenguaje de descripción que soporta una variedad de entradas incluyendo ecuaciones de alto nivel, diagramas de estados y tablas de verdad.

- SystemC es un conjunto de librerías y macros implementadas para ser utilizadas como extensión de C++, esta puede agregar modelos de constructores<sup>6</sup> como: la concurrencia, relojes, módulos e interconexiones en base al núcleo de C++.

- Verilog es uno de los lenguajes de descripción de hardware más usados, permite usar diferentes niveles de descripción de sistemas digitales en un mismo ambiente, admite la descripción estructural del diseño en base a los componentes básicos como transistores, compuertas lógicas, multiplexores, etc., los cuales se enfocan principalmente en la conducta del sistema.

Con el fin de estandarizar los sistemas desarrollados, el IEEE<sup>7</sup> y el Departamento de Defensa de los Estados Unidos iniciaron el desarrollo de un lenguaje llamado VHDL, su nombre viene de VHSIC que significa *Very High Speed Integrated Circuit* y HDL de las siglas *Hardware Description Language*, es decir Lenguaje de Descripción de Hardware para Circuitos Integrados de Velocidad Muy Alta.

El lenguaje VHDL fue concebido para cubrir varias necesidades que surgen durante el proceso de diseño. Permite realizar una descripción funcional o de comportamiento del circuito, utilizando técnicas procedimentales. Asimismo, permite describir la estructura del diseño y declarar las entidades y subentidades que lo forman especificando una jerarquía entre las mismas y sus interconexiones. Por último, permite simular el diseño con herramientas de síntesis especiales, para poder abstraer la descripción de un circuito, hasta obtener un diseño solamente estructural.

<sup>&</sup>lt;sup>6</sup> Un constructor son variables, métodos y funciones que pueden ser utilizados cuando se inicializa o se crea el objeto.

<sup>&</sup>lt;sup>7</sup> El IEEE (por sus siglas en ingles The *Institute of Electrical and Electronic Engineers*). Es una organización dedicada a la normalización de procesos en el área de ingeniería a nivel mundial.

Las características más importantes de VHDL son las siguientes:

- Sintaxis parecida al Lenguaje ADA<sup>8</sup>.

- Interfaz única que permite ser conectada a otros elementos.

- Comportamiento preciso.

- Estructura jerárquica.

- Se puede simular cualquier operación lógica y de temporización.

#### 1.1.1 DISEÑO EN VHDL

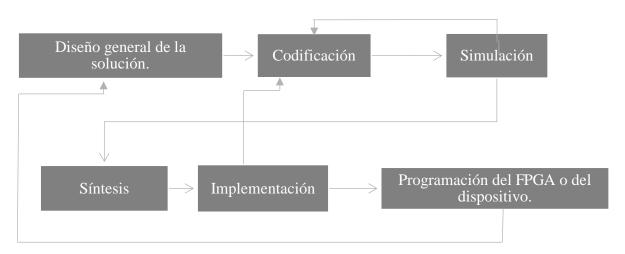

VHDL permite describir de forma estructurada un circuito, es decir, diseñarlo a partir de pequeños circuitos más sencillos, además, para desarrollar estos circuitos se debe seguir un proceso de diseño que va a permitir elaborar de forma estructurada cada módulo planteando varias etapas en el proceso, donde, de producirse un error, debe ser corregirlo antes de proceder al siguiente paso. Las etapas de diseño son las siguientes:

- Análisis: recopilación de todos los requerimientos funcionales obtenidos durante una etapa de descubrimiento.

- Delimitación: parte del proceso donde se definen los procesos de investigación, tiempos de desarrollo y recursos disponibles.

- Conceptualización: plasmar una idea generalizada con base al análisis realizado y delimitaciones definidas previamente.

- Definición del problema: esta etapa es considerada crucial, porque puede decidir el tipo de preguntas y la calidad de resultados que se desean obtener durante todo el proceso. Además de plantear una solución para generar una hipótesis que definirá el rumbo que tomará el diseño.

- Diseño general de la solución (Top Level): en esta etapa se trata al circuito como una caja negra, donde solo se observan las entradas y salidas de los diferentes módulos que conforman el sistema y cómo se comunican entre sí.

<sup>&</sup>lt;sup>8</sup> ADA es un lenguaje de programación orientado a objetos utilizado principalmente para aplicaciones donde se requiera mucha seguridad.

- Codificación: una vez definidas las interfaces del proyecto se tienen que describir en VHDL, preferentemente en un editor especializado, el cual verifique que toda la sintaxis sea la correcta.

- Simulación: una vez que el código es correcto se definen entradas de prueba y se verifica que las salidas correspondan a los valores esperados.

- Síntesis: convierte el modelo descrito en el conjunto de conexiones de circuitos necesarios para la implementación sobre el FPGA y la tarjeta de desarrollo que se utilizará.

- Implementación: mapeo de las conexiones generadas en la síntesis de acuerdo con los recursos disponibles de la tarjeta de desarrollo, generando un archivo tipo bit<sup>9</sup>.

- Programación de la tarjeta de desarrollo: si se cumplieron exitosamente todas las etapas anteriores, incluyendo la generación del archivo bit, se debe descargar dicho archivo hacia el FPGA para observar el comportamiento real del diseño.

Figura 1. 1 Proceso de diseño en VHDL.

#### 1.1.2 ELEMENTOS BÁSICOS DE VHDL

Cualquier diseño que se realice en VHDL debe ser descrito por sus señales y como interactúan entre ellas, indicando cuántos puertos de entrada y salida se asumen, a esto se le conoce como la entidad, la cual se muestra en la figura 1.2. Una entidad puede definirse como

<sup>&</sup>lt;sup>9</sup> Archivo generado por el editor especializado para programar el dispositivo FPGA el cual contiene todo el mapeo de las interconexiones de ruteo que determinará el comportamiento del circuito dentro del FPGA.

una representación de un sistema electrónico en la cual se describen únicamente los elementos externos que deben tener un nombre, si son entrada o salida y el tipo de datos que van a transmitir o recibir.

Figura 1. 2 Entidad en VHDL.

Una vez descrita la entidad, se debe especificar cómo deberán funcionar los puertos de salida con respecto a las entradas, a este elemento se le conoce como arquitectura, donde, por medio de funciones propias de VHDL, se va a describir el comportamiento de la entidad, por lo que una arquitectura siempre irá asociada a una entidad. Las principales características de una arquitectura son las siguientes:

- Describir el comportamiento del circuito.

- Declarar las señales internas, los procedimientos variables y constantes necesarios en el diseño.

- Describir de forma estructural o por comportamiento.

#### 1.2 ANTECEDENTES

Numerosos circuitos integrados (CI) utilizan circuitos lógicos de uso común, por ejemplo, compuertas lógicas, codificadores, convertidores o sumadores, estos componentes son de los años 70, por esta razón, actualmente son utilizados únicamente con fines didácticos. Dependiendo de la cantidad de transistores, compuertas o funciones de las que se compone el CI, es decir, de su escala de integración; se clasifican en pequeña (SSI por sus siglas en inglés Small Scale Integration) las cuales se consideran las más pequeñas con solo algunos transistores. Mediana (MSI por sus siglas en inglés Medium Scale Integration) estos integrados fueron utilizados en 1970 por los primeros ordenadores. Gran (LSI por sus siglas en inglés Large Scale Integration) este tipo de escala es utilizado en los primeros microprocesadores. Muy grande

(VLSI por sus siglas en inglés Very Large Scale Integration) utilizados para procesadores más potentes en marcas reconocidas. Ultra (ULSI por sus siglas en inglés Ultra Large Scale Integration) utilizado en microprocesadores complejos a principios de los 80s para el desarrollo de la serie 8086 de Intel®.

Un gran problema fue que, si el diseñador requería diseños de circuitos lógicos más complejos, se necesitaban más circuitos integrados, dando como resultado alterar el diseño original y modificarlo en un circuito más complejo y en un PCB<sup>10</sup> más grande, dejando de optimizar espacio. Por esta razón, los nuevos circuitos tienen una mayor escala de integración, es decir, contienen más componentes por circuito integrado. Además, el hecho de modificar el diseño en el software implica alteraciones en el hardware, cableado, distribuciones de los circuitos, etc. Por estos hechos, la lógica programable atenúa estos cambios porque solamente se realizan modificaciones dentro del código.

#### 1.2.1 MEMORIAS PROGRAMABLES DE SOLO LECTURA (PROM).

Los circuitos programables, también conocidos como dispositivos programables, pueden ser considerados como un circuito de propósito general, donde el usuario puede modificar la estructura interna. Las características antes mencionadas describen perfectamente a un dispositivo de memoria PROM (*Programmable Read-Only Memory*).

La memoria PROM utilizan bits de direccionamiento donde cada una de estas direcciones tiene un tamaño fijo de memoria que depende del dispositivo utilizado. Las memorias PROM sólo pueden ser programadas una vez.

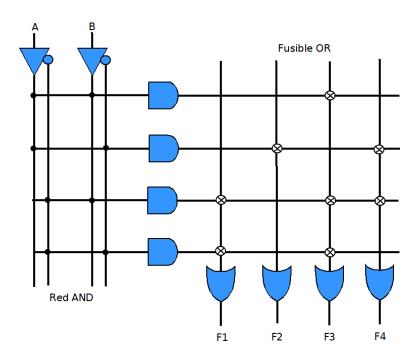

En la figura 1.3 se puede observar la estructura interna de una PROM como dispositivo lógico programable. La PROM se compone de una matriz AND fija y una OR programable.

6

<sup>&</sup>lt;sup>10</sup> Un PCB por sus siglas en inglés *Printed Circuit Board* es la placa donde se conectan los dispositivos electrónicos de forma permanente.

Figura 1. 3 Configuración de una PROM.

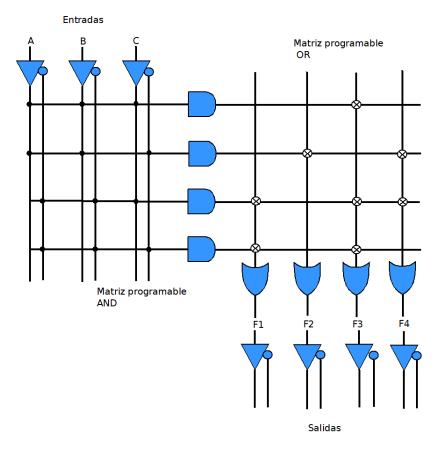

#### 1.2.2 DISPOSITIVOS LÓGICOS PROGRAMABLES (PLD)

El **PLD** (Programmable Logic Device) es un dispositivo que consiste en una matriz de compuertas AND conectada con otra matriz de compuertas OR. Este diseño permite al circuito ser modelado como una suma de productos. Una de las ventajas es que este circuito puede ser muy eficiente, solamente si se implementa en diseños que no superan a unos cientos de compuertas. Un problema que se puede ver es que la arquitectura es muy rígida y está muy limitada a un número de entradas y salidas.

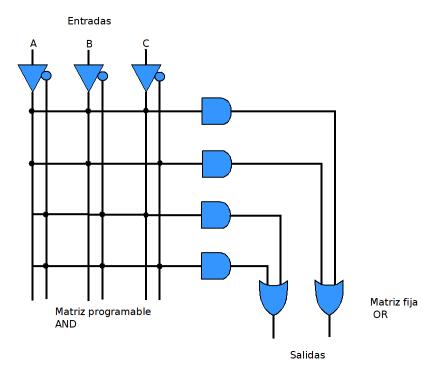

#### 1.2.3 ARREGLOS LÓGICOS PROGRAMABLES (PLA)

Los *PLA* (por sus siglas en inglés Programmable Logic Array) consisten en dos matrices que son programables, una AND y otra OR. Tienen la característica de que en las entradas y las salidas hay compuertas NOT para obtener mayor versatilidad en la salida (ver figura 1.4). Los PLA pueden ser conectadas externamente a Flip-Flop's para poder diseñar circuitos secuenciales.

Figura 1. 4 Configuración de un PLA.

#### 1.2.4 LÓGICA DE ARREGLOS PROGRAMABLES (PAL)

Los PAL (por sus siglas en inglés Programmable Array Logic) son considerados una variante de las PLA que consisten en dos planos:

- 1. Un plano AND programable.

- 2. Un plano OR fijo.

En la figura 1.5, se incluyen inversores en la entrada con las que se pueden implementar funciones con variables y su complemento (como en el dispositivo lógico anterior PLA). En las salidas se añade un arreglo fijo OR, donde se limita mucha de la funcionalidad y flexibilidad que ofrecía el circuito anterior (PLA).

Figura 1. 5 Configuración de un PAL.

#### 1.2.5 ARREGLOS LÓGICOS GENÉRICOS (GAL)

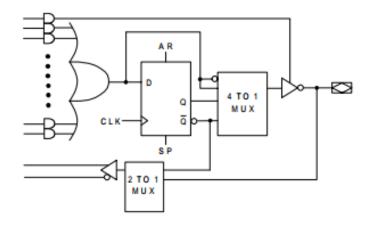

La *GAL*, por sus siglas en inglés *Generic Array Logic*, es básicamente un PLA (como se muestra en la figura anterior 1.4) pero contiene una Macrocelda que es un conjunto de Flip-Flop's, todo esto para cambiar el estado lógico de la salida además de realimentar las salidas de los Flip-Flop's (se puede observar en la figura 1.6). Utiliza una matriz de memoria EEPROM, dando la oportunidad a la GAL de ser programada varias veces.

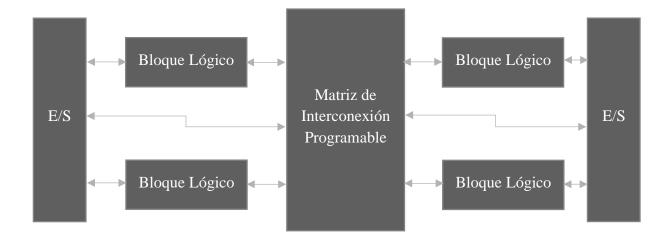

#### 1.2.5 DISPOSITIVOS LÓGICOS PROGRAMABLES COMPLEJOS (CPLD)

Un *CPLD* (por sus siglas en inglés *Complex Programmable Logic Device*) es un PLD a un mayor nivel de integración y tiene las siguientes características.

- Permiten implementar sistemas más eficientes.

- Utilizan menos espacio.

- Mejoran la confiabilidad en el circuito.

- Reducen costos.

Figura 1. 6 Macrocelda de una GAL.[3]

El CPLD se forma con múltiples bloques lógicos, donde cada uno es similar a un PLD. Los bloques lógicos se comunican entre sí utilizando una matriz programable de interconexiones lo cual hace más eficiente el uso del silicio y tiene un mejor desempeño. La arquitectura de un CPLD se compone de tres bloques principales:

- 1) Bloque Lógico (Logic Block): un Bloque Lógico es muy parecido a un PLD donde cada uno de ellos poseen generalmente una matriz de compuertas AND, una matriz de compuertas OR y una configuración para la distribución de los productos en las diferentes macroceldas del bloque. La cantidad de bloques lógicos que puede tener un CPLD dependerá de la familia y del fabricante del dispositivo.

- 2) Matriz de Interconexión Programable (Programmable Interconnect Matrix): permite unir los pines de I/O con las entradas del bloque lógico o sus salidas a las entradas del bloque lógico.

- 3) Bloque de Entrada/Salida (Input Output Block): La función del Bloque de I/O es permitir el paso de la señal hacia adentro o al exterior del dispositivo.

Se pueden observar los bloques correspondientes del diagrama del circuito CPLD en la figura 1.7.

Figura 1. 7 Estructura básica de un CPLD.

#### 1.2.6 ARREGLO DE COMPUERTAS PROGRAMABLES EN CAMPO (FPGA)

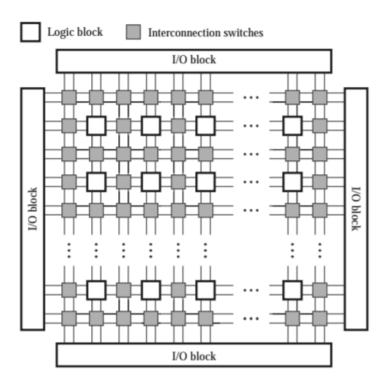

El Arreglo de Compuertas Programables en Campo o Field Programmable Gate Array, son circuitos de alta densidad programables por el usuario con un tiempo de respuesta mucho más rápido en comparación de otros sistemas. Los FPGA presentan líneas de interconexión, las cuales son agrupadas en canales verticales y horizontales, donde disponen de células de memoria de configuración que son distribuidas a lo largo de todo el chip[10] (como se puede observar en la figura 1.8), éstas almacenan toda la información necesaria para programar los dispositivos mencionados anteriormente.

#### 1.3 PROCESAMIENTO DE IMÁGENES EN FPGA

El procesamiento digital de imágenes ha tomado mucha relevancia en diversas áreas de investigación, por ejemplo, aplicaciones industriales, ciencias médicas, satélites o videojuegos, estas aplicaciones usualmente requieren el suavizado de la imagen, la eliminación del ruido o realzar y detectar bordes, por mencionar algunos. Generalmente los algoritmos empleados requieren de mucha velocidad de procesamiento, flexibilidad y tiempo de desarrollo para ser

completados exitosamente. Existen herramientas de software que pueden solventar estas necesidades haciendo uso de una computadora, esto hace a la implementación del algoritmo mucho más sencilla, pero se pierde velocidad de ejecución.[2]

Figura 1. 8 Estructura de una FPGA<sup>11</sup>.

La solución que se le ha dado a este tipo de problemas es el uso de arquitecturas de procesadores en paralelo, sin embargo, están limitadas a pocas aplicaciones por sus altos costos de diseño ya que hay sistemas que pueden alcanzar un valor de más de \$4000 dólares.[11] Los FPGA logran hacer frente a las exigencias de estos procesos ofreciendo grandes ventajas en cuanto a velocidad de procesamiento y costos del proyecto, ya que son capaces de realizar operaciones completas o reprocesar los datos antes de utilizarlos sin perder velocidad en el proceso[12].

12

<sup>&</sup>lt;sup>11</sup> Imagen tomada de: S. D. Brown y Z. G. Vranesic, Fundamentals of digital logic with VHDL design, 3<sup>rd</sup> ed. New York, NY. McGraw-Hill, 2009.

#### 1.3.1 VIDEOJUEGOS EN UN DISPOSITIVO FPGA

Los videojuegos han formado parte de la vida diaria de la sociedad desde hace mucho tiempo, se puede considerar al OXO<sup>12</sup> como el primer videojuego de la historia en 1952. En los años ochenta la industria de los videojuegos tuvo un crecimiento exponencial debido a las máquinas recreativas y a las primeras consolas domésticas. [13]

En las consolas antiguas, los recursos de hardware no eran muchos, se requería de un gran procesamiento y mucha memoria, esto hizo que los desarrolladores emplearan métodos muy ingeniosos para la creación de sus juegos. Los cartuchos de esa época guardaban los gráficos en una memoria separada del código del juego, por otra parte, la tarjeta madre de la consola tenía el CPU donde se ejecutaba toda la lógica del juego y la parte gráfica era procesada por la unidad de procesamiento de imágenes conocida como PPU (por sus siglas en inglés *Picture Processing Unit*). Este dispositivo tenía acceso directo a la memoria donde estaban almacenadas las imágenes y las desplegaba en la pantalla generando cada cuadro a la vez.

Una sola imagen en pantalla requería de 61440 pixeles[14], que para un cartucho de esa época era imposible de almacenar en ese espacio. Para solventar eso, se creó el concepto de "tiles" el cual consiste en almacenar pequeños cuadros con fragmentos de una imagen y reutilizarlos una y otra vez a lo largo del juego y guardarlos en una sola imagen conocida como la tabla de patrones similar a la mostrada en la figura 1.9.

Una plataforma de videojuegos, en su forma más simple, solo requiere una interfaz que interactúe con el jugador, otra que lo haga con las salidas y un mecanismo que permita implementar la lógica del juego[15]. Como se puede ver en la figura 1.10, la estructura simple de un videojuego consta de esas partes esenciales. Pueden agregarse muchas más, pero eso dependerá de los requerimientos y alcances que permita el juego.

13

<sup>&</sup>lt;sup>12</sup> Videojuego desarrollado por Alexander Douglas, era una versión computarizada del juego del gato que permitía enfrentar a un jugador contra la máquina.

Figura 1. 9 Tabla de patrones.

Figura 1.10 Diagrama de una estructura simple de un videojuego. [16]

#### 1.4 DISEÑO CON FPGA

De forma física, el proceso de un circuito digital utilizando una matriz lógica programable puede descomponerse en dos etapas básicas:

- 1. Dividir el circuito en bloques básicos, asignándolos a los bloques configurables del dispositivo.

- 2. Conectar los bloques de lógica mediante los conmutadores necesarios.

A continuación, se mencionan los bloques principales de los que se componen los FPGA:

- 1. *Bloques lógicos*, cuya estructura y contenido se denomina arquitectura. Suelen incluir biestables para facilitar la implementación de circuitos secuenciales. Otros módulos de importancia son los bloques de Entrada/Salida.

- 2. **Recursos de interconexión**, cuya estructura y contenido se denomina arquitectura de ruteo.

- 3. *Bloques de memoria*, son los que se carga, durante el RESET para configurar bloques y conectarlos.

Existen muchas ventajas que puede proporcionar el uso de los FPGA como:

#### • Hardware a la medida.

Cuando se hace referencia al termino de "hardware a la medida" es cuando el diseñador no tiene que buscar los productos en el mercado que mejor se adapten a sus diseños, sino que se los diseña a la medida de sus necesidades, o reutiliza o modifica los diseños ya existentes. En un sistema que incorpore un FPGA, es el diseñador que implementa solamente los controladores necesarios para nuevas posibilidades de diseño, por ejemplo, el crear una CPU específica para una aplicación determinada junto con sus propios controladores de periféricos.

#### Reducción del ciclo de diseño.

El modelo de diseño de hardware basado en HDL contiene muchas de las ventajas del diseño software. El circuito es ahora un archivo de texto, que se puede editar, simular, modificar y finalmente sintetizar. Se pueden crear repositorios de hardware, con colecciones de diseños

ya probados: controladores de puerto VGA, UART, temporizadores, CPU, etc., donde el diseñador puede crear prototipos de manera muy rápida, probarlos, medirlos y modificarlos.

#### Flexibilidad.

Con el mismo hardware, se puede conseguir un sistema con comportamientos diferentes. En la misma tarjeta, se puede tener sintetizada una CPU además de poder probar un puerto con un protocolo UART.

#### • Posibilidad de transferir algoritmos al hardware.

En los diseños mixtos de microcontrolador con FPGA, se puede decidir el implementar una solución de hardware frente a una puramente de software, consiguiéndose una mayor velocidad. Por ejemplo, la implementación de algoritmos de cifrado. En un microcontrolador de 8 bits esto sería un proceso lento, pero se vuelve viable si se añade un hardware que haga el cifrado.

#### • Diseños de hardware libre.

Posibilidad de realizar diseños que se compartan dentro de una comunidad y que cualquier diseñador pueda utilizarlos, modificarlos y distribuir las modificaciones. Esto es especialmente útil en el campo de la docencia y la investigación, donde se potencia si el hardware en el que se prueban los diseños también es libre.

#### • Paralelismo

Una de las ventajas más notorias de usar un FPGA es la programación en paralelo. Ésta ofrece el beneficio de realizar 2 o más procesos secuenciales de forma concurrente, dando la oportunidad de implementar diversos sistemas independientes funcionando en linea o módulos que dependen de la señal procesada de otro sector.

Las aplicaciones de los FPGA pueden brindar más de una solución y actúan en muchos campos, esto se debe al amplio manejo de datos y señales que brindan estos dispositivos. Dentro de las áreas de aplicación se encuentran[10]:

Aerodefensa espacial: son utilizados en radares y sistemas de guía, además pueden ser implementados en diferentes áreas de estudio como: industrial o comercial a través de las tecnologías de la FPGA.

*Prototipos para ASIC*: este tipo de aplicación es una de las más utilizadas, ya que en una FPGA se pueden crear rápidamente muchos sistemas que cumplan las funciones propias de un ASIC con la ventaja de poder ser probados de forma inmediata.

*Audio y video*: en el manejo de una gran gama de señales que permiten que los FPGA brinden varias soluciones de costo reducido y con gran confiabilidad.

*Automotriz*: los sistemas de navegación y asistencia al conductor, monitoreo del correcto funcionamiento de un vehículo, sistemas de información y entretenimiento pueden ser creados con estos dispositivos.

*Informática de alto rendimiento*: con la integración de microprocesadores dentro del chip FPGA se puede lograr una aceleración de hardware, lo que conduce a un alto rendimiento en el procesamiento de datos y señales.

*Centro de datos*: diseñado para grandes anchos de banda, donde los FPGA se pueden implementar como servidores de baja latencia, sistemas de redes informáticas y aplicaciones de control de datos.

*Seguridad*: ya se habló sobre el procesamiento de señales de audio y video, así como la posibilidad de tener un microprocesador dedicado, si a esto se agregan sistemas biométricos como sensores de huellas digitales o de voz y de control de datos, se tienen los elementos fundamentales para la implementación de sistemas de seguridad y vigilancia.

**Área médica**: la gran capacidad de procesamiento, visualización y muestreo de datos permite que se puedan crear aplicaciones para equipos de monitoreo, diagnóstico y aplicación de terapias.

*Aplicaciones inteligentes*: en la búsqueda de la comodidad, los sistemas inteligentes han tomado un gran auge, un FPGA puede adaptarse a las exigencias que demandan estos sistemas.

*Equipos medidores y de pruebas*: se pueden diseñar toda una gran gama de equipos, como ejemplo se tienen: osciloscopios, generadores de señal y analizadores, analizadores lógicos, multímetros, equipos de medición para industria automotriz, probadores analógicos de radiofrecuencia, probadores de señales mixtas, probadores de memoria, etc.[10]

Como se puede deducir, el campo de aplicación de estos dispositivos programables es muy amplio. El trabajo se centra en desarrollar un sistema de procesamiento de imágenes complementado con una aplicación para mostrar el proceso de diseño e implementación. Para lo cual, en los siguientes capítulos se abordan las bases de la aplicación y los detalles de dicho proceso.

# CAPÍTULO 2 CONCEPTOS PARA EL DISEÑO DEL SISTEMA DE PROCESAMIENTO DE IMÁGENES

En este capítulo se presentará la propuesta de solución para el sistema de procesamiento de imágenes, se definirán las interfaces a utilizar y los protocolos necesarios para establecer una comunicación eficiente entre los dispositivos de entrada y salida y la tarjeta de desarrollo. Posteriormente, se explicará los conceptos teóricos relacionados a cada una de las interfaces, como son el estándar VGA<sup>13</sup>, el protocolo I2S<sup>14</sup> y el proceso para generar y guardar datos en la memoria de la FPGA y poder acceder a ellos cuando sea necesario.

#### 2.1 DIAGRAMA GENERAL DE LA SOLUCIÓN

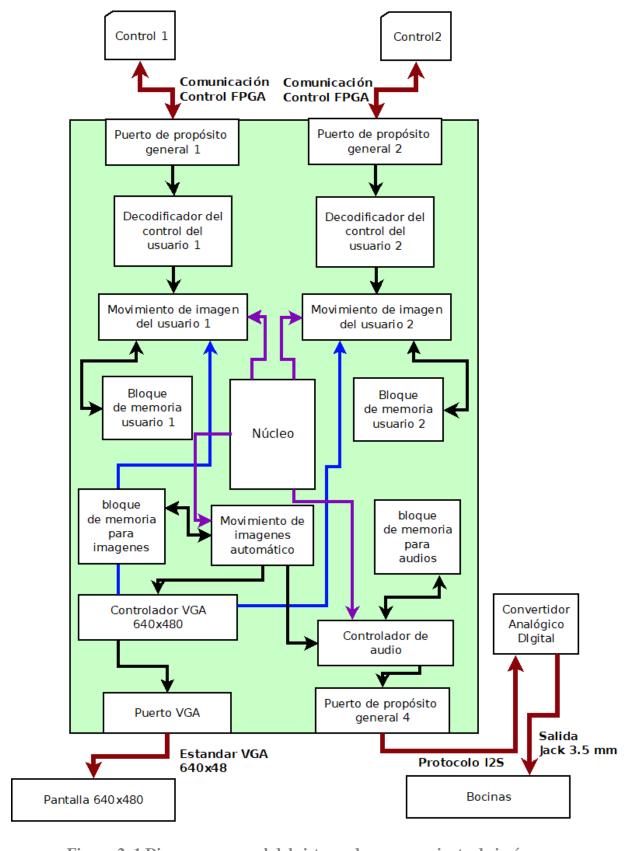

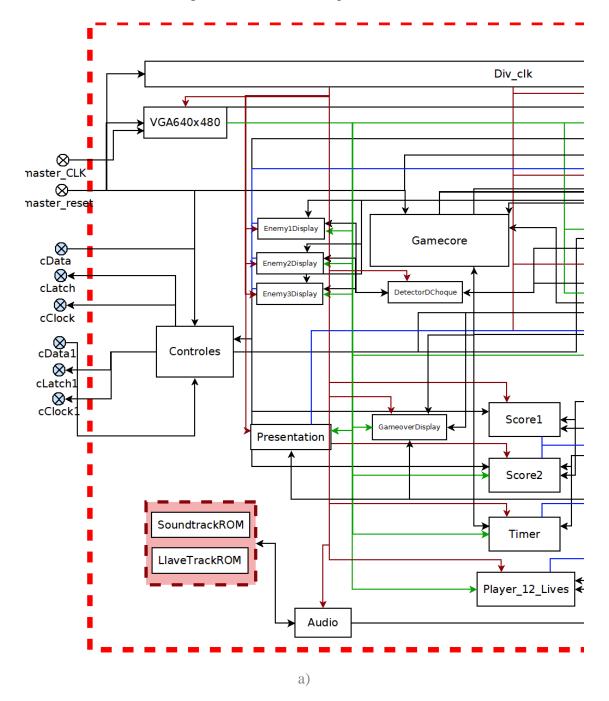

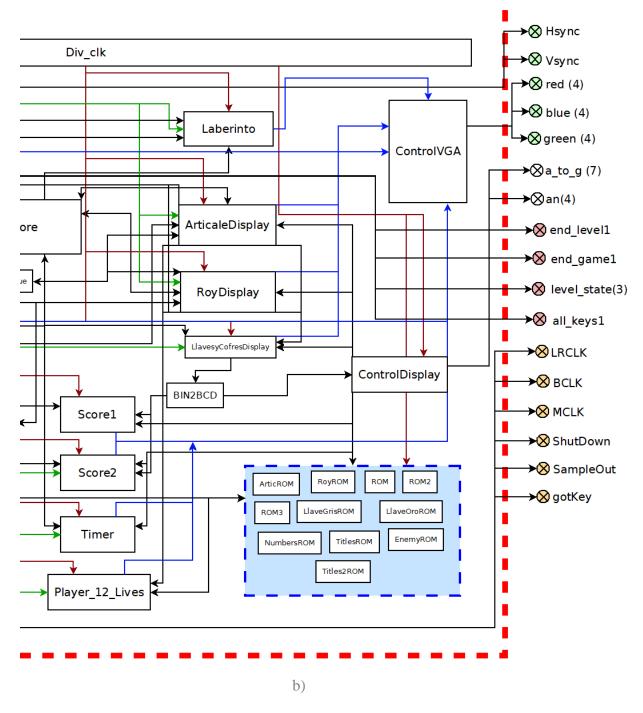

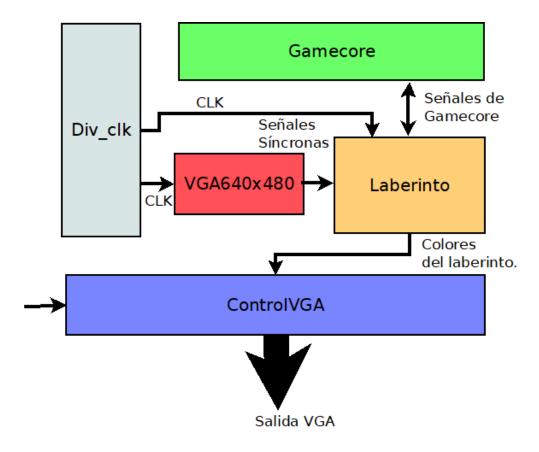

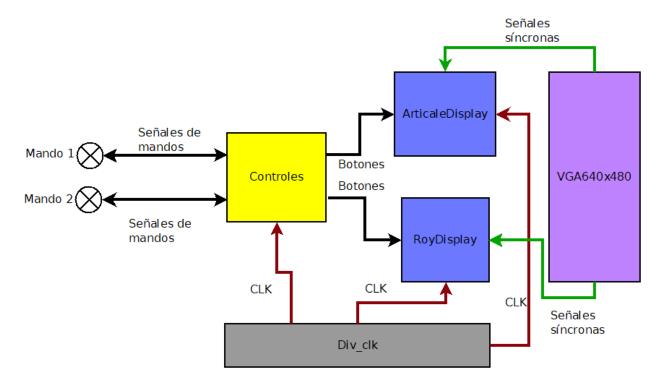

En la figura 2.1, se muestran las interfaces involucradas en la solución propuesta para el sistema de procesamiento de imágenes, como se observa, el sistema es controlado totalmente por el FPGA de la tarjeta de desarrollo. Primeramente, se puede ver en la parte superior de la figura 2.1, que el diseño cuenta con un par de controles para permitir a dos usuarios el manipular las imágenes por medio de la transmisión de datos. Una vez que se obtienen dichos datos de los controles serán enviados a un módulo que determinará el movimiento de la imagen, el cual va a estar conectado a un bloque de memoria para obtener la información de la imagen y enviarla al controlador VGA. De igual forma, existe un bloque que va a interactuar algunas imágenes de forma independiente al usuario en la pantalla accediendo a su propio bloque de memoria y, de la misma forma, será enviado al módulo VGA para ser desplegado en pantalla con las otras imágenes.

Como más de un bloque será mostrado en pantalla, el sistema cuenta con un controlador VGA el cual seleccionará que imagen será desplegada en un determinado instante de tiempo, dependiendo del píxel que se esté mostrando en ese momento.

<sup>&</sup>lt;sup>13</sup> VGA (como en sus siglas en inglés Video Graphics Array) la matriz de gráficos de video es un estándar que se implementó para la transmisión de datos de imágenes.

<sup>&</sup>lt;sup>14</sup> I2S (como en sus siglas en inglés Integrate Interchip Sound) es una interfaz de tipo serial para interconectar dispositivos digitales de audio entre sí.

Figura 2. 1 Diagrama general del sistema de procesamiento de imágenes.

El controlador de audio va a recibir información en tiempo real para poder seleccionar que audio va a ser enviado por medio del protocolo I2S al convertidor digital-analógico, para ser reproducido por medio de un par de bocinas a través de un conector tipo jack de 3.5mm. Los detalles de todos los protocolos y estándares utilizados se van a explicar más a detalle a lo largo de este capítulo.

## 2.2 IMÁGENES DIGITALES Y AUDIO.

## 2.2.1 LAS IMÁGENES DIGITALES.

Las imágenes pueden manifestar la apariencia que pudiera tener un objeto real o imaginario, dándole al espectador la capacidad de observar y entender lo que el expositor trata de mostrar. Con el avance de la tecnología, se han obtenido mejores formas de generar y mostrar figuras digitales.

Una imagen digital es definida como una representación bidimensional de una ilustración a partir de un conjunto de valores del mismo tipo llamado matriz, el cual puede ser de tipo binario (1 pixel<sup>15</sup> = 1 bit, donde 0 es negro y 1 es blanco), escala de grises (1 pixel = 1 byte, donde 0 es negro y 255 blanco, es decir, permite 256 niveles de gris) y a color (1 pixel > 1 byte, debido a que se requieren 3 valores de colores: rojo, verde y azul).

Al ser una imagen considerada como una figura matricial, se puede observar como un mapa de bits. Un factor que influye directamente en la estructura de las imágenes es su resolución, por esta razón, podría cambiar su tamaño y la cantidad de espacio en bits de memoria.

El tamaño de la imagen se representa con medidas bidimensionales (largo \* ancho), donde se proporciona el dato total de pixeles que contiene la imagen (pixeles = largo \* ancho).

21

<sup>&</sup>lt;sup>15</sup> El píxel es la unidad más pequeña de una imagen digital y está representado por un número para formar una imagen completa

Ejemplo:

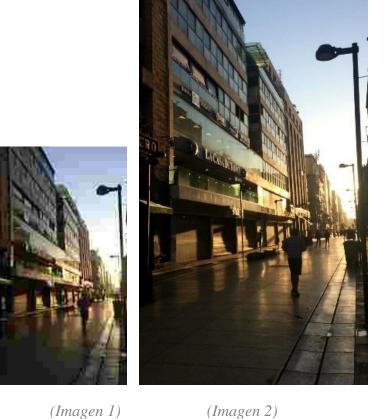

La cantidad de pixeles contenidos en las imágenes 1 y 2 de las figuras 2.2 son las siguientes:

$$Pixeles_{imagen 1} = 150 * 267 = 40,050 pixeles$$

$$Pixeles_{imagen 2} = 720 * 1280 = 921,600 pixeles$$

Figura 2. 2 Ejemplo de baja (Imagen 1) y alta resolución (Imagen 2) en una misma imagen.

El espacio en memoria de la imagen 2 (921,600 pixeles) será mucho mayor al espacio designado para la imagen 1 (40,050 pixeles).

Una imagen digital puede ser guardada en celdas de memoria, siempre y cuando los recursos lo permitan. Para obtener el dato deseado, es necesario conocer una dirección donde fue asignada dentro de la memoria.

#### 2.2.2 EL SONIDO

El sonido tiene diversas definiciones dependiendo el área que se estudie, en su sentido elemental se puede describir como la sensación producida en el oído por medio de vibraciones transmitidas por un medio elástico, por ejemplo, el aíre o el agua.

Como cualquier fenómeno físico, las ondas de sonido tienen características propias que son necesarias para poder entenderlas y utilizarlas. Algunas de estas características son:

**Frecuencia:** el número de ciclos completos que puede realizar una onda durante un segundo y se mide en Hertz (Hz). Para el ser humano el rango audible se encuentra entre los 20Hz a los 20KHz.

**Amplitud:** es la altura máxima de la onda y corresponde a la intensidad del sonido, comúnmente es expresada en la cantidad de energía transportada.

**Longitud de onda:** distancia recorrida por una onda en un instante de tiempo.

El sonido puede almacenarse de forma analógica o digital. La primera consiste en convertir, por medio de un transductor, los cambios en la presión de aire a cambios de tensión eléctrica, estos cambios pueden almacenarse en cintas magnéticas como un casete o un disco de vinilo, sin embargo, estos sistemas tienden a desgastarse muy pronto y con el tiempo pierden su calidad.

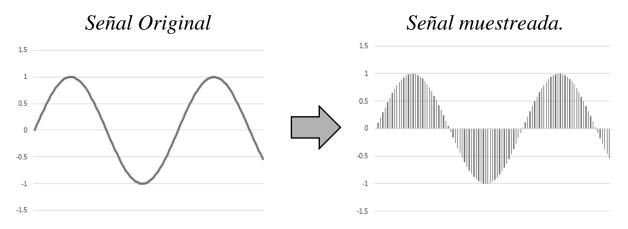

El segundo tipo de almacenamiento es el digital. El audio digital divide la señal en pequeños instantes de tiempo denominados muestras y se les asigna un valor binario, este proceso se le llama muestreo del audio. Existen varios tipos de dispositivos que se pueden almacenar audio digital, algunos de ellos son: discos CD-ROM, discos CD-audios, DVD, disquetes, tarjetas de memoria tipo flash, etc.

### 2.2.3 CONVERSIÓN ANALÓGICO-DIGITAL

El proceso de muestreo es posible por medio de los convertidores analógicos-digitales, estos sistemas toman una muestra de la señal analógica y le asignan un valor binario que puede ser almacenado en una memoria. Un instante después, se toma una nueva muestra y se almacena

de nuevo, la frecuencia con la que se realiza este proceso debe ser al menos el doble de la máxima frecuencia de la señal original (Teorema de Nyquist).

Además del muestreo de la señal, el proceso de conversión analógico-digital del audio tiene otros dos pasos para completarlo correctamente los cuales son los siguientes:

Figura 2. 3 Muestreo de una señal de audio.

Cuantización: cuando el proceso de muestreo terminó las muestras tomadas tienen valores continuos (voltajes) por lo tanto deben ser convertidos a valores discretos.

Codificación: ya que se tiene cuantizada la señal, cada muestra debe ser convertida a su valor binario. La resolución del audio dependerá de cuántos bits se utilicen para codificar la señal y después almacenarla.

Figura 2. 4 Flujo de conversión Analógico-Digital.

# 2.3 ESTÁNDARES Y PROTOCOLOS DE COMUNICACIÓN PARA LOS PUERTOS DE ENTRADA Y SALIDA.

## 2.3.1 ESTÁNDAR VGA.

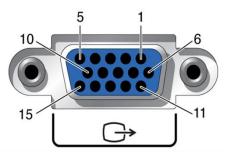

El estándar VGA[17] es un sistema de transmisión analógica de imágenes por medio de los 3 componentes RGB (Red, Green and Blue). Creado por IBM® para transmitir imágenes hacia las pantallas o proyectores a través de un conector de 15 pines.

El puerto VGA (Video Graphics Array) es un conector disponible en la tarjeta de desarrollo como un puerto de entrada y salida de información. El cual tiene sus conexiones físicas con el FPGA como se muestra en la figura 2.5.

Pin 1: Canal Rojo

Pin 6: Retorno Rojo

Pin 11: N/C

Pin 2: Canal Verde

Pin 7: Retorno Verde

Pin 12: SDA

Pin 3: Canal Azul

Pin 8: Retorno Azul

Pin 13: HSync

Pin 4: N/C

Pin 9: +5V CD

Pin 14: VSync

Pin 5: GND Tierra

Pin 10: GND Tierra

Pin 15: SCL

Figura 2. 5 Diagrama de conexiones del puerto VGA con la FPGA.[18]

N/C = No conectado.

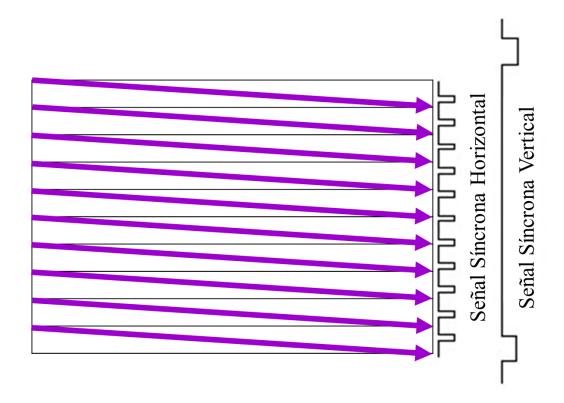

La emisión de energía en el espectro RGB es proporcional al voltaje correspondiente a las señales de colores Rojo, Verde y Azul. Cada punto coloreado en la pantalla es un píxel. La pantalla despliega pixeles comenzando en la esquina superior izquierda, desplazándose a la derecha, línea por línea, hasta la parte inferior de la pantalla. Un pulso de sincronía horizontal se encarga de sincronizar cada nueva línea. Una vez que se alcanza la parte inferior de la

pantalla, un pulso de sincronía vertical provocará un nuevo comienzo desde la parte superior izquierda como se observa en la figura 2.6.

Figura 2. 6 Diagrama de señales síncronas en pantalla.

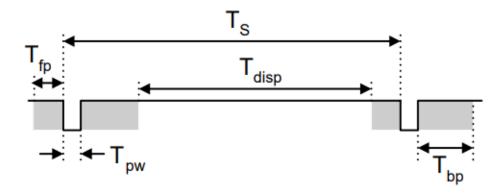

Una vez explicada la importancia de las señales síncronas, la figura 2.7 muestra todas las regiones que contiene una señal síncrona general:

- T<sub>s</sub> es el periodo de la señal *Synchronous* (Síncrona).

- T<sub>disp</sub> es la señal *Dysplay Timing* (Tiempo en pantalla (HV para la señal síncrona horizontal y VV para la señal síncrona vertical.

- T<sub>fp</sub> es la señal *Front Porch* (Porción Frontal no Visible).

- T<sub>bp</sub> es la señal *Back Porch* (Porción Posterior no Visible).

- T<sub>pw</sub> es el *Pulse Width* para identificar las señales síncronas (Ancho del Pulso).

Figura 2. 7 Diagrama general de tiempos para las señales síncronas.

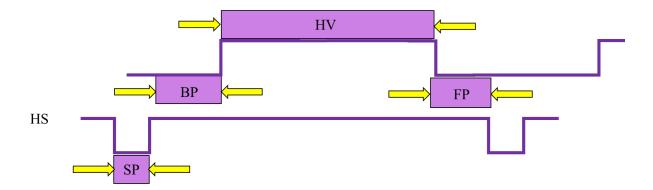

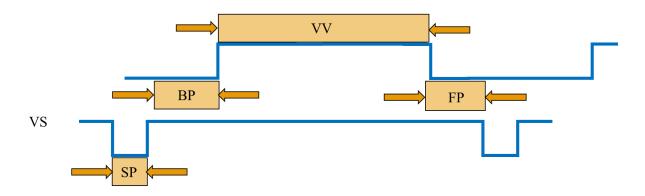

Los pulsos síncronos se basan en los requerimientos técnicos para la resolución 640x480, [17] para su buen funcionamiento se debe tener presente lo siguiente:

- 1. **Señal de sincronía horizontal** (HS): se compone de 4 regiones, como se muestra en la figura 2.8:

- Pulso de sincronía (SP).

- o Back Porch (BP).

- Video horizontal (HV).

- o Front Porch (FP).

- 2. **Señal de sincronía vertical** (VS): se compone de 4 regiones como se muestra en la figura 2.8:

- o Pulso de sincronía (SP).

- Back Porch (BP).

- Video Vertical (VV).

- o Front Porch (FP).

- 3. Las entradas al monitor Rojo, Verde y Azul: son señales de tipo analógicas, Algunas tarjetas de desarrollo ya poseen un convertidor digital analógico como un convertidor digital analógico con resistencias ponderadas.

#### Sincronización horizontal

#### Sincronización vertical

Figura 2. 8 Señales de sincronización horizontal y vertical.

### 2.3.2 PROTOCOLO I2S.

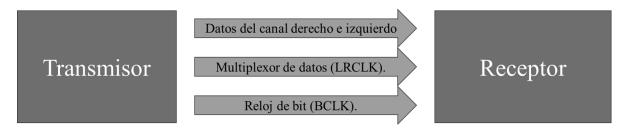

El protocolo I2S (por sus siglas en inglés *Integrated Interchip Sound*) es un estándar de transferencia de audio, ampliamente utilizado para transmitir datos de audio desde un microcontrolador, DSP o FPGA hacia un decodificador de audio para reproducir su contenido. Las especificaciones de este protocolo fueron descritas en el documento "*I2S bus specification*[19]" por Philips Semiconductor en febrero de 1986 y tuvo su última revisión en junio de 1996. Al utilizar este protocolo se minimiza el número de conexiones requeridas para entablar la comunicación entre dos dispositivos utilizando únicamente 3 líneas para la sincronización. El diagrama básico de la conexión de entre dos dispositivos comunicados por I2S se muestra en la figura 2.9.

Figura 2. 9 Diagrama básico de conexión por medio del protocolo I2S.

En el protocolo I2S se puede transmitir audio entre 8 y 32 bits de resolución por canal (esta cantidad puede variar dependiendo el módulo con el que se esté trabajando), esta información va a ser enviada a través de la primera línea de datos que se llama SDATA (Serial Data).

En el caso de esta transmisión, la línea SDATA está multiplexada en el tiempo, por lo que primero se enviarán todos los bits de datos del canal izquierdo comenzando por el bit más significativo (MSB) y hasta que se haya enviado su bit menos significativo (LSB) comenzará a enviarse el MSB del canal derecho y al enviarse el LSB de este canal terminará la transmisión de esa muestra para repetir el proceso con la siguiente.

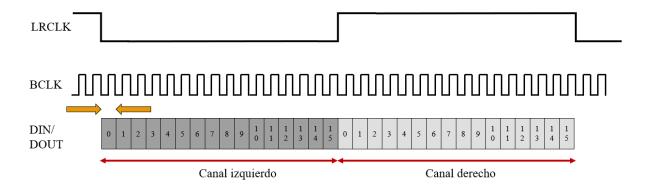

Hay dos formas de sincronizar el canal izquierdo y derecho por medio del protocolo I2S, sus diagramas de tiempos se explican a continuación.

#### • Transmisión I2S.

Para sincronizar los canales de audio se tiene el reloj que va a multiplexar los canales en el tiempo (LRCLK), este reloj va a tener la frecuencia a la cual se haya muestreado la señal de audio que se esté transmitiendo. Si el LRCLK se encuentra en un nivel alto se va a transmitir el canal izquierdo, de lo contrario se tiene que transmitir el canal derecho. Cada bit, de cada canal, se va a transmitir durante un determinado tiempo, que va a ser igual al inverso de la frecuencia de muestreo dividida entre los bits de resolución de la muestra por 2. Por ejemplo, si se tiene una frecuencia de muestreo de 44.1 KHz y cada canal de audio tiene una resolución de 16 bits el tiempo de transmisión de cada uno de los 16 bits enviados será:

Tiempo de bit =

$$\frac{\frac{1}{44.1KHz}}{16(2)}$$

= 708.6168ns

El tiempo de bit servirá para calcular la frecuencia que va a tener el reloj de bit (BCLK), para obtenerla únicamente se calcula el inverso del tiempo obtenido:

$$F(BCLK) = \frac{1}{708.6168nS} = 1.4112MHz.$$

Una vez que se tienen las dos señales que van a sincronizar la transmisión de audio, en el caso del protocolo I2S, se debe asegurar que el LRCLK haga el cambio de un estado a otro cuando el BCLK haga el cambio de nivel alto a nivel bajo (flanco de bajada). El MSB del canal izquierdo va a comenzar a enviarse en el primer flanco de bajada del BCLK después de que el LRCLK haya cambiado de un nivel alto a un nivel bajo y el LSB del canal izquierdo va a transmitirse en el flanco de bajada del BCLK el mismo que indica el flanco de subida de la señal LRCLK. Por lo tanto, el canal derecho va a comenzar su transmisión en el primer ciclo de bajada después de este cambio, es decir, el inicio del envío de información de cada canal tiene un flanco de reloj de retardo[20]. El diagrama de tiempos de este proceso se observa en la figura 2.10.

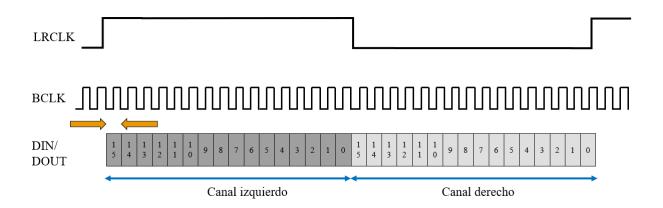

#### • Transmisión I2S justificado a la izquierda.

Para el modo I2S justificado a la izquierda la frecuencia de las señales LRCLK Y BCLK se mantienen, la diferencia entre este modo y el anterior es el tiempo de inicio de transmisión. El bit más significativo del canal izquierdo va a transmitirse al comenzar el flanco de subida del LRCLK y durante el flanco de bajada del BCLK correspondiente por lo que el paquete de datos de ese canal terminará de transmitirse en el flanco de bajada del LRCLK para que el canal derecho se transmita durante el tiempo que dure la señal en nivel bajo[20]. La imagen 2.11 muestra el diagrama de tiempos que describe el comportamiento de este tipo de transmisión.

Los dos modos de transmisión I2S mostrados anteriormente, pueden enviar audio con la misma calidad, queda a elección del usuario decidir cuál de los dos usar, por lo tanto, de aquí en adelante cuando se mencione la transmisión I2S se va a referir al modo justificado a la izquierda.

Figura 2. 10 Diagrama de tiempos de transmisión I2S.

Figura 2. 11 Transmisión I2S justificada a la izquierda.

Como se puede observar, los protocolos y estándares están delimitados a las características que los rigen. El trabajo se centra en desarrollar un sistema de procesamiento de imágenes que cumpla con esas peculiaridades, considerando complementarlo con la aplicación. Para lo cual, en los siguientes capítulos se abordan definiciones, diseños e implementación de la aplicación como tal.

## CAPÍTULO 3 DISEÑO DE UNA APLICACIÓN PARA VIDEOJUEGOS

En el capítulo anterior se describió el diseño general del sistema, conceptos necesarios para el procesamiento de imágenes, algunos estándares y protocolos de comunicación, que servirán como base para la implementación de la aplicación.

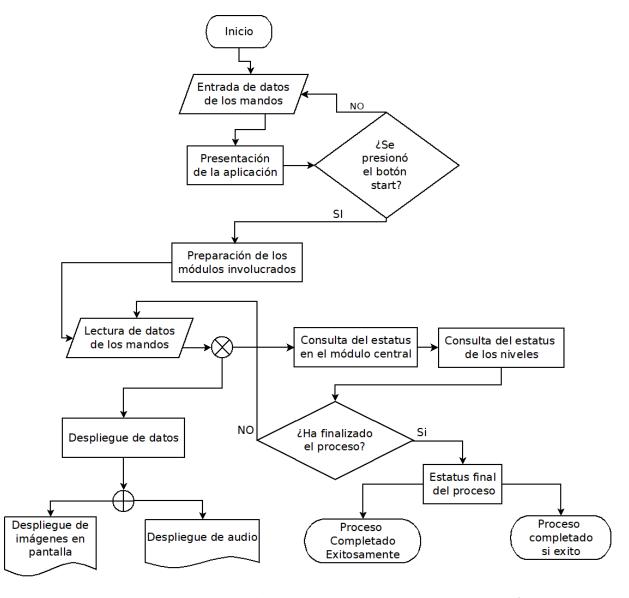

En este capítulo se definirán y explicarán las funcionalidades generales del sistema, la justificación de la implementación de la aplicación, el despliegue de las imágenes y la jerarquía que tiene la imagen sobre la pantalla, definiciones generales sobre algunos módulos y las máquinas de estados correspondientes del flujo de la aplicación.

## 3.1 PLANTEAMIENTO DE LA APLICACIÓN

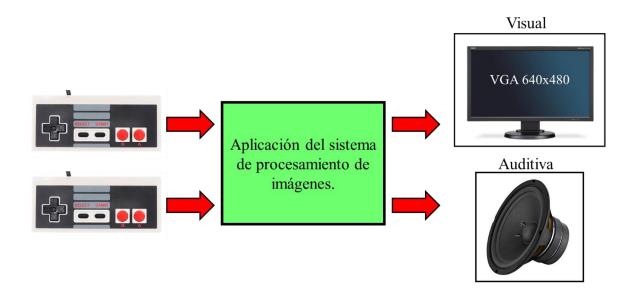

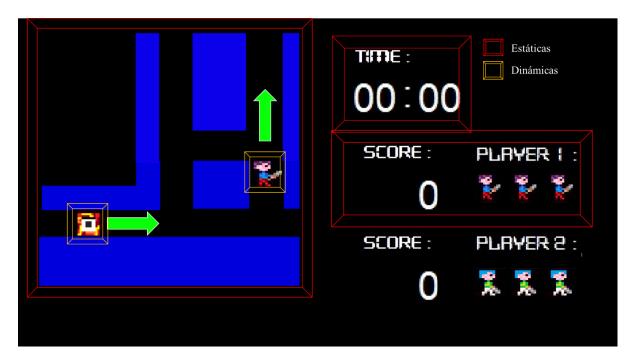

El diseño de la aplicación está implementado como un sistema de videojuegos de los años 80, el cual cuenta con un sistema de mandos de entrada y 2 tipos de salida de datos; la parte visual que está desplegado en una pantalla de 640x480 de resolución y la auditiva que se puede apreciar sobre una bocina conectada por medio de un conector Jack de 3.5 mm como se puede ver en la figura 3.1. Por el momento solamente se hablará de la funcionalidad, en el siguiente capítulo se detallará sobre las características físicas.

Figura 3. 1 Modelo general del sistema completo.

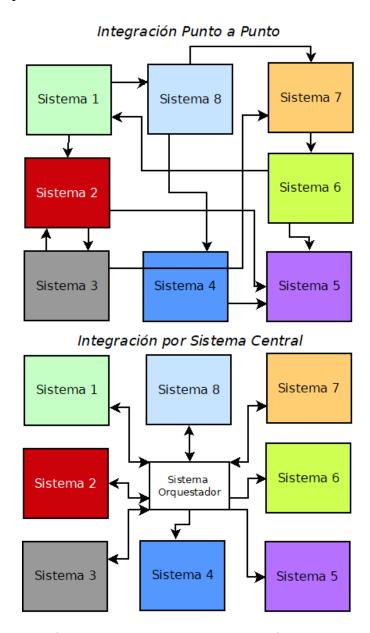

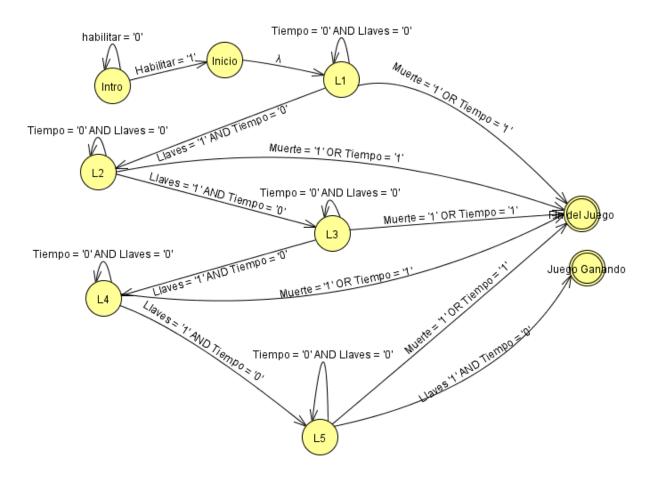

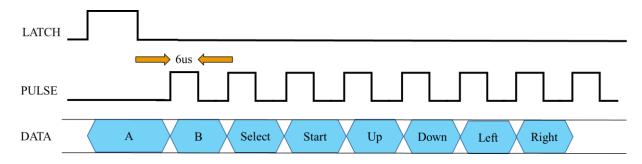

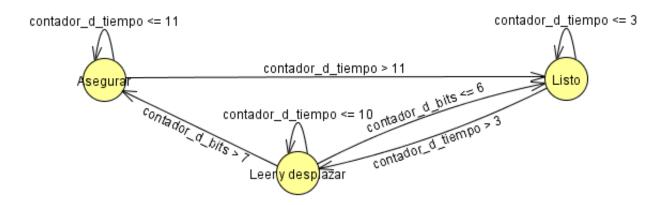

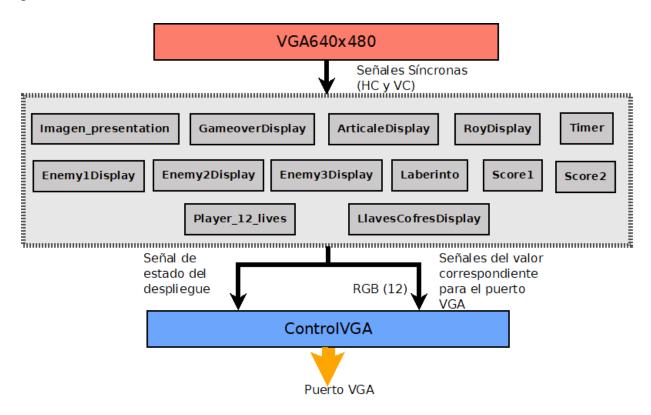

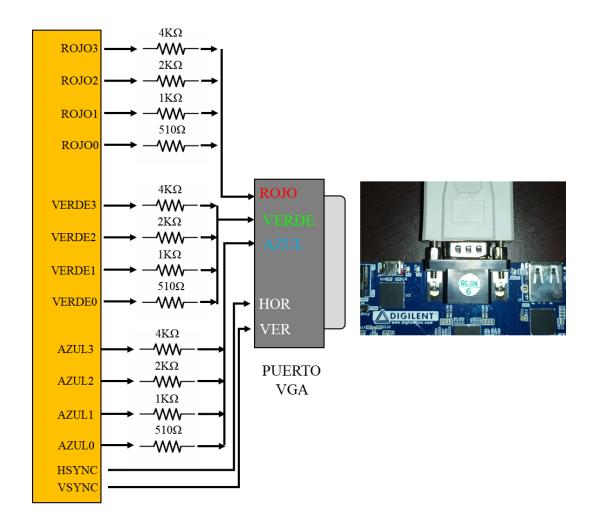

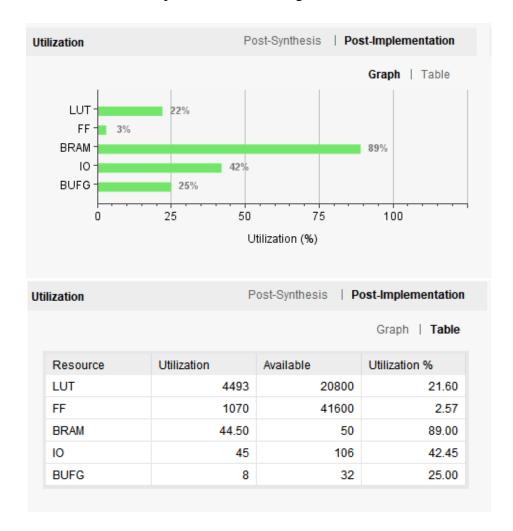

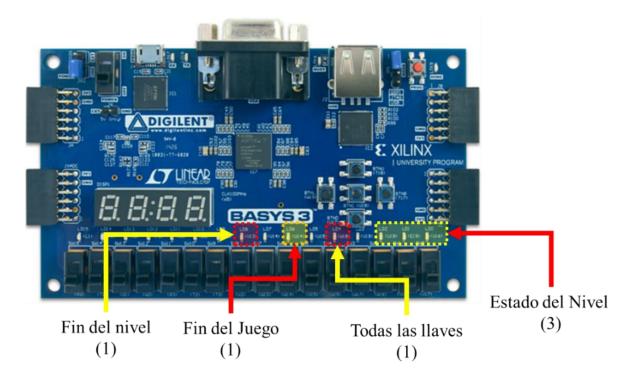

El funcionamiento de la aplicación está basado en un sistema apoyado en el concepto de microservicios <sup>16</sup>, donde se separan todas las funcionalidades que requiere la aplicación en pequeños módulos independientes para la funcionalidad del sistema. Otro concepto en el que se basa el sistema es la orquestación <sup>17</sup> de los módulos, este es utilizado para organizar y dirigir a los módulos en un mismo proceso, proporcionando señales a los estados para que los módulos funcionen sobre el mismo flujo de la aplicación.