# UNIVERSIDAD NACIONAL AUTÓNOMA DE MÉXICO

## FACULTAD DE ESTUDIOS SUPERIORES ACATLÁN

Cálculo del tensor del gradiente gravimétrico a partir de un ensamble de prismas rectangulares en estaciones de trabajo multi-GPU utilizando un paradigma híbrido OPENMP/CUDA.

**TESIS**

QUE PARA OBTENER EL TÍTULO DE:

LIC. EN MATEMÁTICAS APLICADAS Y COMPUTACIÓN

## PRESENTA:

FELIPE ANDRÉS TORRES TORRES

ASESOR: DR. CARLOS COUDER CASTAÑEDA

Santa Cruz Acatlán, Estado de México FECHA: Abril 2019

UNAM – Dirección General de Bibliotecas Tesis Digitales Restricciones de uso

### DERECHOS RESERVADOS © PROHIBIDA SU REPRODUCCIÓN TOTAL O PARCIAL

Todo el material contenido en esta tesis esta protegido por la Ley Federal del Derecho de Autor (LFDA) de los Estados Unidos Mexicanos (México).

El uso de imágenes, fragmentos de videos, y demás material que sea objeto de protección de los derechos de autor, será exclusivamente para fines educativos e informativos y deberá citar la fuente donde la obtuvo mencionando el autor o autores. Cualquier uso distinto como el lucro, reproducción, edición o modificación, será perseguido y sancionado por el respectivo titular de los Derechos de Autor.

#### AGRADECIMIENTOS

Antes que nada gracias al principio de causalidad por permitirme lograr este proyecto de vida.

A mi familia que siempre me a brindado su apoyo incondicional.

A la UNAM, gracias por la gran experiencia que me brindó durante mi etapa estudiantil.

Al Centro de Desarrollo Aeroespacial del Instituto Politécnico Nacional, gracias por el apoyo para poder realizar los experimentos requeridos en este trabajo.

Al Dr. Carlos Couder Castañeda, por sus enseñanzas y su gran apoyo durante este trabajo.

## ÍNDICE GENERAL

| ΙΝ΄ | CRODUCCIÓN 1                                                  |  |  |  |  |

|-----|---------------------------------------------------------------|--|--|--|--|

| 1   | 1 ARQUITECTURA DE LOS CPU Y GPU 7                             |  |  |  |  |

|     | 1.1 Antecedentes 7                                            |  |  |  |  |

|     | 1.2 Arquitectura CPU 8                                        |  |  |  |  |

|     | 1.3 Rendimiento CPU 9                                         |  |  |  |  |

|     | 1.4 Ley de Amdahl 10                                          |  |  |  |  |

|     | 1.5 Organización de un sistema multiprocesador 11             |  |  |  |  |

|     | 1.6 Concurrencia 12                                           |  |  |  |  |

|     | 1.7 Sistemas paralelos 14                                     |  |  |  |  |

|     | 1.8 Plataformas de cómputo paralelas 15                       |  |  |  |  |

|     | 1.9 Evolución de la GPU 16                                    |  |  |  |  |

|     | 1.10 Pipeline gráfico 17                                      |  |  |  |  |

|     | 1.11 Arquitectura GPU 19                                      |  |  |  |  |

|     | 1.12 Diferencias entre el CPU y el GPU 20                     |  |  |  |  |

| 2   | PARADIGMA DE LA PROGRAMACIÓN EN OPENMP Y CUDA 23              |  |  |  |  |

|     | 2.1 La arquitectura CUDA 23                                   |  |  |  |  |

|     | 2.2 Plataforma de cálculo paralelo CUDA 24                    |  |  |  |  |

|     | 2.3 Modelo de programación CUDA 27                            |  |  |  |  |

|     | 2.4 OPENMP 28                                                 |  |  |  |  |

|     | 2.5 Modelo de programación OpenMP 30                          |  |  |  |  |

|     | 2.5.1 Características de OpenMP 31                            |  |  |  |  |

| 3   | MODELACIÓN NUMÉRICA DEL PROBLEMA DIRECTO DE LA GRA-           |  |  |  |  |

|     | DIOMETRÍA GRAVIMÉTRICA 35                                     |  |  |  |  |

|     | 3.1 Introducción 35                                           |  |  |  |  |

|     | 3.2 Gravimetría 35                                            |  |  |  |  |

|     | 3.3 Cálculo del tensor y gradiente del tensor gravimétrico 36 |  |  |  |  |

| 4   | DISEÑO E IMPLEMENTACIÓN DEL ALGORITMO EN OPENMP Y CU-         |  |  |  |  |

|     | DA 43                                                         |  |  |  |  |

|     | 4.1 Trabajos Relacionados 43                                  |  |  |  |  |

|     | 4.2 Diseño 43                                                 |  |  |  |  |

| 5   | RESULTADOS EXPERIMENTALES 53                                  |  |  |  |  |

|     | 5.1 Configuración del experimento 53                          |  |  |  |  |

|     | 5.2 Experimentos sobre un GPU 55                              |  |  |  |  |

|     | 5.3 Rendimiento utilizando Múltiples GPUs 60                  |  |  |  |  |

|     | 5.4 Comparación contra un cluster de computadoras 62          |  |  |  |  |

|     | 5.5 Validación del código numérico 64                         |  |  |  |  |

Conclusiones 67

A GLOSARIO Y ACRÓNIMOS 71

BIBLIOGRAFÍA 73

## ÍNDICE DE FIGURAS

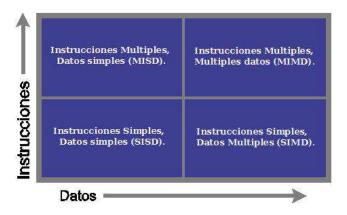

| Figura 1.1  | Taxonomía de Flynn 15                                                                                                                                              |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

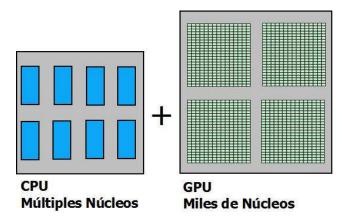

| Figura 1.2  | Diferencias entre el número de núcleos del CPU y el GPU. 20                                                                                                        |

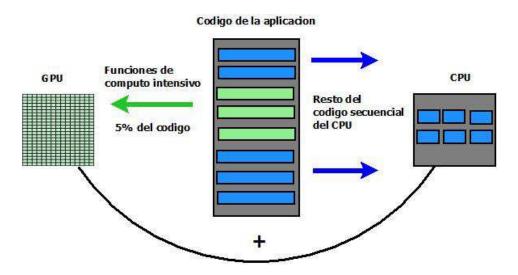

| Figura 1.3  | Flujo de un código de aplicación ejecutado en paralelo 21                                                                                                          |

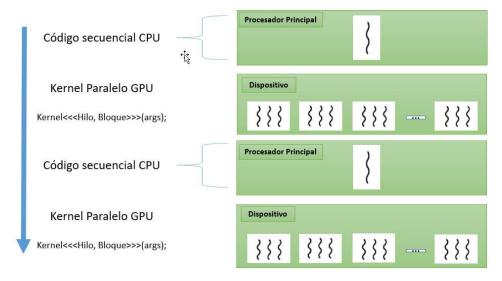

| Figura 2.4  | Ejecución de un programa CUDA 26                                                                                                                                   |

| Figura 2.5  | Modelo fork-join de memoria compartida. 31                                                                                                                         |

| Figura 3.6  | Cartografía de los gradientes gravitatorios.  36                                                                                                                   |

| Figura 3.7  | Componentes del tensor gravimetrico.  42                                                                                                                           |

| Figura 4.8  | Metodología de Foster utilizada para la construcción del algoritmo. 44                                                                                             |

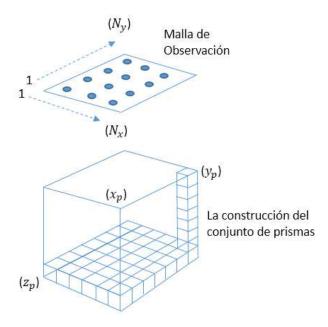

| Figura 4.9  | Construcción de un prisma de densidades constantes con res-                                                                                                        |

| 0           | pecto a una malla de observación. 45                                                                                                                               |

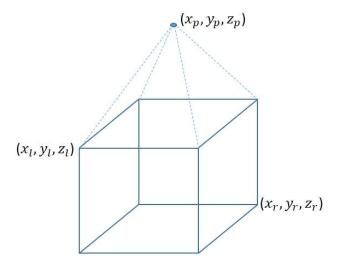

| Figura 4.10 | Cálculo de una anomalía producida por un prisma con res-                                                                                                           |

| D. 4.11     | pecto a un punto de observación. 46                                                                                                                                |

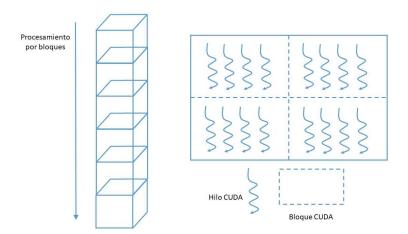

| Figura 4.11 | Partición por puntos de observación. 47                                                                                                                            |

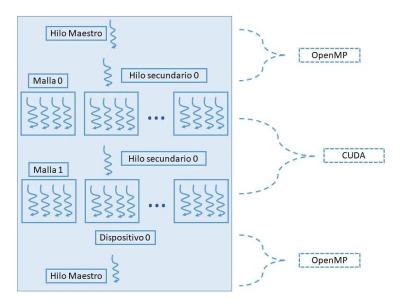

| Figura 4.12 | Modelo de programación OpenMP/CUDA. 48                                                                                                                             |

| Figura 4.13 | Arquitectura GPU CUDA. 49                                                                                                                                          |

| Figura 4.14 | Particionado por prismas usando diferentes espacios de memoria. 50                                                                                                 |

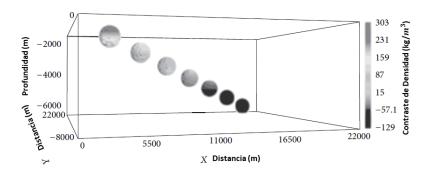

| Figura 5.15 | Configuración del problema de las 7 esferas de densidad variable en el subsuelo, conformadas por 251,946 prismas.  53                                              |

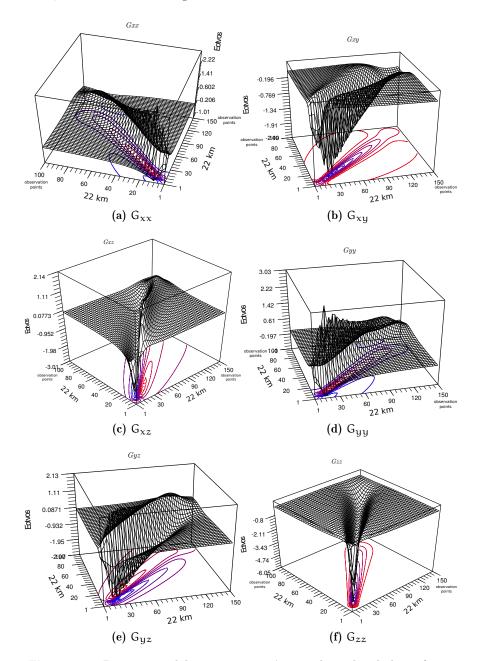

| Figura 5.16 | Respuestas del tensor gravimétrico, obtenidas de las esferas. 54                                                                                                   |

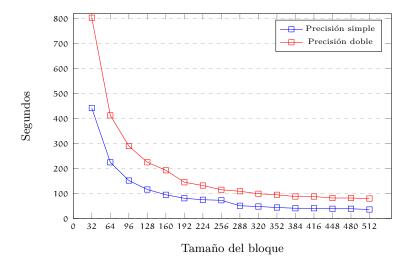

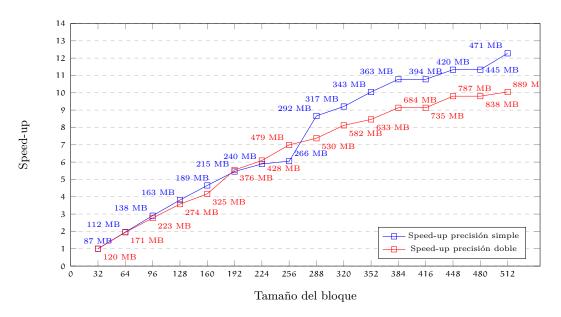

| Figura 5.17 | Comparación del tiempo de ejecución usando un tamaño de bloque variable en múltiplos de 32, en precisión doble y sencilla. 57                                      |

| Figura 5.18 | Comportamiento del speed-up incrementando el número de<br>hilos por bloque en doble y precisión sencilla, con su respec-<br>tiva cantidad de memoria requerida. 57 |

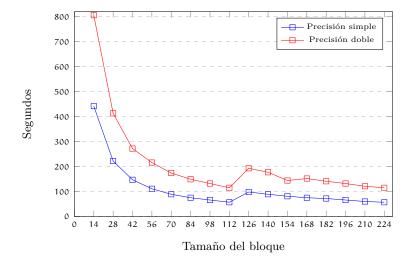

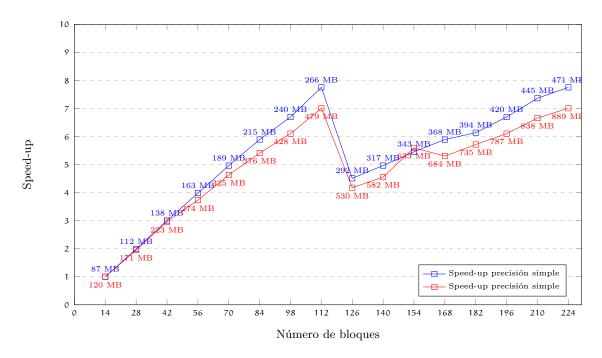

| Figura 5.19 | Tiempo de cómputo obtenido al variar el número de bloques. 59                                                                                                      |

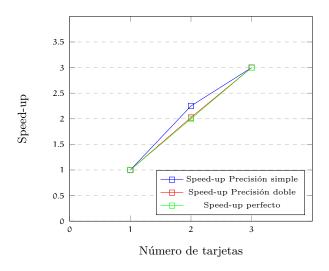

| Figura 5.20 | Speed-up. 60                                                                                                                                                       |

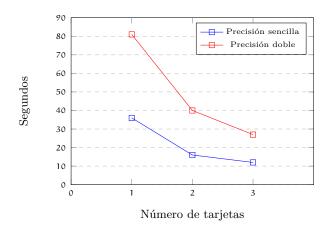

| Figura 5.21 | Comparación del tiempo de ejecución, utilizando tres tarjetas |

|-------------|---------------------------------------------------------------|

|             | gráficas (C2070) en precisión sencilla y doble. 61            |

| Figura 5.22 | Speed-up obtenido con 3 tarjetas. 62                          |

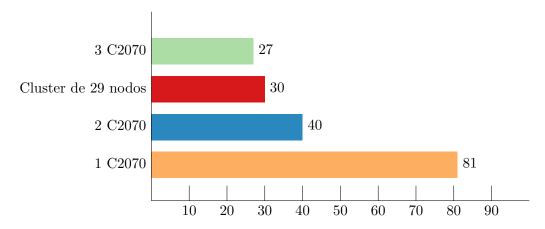

| Figura 5.23 | Tiempos de cómputo (segundos) obtenidos con 3 tarjetas y      |

|             | un cluster de 29 nodos 63                                     |

## ÍNDICE DE TABLAS

| Tabla 1 | Tiempos de cómputo obtenido, usando precisión sencilla y                                                                                                                                                                |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Tabla 2 | doble. PS-Precisión Simple, PD-Precisión Doble 56  Tiempos de cómputo obtenidos y memoria utilizada usando OpenMP y CUDA y una malla en múltiplos de 14 con precisión simple y doble. PS-Precisión Simple, PD-Precisión |

|         | Doble 59                                                                                                                                                                                                                |

| Tabla 3 | Tiempos de cómputo obtenidos utilizando tres GPUs en pre-                                                                                                                                                               |

|         | cisión sencilla y doble. PS-Precisión Simple, PD-Precisión                                                                                                                                                              |

|         | Doble 61                                                                                                                                                                                                                |

| Tabla 4 | Speed-Up obtenidos utilizando tres tarjetas gráficas con pre-                                                                                                                                                           |

|         | cisión simple y doble. PS-Precisión Simple, PD-Precisión Do-                                                                                                                                                            |

|         | ble 62                                                                                                                                                                                                                  |

| Tabla 5 | Errores de los componentes del vector gravimétrico, calcula-                                                                                                                                                            |

|         | dos en los GPUs en precisión doble precisión, con respecto a                                                                                                                                                            |

|         | su contraparte en el cluster. 64                                                                                                                                                                                        |

| Tabla 6 | Errores de los componentes del tensor de gravedad de gra-                                                                                                                                                               |

|         | vedad en doble precisión, con respecto a su contraparte se-                                                                                                                                                             |

|         | cuencial. 65                                                                                                                                                                                                            |

La primera supercómputadora Cray-1 fue construida en 1976 por Seymor Cray, y se pensaba que podría satisfacer la demanda de cómputo requerida en ciencia e ingeniería de aquellos tiempos, sin embargo, actualmente un iPhone X tiene mayor poder de cómputo que la Cray-1.

La necesidad de cómputo que requieren los problemas actuales de computación donde se necesita exactitud y precisión (computación dura) y de inteligencia artificial, son enormes, la simulación del clima, la propagación de ondas sísmicas, la formación de galaxias, la simulación de yacimientos, la dinámica molecular, demandan cada vez más poder de cómputo a bajo costo, no obstante, con la introducción de las unidades de procesamiento gráfico (GPUs) en la computación de alto rendimiento cambio la arquitectura de los equipos y el paradigma de programación y aunque los aceleradores gráficos hacen que muchas aplicaciones puedan acelerar su ejecución a un bajo costo energético existen inconvenientes, en relación a que son relativamente caras de adquirir, relativamente más complejas de programar y sobre todo que el código no es tan fácil de migrar, es decir, está fuertemente ligado a la arquitectura para el que fue desarrollado.

A pesar de que la programación para equipos de alto rendimiento requiere una mayor complejidad debido a la introducción de los GPUs, la construcción de supercómputadoras en los últimos años integra dentro de su arquitectura GPUs, debido a que existe una necesidad inherente de incluirlas para aumentar el rendimiento a un bajo consumo energético, por ejemplo, de acuerdo a la lista de las 500 computadoras más poderosas (www.top500.org) la máquina más poderosa a Junio del 2018 es la Summit - IBM Power System AC922, IBM POWER9 22C 3.07GHz, NVIDIA Volta GV100, Dual-rail Mellanox EDR Infiniband, que utiliza GPUs Volta.

La introducción de los GPUs nació de la necesidad de las limitantes físicas que imponen las velocidades de frecuencia alcanzadas por materiales de los procesadores convencionales y aunque se introdujo la idea de incorporar más de un núcleo de procesamiento por procesador esta tecnología no ha sido suficiente para cubrir la demanda de cómputo, por lo que la evolución del hardware de cómputo de alto rendimiento con multiprocesadores (clusters) básicamente ha seguido dos líneas de desarrollo, la tecnología multinúcleo (multicore) como el procesador Xeon E7-8894 v4 que integra 24 cores con HiperHilado y la tecnología de los GPU (Chai et al., 2007).

Es necesario mencionar, que existen otra clase de aceleradores como los coprocesadores Xeon Phi basados en tecnologías multinúcleo, los cuales tienen la ventaja de

#### 2 INTRODUCCIÓN

que el modelo de programación no cambia al conservar la misma arquitectura x86, sin embargo, no han alcanzado el poder de cómputo que ofrecen los GPUs (Teodoro et al., 2014).

La evolución de los sistemas de computo implicó un cambio en el paradigma de programación al incorporar los GPUs, el diseño de aplicaciones numéricas de propósito científico e ingenieril, tenían que rediseñarse para adaptarse a este nuevo paradigma, y aunque en los últimos 10 años NVIDIA ha tratado de mantener un estándar de programación a través de CUDA (Compute Unified Device Architecture) que incluye: los drivers, el compilador y las librerías; no obstante, cada versión nueva de CUDA exige una mayor versión del hardware, dejando obsoletos a varias arquitecturas previas, actualmente CUDA se encuentra en la versión 9 y la arquitectura de hardware más avanzanda es la Volta, representada con su tarjeta más poderosa la Tesla V100. Y aunque es relativamente caro adquirir una Tesla V100, actualmente es posible realizar programación con los GPUs que están incluidos en los equipos de escritorio y poder desarrollar aplicaciones que no demandan mucho rendimiento.

No obstante, a pesar del vertiginoso crecimiento que ha tenido la arquitectura de los GPUs, y que constantemente las interfaces de programación se actualizan, se puede considerar que se han mantenido en su mismo concepto y metodología, ya que la base de la programación del GPU desde sus origines es el kernel, el cual es un fragmento de código (codelet) que contiene una función que se ejecuta en paralelo por muchos hilos contenidos en bloques, y es la esencia de la programación en GPUs. Las aplicaciones migradas que originalmente se ejecutaban en equipos multinúcleo o cluster son demasiado vastas, se listan algunas de las aplicaciones desarrolladas que pueden ser relevantes en su campo:

Modulación directa de campos gravitacionales en MPI (Couder-Castañeda et al., 2013; Couder-Castañeda et al., 2015), reconstrucción de imágenes 3D (Zhang et al., 2014), propagación de ondas acústicas (Nakata et al., 2011), estudios de turbulencia convectiva (Calore et al., 2016), modelación de transporte radiativo (Al-Refaie et al., 2017), cómputo de estructuras Lagrangianas coherentes (Lin et al., 2017), flujos en medios porosos (Huang et al., 2015), compresión de gráficos (Kaczmarski et al., 2015), procesamiento de imágenes (Galizia et al., 2015), aceleración de consultas en bases de datos(Strohm et al., 2015), modelación en multi-física (Krol et al., 2015), resolución de las ecuaciones de transporte de Boltzmann (Priimak, 2014), aceleración de códigos de Dinámica de Fluidos Computacional (Xu et al., 2014).

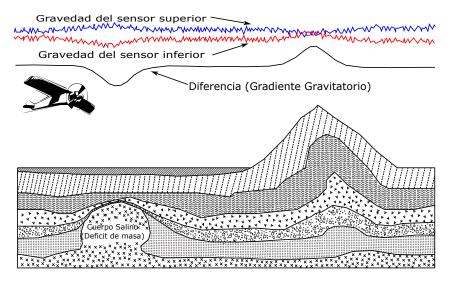

La aplicación que se aborda en este trabajo es la modelación directa de la gradiometría de gravedad, la cual tiene su origen en la guerra fría y era utilizada en los submarinos de guerra para guiarse en la oscuridad, ya que los sonares podían ser detectados por el enemigo, por tal motivo, para que la navegación submarina fuera discreta, medían las variaciones minúsculas de la tracción gravitatoria causadas por las dorsales submarinas; los gravímetros más sofisticados los portaban los submarinos estadounidenses y durante muchos años fue un secreto militar bien guardado, no obstante, ahora la tecnología se ocupa para precisar la localización de las bolsas de petróleo y de gas en las profundidades del subsuelo.

El pionero en medir la fuerza de gravedad de manera novedosa en 1890 fue el barón Roland von Eötvös, físico húngaro, que con un instrumento sencillo medía variaciones diminutas de gravedad en un lugar causadas por la presencia de un objeto cercano de masa suficiente, este primer aparato se llamó gravímetro. Actualmente los gravímetros más comunes usan resorte, pero existen de muy alta tecnología electrónicos que pueden ser utilizados en la carga útil de un nanosatélite (Hernández-Gómez et al., 2017).

Actualmente la utilización de la gravimetría es una de gran utilidad para la exploración geofísica enfocado a la minería, hidrocarburos, estudios de la corteza terrestre y fuentes geotermales. El uso de aviones y barcos para transportar gravímetros son los medios de transporte más comunes debido a que cubren áreas extensas.

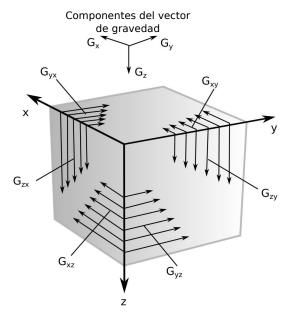

Los nuevos métodos de exploración requieren calcular todo el tensor gravimétrico, el cual está conformado por las primeras derivadas del vector de gravedad en las tres direcciones ortogonales. La variación en la densidad produce las anomalías gravimétricas en el subsuelo, y la aproximación por el modelado directo consiste en discretizar el subsuelo y calcular el efecto acumulativo de cada celda discreta para calcular el efecto total. Los resultados obtenidos de manera estocástica pueden ser comparados con los datos medidos en campo y se modifica el modelo de densidades propuestos hasta que lo observado contra lo calculado coincida. No obstante, el proceso de calcular el modelo de densidades, conocido como problema directo, es altamente costoso computacionalmente, por lo que existen distintos trabajos que lo abordan computacionalmente para reducir el tiempo de cómputo.

La modelación directa es un requisito para muchas aplicaciones geofísicas, debido a que permite calcular las anomalías de la gravedad en modelos geológicos a escala local o regional. Trabajos relacionados pueden verse en (Chen and Zhang, 2018), donde se lleva a cabo el cálculo del modelo directo en un solo GPU con unión de celdas; el cálculo directo en un solo GPU puede consultarse en (Moorkamp et al., 2010a), el cálculo directo en multi-GPU utilizando OpenACC (Couder-Castaneda et al., 2013) y utilizando aceleradores Xeon Phi (Arroyo et al., 2015). La diferencia esencial de los trabajos encontrados que existen en la literatura y el elaborado en esta tesis, es que se propone un diseño basado en prismas convencionales y paralelizado en múltiples GPUs bajo herramientas 100 % gratuitas, sin el uso de directivas como Openacc, lo cual facilita su migración relativamente fácil entre compiladores gratuitos.

#### 4 INTRODUCCIÓN

#### JUSTIFICACIÓN

El tiempo del cálculo del tensor del gradiente gravimétrico tiene relevancia en las áreas de geofísica, donde se utilizan en la exploración de los hidrocarburos, la distribución de cuerpos salinos o someros e incluso modelos sísmicos, este tipo de problemas en su mayoría tienen que procesar una gran cantidad de datos y realizar los cálculos en el menor tiempo posible.

Para la aplicación desarrollada en este trabajo existe una versión previa, implementada utilizando la librería de paso de mensajes (MPI) como control de distribución, la ventaja de usar MPI, es que permite utilizar a la unidad de procesamiento de gráficos (GPU) que están distribuidos en el cluster de computadoras, no obstante, los inconvenientes es que los GPUs que se encuentran integrados en la misma plataforma, no sacan provecho de la velocidad que les puede proporcionar la placa base en la que están integrados. Por tal motivo, se enfocó en desarrollar una aplicación para la modelación directa de campos gravitacionales para plataformas multi-GPU integradas en la misma placa base y de uno a tres GPUs, con la finalidad de obtener el máximo rendimiento.

El tensor del gradiente gravimétrico se calculará a partir de una integración de las API (Application programming interface) OpenMP y CUDA y se construyen dos estructuras, una bidimensional y una tridimensional para realizar el ensamble de prismas del gradiente gravimétrico para con ello mostrar que es posible reducir los tiempos de cómputo en comparación con la ejecución en un CPU convencional y con esto mejorar el rendimiento de la aplicación.

#### OBJETIVO

Diseñar e implementar un código híbrido OpenMP/CUDA en lenguaje C para calcular el tensor del gradiente gravimétrico a partir de un ensamble de prismas rectangulares.

Los objetivos particulares son:

- Crear una estructura de datos bidimensional en CUDA que permita el manejo de arreglos bidimensionales para el manejo de la malla de observaciones.

- Desarrollar una estructura de datos tridimensionales en CUDA que permita el manejo de arreglos tridimensionales para el manejo del ensamble de prismas.

- Migrar las funciones que calculan el tensor a kernels CUDA.

- Validar con ejemplos conocidos los cálculos.

- Diseñar el código utilizando OpenMP como controlador y CUDA como paralelizador.

- Llevar a cabo pruebas de rendimiento desde un GPU hasta 3 GPUs.

## HIPÓTESIS

Es posible reducir el tiempo de cómputo del cálculo directo del tensor del gradiente gravimétrico a partir de un ensamble de prismas rectangulares utilizando GPUs integrados en la misma estación de trabajo.

#### ARQUITECTURA DE LOS CPU Y GPU

Se introducen las arquitecturas de memoria compartida, los sistemas multi-núcleo y los GPU de NVIDIA.

#### 1.1 ANTECEDENTES

Desde tiempos antiguos el hombre ha necesitado hacer cálculos. Ésto lo ha llevado a construir artefactos que lo ayuden a realizarlos de una manera más fácil y rápida. Algunas de las herramientas que se han construido a lo largo del tiempo son: el ábaco, el cuadrante, tablas de Neper, las reglas de cálculo, entre otros.

A partir del siglo XVII se realizaron progresos mecánicos en los sistemas de cálculo. Aparecen las calculadoras mecánicas, como la máquina de Pascal y la máquina Leibnitz.

En 1820, Charles Babbage, construye la máquina analítica, algunas de sus características son:

- Trabajaba con una aritmética de 50 dígitos decimales.

- Consiguió mejorar los tiempos de los cálculos aritméticos a un segundo para sumar y restar y un minuto para multiplicar y dividir.

- Trabajó con tarjetas perforadas para indicar las operaciones a realizar y las variables.

En 1943, Mauchly y Eckert construyeron ENIAC (Electronic Numeric Integrator and Calculator). Fue considerada la primer computadora digital electrónica. Esta computadora estaba orientada a resolver problemas de carácter científico.

En los años siguientes fueron apareciendo computadoras para uso personal como la Comodore Pet, Apple II, TR-80, todas estas maquinas contaban con un solo procesador.

La constante demanda de las nuevas aplicaciones hizo que la industria de los monoprocesadores se encontrara en una situación límite respecto al cumplimiento de la Ley de Moore que afirmó que el número de transistores en un microprocesador se duplicaría cada año, aunque posteriormente en 1975 esta ley se modificó y predijo que el ritmo bajaría aproximadamente cada 18 meses. Como los monoprocesadores

alcanzaron su rendimiento máximo, se comenzaron a buscar otras alternativas. Una de ellas fueron los multiprocesadores, computadoras de propósito general con dos o mas núcleos.

Al mismo tiempo que los multiprocesadores eran aceptados por la sociedad en general y ante el auge de la industria de los videojuegos, grandes y relevantes avances tecnológicos fueron hechos en las Unidades de procesamiento de gráficos (GPU), con el objetivo de liberar a la unidad central de procesamiento (CPU) del proceso de renderizado, propio de las aplicaciones gráficas. La gran demanda de los gráficos de alta calidad motivó el incremento de la potencia de cálculo transformando a las GPU en potentes coprocesadores paralelos. Si bien su origen fue brindar asistencia en aplicaciones gráficas, su uso como co-procesador paralelo de la CPU para resolver aplicaciones de propósito general constituye uno de los tópicos más actuales en la computación de alto desempeño.

A partir del 2005, se comenzó a utilizar la gran potencia de cálculo y el alto número de procesadores de las GPU como arquitectura masivamente paralela para resolver tareas no vinculadas con actividades gráficas, es decir utilizarlas en aplicaciones de propósito general. En este ámbito surgieron varias técnicas, lenguajes y herramientas para la programación de GPU como co-procesador genérico a la CPU. La evolución de estas fue tan rápida como su popularización. Una de las herramientas más difundidas es CUDA que es una arquitectura de cálculo paralelo desarrollada por la compañía NVIDIA.

#### 1.2 ARQUITECTURA CPU

La arquitectura de computadoras se refiere a los atributos de un sistema que son visibles a un programador, en otras palabras, son aquellos atributos que tienen un impacto directo en la ejecución lógica de un programa. La organización de las computadoras se refiere a las unidades funcionales y sus interconexiones, que dan lugar a especificaciones arquitectónicas, como ejemplo tenemos el número de bits usados para representar varios tipos de datos (números, caracteres, booleanos), mecanismos de entrada y salida (E/S) y técnicas para direccionamiento de memoria.

Los componentes de una computadora y sus funciones son:

- Procesador: Se encarga de gestionar y controlar las operaciones.

- Memoria: Almacena información (los programas y los datos necesarios para ejecutarlos).

- Sistema de E/S: Permite la comunicación entre el usuario y la computadora, permitiendo introducir información y desplegar resultados.

• Sistema de interconexión: Proporciona los mecanismos necesarios para interconectar todos los componentes.

En 1945 Von Neumann propuso el modelo de programa almacenado de la computación, donde propone que un programa es una secuencia de instrucciones que son ejecutadas secuencialmente (Von Neumann and Mauchly, 1945).

La mayoría de las computadoras se han construido siguiendo la arquitectura de Von Neumann que cuenta con la estructura:

- Entrada: Unidad que transmite instrucciones y datos del exterior a la memoria (pasando por la ALU).

- Memoria: Unidad que almacena instrucciones y datos, así como los resultados parciales y finales de los programas.

- ALU: Unidad que realiza las operaciones aritmético-lógicas (suma, multiplicación, resta y operaciones lógicas).

- Unidad de control: Interpreta las instrucciones y coordina el resto del sistema.

- Salida: Transmite los resultados al exterior.

El funcionamiento de la arquitectura parte de las instrucciones máquina que se almacenan en memoria, accediendo mediante direcciones y ejecutando los siguientes pasos:

- Búsqueda de la instrucción.

- Decodificación.

- Cálculo de la dirección de los operandos.

- Búsqueda de los operandos.

- Ejecución (realiza la operación y almacena el resultado).

Cada instrucción máquina debe especificar:

- La operación a realizar en el código de operación.

- Información para calcular las direcciones de los operandos y dónde se guarda el resultado.

- Información de la dirección de la próxima instrucción a ejecutar.

#### 1.3 RENDIMIENTO CPU

La mayoría de las computadoras se construyen utilizando un reloj que funciona a una frecuencia constante (ciclos de reloj). El tiempo, es la medida del rendimiento de

una computadora. La ejecución de un programa se mide en segundos, el rendimiento se mide como una frecuencia de eventos por segundo, ya que un menor tiempo de ejecución significa mayor rendimiento.

El tiempo de un ciclo de reloj se puede referenciar por su duración, por ejemplo: 10 nano segundos, 100 MHZ. Por lo tanto, podemos expresar el tiempo del CPU como:

**Tiempo de CPU** = Ciclos de reloj de CPU para un programa  $\times$  la duración del ciclo de reloj.

Además del número de ciclos de reloj para ejecutar un programa, también podemos contar el número de instrucciones ejecutadas. Si conocemos el número de ciclos de reloj y el número de instrucciones ejecutadas podemos calcular el número medio de ciclos de reloj por instrucción (CPI):

**CPI** = Ciclos de reloj de CPU para un programa / Número de instrucciones ejecutadas

Sin embargo hay que tener en cuenta que la medida real del rendimiento del CPU es el tiempo.

#### 1.4 LEY DE AMDAHL

El término cuello de botella se utiliza para referirse al subsistema o subsistemas que degradan el rendimiento del equipo en general. Dado que todos los componentes de una computadora están interconectados, un cambio en un subsistema tiene un impacto inmediato en el rendimiento del sistema en general.

Ahora bien, estos conceptos pueden ser llevados al rendimiento de un programa. Si se requiere mejorar el rendimiento de un programa, lo mejor es enfocarse en mejorar rutinas donde se tienen identificados problemas de rendimiento.

Si las rutinas mejoran se pueden bajar los tiempos de ejecución. Como métrica se emplea la aceleración o ganancia en tiempos, conocida como speed-up, que se define como el cociente del tiempo empleado por el sistema a evaluar y una referencia:

$$\alpha = \frac{\text{Tiempo consumido}}{\text{Tiempo de referencia}}$$

Para cuantificar el rendimiento global de un sistema a partir del rendimiento de sus partes se utiliza la expresión de la ley de Amdhal, que establece que la mejora obtenida en el rendimiento de un sistema debido a la alteración de uno de sus componentes está limitada por la fracción de tiempo que se utiliza dicho componente. De forma analítica, esta ley se expresa de la siguiente manera:

$$\alpha = \frac{1}{(1-p) + \frac{p}{\alpha_{m}}}$$

donde:

α: Representa el cociente entre el tiempo de ejecución completo del programa antes de mejorar alguno de sus componentes y el tiempo de ejecución después de ser mejorado dicho componente.

$\alpha_m$ : Representa el factor de mejora que se ha introducido en el subsistema alterado.

p: Es la fracción de tiempo que, del sistema completo original utiliza el subsistema que se ha alterado (es decir, cuánto se usa el componente que se ha mejorado en el sistema original).

#### 1.5 ORGANIZACIÓN DE UN SISTEMA MULTIPROCESADOR

En la organización de un sistema multiprocesador hay dos o más procesadores. Cada procesador es autónomo, incluyendo una unidad de control, una ALU, registros y caché. Cada procesador tiene acceso a una memoria principal compartida y a los dispositivos de E/S a través de alguna forma de mecanismo de interconexión. Los procesadores pueden comunicarse entre sí a través de la memoria. También es posible que los procesadores intercambien señales directamente. La memoria a menudo se organiza de forma que sean posibles los accesos simultáneos a bloques de memoria separados.

La organización más común en las PC, estaciones de trabajo y servidores es el bus de tiempo compartido. El bus de tiempo compartido es el mecanismo más simple para construir un sistema multiprocesador. La estructura y las interfaces son básicamente las mismas que las de un sistema de único procesador, que utilice un bus para la interconexión. El bus consta de dos líneas de control, dirección y datos. Para facilitar las transferencias se proporcionan los siguientes elementos:

• Direccionamiento: Debe ser posible distinguir los módulos del bus para determinar la fuente y el destino de los datos.

- Arbitraje: Se proporciona un mecanismo para gestionar las peticiones que compiten por el control del bus, utilizando algún tipo de esquema de prioridad.

- Tiempo compartido: Cuando un módulo está controlando el bus, los otros módulos no tienen acceso al mismo y deben, si es necesario, suspender su operación hasta que se disponga del bus.

En este caso, hay varias CPU además de varios procesadores que intentan tener acceso a uno o más módulos de memoria a través del bus.

Algunas de las ventajas de la organización del bus son:

- Simplicidad: La interfaz lógica y física de cada procesador para el direccionamiento, el arbitraje y para compartir el tiempo del bus, es el mismo que el de un sistema con un solo procesador.

- Flexibilidad: Se pueden conectar más procesadores al bus.

- Fiabilidad: El fallo de cualquiera de los dispositivos conectados no provocara el fallo de todo el sistema.

Sin embargo, la desventaja del bus son las prestaciones. Es decir, todas las peticiones a memoria pasan por el bus. En consecuencia, la velocidad del sistema está limitada por el tiempo de ciclo. Para mejorar las prestaciones, se puede equipar a cada procesador de una memoria caché, con lo cual se reduciría el número de accesos. Normalmente las PC's y las estaciones de trabajo tienen dos niveles de caché, un caché L1 interna (en el mismo chip que el procesador) y una cache L2 externa o interna.

El uso de cachés introduce algunas consideraciones nuevas, puesto que cada caché local contiene una imagen de una parte de la memoria, si se altera una palabra en un caché, podría invalidar una palabra en otro caché. Para evitarlo, se debe avisar a los otros procesadores de que se ha producido una actualización de memoria.

#### 1.6 CONCURRENCIA

La concurrencia en el software es una forma de gestionar los recursos compartidos usados al mismo tiempo. Un término utilizado en la concurrencia es el termino de hilo (thread), un hilo tiene la propiedad de poder compartir recursos entre sí, por ejemplo, el rango de direcciones de memoria asignadas. Podemos definir a un hilo como una secuencia discreta de instrucciones relacionadas que se ejecuta independientemente de otras secuencias de instrucciones. Cada programa tiene al menos un hilo principal, que inicializa el programa y comienza a ejecutar las instrucciones, el hilo principal puede crear otros hilos que realizan varias tareas, o simplemente puede hacer todo el trabajo en sí sin crear más hilos. (Jason Roberts, 2006).

El modelo computacional de hilo cuenta con tres niveles:

- Hilos de nivel de usuario: Hilos creados y manipulados en el software de la aplicación.

- Hilos a nivel de kernel: La forma en que el sistema operativo implementa la mayoría de los hilos.

- Hilos de hardware: Cómo aparecen los hilos en los recursos de ejecución en el hardware.

Algunas ventajas que podemos observar de la concurrencia en el software son las siguientes:

- Permite mayor eficiencia en el uso de los recursos del sistema. El uso eficiente de la utilización de los recursos es la clave para maximizar el rendimiento de los sistemas computacionales.

- Proporciona una abstracción para la implementación de algoritmos de software o aplicaciones que están en paralelo.

Cuando múltiples hilos de ejecución están corriendo en paralelo, significa que los hilos activos están ejecutándose simultáneamente en diferentes recursos del hardware, es decir, múltiples hilos pueden hacer progreso simultáneo. Cuando múltiples hilos de ejecución del software están ejecutándose concurrentemente, las ejecuciones de los hilos son intercaladas dentro de un sólo recurso del hardware.

En los sistemas multitarea, un proceso se puede encontrar en tres estados distintos (Asenjo Plaza Rafael, 2001):

- En ejecución: Está siendo atendido por la CPU, o usando la CPU.

- Listo: El proceso está libre para ser ejecutando.

- Bloqueado: Está a la espera de que ocurra algún evento, normalmente alguna transacción de E/S.

En sistemas monoprocesador sólo puede haber un proceso en ejecución, pero varios listos y bloqueados. El sistema operativo tiene una lista con los procesos listos (ordenados por prioridad) y otra con los procesos bloqueados (en este caso la lista está desordenada).

Las transiciones entre estos estados se producen mediante llamadas del sistema operativo a una serie de funciones, con el nombre del proceso como parámetro, excepto en el caso del paso de listo a bloqueado, que es provocada por el propio proceso cuando necesita realizar una operación de E/S.

#### 1.7 SISTEMAS PARALELOS

Por definición, una arquitectura paralela es aquella que cuenta con varias unidades de procesamiento y permite el procesamiento paralelo. La disposición de las conexiones entre los procesadores y la memoria determina el origen de distintas arquitecturas, las cuales serán más adecuadas para resolver ciertos problemas.

La construcción de una aplicación en paralelo no siempre deriva naturalmente de la aplicación secuencial. En toda aplicación paralela se deben considerar las comunicaciones existentes entre los distintos procesos, las cuales pueden conducir a un mal desempeño del programa.

En sistemas paralelos se pueden distinguir dos conceptos: el paralelismo de las instrucciones y el paralelismo de la máquina

- Paralelismo en las instrucciones: Se produce cuando las instrucciones de una secuencia son independientes y por tanto pueden ejecutarse en paralelo, también depende de la frecuencia de dependencias de datos que haya en el código, estos factores dependen a su vez de la arquitectura del conjunto de instrucciones y de la aplicación. El paralelismo en las instrucciones depende también de lo que se llama latencia de una operación, es decir, el tiempo que transcurre hasta que el resultado de una instrucción está disponible para ser usado como operando de una instrucción posterior, la latencia determina cuánto retraso causará una dependencia de datos.

- El paralelismo de la máquina: Es una medida de la capacidad del procesador para sacar partido al paralelismo de las instrucciones. El paralelismo de la máquina depende del número de instrucciones que pueden captarse y ejecutarse al mismo tiempo, así como de la velocidad y sofisticación de los mecanismos que usa el procesador para localizar instrucciones independientes.

El paralelismo en las instrucciones, como el paralelismo de la máquina, son factores importantes para mejorar el uso de los recursos. Un programa puede no tener el suficiente nivel de paralelismo en las instrucciones como para sacar el máximo partido al paralelismo de la máquina.

El empleo de una arquitectura con instrucciones de longitud fija, como en una arquitectura computacional con un conjunto de instrucciones reducidas (RISC), aumenta el paralelismo en las instrucciones ya que posibilita la segmentación y el paralelismo en la ejecución de instrucciones, así como reducir los accesos a la memoria. Por otra parte, un escaso paralelismo de la máquina limitará las prestaciones sin que importe la naturaleza del programa.

#### 1.8 PLATAFORMAS DE CÓMPUTO PARALELAS

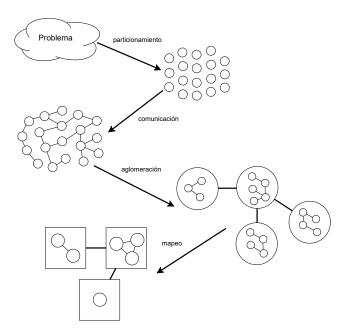

La construcción del software paralelo se basa en la idea de dividir un problema grande en subproblemas, cada uno de los cuales se resuelve en forma concurrente al resto.

Implementar algoritmos paralelos que se ejecuten sobre máquinas paralelas no es una tarea sencilla, ya que no existe una solución paralela única. Para determinar si un programa puede paralelizarse se debe analizar la naturaleza del problema y la relación entre los datos, para el análisis se pueden realizar los siguientes puntos:

- Dividir el trabajo en tareas.

- Asignar tareas a los distintos procesadores.

- Ver la relación de los procesadores.

- Verificar como se organizan las comunicaciones.

Cada uno de estos aspectos, que, si bien aparentan ser independientes no lo son, las decisiones adoptadas en uno influyen directamente en los otros. Estos problemas se pueden resolver si se utiliza una metodología para los desarrollos.

Para lograr la ejecución de software paralelo, el hardware debe proporcionar una plataforma que soporte la ejecución simultánea de múltiples hilos. La arquitectura de computadoras puede ser clasificada por dos diferentes dimensiones. La primera es el número de instrucciones en el flujo que deberán ser procesadas en un solo punto en el tiempo. La segunda es el número de datos que pueden procesarse en un solo punto en el tiempo. A este sistema de clasificación se le conoce como la taxonomía de Flynn (Flynn, 1972), y es representado en la Figura 1.1.

Figura 1.1: Taxonomía de Flynn

La taxonomía de Flynn cuenta con cuatro categorías:

- Una sola instrucción un único dato (SISD): No se ofrece paralelismo en el hardware. Las instrucciones se ejecutan de manera secuencial. Solo un flujo de datos es procesado por el CPU durante un ciclo de reloj dado.

- Múltiples instrucciones un único dato (MISD): Se procesa un único flujo de datos a través de varias secuencias de instrucciones de forma simultánea. En la mayoría de los casos, múltiples flujos de instrucciones necesitan múltiples flujos de datos para ser útil, por lo que en general esta clase de computadora paralela se utiliza más como un modelo teórico que de práctica.

- Una sola instrucción múltiples datos (SIMD): Un flujo de instrucciones simples tiene la capacidad de procesar múltiples flujos de datos simultáneamente. Estas máquinas son útiles en aplicaciones de tratamiento de señales digitales, procesamiento de imágenes y las aplicaciones multimedia, como audio y video.

- Múltiples instrucciones múltiples datos (MIMD): Se tiene la capacidad de ejecutar múltiples flujos de instrucciones, mientras se trabaja en un flujo de datos separado e independiente. Esta es la plataforma de computación en paralelo más común en estos días. Nuevas plataformas como los *clusters* (conjunto de computadoras que se comportan como una sola) caen en esta categoría.

Dado que las máquinas actuales encajan en las categorías SIMD o MIMD, se puede explotar a nivel de datos y nivel de tareas el paralelismo en el software.

La tecnología SMT (Simultaneous Multithreading) permite que un procesador aparezca como múltiples procesadores lógicos. Desde el enfoque de la microarquitectura, las instrucciones de los procesadores lógicos son persistentes y se ejecutan simultáneamente en recursos de ejecución compartida. En otras palabras, se pueden programar múltiples hilos, pero como los recursos de ejecución se comparten la microarquitectura debe determinar cómo y cuándo intercalar la ejecución de los hilos. El siguiente nivel después del procesamiento Multi-Hilado es el procesamiento Multi-Núcleo, estos núcleos cuentan con sus propios recursos de ejecución y de arquitectura, dependiendo del diseño estos procesadores pueden compartir un gran cache en el chip además estos núcleos individuales pueden combinarse con SMT aumentando el número de procesadores lógicos por el doble de núcleos de ejecución.

#### 1.9 EVOLUCIÓN DE LA GPU

La historia de las GPU se inicia en la década de los 60. Las primeras GPU tuvieron capacidades muy reducidas, sin embargo, su crecimiento no se detuvo. Así como la velocidad del procesador avanzó a través de dos líneas: incrementando la velocidad del reloj y/o incrementando el número de núcleos, la evolución de las GPU tuvo su

origen a finales de los 80 cuando se inicia la gran demanda de mejores interfaces gráficas por parte de los sistemas operativos. Esto implicó que a principios de los 90 se comenzaran a vender aceleradores gráficos 2D para computadoras personales.

Al mismo tiempo, en la comunidad profesional y mediante la empresa Silicon Graphics, se introdujó al mercado el uso de gráficos 3D en una gran variedad de ámbitos. Además, se desarrolló la librería OpenGL para ser usada como método independiente de la plataforma y poder escribir aplicaciones gráficas 3D. La demanda de aplicaciones gráficas 3D tuvo un gran crecimiento, el cual fue alentado primero, por el desarrollo de videojuegos en primera persona, FPS (Harrigan., 2004) como Doom, Duke Nukem 3D y Quake, los cuales demandaron constantemente mayores capacidades para lograr mejor realismo.

En 1999 NVIDIA lanza al mercado la tarjeta gráfica Geforce 256, la cual permitía realizar transformaciones e iluminación a través del hardware, además de brindar mejores condiciones de visualización. La siguiente generación de NVIDIA constituyó un gran paso en la tecnología de las GPU, fue considerada la primer GPU con implementación nativa de la primera versión de la interfaz de programación de aplicaciones (API) DirectX8. Esto dio paso a que por primera vez los desarrolladores tuviesen el control en la GPU.

Desde 1999 hasta 2002, NVIDIA dominó el mercado de las tarjetas gráficas con las GeForce. En ese período, las mejoras se orientaron hacia el campo de los algoritmos 3D y la velocidad de los procesadores gráficos. Las memorias también necesitaban mejorar la velocidad, por lo que se incorporaron las memorias del tipo DDR (Double Data Rate) a las tarjetas gráficas (Bruce Jacob, 2007). Las capacidades de memoria de vídeo pasaron de los 32 MB de las Geforce 2 a los 64 y 128 MB de la GeForce 4. A partir del 2006, NVIDIA y ATI tomaron el liderazgo del mercado con sus series GeForce y Radeon, respectivamente.

#### 1.10 PIPELINE GRÁFICO

La GPU desde sus inicios fue un procesador con muchos recursos computacionales. Actualmente ha adquirido notoriedad por su uso en aplicaciones de propósito general, pasó de ser un procesador con funciones especiales a ser considerado la arquitectura base de aplicaciones paralelas y se han convertido en una parte integral de los sistemas actuales de computación.

En los últimos años, su evolución implicó un cambio, dejó de ser un procesador gráfico potente para convertirse en un co-procesador apto para el desarrollo de aplicaciones paralelas de propósito general con demanda de anchos de banda, de procesamiento y de memoria superiores a los ofrecidos por la CPU. Para poder entender a la GPU como una unidad de procesamiento de propósito general (GPGPU) es necesario comprender su funcionamiento desde el punto de vista del hardware, es decir, los gráficos. Esto permitirá realizar una analogía de cada uno de los mecanismos propios con los que se aplican en GPGPU.

La GPU trabaja cuando la aplicación envía a la GPU una secuencia de vértices, agrupados en lo que se denominan primitivas geométricas (polígonos, líneas y puntos) y son tratadas secuencialmente a través de cuatro etapas:

- Transformación de vértices: Es la primera etapa del pipeline de procesamiento gráfico. En ella se lleva a cabo una secuencia de operaciones matemáticas sobre cada uno de los vértices suministrados por la aplicación.

- Ensamblado de primitivas y rasterización: Los vértices generados y transformados en la etapa anterior pasan a esta segunda etapa, donde son agrupados en primitivas geométricas basándose en la información recibida junto con la secuencia inicial de vértices. Como resultado, se obtiene una secuencia de triángulos, líneas o puntos. La rasterización es el proceso por el cual se determina el conjunto de píxeles "cubiertos" por una primitiva determinada. Los resultados de la rasterización son conjuntos de localizaciones de píxeles y conjuntos de fragmentos. Un fragmento tiene asociada una localización de píxel e información relativa a su color y uno o más conjuntos de coordenadas de textura. Se puede pensar en un fragmento como en un "píxel en potencia": si el fragmento supera con éxito el resto de etapas del pipeline, se actualizará la información de píxel como resultado.

- Interpolación, texturas y colores: Una vez hecha la rasterización, el/los fragmentos obtenidos son sometidos a operaciones de interpolación, operaciones matemáticas y de textura y determinación del color final de cada fragmento. Además de establecer el color final del fragmento, en esta etapa es posible descartar un fragmento determinado para impedir que su valor sea actualizado en memoria; por tanto, esta etapa emite uno o ningún fragmento actualizado para cada fragmento de entrada.

- Operaciones Raster: En esta última etapa del pipeline se realizan las operaciones llamadas raster, analizan cada fragmento, sometiéndolo a un conjunto de pruebas relacionadas con aspectos gráficos del mismo. Estas pruebas determinan los valores que tomará el píxel generado en memoria a partir del fragmento original. Si cualquiera de estas pruebas falla, es en esta etapa cuando se descarta el píxel correspondiente, y por tanto no se realiza la escritura en memoria del mismo. En caso contrario, y como último paso, se realiza la escritura en memoria, denominada framebuffer (Godse., 2009), como resultado final del proceso.

El paradigma paralelo estuvo presente desde los inicios de la GPU. En el pipeline gráfico la entrada de un estado es la salida del anterior, en este caso el paralelismo es a nivel de tareas, varios datos pueden estar al mismo tiempo en distintos estados del pipeline. Los recursos son divididos entre las distintas etapas del pipeline, por lo que varias unidades de cómputo trabajan en paralelo en los diferentes estados del pipeline. En otras palabras, los recursos en la GPU se dividen en el espacio. Esto implica un nivel de paralelismo interno en la etapa y otro entre las etapas del pipeline.

#### 1.11 ARQUITECTURA GPU

Algunas de las características básicas de la GPU son las siguientes:

- Siguen el modelo SIMD. Todos los núcleos ejecutan a la vez una misma instrucción, por lo tanto, solo se necesita decodificar la instrucción una única vez para todos los núcleos.

- La velocidad de ejecución se basa en la explotación de la localidad de los datos, tanto la localidad temporal (cuando accedemos a un dato, es probable que se vuelva a utilizar el mismo dato en un futuro cercano) como la localidad espacial (cuando accedemos a una fecha, es muy probable que se utilicen datos adyacentes a los ya utilizados en un futuro cercano y por eso, se utilizan memorias caché que guardan varios datos en una línea del tamaño del bus).

- La memoria de un GPU se organiza en varios tipos de memoria (local, global, constante y textura), que tienen diferentes tamaños, tiempos de acceso y modos de acceso (por ejemplo, solo lectura o lectura/escritura).

- El ancho de banda de la memoria es mayor.

Una GPU está altamente segmentada, lo que indica que posee gran cantidad de unidades funcionales. Estas unidades funcionales se pueden dividir principalmente en dos: aquéllas que procesan vértices, y aquéllas que procesan píxeles. Por tanto, se establecen el vértice y el píxel como las principales unidades que maneja la GPU.

Inicialmente, a la GPU le llega la información de la CPU en forma de vértices. El primer tratamiento que reciben estos vértices se realiza en el vertex shader. Aquí se realizan transformaciones como la rotación o el movimiento de las figuras. Tras ésto, se define la parte de estos vértices que se va a ver, y los vértices se transforman en píxeles mediante el proceso de rasterización. Estas etapas no poseen una carga relevante para la GPU.

Donde se encuentra el principal *cuello de botella* de la GPU es en el siguiente paso: el píxel shader. Aquí se realizan las transformaciones referentes a los píxeles, tales como la aplicación de texturas.

El modelo píxel shader se convirtió en un referente, el cual permitió el desarrollo de aplicaciones sobre GPU, incrementando la complejidad de las operaciones de vértice y fragmentos. La evolución de la arquitectura de las GPU se centró principalmente en las etapas del pipeline gráfico.

#### 1.12 DIFERENCIAS ENTRE EL CPU Y EL GPU

Una diferencia importante entre un CPU y un GPU es la comparación entre la forma en que manejan el procesamiento de tareas. Un CPU está compuesto de varios núcleos optimizados para el procesamiento en serie, mientras que un GPU está formado de miles de núcleos más pequeños y eficientes los cuales están diseñados para realizar múltiples tareas simultáneamente, ver Figura 1.2.

Las GPU poseen miles de núcleos que procesan las cargas de trabajo de forma paralela y muy eficiente.

Figura 1.2: Diferencias entre el número de núcleos del CPU y el GPU.

Una de las mayores diferencias con la CPU recae en su arquitectura. A diferencia del CPU, que tiene una arquitectura de Von Neumann, la GPU se basa en el Modelo Circulante. Este modelo facilita el procesamiento en paralelo, y la gran segmentación que posee la GPU para sus tareas.

En síntesis, el modelo convencional se concentra en el control de las instrucciones, mientras que el circulante lo hace en el ancho de banda de los datos.

Debido a la organización de las GPU respecto a la CPU, hay que tener en cuenta que una GPU no puede acceder directamente a la memoria principal y que una CPU no puede acceder directamente a la memoria de una GPU. Por lo tanto, habrá que copiar los datos entre CPU y GPU de manera explícita es decir de la CPU a la GPU y viceversa.

La Figura 1.3 muestra la relación que se tiene entre el GPU y el CPU es decir cuando el código de una aplicación es lanzado desde el CPU debe tener indicadas secciones específicas que indicaran que esa parte del código debe ser ejecutado en el GPU.

Figura 1.3: Flujo de un código de aplicación ejecutado en paralelo

En este capítulo se aborda las metodologías de programación utilizadas, OpenMP y CUDA, resaltando sus ventajas y considerando sus desventajas.

#### 2.1 LA ARQUITECTURA CUDA

Las unidades de procesamiento gráfico (GPU) implementan en hardware el pipeline gráfico, el cual, al ser un algoritmo paralelo con cómputo intensivo, determinó la evolución de las GPU al enfocar los avances en satisfacer la demanda de mejor rendimiento en la ejecución del pipeline. Ésto unido a su bajo costo hace que cualquier computadora personal cuente con una GPU. Sin embargo, en un principio su programación no era tan simple, implicaba conocer detalles de la arquitectura del pipeline gráfico y utilizar interfaces de programación de aplicaciones (API) como OpenGL (Wright., 2007) o DirectX (Root., 1999).

En el año 2006 NVIDIA presentó la tecnología Compute Unified Device Architecture (CUDA) para su última generación de tarjetas gráficas, la serie G80. CUDA propone una filosofía integradora, con un lenguaje de programación como es C y la arquitectura paralela de una GPU, desvinculándose además del pipeline gráfico.

La tecnología CUDA permite considerar a la GPU como una arquitectura paralela para la resolución de problemas de propósito general. El desarrollo de dichas aplicaciones paralelas es posible principalmente, por dos razones:

- Las tarjetas gráficas NVIDIA, son un componente común en la mayoría de las computadoras personales actuales.

- Es de fácil aprendizaje, más para aquellos programadores con conocimientos de los lenguajes tipo C o C++.

La arquitectura de CUDA es realmente particular en muchos aspectos. A diferencia de otros GPU, CUDA no sólo divide los recursos de computación en vertex y pixel shaders, además añade un pipeline para shaders unificado que permite a cada unidad aritmético lógica (ALU) en el chip ser "transformada" por una aplicación para efectuar operaciones de cómputo de propósito general.

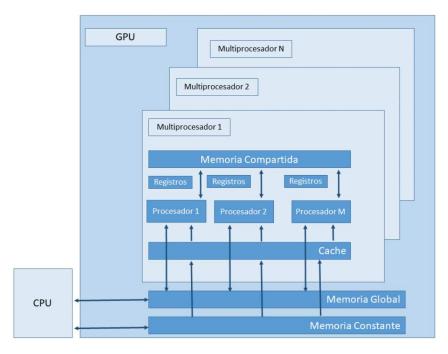

CUDA presenta a la arquitectura de la GPU como un conjunto de multiprocesadores MIMD (Múltiples Instrucciones-Múltiples Datos). Cada multiprocesador posee

un conjunto de procesadores SIMD (Instrucción Simple-Múltiples Datos). Respecto a la memoria, existen numerosos modelos conviviendo en esta arquitectura: cada procesador SIMD posee una serie de registros a modo de memoria local (sólo accesible por el procesador) a su vez cada multiprocesador posee una memoria compartida (accesible por todos los procesadores SIMD del multiprocesador) y finalmente la memoria global, la cual es accesible por todos los multiprocesadores y por ende, por todos y cada uno de los procesadores SIMD.

#### 2.2 PLATAFORMA DE CÁLCULO PARALELO CUDA

No todos los problemas pueden ser resueltos en la GPU, los más adecuados son aquellos que pueden resolverse mediante la aplicación del paradigma paralelo de datos, es decir aplican la misma sentencia o secuencia de código a todos los datos de entrada. Se puede decir que una solución de un problema en GPU será más ventajosa respecto a la solución en la CPU si la aplicación tiene las siguientes propiedades:

- El algoritmo tiene un orden de ejecución cuadrático o superior: el tiempo necesario para realizar la transferencia de datos entre la CPU y la GPU tiene un gran costo, el cual no suele verse compensado por el bajo costo computacional de un método lineal.

- Es mayor la carga de cálculo computacional en cada hilo: de nuevo para compensar el tiempo de transferencia de información es conveniente que cada hilo posea una carga computacional considerable.

- Es menor la dependencia entre los datos para realizar los cálculos, ésto es posible si cada SM sólo necesita de los datos de su memoria local o compartida y no necesita acceder a memoria global, la cual tiene un acceso más lento.

- Es menor la transferencia de información entre CPU y GPU. La situación óptima es cuando la transferencia sólo se realiza una vez, al comienzo y al final del proceso. Esto significa una transferencia de los datos de entrada, desde la CPU a la GPU y una al final, desde la GPU a la CPU, para obtener los resultados. Es bueno no tener transferencias intermedias, ya sea de resultados parciales o datos de entradas intermedios.

- No existen secciones críticas, es decir, varios procesos no necesitan escribir en las mismas posiciones de memoria, las lecturas de memoria global y compartida puede ser simultánea, pero las escrituras en la misma posición de memoria plantean un acceso a un recurso compartido, lo cual implica contar con mecanismo de acceso seguro. Este proceso hace más lenta la solución del proceso global.

Además, es necesario que las estructuras de datos en la aplicación que se ejecuta en la CPU se adapten o puedan transformarse a estructuras más simples del tipo matriz o vector a fin de poder ser compatibles con las estructuras que maneja la GPU.

El modelo de programación CUDA asume que los hilos CUDA se ejecutan en una unidad física distinta, la cual actúa como co-procesador (device) al procesador (host). Como CUDA C es una extensión del lenguaje de programación C, permite al programador definir funciones C, llamadas kernels, las cuales al ser invocadas son ejecutadas en paralelo por N hilos diferentes en la GPU.

Los kernels son el componente principal del modelo de programación de CUDA, son funciones invocadas desde el host (CPU Central) y ejecutadas en el dispositivo. Cuando se invoca un kernel, éste se ejecuta N veces en N hilos diferentes. Cada hilo se diferencia de los demás por su identificador, el cual es único y accesible en el kernel a través de una variable interna y predefinida de CUDA llamada threadIdx. A través de threadIdx se puede definir el comportamiento específico de cada uno de los hilos.

Para la definición de un kernel se deben respetar varias condiciones, las cuales son:

- El tipo de la función kernel es void.

- Debe llevar la etiqueta \_\_global\_\_, la cual identifica a un kernel y determina que la función es invocada desde el host (CPU) y ejecutada en el device (GPU).

- Todos los hilos que se activen durante la ejecución del kernel, ejecutan el mismo programa, el cual coincide con el kernel que lo activó.

- El número de hilos es conocido antes de la ejecución del kernel, ellos serán agrupados, según se indica en la invocación, en grupos denominados bloques. Todos los bloques tienen igual número de hilos.

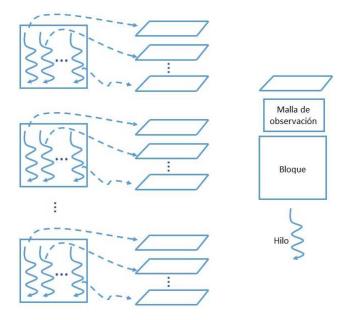

Existe una jerarquía perfectamente definida sobre los hilos de CUDA. Los hilos se agrupan en bloques, los cuales se pueden ver como vectores (una dimensión) o matrices (dos o tres dimensiones). Los hilos de un mismo bloque pueden cooperar entre sí, compartiendo datos y sincronizando sus ejecuciones. Sin embargo, los hilos de distintos bloques no pueden cooperar entre sí.

Los bloques a su vez, se organizan en una malla, la cual puede ser de una o dos dimensiones (en las nuevas arquitecturas, se admiten tres dimensiones). Los bloques e hilos por bloque que tendrá una malla son valores establecidos antes de la invocación, los cuales permanecen invariables durante toda la ejecución del kernel. Dada la organización que provee CUDA para los hilos y como cada uno de ellos tiene un identificador único (threadIdx).

Más específicamente threadIdx tiene tres componentes (x, y, z), permitiendo según la dimensión del bloque, identificar con precisión cada hilo. Cuando el bloque es de una dimensión, las componentes y y z tienen el valor 1, en el caso de un bloque de dos dimensiones sólo la componente z tiene el valor 1.

Lo mismo ocurre con los bloques y las mallas, pero para ellos CUDA tiene definida tres variables: blockIdx y blockDim para bloques, y gridDim para mallas, todas de tres componentes. blockIdx permite identificar a los bloques y las variables blockDim y gridDim contienen el tamaño de cada bloque y de cada malla, respectivamente.

Un programa CUDA está compuesto de una o más fases, las cuales son ejecutadas en el host o en el dispositivo. Aquellas partes que exhiben poco o nada de paralelismo se implementan en el código a ejecutar sobre el host, no así las que pueden ser resueltas aplicando paralelismo de datos, éstas son implementadas a través de código que se ejecutará en el dispositivo, en este caso la GPU. Si bien en el programa CUDA existen dos partes bien diferenciadas, será el compilador el responsable de su diferenciación.

Para ello, el código desarrollado para ejecutarse en el host será compilado con el compilador estándar de C (o el del lenguaje secuencial utilizado) y ejecutado en la CPU como un proceso común. El código a ejecutarse en el dispositivo, escrito en C extendido con palabras claves que expresan el paralelismo de datos y las estructuras de datos asociadas, será compilado con el compilador propio de CUDA (nvcc) (Kandort Edward, 2010).

La Figura 2.4 muestra de manera gráfica la ejecución de un programa en CUDA.

Figura 2.4: Ejecución de un programa CUDA

#### 2.3 MODELO DE PROGRAMACIÓN CUDA

CUDA propone un modelo de programación SIMD (Instrucción Simple-Múltiples Datos) con funcionalidades de procesamiento de vector. La programación de GPU se realiza a través de una extensión del lenguaje estándar C/C++ con constructores y palabras claves. La extensión incluye dos características principales: la organización del trabajo paralelo a través de hilos concurrentes y la jerarquía de memoria de la GPU con sus diferentes costos de acceso. Los hilos en el modelo CUDA son agrupados en Bloques, los cuales se caracterizan por:

- El tamaño del bloque: Cantidad de hilos que lo componen determinada por el programador.

- Todos los hilos de un bloque se ejecutan sobre el mismo SM (Streaming Multiprocessor).

- Los hilos de un bloque comparten la memoria, la cual pueden usar como medio de comunicación entre ellos.

Varios bloques forman una malla y los hilos de diferentes bloques de un malla no se pueden comunicar entre si, esto permite que el administrador de bloques sea rápido y flexible, no tiene en cuenta el número de SM utilizados para la ejecución del programa. Además de las variables en la memoria compartida, los hilos tienen acceso a otros dos tipos de variables: locales y globales. Las variables locales residen en la memoria dinámica de acceso aleatorio (DRAM) de la tarjeta y son privadas a cada hilo.

Las variables globales también residen en la memoria DRAM de la tarjeta, se diferencian de las locales en que pueden ser accedidas por todos los hilos aunque pertenezcan a distintos bloques. Esto lleva a una manera de sincronización global de los hilos.

Como la memoria DRAM es más lenta que la memoria compartida, los hilos de un bloque se pueden sincronizar mediante una instrucción especial, la cual es implementada en memoria compartida.

En un programa CUDA se diferencian dos ámbitos: el host y el dispositivo (device). El host es el ordenador al cual está conectada la tarjeta gráfica y será quien rija su comportamiento. El device es la tarjeta gráfica.

La comunicación de datos entre el host y el dispositivo se lleva a cabo a través de la memoria, sin embargo cada uno (el host y el device) tiene su propio espacio de memoria, las cuales son independientes.

Para resolver un problema en la GPU, se necesita transferir los datos de entrada del programa a la GPU y una vez obtenidos los resultados, transferir los a la CPU.

CUDA proporciona funciones para realizar estas tareas las cuales se muestran a continuación:

Listado 1: Directivas CUDA para la transferencia entre el host y el device

```

//Copia la variable dev_a del host al device

Memcpy( dev_a, a, N * sizeof(int), cudaMemcpyHostToDevice);

//Devuelve el resultado desde la GPU a la variable C del host

Memcpy( c, dev_c, N * sizeof(int), cudaMemcpyDeviceToHost);

```

La función **cudaMemcpyHostToDevice** copia de la memoria principal a la memoria del dispositivo y la función **cudaMemcpyDeviceToHost** copia desde la memoria del dispositivo a la memoria principal del host.

Sin embargo para poder realizar las transferencias a memoria es necesario gestionar la memoria global en la GPU, por lo que CUDA proporciona funciones para asignar y liberar espacio de memoria. A continuación se muestran dichas funciones:

Listado 2: Directivas CUDA para la asignación y la liberación de memoria

```

//Reserva memoria en la GPU

cudaMalloc( (void**)&dev_a, N * sizeof(int));

//Libera la memoria reservada de la GPU

cudaFree( dev_a );

```

La función cudaFree, libera el espacio de memoria apuntado por la variable que recibe como parámetro.

Una vez asignada la memoria en el dispositivo a cada uno de los objetos con los que se va trabajar, es necesario transferir los datos desde el host al device.

En CUDA, la función kernel especifica el código a ser ejecutado por todos los hilos en forma paralela en el dispositivo. Como los hilos ejecutan el mismo código sobre distintos conjuntos de datos, el código es un ejemplo del modelo SIMD.

#### 2.4 OPENMP

La API OpenMP fue desarrollada para permitir la programación paralela de memoria compartida portátil. Su objetivo es apoyar la paralelización de aplicaciones en varias disciplinas. Además, sus creadores intentaron proporcionar un enfoque que fue relativamente fácil de aprender y aplicar. También se consideró permitir a los programadores trabajar con un único código fuente es decir un único conjunto de

archivos fuente que contiene el código para las versiones secuencial y paralela de un programa, por lo que el mantenimiento del programa se simplifica mucho.

OpenMP está compuesto de tres elementos:

- Directivas de compilación.

- Rutinas de librería.

- Variables de entorno.

Estos objetivos han contribuido en gran medida a darle a la API de OpenMP su forma actual.

OpenMP se basa en un gran cuerpo de trabajo que admite la especificación de programas para su ejecución por una colección de hilos que cooperan entre sí. El sistema operativo crea un proceso para ejecutar un programa y asigna recursos a ese proceso, incluidas páginas de memoria y registros para almacenar valores de objetos. Si varios hilos colaboran para ejecutar un programa, compartirán los recursos, incluido el espacio de direcciones.

Los hilos individuales necesitan solo unos pocos recursos propios: un contador de programa y un área en la memoria para guardar las variables que son específicas para él (incluidos los registros y una pila). Se pueden ejecutar múltiples hilos en un solo procesador o núcleo y se pueden intercalar a través de multihilado simultáneo (multithreading).

Algunas ventajas de OpenMP son las siguientes:

- Estandarización: Proporciona un estándar entre la variedad de arquitecturas de memoria compartida.

- Es claro y directo: Establece un conjunto de simples y limitadas directivas para equipos donde se puede utilizar memoria compartida. Se puede implementar un paralelismo significativo utilizando solo tres o cuatro directivas.

- Fácil de usar: Proporciona la capacidad de poner en paralelo de forma incremental un programa secuencial, a diferencia de librerías de paso de mensajes que requieren de un enfoque de todo o nada. Proporciona la capacidad de implementar paralelismo con granularidad gruesa y granularidad fina.

- Portabilidad: Es compatible con C/C++ y Fortran. Puede ser utilizada en sistemas operativos como Windows, Unix y Linux.

#### 2.5 MODELO DE PROGRAMACIÓN OPENMP

Así como existen diferentes clases de hardware paralelo también existen diferentes modelos para la programación paralela. OpenMP se centra en el modelo de memoria compartida (o espacio de direcciones compartido) como modelo de programación. Este modelo como su nombre lo indica asume que los programas serán ejecutados en más de un procesador donde compartirán la memoria del equipo (Chapman Barbara, 2008).

OpenMP se basa en directivas: el paralelismo se especifica a través de directivas que se insertan el código.

Los hilos individuales necesitan solo un par de recursos para sí mismos: un contador de programa y un área en memoria para salvar variables que son específicos para el hilo incluyendo registros y una pila. Múltiples hilos se pueden ejecutar en un solo procesador o núcleo a través de cambio de contexto que puede intercalarse mediante multihilado simultaneo.

Los hilos se ejecutan simultáneamente en varios procesadores o núcleos que pueden trabajar concurrentemente para ejecutar un programa en paralelo. Programas multihilados pueden ser escritos de diferentes maneras algunas de las cuales permiten interacciones complejas entre hilos.

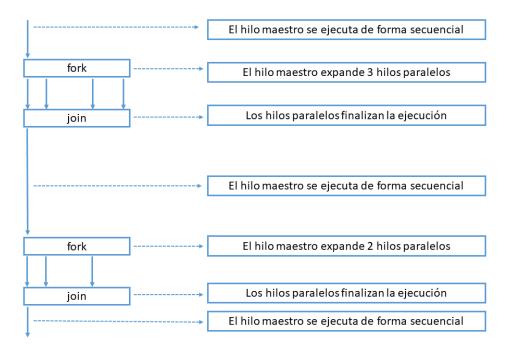

OpenMP intenta facilitar la programación y ayudar al usuario a evitar una serie de problemas potenciales de programación ofreciendo un enfoque estructurado para la programación multihilo. OpenMP es compatible con el modelo de programación "fork-join", como se muestra en la Figura 2.5.

Bajo este enfoque el programa comienza con un único hilo de ejecución. El hilo que ejecuta este código se le conoce como hilo maestro. Cada vez que un constructor paralelo de OpenMP se encuentra con un hilo mientras se está ejecutando el programa, se crea un conjunto de hilos (el "fork") y se convierte en el hilo maestro del conjunto de hilos y colabora con los demás hilos del conjunto para ejecutar el código dinámicamente encapsulando al constructor.

Al final del código del constructor, solo el hilo original o el hilo maestro del conjunto de hilos continua y los demás finalizan (el "join"). Cada parte del código encapsulado por el constructor paralelo es llamada región paralela.

El trabajo de la implementación de OpenMP en un código es separar las secciones de bajo nivel y crear hilos independientes para ejecutar el código y asignarles trabajo, esto dependiendo de la estrategia que sea requerida.

Figura 2.5: Modelo fork-join de memoria compartida.

# 2.5.1 Características de OpenMP

OpenMP comprende un conjunto de directivas de compilación, rutinas de biblioteca de tiempo de ejecución, y las variables de entorno para especificar el paralelismo de memoria compartida en los lenguajes FORTRAN y C/C++.

OpenMP es comúnmente utilizado para incrementar la paralización en un código secuencial existente, y esta tarea se logra mediante la creación de regiones paralelas. Para lograr esto, se especifica la región paralela insertando una directiva antes del código que se va a ejecutar en paralelo para indicarle al compilador que deberá a empezar a ejecutar la sección en paralelo.

Una directiva en OpenMP es una instrucción con un formato especial utilizando la palabra "#PRAGMA" que se aplica generalmente a una parte del código seguido por el código secuencial.

Una rutina o una directiva de OpenMP afectan solo a aquellos que se encuentran contenidas en estas. Muchas de las directivas se aplican a un bloque estructurado del código y una sentencia ejecutable en C/C++, puede ser un conjunto de declaraciones con una sola entrada y una sola salida. En otras palabras, el programa no puede ramificarse adentro o afuera de los bloques del código asociados con las directivas. El final del bloque es explícito en C/C++, solo el comienzo debe ser marcado.

OpenMP proporciona los medios para que el programador pueda:

- Crear grupos de hilos para la ejecución paralela.

- Especificar como repartir el trabajo entre el grupo de hilos.

- Declarar variables compartidas y privadas.

- Sincronizar los hilos y habilitarlos para poder ejecutar solo ciertas operaciones (es decir, sin la interferencia de los otros hilos).

Al final de la región paralela existe una barrera implícita de sincronización: esto significa que ningún hilo puede avanzar hasta que todos los otros hilos en el grupo han alcanzado ese punto del programa. Posteriormente, la ejecución del programa continúa con el hilo o los hilos que existían previamente.

Si un conjunto de hilos ejecutan una región paralela y se encuentra con otra directiva paralela, cada hilo en el conjunto actual crea un conjunto de nuevos hilos y se convierten en hilos maestros de cada nuevo conjunto. La anidación permite la realización de programas paralelos de varios niveles.

Las directivas OpenMP siguen las convenciones de los estándares para directivas de compilación en C/C++, son case sensitive, solo puede especificarse un nombre de directiva por directiva y cada directiva se aplica, al menos, a la sentencia que la sigue. que puede ser un bloque estructurado. En directivas largas puede continuarse en la siguiente línea haciendo uso del carácter al final de la línea.

A continuación se muestra como se construyen regiones paralelas en OpenMP.

Listado 3: Directivas en OpenMP

```

//Inicio de region paralela

#pragma omp parallel private(identificador)

{

//Obtiene el numero identificador de cada hilo

identificador = omp_get_thread_num();

//Obtiene el numero de hilos que se levantaron

nhilos = omp_get_num_threads();

//fin de region paralela

```

Existen clausulas en las directivas que permiten dirigir el comportamiento de la directiva. En particular, pueden utilizarse para especificar paralelizaciones condicionales, especificar el grado de concurrencia (número de hilos) e incluyen mecanismos para la gestión de los datos. Algunas de las cláusulas aplicables a directivas OpenMP son:

- Paralelización condicionada: Sólo puede utilizarse una clausula if en una directiva paralela.

- Grado de concurrencia: Clausulas como num\_threads, nowait, ordered.

- Gestión de datos: Dentro de esta categoría se tienen directivas como private, firstprovate, lastprivate, copyin entre otras.

El estándar OpenMP define una API para llamadas a funciones de librería. Así, encontramos funciones para averiguar el número de hilos y procesos, y para establecer el número de hilos a utilizar, funciones de propósito general que permiten la creación y gestión de semáforos, funciones para la temporización y medición de tiempos, y funciones para paralelismo anidado y para la gestión dinámica de hilos. Algunas de las funciones se mencionan a continuación:

- void omp\_set\_num\_threads: Establece el número de hilos a utilizar en las siguientes regiones paralelas.