## UNIVERSIDAD NACIONAL AUTÓNOMA DE MÉXICO

# **FACULTAD DE INGENIERÍA**

# "MULTIPLICADORES DE FRECUENCIA BASADOS EN TRANSISTORES TIPO FET"

T E S I S

QUE PARA OBTENER EL GRADO D E

MAESTRÍ EN TELECOMUNICACIONES (Ingeniena

Electrica) P R E S E N T A :

ING. ADELA WINGARTZ PLATA

ASESOR: DR. OLEXANDER MARTINYUK

MÉXICO, D.F.

2005

m. 342205

UNAM – Dirección General de Bibliotecas Tesis Digitales Restricciones de uso

## DERECHOS RESERVADOS © PROHIBIDA SU REPRODUCCIÓN TOTAL O PARCIAL

Todo el material contenido en esta tesis esta protegido por la Ley Federal del Derecho de Autor (LFDA) de los Estados Unidos Mexicanos (México).

El uso de imágenes, fragmentos de videos, y demás material que sea objeto de protección de los derechos de autor, será exclusivamente para fines educativos e informativos y deberá citar la fuente donde la obtuvo mencionando el autor o autores. Cualquier uso distinto como el lucro, reproducción, edición o modificación, será perseguido y sancionado por el respectivo titular de los Derechos de Autor.

Índice

| Índice                                                                                                       | no.         |

|--------------------------------------------------------------------------------------------------------------|-------------|

| Introducción                                                                                                 | Pagina<br>1 |

| Objetivos                                                                                                    | 3           |

| Principio de operación de un doblador de frecuencias en base a un transistor FET y modelos de funcionamiento | 4           |

| 1.1. Principales componentes de multiplicadores de frecuencia.                                               | 5           |

| 1.2. Dobladores de frecuencia en base a transistores                                                         | 6           |

| 1.3. Modelos del funcionamiento de los transistores tipo FET                                                 | 12          |

| 1.4 Principio de operación de un doblador de frecuencias en base a un transistor FET                         | 22          |

| 2- Estudio de circuitos de microondas utilizados en el manejo de las señales en el doblador de frecuencias   | 30          |

| 2.1- Intermodulación                                                                                         | 31          |

| 2.2- Arreglo del circuito como doblador balanceado                                                           | 32          |

| 2.3- Análisis de las señales en el doblador balanceado                                                       | 35          |

| 2.4- Circuito doblador de frecuencia con un elemento híbrido                                                 | 37          |

| 3 Diseño de un doblador de frecuencias                                                                       | 40          |

| 3.1- Datos técnicos del transistor tipo HEMT modelo ATF-36077                                                | 41          |

| 4 Arreglos del doblador de frecuencias                                                                       | 56          |

| 4.1- Arreglo con divisor resistivo                                                                           | 56          |

| 4.2 Dispositivo híbrido ideal a la entrada del arreglo                                                       | 65          |

| 4.3 Anillo hibrido                                                                                           | 69          |

| 4.3.1 Análisis de las señales en el anillo híbrido                                                           | 69          |

| 4.4 Arreglo de doblador de frecuencia con dos anillos híbridos                                               | 81          |

| 4.4.1. Cambio en las dimensiones del segundo anillo                                                          | 87          |

| <ol> <li>4.5 Arreglo de doblador de frecuencias con transformadores de cuarto de<br/>onda</li> </ol>         | 91          |

| <ol> <li>Arreglo de doblador de frecuencias con un divisor de Wilkinson a la<br/>salida</li> </ol>           | 96          |

| Conclusiones generales                                                                                       | 105         |

| Referencias                                                                                                  | 107         |

## MULTIPLICADORES DE FRECUENCIA BASADOS EN TRANSISTORES TIPO FET.

## INTRODUCCIÓN

En sistemas de telecomunicaciones, las señales de microondas se generan básicamente mediante la multiplicación de frecuencias en sistemas de un solo chip o bien de módulo multichip (MCM). Los multiplicadores de frecuencia se utilizan ampliamente en aplicaciones de microondas con el fin de extender el límite superior de frecuencia de los osciladores variables o fijos en sistemas de comunicación. Los osciladores locales se utilizan básicamente en aplicaciones como estudios atmosféricos y de radio astronomía, así como en un gran número de sistemas de comunicaciones de radar, civiles y militares.

Las señales en frecuencias de microondas se obtienen mediante osciladores de microondas y multiplicadores de frecuencias, que también se emplean en un gran número de sistemas de comunicaciones. Actualmente, se investigan diseños de arreglos que permitan extender el límite superior de las frecuencias en los dispositivos que se utilizan para diferentes aplicaciones de microondas [3]-[8].

Tanto el mezclador como el multiplicador de frecuencias son elementos con los que se cuenta desde hace bastante tiempo, no obstante continúan las investigaciones respecto a su desempeño en arreglos de circuitos multiplicadores de frecuencias a fin de mejorar sus diseños, buscando nuevos recursos y arreglos, aumentando su eficiencia y aplicaciones [3].

Los resultados de experimentos registrados en publicaciones de los últimos años, nos ayudan a tener una visión más amplia de las posibilidades que ofrecen dispositivos, materiales, modelos matemáticos y nuevas tecnologías para encontrar el aprovechamiento de estos recursos en mejoras de los diseños y fabricación de dispositivos multiplicadores para distintas aplicaciones [7].

El presente trabajo inicia explicando las construcciones básicas y usos de diferentes componentes (diodos y transistores que se construyen en base en el material de Galio Arsénico, GaAs) como base para diseñar dobladores [2]. Dobladores y mezcladores de frecuencia tienen el mismo principio de operación, por eso se da una descripción del principio de funcionamiento de los circuitos mezcladores y multiplicadores que trabajan con transistores tipo FET, mencionando las ventajas que ofrecen. Se explica también el uso de componentes híbridos, para circuitos de microondas, obteniendo un arreglo de doblador balanceado consiguiendo la supresión de respuestas no deseadas en la señal de salida. En el Capítulo I de este trabajo se hace una revisión de los diferentes tipos de mezcladores, para

encontrar un arreglo de elementos prácticos y de uso general en la creación de un multiplicador de frecuencias, así como una investigación y descripción de varios métodos del diseño de dobladores de frecuencia.

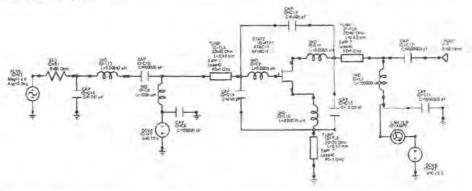

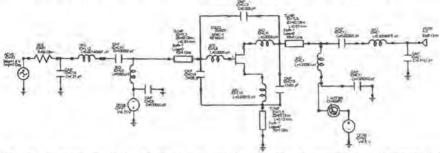

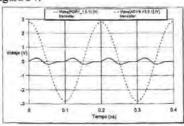

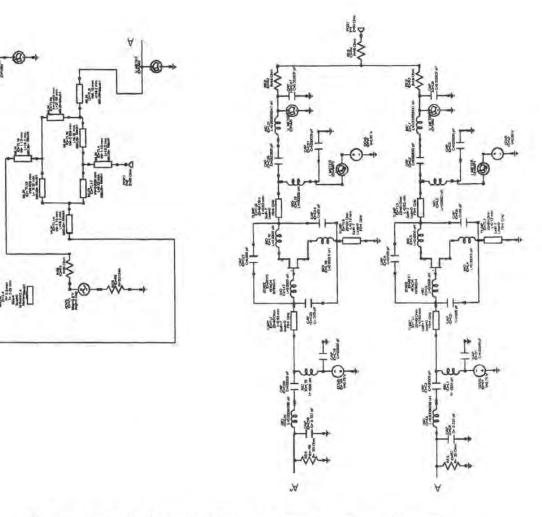

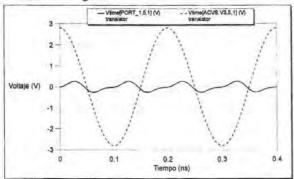

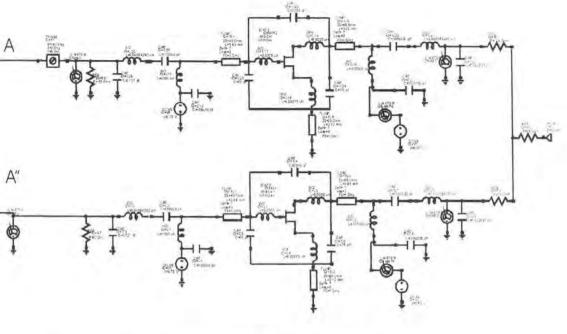

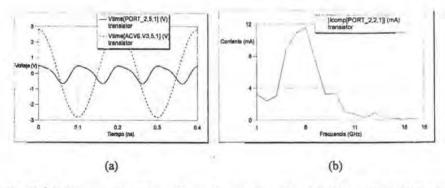

Diseñamos un arreglo de doblador de frecuencias, en el cual mediante un circuito híbrido de 180°, se divide la señal de entrada y se asegura la supresión de armónicas y frecuencias reflejadas, con señales producto de la división, completamente aisladas y defasadas entre sí en 180°. Cada división de la señal a la entrada, alimenta un multiplicador de frecuencias formado por un transistor tipo HEMT, con polarización óptima para obtener el mayor valor de 2ª, armónica en su respuesta, con circuitos de acoplamiento.

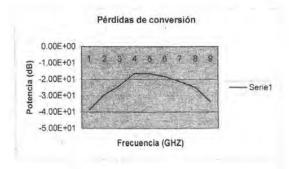

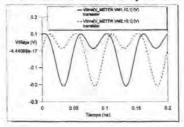

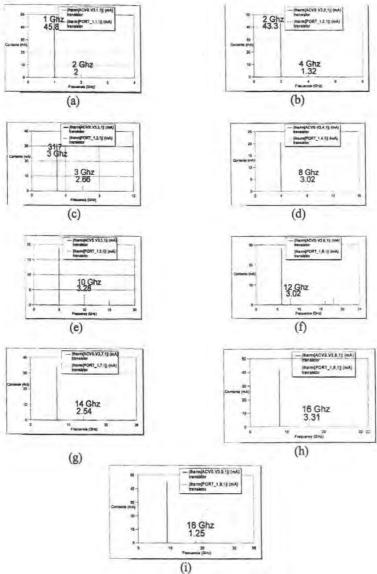

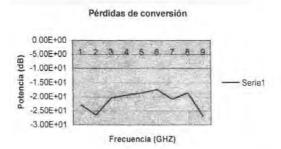

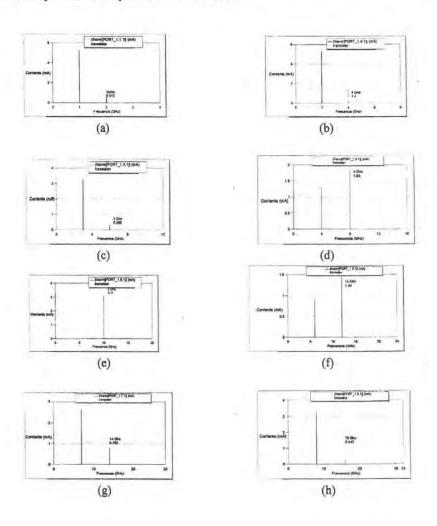

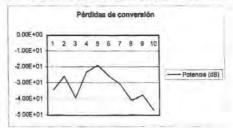

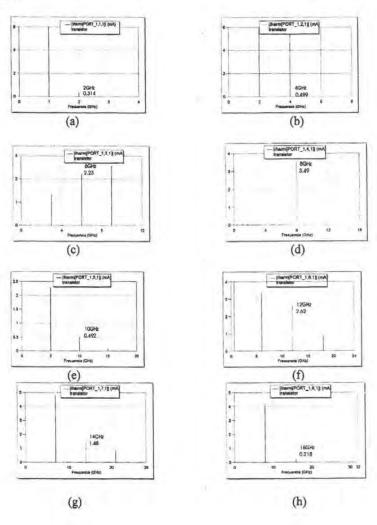

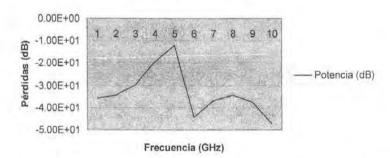

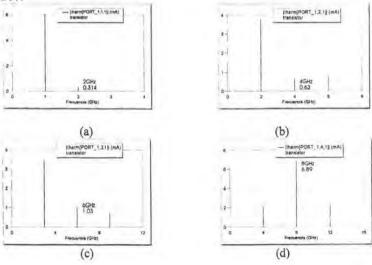

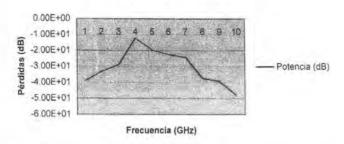

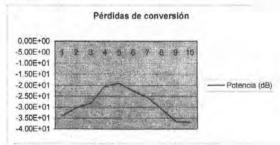

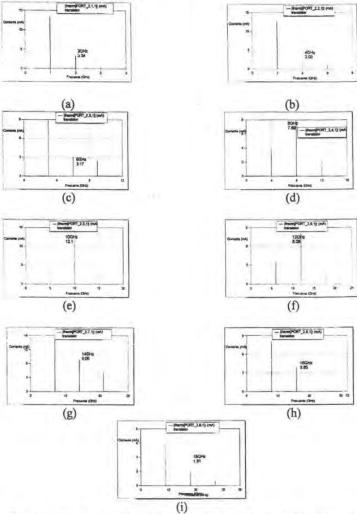

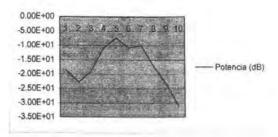

Las señales producto de la multiplicación de frecuencias, al salir de cada arreglo de transistores, se suman en otro acoplador: un divisor de Wilkinson, en donde las componentes de segunda armónica de cada señal se suman constructivamente, obteniéndose una señal de corriente con una frecuencia igual al doble de la de entrada, con valores de pérdidas de conversión mejores a –10 dB en un rango de frecuencias de 4GHz a 7 GHz.

## Objetivos:

- Estudio de los transistores como dobladores de frecuencias.

- Desarrollar un circuito doblador de frecuencias que maneja una banda de frecuencias a la entrada de 5 a 10 GHz.

- Comprobar que nuestra propuesta maneja valores aceptables en las pérdidas de conversión.

## PRINCIPIO DE OPERACIÓN DE UN DOBLADOR DE FRECUENCIAS EN BASE A UN TRANSISTOR FET Y MODELOS DE FUNCIONAMIENTO.

Objetivo: Explicación de los sistemas de telecomunicaciones que usan los dobladores ó multiplicadores de frecuencias, así como las características de los multiplicadores basados tanto en diodos como en transistores. Mostrar el principio de operación de transistores como dobladores, y modelos que lo representan.

En un sistema de comunicaciones de microondas, la potencia del transmisor se aplica a una antena, la cual se diseña para tener las propiedades direccionales apropiadas. El medio en el que se lleva a cabo la propagación entre la antena transmisora y la antena receptora tiene lugar generalmente en la atmósfera. La energía incidente en la antena de recepción se alimenta mediante una línea de transmisión o guía de onda a un receptor. Así como para frecuencias más bajas de radio, los receptores generalmente son del tipo superheterodinos, en los cuales la modulación en la portadora se transfiere a una frecuencia menor o intermedia mediante el proceso de cambio de frecuencia. Esto se lleva a cabo mediante el aumento en frecuencia de la señal recibida con la señal de un oscilador local en un dispositivo no lineal: el mezclador o doblador.

Los osciladores convencionales que se utilizan para generar señales de microondas, funcionan en base a transistores con las configuraciones necesarias. Los dispositivos convencionales tales como triodo de vacío no podrían trabajar en altas frecuencias. Por eso, se desarrollaron dispositivos que utilizan diferentes métodos de generación de microondas, ejemplos de esto son los diferentes dispositivos utilizados en la generación de ondas de altas frecuencias como el klystron, el magnetrón y el tubo de onda viajera.

Finalmente, la modulación se extrae a partir de la señal de frecuencia intermedia en un detector, o demodulador, se puede incluir un amplificador en la frecuencia de la portadora, dependiendo del desarrollo requerido.

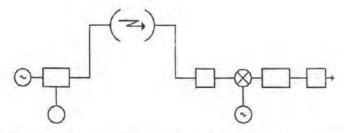

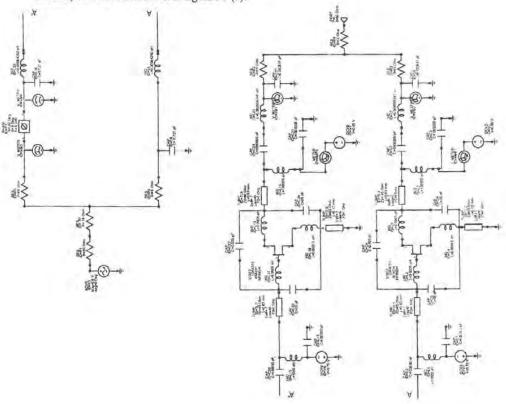

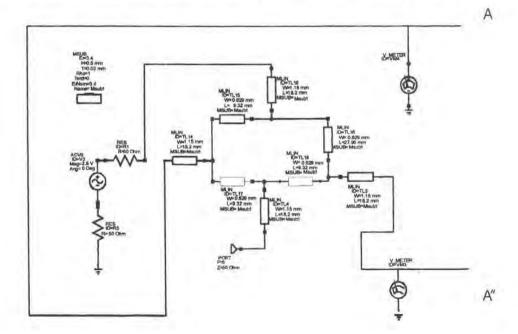

Los elementos más importantes de un sistema de transmisión de microondas se describen en la figura 1;

Figura 1. Un sistema de comunicación en microondas: A, fuente de potencia de RF; B, amplificador; C, fuente de modulación; D, antena transmisora; E, antena receptora; F, amplificador RF; G, doblador; H oscilador local; I, amplificador de frecuencia intermedia; K, demodulador o detector. (Referencia: Telecommunication systems, Pierre Girard Fontollinet, Artech House, 1986, [1], pág. 15).

### I.1 PRINCIPALES COMPONENTES DE MULTIPLICADORES DE FRECUENCIA.

Para elaborar un circuito multiplicador de frecuencias, el dispositivo básico utilizado es el diodo, la construcción de dobladores de frecuencia en base a diodo, aprovecha las características no lineales de corriente-voltaje que ofrecen dichos dispositivos. los cuales producen la multiplicación de armónicas de las señales de microondas. Los diodos del tipo de barrera Schottky pueden trabajar con un rango de frecuencias desde menos de 1 GHz hasta más de 300 GHz. El modelo original del diodo, creado por W. Schottky, se basa en la consideración de que en el análisis de señal grande, el voltaje aplicado (señal L.O.), se utiliza sólo para variar la conductancia y la capacitancia del diodo. De esta forma, la conversión de frecuencias ocurre por medio de los elementos lineales y variantes en el tiempo que se emplean en el análisis de señal pequeña.

Las pérdidas de conversión son la relación que nos indica la potencia aprovechada por el dispositivo mezclador o doblador de frecuencias, así como la potencia necesaria para su funcionamiento. El factor óptimo de potencia disipada en el transistor es de 3 a 6 dBm.

Las pérdidas de conversión son una figura de mérito que necesitamos conocer al trabajar con transistores, nos indica la relación entre la potencia disponible aplicada en la fuente con la potencia entregada a la salida del transistor, como medida de la eficiencia de nuestro dispositivo:

Pérdidas de conversión:

$$L = \frac{Potencia entregada a la salida del dispositivo}{Potencia entregada disponible desde la fuente}$$

(1.1)

En el desarrollo de la investigación acerca del comportamiento del multiplicador de frecuencias, y en los primeros trabajos realizados para entender tanto su funcionamiento.

como sus posibles aplicaciones, se obtuvo una mejor comprensión tanto del su uso como de su diseño. La investigación de la aplicación de los diodos semiconductores como mezcladores de microondas empezó en los MIT Radiation Laboratories como parte del desarrollo del radar, al principio de los años 40, pero fue hasta 1948 cuando se creó el primer arreglo de circuitos del mezclador que utilizaba diodos. Las posteriores mejoras en la fabricación de este tipo de circuitos y la comprensión de su funcionamiento, también aumentaron el rendimiento de este tipo mezcladores. Los primeros trabajos teóricos acerca del comportamiento del diodo, se lograron con métodos numéricos, así como el uso de programas de computadora en los cuales se simula el comportamiento de los dispositivos, con resultados que tienen gran similitud con las mediciones experimentales.

Como ejemplo de trabajos y propuestas recientes en el uso de los diodos como componentes de multiplicadores, puede mencionarse una propuesta de X. Mélique y J. Carbonell [2], que presenta arreglos de diodos, específicamente diodos de heteroestructura HBV's con los que se presentan arreglos de diodos de alta calidad fabricados en base a capas de InP, con señales RF en una amplia banda de frecuencias con ondas de hasta 110 GHz, y usando un arreglo de diodos, alimentado con un alto valor de voltaje de hasta 12V.

Como resultado, actualmente los mezcladores y multiplicadores, en especial los basados en diodos tipo Schottky ya alcanzaron su máximo desarrollo y rendimiento, así como en métodos de fabricación, y tienen aún ventajas importantes, por lo que otras tecnologías, como las del mezclador o multiplicador de frecuencias basado en transistores tipo FET tienen pocas posibilidades de desplazarlos por completo. Sin embargo, éste último tipo de mezcladores se puede utilizar para aplicaciones que trabajan hasta los 50 GHz, obteniéndose una mejor respuesta y figura de ruido del sistema.

#### 1.2 DOBLADORES DE FRECUENCIA EN BASE A TRANSISTORES.

De la misma forma en que las características no lineales de los diodos se utilizan para generar un espectro de salida formado por la suma y la diferencia de frecuencias de dos señales de entrada, generándose el proceso de mezclado o multiplicación de frecuencias, podemos trabajar con dispositivos basados en transistores tipo FET, los cuales también presentan una característica no lineal, que les permite funcionar como mezcladores o multiplicadores, además ofrecen alta ganancia. Los multiplicadores, con aplicación en la generación de microondas, se emplean básicamente en receptores, y se utilizan para extender el límite superior de frecuencia de osciladores variables o fíjos en sistemas de comunicación que también pueden construirse en tecnología MMIC para un gran número de aplicaciones.

Así como se aprovecha la característica exponencial de la relación entre el voltaje aplicado y la corriente de salida en los diodos para aplicaciones en multiplicadores, para generar efectivamente las armónicas, también se utiliza la opción de los transistores MESFET construidos de galio arsénico (GaAs), para circuitos multiplicadores de frecuencia, por que la relación cuadrática que existe entre el voltaje de la compuerta (o gate) y la corriente de drenaje (drain) de un MESFET ideal presenta una característica importante para su uso como doblador de frecuencia.

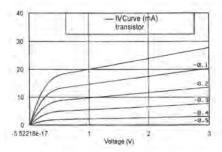

El análisis teórico de las propiedades de las señales en el caso del mezclador basado en el MESFET de GaAs, muestra que a partir de los parámetros del circuito equivalente del transistor, el dispositivo genera el mezclado de frecuencias cuando se varían los elementos de señal pequeña mediante una señal de oscilador local, aplicada generalmente en las terminales de compuerta y fuente. La transconductancia del transistor, como función del potencial entre la compuerta y la fuente de Vgg, para un valor del voltaje entre el drenaje y la fuente de Vdd, tiene un máximo sobre la curva característica I-V del transistor, por lo cual el transistor se polariza para los voltajes en los que se presente este valor máximo de transconductancia.

Los multiplicadores de frecuencia basados en el FET (Field Effect Transistor, en inglés, o Transistor de efecto de campo), en especial los fabricados con material de silicio, se han utilizado en receptores desde los años sesenta, pero sólo hasta épocas recientes se han tomado en cuenta los multiplicadores de FET fabricados en GaAs. Los primeros arreglos que los incluían operaban en UHF y se obtenían ganancias de conversión, pero con valores de figuras de ruido que necesitaban mejorarse, como muestran los resultados de las primeras investigaciones [3], donde los circuitos de mezcladores de frecuencias con FET de GaAs, se alimentan con señales de entrada de 3 GHz.

Con el uso de transistores tipo FET en mezcladores y multiplicadores de frecuencias, se obtienen varias ventajas en comparación con los que trabajan con diodos, tales como menor ruido e intermodulación, una menor potencia de entrada LO. Además, se presenta la posibilidad de realizar ganancia de conversión en lugar de pérdidas de conversión. Un receptor que usa un mezclador de FET necesita menos pasos de amplificación y de filtración para su funcionamiento. Los mezcladores basados en FET en la práctica, generalmente tienen una pérdida de conversión de entre 4 y 7 dB. Además, las pérdidas de conversión en un mezclador FET dependen de la potencia de la señal OL. y los valores mínimos de las pérdidas de conversión generalmente ocurren para potencias de LO entre 0 y 10 dBm. Los primeros estudios de circuitos del uso de los FET como mezcladores "upconverter", muestran que es posible obtener una ganancia de conversión total de hasta 3.5 dB en la conversión de 70 MHz a 6GHz [4].

Debido a que los diodos, como elementos de circuitos de microondas, además tienen buena respuesta para usos en circuitos de mezcladores y multiplicadores balanceados y son más económicos, el uso de mezcladores de FET por parte de diseñadores e investigadores tardó algunos años en llevarse a cabo. Sin embargo, por los bajos níveles de distorsión y alta estabilidad, obtenidos en mezcladores de FET, así como de una ganancia mucho mayor, se considera cada vez más el uso de este tipo de dispositivos tanto en mezcladores como en multiplicadores, con el desarrollo de los FET's de alto desempeño.

Para frecuencias cercanas a 1 GHz, el transistor de tipo MESFET es la opción que ofrece las mismas ventajas que el de tipo FET presenta a menores frecuencias. El transistor tipo MESFET, es un transistor tipo JFET que utiliza en su fabricación galio arsénico y una compuerta de unión tipo Schottky, que puede trabajar en la región de frecuencias de microondas. El transistor tipo MESFET, debido a su mayor movilidad de electrones, comparado con el que se obtiene en el material de silicio, se usa en el diseño de circuitos integrados de microondas tales como mezcladores y multiplicadores debido a que trabaja con un alto rendimiento, mayor ganancia, y potencia de salida para frecuencias del orden de hasta 50 GHz. Los MESFET presentan también una mayor velocidad de saturación de los electrones, y menor figura de ruído en amplificadores, debido a la alta movilidad que los electrones logran en el material de GaAs. Dicha situación se presenta también en mezcladores de doble compuerta, los cuales, tienen una compuerta para la señal LO y la otra para la entrada RF, con un buen aislamiento entre ambas señales de entrada, para su uso como mezcladores.

Los mezcladores de frecuencias pueden trabajar como multiplicadores cuando se maneja la señal de oscilador local (LO) igual a la de RF; basados en MESFET de GaAs, presentan mayor ganancia y potencia de salida. Aunque son componentes electrónicos de microondas que no se utilizan comúnmente, tienen importantes ventajas sobre otras tecnologías, porque trabajan en amplios anchos de banda con ganancias de conversión mayores a la unidad. En comparación con los MESFET, se obtienen multiplicadores de alta frecuencia. Para arreglos en los que se utilizan cadenas de multiplicadores de diodo, frecuentemente se necesitan amplificadores de alta ganancia y potencia, los cuales consumen más energía que el resto del receptor, por lo cual los multiplicadores basados en MESFETs son una opción eficiente y de bajo consumo.

La estructura del MESFET de GaAs, tiene una longitud en dirección del flujo de electrones de hasta 0.25µm para dispositivos de telecomunicaciones. Debido a la alta movilidad de los electrones que se puede lograr en el canal de GaAs, y mayor velocidad de saturación en el

canal corto del dispositivo, el tiempo de tránsito del electrón en el canal es del orden de algunos picosegundos.

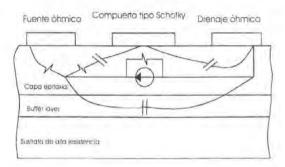

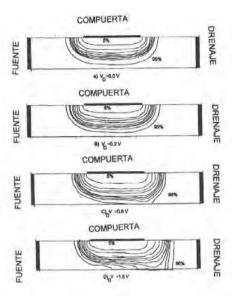

La figura 2 muestra una sección transversal de un MESFET. El canal es una capa epitaxial moderadamente dopada, creada sobre un sustrato sin dopar. Al aplicar un voltaje de a ambos extremos del canal, se crea un campo eléctrico longitudinal. En operación normal, el campo longitudinal aumenta hasta un valor que acelera los electrones a su velocidad de saturación, creando una corriente desde la fuente al drenaje. La compuerta (gate) crea, mediante el voltaje de alimentación, una región empobrecida en portadores de carga que se extiende en parte del canal, y mediante la aplicación de una variación en el voltaje de la compuerta a fuente (o source), aumenta el espesor de esa región, y consecuentemente, se reduce el ancho del canal de conducción, así como la corriente del mismo.

Fig. 2.- Corte transversal de la estructura del FET y su relación con el circuito equivalente. (Referencia: S Maas, Mixers. Notwood, MA: Artech House, 1988, pág. 65).

En el caso del MESFET de GaAs, su operación se caracteriza por la alta velocidad de saturación los electrones. En este material se alcanzan grandes velocidades en los electrones, trabajando con un valor de campo eléctrico relativamente bajo, en comparación con el que se necesita para el caso del FET de silicio. Debido a estas condiciones, los electrones pueden moverse a una velocidad de saturación a través de la mayor parte del canal. Obteniéndose tiempo de tránsito muy corto, y una alta capacidad de respuesta en frecuencia. A diferencia del caso que se presenta en los JFET de silicio, la condición de saturación de corriente no se presenta porque el canal se "obstruya", sino porque ya no se puede aumentar aún más el valor de la caída del voltaje en el canal.

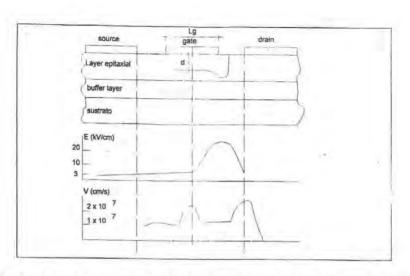

En la figura 3 se muestra cómo es la formación de la capa del dipolo, que se concentra debajo de la salida de la compuerta. Para voltajes muy bajos de drenaje-fuente (drainsource), menores a 0.2-0.3 V, los electrones en el canal se mueven a una velocidad proporcional a la magnitud del campo eléctrico, el cual es proporcional al voltaje drenaje-

fuente. La corriente es proporcional al grosor del canal para un voltaje drenaje-fuente, por lo que canal del MESFET funciona como un resistor controlado por el voltaje de la compuerta (gate), en esas condiciones se dice que opera en su región lineal. Cuando el voltaje drenaje-fuente aumenta a mayores valores, el canal va disminuyendo su grosor del lado de la compuerta más cercano al drenaje. Aunque la corriente debe ser la misma a través de todo el canal, la velocidad del electrón cerca del lado del drenaje aumenta, así como el campo eléctrico, debido a que el canal de conducción es más estrecho en ese punto que cerca del lado de la fuente.

Un factor importante en la determinación de la corriente, es el número de electrones móviles, así como la velocidad a lo largo del canal, debida al efecto de la saturación de la velocidad en los electrones del lado del drenaje,  $v=\mu E$ , donde  $\mu$  es la movilidad para el material y el campo dados, y E es el campo eléctrico suministrado.

Se obtiene la gráfica de la velocidad de los electrones que muestra que cerca de la fuente, el decremento en el número de electrones móviles en la región de saturación es pequeño. Debido a la relación lineal entre el campo eléctrico y la velocidad, la modulación del espesor del canal da como resultado un pequeño incremento en la corriente. Cerca del drenaje, donde el ancho del canal es más angosto, la velocidad se satura, y cuando el voltaje de drenaje a fuente llega a un valor suficientemente alto, los electrones llegan a su velocidad de saturación en el lado del drenaje.

Los electrones víajan a una velocidad de saturación, con lo que la densidad de carga aumenta, entonces se forma una región de acumulación de electrones, con densidad de carga neta negativa. Entre la parte más angosta del canal y el contacto del drenaje, los electrones permanecen a una velocidad de saturación, pero entonces, el canal se abre abruptamente, resultando en una reducción de electrones y una carga positiva neta, debida a los átomos donadores ionizados que se encuentra en el otro lado del punto en el que se reduce al máximo el canal de conducción.

Por eso, se presenta el efecto de dispersión de los electrones debido a los átomos de dopaje, por lo que los electrones alcanzan una velocidad de saturación.

Fig. 3.- Campo eléctrico y velocidad de los electrones en el canal de conducción del transistor (Referencia: S Maas, Mixers. Notwood, MA: Artech House, 1988, pág. 61).

Para aprovechar las características del MESFET en distintos arreglos y circuitos, se necesita una descripción cuantitativa de su operación, mediante un modelo, que incluya tanto las no linealidades del FET, que son las que ocasionan el fenómeno del mezclado o doblado de frecuencias, al igual que sus características lineales, en un circuito equivalente con una combinación de ambos tipos de elementos: lineales y no lineales. El análisis teórico del MESFET, en el que se representa el circuito equivalente, así como un circuito en el que se representan las señales que intervienen en su funcionamiento, y sus respectivas frecuencias (señal L.O., imagen y señal de salida).

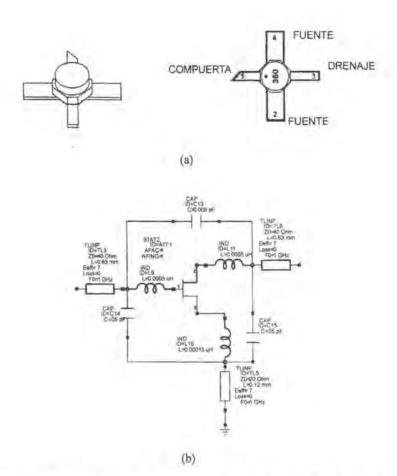

Otro tipo de construcción de transistor que podemos considerar, es el HEMT (High Electron Mobility Transistor, sus iniciales en inglés), el cual es básicamente un MESFET fabricado sobre un material de heterounión (AlGaAs sin dopar), entre otras dos capas de GaAs que presenta mayor movilidad de electrones y consecuentemente, aún mayor velocidad de saturación que en la opción de GaAs, aumentando la ganancia y reduciendo la figura de ruido. Presenta otra opción en los elementos que pueden utilizarse en mezcladores o dobladores de frecuencia.

Las características que presentan los HEMT, (mayor movilidad y mayor velocidad de saturación de los electrones) se deben a que no funciona en base a GaAs dopado que dispersa a los electrones, por lo que alcanzan una alta velocidad a través de todo el material. La movilidad del electrón se incrementa aún más a bajas temperaturas consiguiéndose niveles de temperaturas de ruido muy bajos.

El circuito equivalente de los transistores HEMT es casi igual al del MESFET de GaAs, aunque la curva característica I/V que representa al HEMT en el drain es con una pendiente menor, lo cual significa que la resistencia de drenaje a fuente es por lo general menor que en el MESFET. La transconductancia de un HEMT aumenta muy rápidamente con el voltaje de la compuerta, por lo que el dispositivo tiene un comportamiento más "no lineal" que el MESFET de GaAs. Por lo tanto, también se necesita de una potencia relativamente baja en LO para obtener buenos valores de pérdidas de conversión. Debido a que la capa de conducción es más delgada en los HEMT, se crea un menor número de electrones por unidad de área en el canal de conducción. Para corregir esta característica, se hacen construcciones que utilizan múltiples capas de heteronuniones con las que pueden conseguirse buenos niveles de corriente y de potencia para alta frecuencia.

Debido a que la variación de la transconductancia en el tiempo es la principal contribución a la acción del mezclador o doblador de frecuencias, se busca aumentar el rango de frecuencias en las que se presenta dicha variación. Se busca maximizar este rango de frecuencias y conseguir que permanezca constante en la región de corriente de saturación para todo el ciclo de la señal aplicada LO. Para eso, se polariza el transistor a un valor cercano al voltaje de corte. Además, es necesario corto circuitar el drenaje, tanto para la frecuencia fundamental LO, como para todas sus armónicas, evitando de esta forma variaciones en el voltaje aplicado a la capacitancia de compuerta a drenaje, obteniendo una mayor estabilidad en el multiplicador.

El HEMT presenta un alto valor de transconductancia, por lo que es capaz tanto de amplificar como de multiplicar frecuencias. Por lo tanto, el mezclador o multiplicador no debe presentar una ganancia lineal en la frecuencia de la señal de entrada, porque pueden aparecer componentes de la señal aplicada, (no deseadas) en la salida. Las componentes de la señal aplicada se pueden suprimir por medio del acoplamiento, por lo que el circuito de acoplamiento en la salida se calcula para la señal de frecuencia IF.

#### 1.3 MODELOS DEL FUNCIONAMIENTO DE LOS TRANSISTORES TIPO FET.

Para lograr un modelo básico que explique el funcionamiento del FET, que obtenga los parámetros de la señal pequeña: la conductancia del drenaje g<sub>d</sub>, la transcondutancia g<sub>m</sub> y la capacitancia C<sub>gs</sub>, se deben tomar en cuenta las condiciones de flujo de corriente que se presentan para distintos valores de voltaje. El campo eléctrico necesario para obtener la

saturación de la velocidad de electrones, es aproximadamente de 3X10<sup>3</sup> V/cm en el material de GaAs.

Existe un análisis numérico bidimensional [5], que utiliza ecuaciones básicas para obtener la distribución de los electrones en el canal de conducción de un transistor, con el fin de encontrar una expresión con los elementos de su circuito equivalente que nos represente su comportamiento.

En el análisis se utiliza la ecuación de Poisson y la ecuación de la continuidad de corriente, para proponer un modelo de la conductancia del drenaje, que describa las características de corriente-voltaje del dispositivo. El análisis numérico bidimensional en el que se resuelven simultáneamente ambas ecuaciones obtiene una imagen eficiente de su operación.

Del análisis necesitamos obtener principalmente la distribución de la corriente, la longitud del canal, el número total de portadores de carga en la vecindad del drenaje, que decrece al incrementarse el voltaje en el mismo, por lo que la única forma de incrementar la corriente del drenaje, es a través del vector de velocidad, de manera que aumente su componente en dirección del eje x (dirección fuente a drenaje).

Se puede proponer un modelo para el J-FET, conociendo el cambio gradual de la concentración de electrones, en la capa de material en donde se lleva a cabo su movimiento. La ecuación de Poisson se resuelve en función de la distribución aproximada de electrones. El vector velocidad de los electrones, incluyendo el efecto de la velocidad de saturación, se calcula para la distribución del potencial en el canal de conducción, que se obtiene como solución a la ecuación de Poisson. Las características de voltaje y corriente se calculan a partir de un análisis bidimensional. Con este análisis podemos obtener, los parámetros de señal pequeña: gd, conductancia del drenaje, gm, transconductancia, y Cgs, capacitancia entre la compuerta y la fuente.

Fig. 4.- Diagrama del transistor analizado.

Fig. 5.- Contornos de la distribución de la densidad de electrones, con un voltaje de polarización =0 V (Referencia: Drain conductance on FETs, [4] pág. 547).

Si tenemos un modelo esquemático del FET como el que se muestra en la figura 4, podemos iniciar su análisis bidimensional, a partir de las ecuaciones básicas de Poisson y de la continuidad en la corriente, para describir el movimiento de los electrones, en la operación del transistor, mediante ecuaciones diferenciales en derivadas parciales, las cuales son:

$$\nabla^2 \psi = -\frac{q}{\varepsilon} (N_D - n) \tag{1.2}$$

$$q\frac{\partial n}{\partial t} = \nabla \cdot \mathbf{J} \tag{1.3}$$

$$\mathbf{J} = qn\mathbf{v} + qD\nabla n \tag{1.4}$$

$$\mathbf{J}_{tot} = \mathbf{J} + \varepsilon \frac{\partial E}{\partial t}$$

(1.5)

### Donde:

| Ψ           | Potencial                                 |

|-------------|-------------------------------------------|

| n           | Densidad de electrones                    |

| ε           | Constante dieléctrica                     |

| E           | Campo eléctrico                           |

| V           | Velocidad                                 |

| q           | Carga eléctrica                           |

| ND          | Concentración de donadores en el material |

| J           | Densidad de corriente                     |

| $J_{tot}$   | Densidad de corriente total               |

| γ           | Índice de deformación o doblamiento       |

| α           | Posición del punto de corte               |

| D           | Coeficiente de difusión                   |

| a           | Espesor del canal                         |

| $\lambda_D$ | Longitud de Debye                         |

| Vbi         | Potencial acumulado                       |

| VG          | Voltaje en la compuerta                   |

Para tener un modelo de la distribución de electrones en el canal de conducción, podemos conocer el cambio de la distribución a través del mismo, mediante una aproximación senoidal del contorno del canal de conducción, conociendo también la modulación de la longitud del canal en la región cercana a la fuente, mediante la distribución de la densidad de los electrones. Y finalmente el cambio en la dirección del vector velocidad en la cercanía del extremo del drenaje, mediante la solución de la ecuación de Poisson, que muestra el cambio en la dirección de la velocidad de los electrones hacia la componente en x.

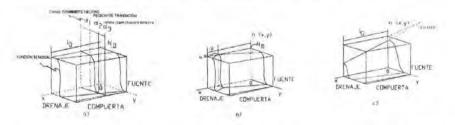

Fig. 6.- Distribución de electrones a) antes del voltaje de corte, b) después del voltaje de corte c)modo de voltaje de corte, (Referencia: Drain conductance on FETs, [5], pág. 549).

Como se muestra en la figura 6, la distribución de electrones en la dirección del eje y se divide en tres regiones: el canal completamente neutro, la región de transición y la región del canal completamente estrecho.

La densidad de la distribución de electrones puede considerarse como una función escalar del campo eléctrico:

Para el canal completamente neutro 0<y<d1(x)

$$n=N_D$$

(1.6)

Para la región de transición, d<sub>1</sub>(x)<y< d<sub>1</sub>(x)+d

$$n = N_{D} \left[ 1 - \alpha (x - \gamma) \right]^{1 + \cos \frac{\pi}{2}} \frac{(y - d_{1}(x))}{2}$$

(1.7)

Para la región completamente obstruida, d<sub>1</sub>(x)+d<y< a

La solución de la ecuación de Poisson se resuelve bajo condiciones dadas de distribución de densidad de electrones, si asumimos la solución, de la forma:

$$\psi = \psi_0 + \psi_1$$

(1.9)

Donde:

ψ<sub>0</sub>= Potencial en x=l<sub>g</sub>

ψ1= Potencial en y=0

Y asumimos las dos componentes de manera que:

$$\nabla^2 \psi_0 = 0$$

(1.10)

$$\nabla^2 \psi_1 = -\frac{q}{\varepsilon} \left\{ N_D - n(x, y) \right\} \quad (1.11)$$

Considerando que la caída de potencial en la región  $lg \propto$ , mostrada en la figura 6, es muy pequeña, el voltaje en el drenaje  $V_D$  se determina mediante el potencial  $\psi_1$  y  $\psi_0$  en x=lg y y=0. Asumiendo que en ese punto  $\psi_1$  y  $\psi_0$  son  $V_0$  y  $V_1$  respectivamente,  $V_D$  está dado por:

$$V_{D} = V_{0} + V_{1} \tag{1.12}$$

La solución a la ecuación de Poisson, nos da el potencial Vp o voltaje de corte, en función de la cantidad de donadores de electrones, en la región de baja densidad, que se extiende, entre el canal y la compuerta en función del potencial  $\psi_1$ .

La apertura en el canal  $d_1(x)$ , que es una función decreciente de x, también se determina por  $\psi_1$ . El voltaje de corte se define en el punto  $d_1(x=lg)=0$ , como solución a la ecuación de Poisson para una distancia dentro del canal  $d_1(x)=g$ 0.

$$V_{p} = \frac{qN_{D}}{2\varepsilon} (a-d)^{2} + \frac{qN_{D}}{2\varepsilon} d(a-d) + \frac{qN_{D}}{2\varepsilon} \left(\frac{1}{2} - \frac{2}{\pi^{2}}\right) d^{2} - (V_{h} + V)_{G}$$

(1.13)

En la región de transición, formada por un exceso de voltaje, de valor mayor a Vg ( $\gamma$ <x<lg) y para 0<y<d, el potencial  $\Psi$ 1 es:

$$\psi_{1} = -\frac{qN_{D}}{4\varepsilon}y^{2} + \frac{qN_{D}}{2\varepsilon}\binom{d}{\pi}^{2}\left(1 - \cos\frac{\pi y}{d}\right) + \frac{qN_{D}}{\varepsilon}\alpha(x - \gamma)\left\{\frac{1}{2}\binom{d}{\pi}^{2}\cos\frac{\pi y}{d} - \frac{y^{2}}{4}\right\} + g(x) \quad (1.14)$$

donde:

$$g(x) = \frac{qN_D}{4\varepsilon} \left( \frac{ad}{2} - \frac{d^2}{4} + \frac{d^2}{2\pi^2} \right) \alpha(x - \gamma) + V_P \quad (1.15)$$

Los parámetros α y γ denotan la relación de la región de baja densidad de electrones y la posición del punto del voltaje de corte, respectivamente, y dependen de la polarización del drenaje.

En la cercania del drenaje,  $\frac{\partial n}{\partial y}$  es una función decreciente de  $\alpha$ , por lo tanto, también en la

componente de y de la corriente de difusión cuando se incrementa  $\alpha$ , por lo que se tiene un decremento en  $v_y$ , componente "y" de la velocidad de los electrones. Ex es una función siempre en incremento de  $V_D$ , la disminución en  $v_y$ , velocidad "y", es un incremento en  $v_x$ , velocidad en "x", aún para la región de velocidad de saturación.

La distribución de potencial queda definida en todo el canal, por lo tanto, se puede calcular el valor de la corriente "I" en el drenaje, a partir de la integración de la densidad de corriente, en donde se puede incorporar tanto el efecto de la velocidad de saturación como el del voltaje de corte.

La corriente se calcula a partir de las distribuciones de densidad de electrones asumidas, y estos parámetros se pueden determinar a partir de  $V_0$  o  $V_1$ . El valor de  $V_0$  debe encontrarse de manera que se satisfaga la continuidad de la corriente.

Fig. 7.- Cambios en la dirección del vector de velocidad para diferentes distancias en el canal de conducción, (Referencia: Drain conductance on FETs, [5]) pág. 548.

La corriente total en el dispositivo se obtiene mediante la integración de la densidad de corriente a lo largo de un plano "P" que rodea los electrodos:

La corriente del drenaje se calcula para ambos extremos del canal, para x=0 y x=lg.

$$I = \int_{P} \mathbf{J}_{\text{tot}} \bullet ds = \int \mathbf{J}_{\text{tot}} dy \quad (1.16)$$

Donde |Jtot| x es la componente en x de Jtot

$$I_{\kappa} = \int_{\tau=0} J_{s} dy \tag{1.17}$$

$$I_{ii} = \int_{y=10}^{y} J_x dy \tag{1.18}$$

### Donde:

Is- Corriente en la fuente I<sub>D</sub>- Corriente en el drenaje

Por lo tanto, Vo se calcula para I<sub>S</sub>=I<sub>D</sub>. La característica de corriente-voltaje es un resultado del procedimiento anterior.

La conductancia gd y la transconductancia gm se obtienen a partir de las características de corriente-voltaje:

$$g_{d} = \begin{pmatrix} \partial I \\ \partial V_{D} \end{pmatrix}_{V_{ij} = cons \tan i\psi}$$

(1.19)

$$g_{m} = \begin{pmatrix} \partial I \\ \partial V_{G} \end{pmatrix}_{D = constante}$$

(1.20)

Por otra parte, la carga total Q por unidad de espesor en el dispositivo está dada por:

$$Q = \iint q(N_n - n)dx dy \quad (1.21)$$

Dado que la distribución de n ya se conoce, la capacitancia de compuerta a fuente  $C_{gs}$  está dada por:

$$C_{ge} = \begin{pmatrix} \partial Q \\ \partial V_G \end{pmatrix}_{1GB = colib \text{ tan } te}$$

(1.22)

Los modelos existentes que representan el comportamiento del transistor FET no han sido del todo exactos. El análisis bidimensional mostrado, representa una manera más exacta de modelar la corriente en el dispositivo, aunque es muy complejo y requiere de mucho tiempo de cálculo de simulación en computadora, por lo que se prefieren otros modelos más prácticos para modelar el funcionamiento del FET.

Para utilizar un dispositivo como el FET en un multiplicador o doblador de frecuencias, se construye primero un modelo que pueda simular el comportamiento del dispositivo. El modelo debe hacer uso de los valores eléctricos medidos en el transistor e interpretarlos mediante fórmulas empíricas aproximadas.

Existen varios análisis que utilizan modelos o circuitos equivalentes, que simulan el comportamiento del dispositivo, y que pueden utilizarse en el diseño de mezcladores, nuestro análisis se basa en el circuito equivalente del FET de señal grande y de señal pequeña que proporcionan un modelo exacto no lineal del transistor de FET, y que pueda simularse en programas de computadora.

La operación del mezclador y del multiplicador dependen básicamente de la variación de la transconductancia, (la primera derivada de la característica I/V del gate). La transconductancia del FET; dI<sub>g</sub>/dV<sub>g</sub>, es la relación que determina la conversión de frecuencias en los mezcladores, con el voltaje de compuerta a fuente (y algunas veces compuerta a drenaje), por lo que es de especial importancia que el modelo anticipe exactamente el comportamiento de dicha transconductancia, para cualquier combinación de voltajes de polarización.

En el modelo aparecen elementos tales como las capacitancias de compuerta a fuente y de compuerta a drenaje entre otros, y aunque no contribuyan de manera importante al proceso de multiplicación o mezclado, es preciso modelarlas con exactitud, debido a que también de su valor promedio depende la magnitud de la impedancia de entrada. En la mayoría de los mezcladores y dobladores activos, la señal LO se aplica a la compuerta, y esta señal de voltaje alterno ocasiona que varíen las capacitancias, mismas que pueden determinarse sólo si la no linealidad capacitiva está bien representada en el modelo.

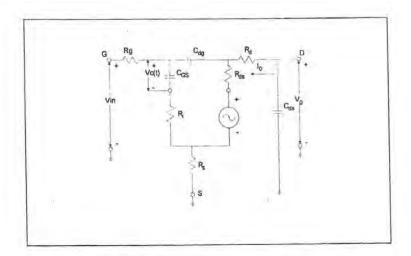

En el caso de los MESFETs de GaAs, sus primeros modelos se desarrollaron para mejorar el entendimiento de la operación de éstos dispositivos, de manera que pudieran aprovecharse en el programa simulador de circuitos SPICE. Las limitaciones de los primeros modelos fueron evidentes, aunque a través de varios trabajos e investigaciones, actualmente se han mejorado. Los modelos más utilizados son los desarrollados por Curtice y Ettenberg, Materka y Kacprak, y el de Statz.

La figura 8 muestra el circuito equivalente no lineal de un MESFET: está formado por cinco elementos no lineales: Cgs, Cgd, Id, y dos diodos (en c.c.), los cuales se controlan por medio de los voltajes, Vg y Vd, o sea, los voltajes internos de compuerta y drenaje, que incluyen las caídas de voltaje a través de las resistencias parásitas Rs y Rd: las resistencias primarias de contactos óhmicos en la fuente y el drenaje respectivamente.

Todos los demás elementos en el circuito equivalente son lineales, tales como la resistencia Rg, que es la resistencia del metal de la compuerta del FET, y Ri, la resistencia de la parte óhmica en la región de estrechamiento del canal de conducción. Los diodos representan la unión de la compuerta, y tienen un pequeño efecto siempre y cuando el voltaje a través de éstos, no exceda su voltaje máximo, de aproximadamente 0.5V: si se excede, los diodos empiezan a conducir y a restringir el voltaje de unión a un valor positivo bajo.

Fig. 8. Circuito equivalente del transistor MESFET de GaAs (Ref.: Performance of GaAs MESFET Mixers at X Band, [6] pág. 351).

Cgs y Cgd son las capacitancias parásitas de compuerta a fuente y de compuerta al drenaje, al igual que las de un diodo Schottky, se definen como capacitancias diferenciales. El cambio de la carga en la región de estrechamiento junto con el voltaje, de manera distinta de como sucede con el diodo, son funciones tanto de Vg, como de Vd:

$$C_{gs}(V_g, V_d) = \frac{\partial Q_d}{\partial V_g}\Big|_{V_d - V_g = cle}$$

(1.23)

$$C_{gd}(V_g, V_d) = \frac{\partial Q_d}{\partial V_g}\Big|_{V_g = cte}$$

(1.24)

Donde Qd es la carga total positiva en la región de estrechamiento.

El otro elemento no lineal en el circuito equivalente del MESFET es Id, la corriente del drain o drenaje, que también es función tanto de Vg como de Vd. La transconductancia =∂I/∂Vg se puede encontrar a partir de:

$$g_{m}(V_{g}, V_{d}) = \frac{\partial I_{d}}{\partial V_{g}}$$

$$V_{d} = cons \tan w$$

(1.25)

La ganancia de conversión se obtiene en función de los parámetros del circuito equivalente [6].

## 1.4 PRINCIPIO DE OPERACIÓN DE UN DOBLADOR DE FRECUENCIAS EN BASE A UN TRANSISTOR FET

Para lograr un circuito que nos dé como resultado un efecto de mezclador o de doblador de frecuencias, que sea capaz de actuar como un interruptor para la frecuencia de la señal LO, y que también sea lineal para evitar la intermodulación, necesitamos modelar el transistor de GaAs tipo FET, en donde se utiliza la resistencia del canal de conducción como una resistencia variable en el tiempo.

El mezclado de frecuencias se origina de manera convencional, aplicando una señal grande LO y una señal pequeña RF a un dispositivo no lineal; la señal LO modula la conductancia para la frecuencia a la que se trabaja, generando una señal de corriente con armónicas de distinto orden a las señales de alimentación, con lo que se obtiene la conversión de frecuencias. El canal no polarizado opera como un resistor, cuyo valor puede variarse cambiando la señal de voltaje con la que se alimenta a la compuerta [6].

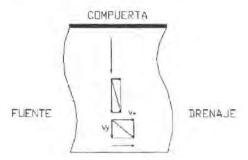

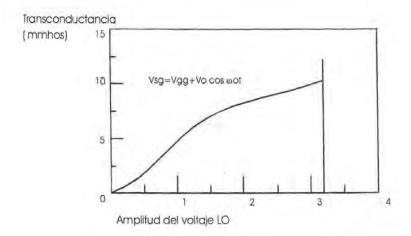

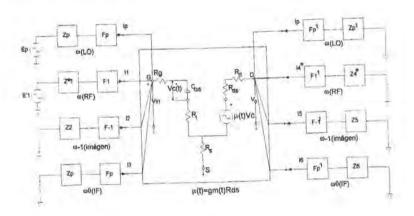

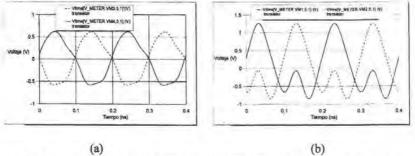

Para llevar a cabo la acción del doblador, el MESFET opera en configuración de fuente común (common source): la señal LO se aplica a la compuerta, y finalmente, la señal IF de salida se filtra del drenaje. En la 1ª. representación del circuito equivalente, el doblado de frecuencias ocurre en un FET cuando los elementos de señal pequeña, varían en una relación periódica mediante la acción de una señal grande de oscilador local (LO), alimentado en la terminal de la compuerta. La figura 9 es una gráfica de la transconductancia en función del voltaje de polarización Vgg, para un valor de voltaje Vdd de 3.0 V.

Fig. 9. Transconductancia de conversión como función de la señal aplicada LO, (Ref.: Performance of GaAs MESFET Mixers at X Band, [6] pág. 354).

El análisis completo de un transistor usado como mezclador o doblador debe dar como resultado la expresión para las pérdidas de conversión, incluyendo los efectos de la capacitancia no lineal del circuito equivalente del transistor, representados en los análisis de señal grande y de señal pequeña.

Las propiedades de señal pequeña, tales como pérdidas y nivel de ruido dependen de las señales de voltaje y corriente de la señal grande producidas en el transistor por la señal de entrada LO, de la cual la corriente y voltaje pueden describirse en series de Fourier como:

$$V_{j}(t) = \sum V_{k} \sum_{k=\infty}^{\infty} e^{jk\omega_{in}t} \qquad (1.26)$$

$$i_d(t) = i_c(t) + i_d(t)$$

(1.27)

Donde:

ie(t)- corriente a la salida del transistor.

ic(t)- corriente en el capacitor.

id(t)- corriente en el resistor.

En la operación del transistor como mezclador, si en presencia del voltaje de polarización se alimenta también una señal grande de LO, en las terminales compuerta-fuente, la transconductancia se convierte en una función variante en el tiempo  $g_m(t)$  con un periodo igual al de LO, por lo que se puede representar de la siguiente manera:

$$g_m(t) = \sum_{k=-\infty}^{\infty} g_k e^{jk\omega_{(i)}t}$$

(1.28)

donde:

$$g_{k} = \frac{1}{2\pi} \int_{0}^{2\pi} g(t)e^{-jk\omega_{OL}t} d(\omega_{OL}t)$$

(1.29)

Donde:

ωoL= frecuencia de la señal LO.

El factor de amplificación en un transistor es  $\mu(t) \cong R_d g_m(t)$ , donde  $R_d = R_0$ , es la componente promedio en el tiempo de la resistencia del drenaje; cuando se alimenta con una segunda señal pequeña Vc(t), de magnitud mucho menor a la señal LO, y de frecuencia  $\omega_1 \neq \omega_{0L}$ , ésta pasa por la capacitancia de la compuerta, Csg, y debido a la acción no lineal del cambio de la transconductancia, variante en el tiempo, se genera una señal  $\mu(t) V_c(t)$ , reemplazando la fuente convencional en el FET por una fuente  $V_c(t)$  en el circuito del drenaje, ocasionando el proceso de mezclado o cambio de frecuencias en el FET, puesto que la señal de voltaje generada posee componentes de frecuencia  $|n\omega_0\pm\omega_1|$ , donde "n" tiene valores enteros. Debido a que Vc(t) es pequeño, se consideran los productos del mezclado de frecuencias que son función de la frecuencia RF:  $\omega_r$ .

En la figura 10 se muestran los circuitos de alimentación, de imagen y de IF;  $V_1$ ,  $V_2$ ,  $V_3$  e  $I_1$ ,  $I_2$ ,  $I_3$  representan las amplitudes complejas del voltaje y la corriente de la señal de entrada, su imagen y la componente de la señal IF, respectivamente en un mezclador, en la compuerta, y  $V_4$ ,  $V_5$   $V_6$  e  $I_4$ ,  $I_5$ ,  $I_6$  son las amplitudes de corriente y voltaje de las componentes en el drenaje. Existe la respuesta de la imagen, que se presenta cuando la frecuencia de RF es  $\omega r = \omega_0 \pm \omega i$ , lo que genera que a la salida tengamos una señal de frecuencia igual a  $\omega r \pm \omega_0 = 2\omega_0 \pm \omega i$ ,  $\omega i$  y  $-\omega i$ , esta última frecuencia se llama la respuesta imagen del mezclador, que se necesita eliminar, aunque es muy difícil de distinguir de la respuesta directa. Puede eliminarse sólo mediante el filtrado la señal RF a la entrada del mezclador.

Si la señal de entrada es alimentada por una fuente de voltaje  $E_1$  que tiene una impedancia interna  $Z_1$ , y una frecuencia  $\omega_1$ ; así como las demás componentes de frecuencia, incluida la señal a la frecuencia deseada de  $\omega_3$ . Tomando en cuenta las terminaciones en impedancias complejas, entonces podemos relacionar el voltaje y las corrientes en las terminales compuerta-fuente y drenaje-fuente,  $V_k$  e  $I_k$  en la siguiente forma:

$$V_k = E_k - I_k Z_k$$

,  $(k=1, 2, ..., 6)$  (1.30)

Donde E<sub>k</sub>=0 para k≠1.

ω<sub>p</sub>- Frecuencia de la señal LO.

ω<sub>1</sub>-Frecuencia de la señal RF.

Fig. 10.- Circuito equivalente del transistor mostrando las señales de entrada, salida e imagen, (Ref.: Performance of GaAs MESFET Mixers at X Band, [6] pág. 352).

Se representan también filtros ideales marcados con Fk y Fk', los cuales representan a los circuitos de acoplamiento, que permiten el paso de sus respectivas frecuencias y eliminan las componentes de las otras señales, con esta representación, obtenemos el resultado del doblado y mezclado en las frecuencias a la salida del circuito.

A partir del circuito equivalente, se pueden establecer las relaciones entre éstas frecuencias mediante el análisis de mallas, en notación matricial tenemos [6]:

$$[E] = [V] + [Z_t][I] = [Z_m][I] + [Z_t][I]$$

(1.31)

Donde:

$$[E] = \begin{bmatrix} E_1^* \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \end{bmatrix} \qquad [V] = \begin{bmatrix} V_1^* \\ V_2 \\ V_3 \\ V_4^* \\ V_5 \\ V_6 \end{bmatrix} \qquad [I] = \begin{bmatrix} I_1^* \\ I_2 \\ I_3 \\ I_4^* \\ I_5 \\ I_6 \end{bmatrix}$$

(1.32)

[Zm] es la matriz de impedancias del transistor y [Zt] es la matriz que representa las impedancias en sus terminaciones.

$$[Z_m] = \begin{bmatrix} Z_{11}^* & 0 & 0 & Z_{14}^* & 0 & 0 \\ 0 & Z_{22} & 0 & 0 & Z_{25} & 0 \\ 0 & 0 & Z_{33} & 0 & 0 & Z_{36} \\ Z_{41}^* & 0 & Z_{43} & Z_{44}^* & 0 & 0 \\ 0 & Z_{52} & Z_{53} & 0 & Z_{55} & 0 \\ Z_{61}^* & Z_{62} & Z_{63} & 0 & 0 & Z_{66} \end{bmatrix}$$

(1.33)

$$[Z_{i}] = \begin{bmatrix} Z_{1}^{*} & 0 & 0 & . & . & . \\ 0 & Z_{2} & & & & \\ 0 & & Z_{3} & & & \\ . & & & Z_{4}^{*} & & \\ . & & & & Z_{5} & \\ . & & & & Z_{6} \end{bmatrix}$$

(1.34)

Los elementos de la matriz [Zm] están en función de las componentes del circuito equivalente del transistor:

$$Z_{kk}(\omega_k) = R_{gm} + R_s + R_s + \frac{1}{j\omega C}, \quad (k = 1,2,3)$$

(1.35)

$$= R_{dr} + R_r + R_s, (k = 4,5,6)$$

(1.36)

$$Z_{14} = Z_{25} = Z_{36} = R_x \tag{1.37}$$

$$Z_{14} = \frac{-g_0 R_y}{j\omega_i C} + R,$$

(1.38)

$$Z_{61} = \frac{-g_1 R_d}{j \omega_1 C}$$

(1.39)

$$Z_{52} = \frac{-g_0 R_d}{j \omega_2 C} + R, \qquad (1.40)$$

$$Z_{62} = \frac{-g_1 R_d}{j \omega_2 C} \tag{1.41}$$

$$Z_{63} = \frac{-g_0 R_d}{j \omega_3 C} + R_s \tag{1.42}$$

$$Z_{43} = Z_{53} \frac{-g_1 R_d}{i \omega_5 C}$$

(1.43)

Donde:

C= el valor promedio en el tiempo de la capacitancia de la fuente a compuerta (sourcegate).

R<sub>d</sub>= Resistencia del drenaje o drain.

R<sub>gm</sub>= Resistencia parásita de contacto de la compuerta o gate.

R<sub>s</sub>= Resistencia parásita de contacto de la fuente o source.

R<sub>dr</sub>= Resistencia parásita de contacto del drenaje.

La ganancia de conversión Gav entre la entrada RF; del puerto 1, y la salida lF en el puerto 6 puede expresarse como:

$$G_{av} = 4R_g R_L \left| \frac{I_6}{E_L} \right|^2$$

(1.44)

Donde la impedancia de entrada es:

$$R_{in} = R_{gan} + R_i + R_s \tag{1.45}$$

La ganància tiene un valor máximo al centro de la banda de frecuencias en que se trabaja, cuando la fuente y la carga están acopladas al FET, o sea que  $R_g=R_{in}$ ,  $X_g=(\omega_1C)^{-1}$ ;  $R_i=R_d$ ,  $X_i=0$ , entonces la ganancia resulta igual a:

$$G_{c} = \frac{G_{m}^{2}, \max_{L}}{16\omega_{RF}^{2}C_{gr}^{2}(R_{x} + R_{i} + R_{g})}$$

(1.46)

Ésta es la ganancia máxima disponible, y el valor óptimo de ésta ganancia para de un mezclador o cambiador de frecuencias es de 5 a 6 dB. Sin embargo, a mayores valores de ganancia de conversión se presenta una distorsión por intermodulación, además de que se incrementa la figura de ruido del receptor, en multiplicadores o dobladores de frecuencia del tipo FET, por lo que en su diseño no es tan importante el conseguir muy altos valores de ganancia, sino llevar a cabo una baja figura de ruido y de pérdidas de conversión para un valor específico de ganancia. En el diseño propuesto en este trabajo se obtuvieron valores aceptables de pérdidas de conversión, con bajo nivel de ruido, así como una baja intermodulación, con el tipo de transistor utilizado (HEMT).

El valor de la mínima potencia requerida en la señal LO para el funcionamiento del doblador de frecuencias, se calcula en base a los valores de los elementos presentes en el circuito equivalente y obtenidos a partir de mediciones de parámetros S, con los que se obtiene una aproximación de dicha potencia requerida mediante la expresión:

$$P_{I,O} = \frac{1}{2} \left( V_{g,\text{max}} - V_{gg} \right)^2 \omega_P^2 C_{gg}^2 \left( R_x + R_i + R_g \right) \quad (1.47)$$

En el diseño de mezcladores o dobladores de frecuencias se necesita acoplar el dispositivo mezclador en sus tres puertos. Es un proceso complicado debido a que se presentan varias

frecuencias con sus respectivas armónicas. La potencia de señales no deseadas puede disiparse en las terminaciones resistivas, y también se puede bloquear con las terminaciones de elementos reactivos, aunque se incrementen las pérdidas en el arreglo total del mezclador. Para conocer las pérdidas de conversión, figura de mérito muy importante en el funcionamiento del dispositivo mezclador de frecuencias, se calcula la relación entre la potencia disponible a la entrada, en la señal RF con la potencia de salida:

Pérdidas de conversión = 10 log potencia disponible de entrada RF

potencia de salida IF (1.48)

Los valores de las pérdidas de conversión más convenientes, se obtienen para altos valores de voltaje LO. Por lo que la señal LO de potencia requerida aplicada a la compuerta, se calcula con la ecuación (1.47).

Conclusión: Con la ayuda de las ecuaciones y modelos matemáticos que simulan el comportamiento del FET, en función de los voltajes aplicados, podemos diseñar un arreglo doblador de frecuencias con base en transistores tipo FET, de los que podemos aprovechar sus características, y los efectos de los elementos representados en su circuito equivalente.

## ESTUDIO DE CIRCUITOS DE MICROONDAS UTILIZADOS EN EL MANEJO DE LAS SEÑALES EN EL DOBLADOR DE FRECUENCIAS.

Objetivo: Describir los efectos eléctricos más importantes considerados en el diseño del doblador de frecuencias, así como los que corresponden al circuito híbrido, que forma parte del arreglo final, aprovechando sus características en el funcionamiento del doblador, y lograr un manejo más eficiente de la potencia de las señales de entrada y salida en el circuito.

La potencia de la señal LO necesaria para obtener las menores pérdidas de conversión es también resultado de un voltaje de polarización lo mas cercano posible al voltaje de corte (pinch-off). Esto se debe a que la ganancia y pérdidas de conversión dependen principalmente de la polarización de la compuerta y de la aplicación de la señal LO. El voltaje instantáneo entre las terminales de compuerta y fuente se puede representar como:

$$V_{\text{NK}}(t) = V_{\text{KK}} + V_{n} \cos \omega_{0} t \qquad (2.1)$$

A partir de resultados experimentales, se comprobó que para un valor de polarización Vsg~Vpinch-off se presentan mejores valores de pérdidas de conversión, así como un valor máximo en la transconductancia, y en la magnitud de las armónicas de la señal de salida.

El bajo valor de la impedancia a la salida en el drenaje, se encontró mediante el acoplamiento de impedancias, para la frecuencia del mezclador y sus primeras armónicas, evitando así distorsiones en la señal de corriente a la salida.

En teoría, a partir de los elementos del circuito equivalente del transistor, la impedancia de entrada es:

$$Z_m(\omega_n) = R_g + R_s + R_i + \frac{1}{j\omega_n C_{gg0}}$$

(2.2)

Donde Cgs<sub>0</sub> es la capacitancia de compuerta a source para el FET a un voltaje cero, y las resistencias Ri, Rs, y Rg son las resistencias en el circuito equivalente del FET, la impedancia de entrada puede estimarse a partir de los parámetros de dispersión S del dispositivo, considerando que el coeficiente de reflexión a la entrada de un transistor, en función de dichos parámetros es aproximadamente.

$$\Gamma_{m} = S_{11} - \frac{S_{21}S_{12}}{1 + S_{22}}$$

(2.3)

de donde se deriva la impedancia de entrada en función de los coeficientes de reflexión:

$$Z_{m} = Z_{n} \frac{\left(1 + \Gamma_{m}\right)}{\left(1 - \Gamma_{m}\right)} \tag{2.4}$$

En nuestro trabajo, conocimos el valor de las impedancias mediante el programa de simulación.

A continuación analizamos efectos y características tanto del transistor como de los arreglos de circuitos de microondas utilizados en nuestro trabajo.

### 2.1 INTERMODULACIÓN

La conversión de frecuencias necesita de un dispositivo no lineal para llevarse a cabo, tal como el diodo y el transistor, pero la característica no lineal también da como resultado el efecto de la intermodulación, que se manifiesta en la producción de armónicas y productos del mezclado de frecuencias no deseadas, lo cual también incrementa la pérdida de conversión, así como la distorsión en la señal obtenida.

Si se toma en cuenta que el voltaje con el que se trabaja en un sistema que usa un dispositivo no lineal puede expresarse como una serie de Taylor en donde:

$$v_{whila} = a_0 + a_1 v_m + a_2 v_m^2 + a_3 v_m^3 + \dots$$

(2.5)

Trabajando con un mezclador o doblador, los términos de 2º orden en adelante son muy importantes, en especial cuando la entrada al sistema está formada por dos frecuencias muy cercanas:

$$v_m = \cos \omega_1 t + \cos \omega_2 t \tag{2.6}$$

Donde:

ω<sub>1</sub>= frecuencia de la señal LO.

ω2= frecuencia de la señal RF.

Por lo que el espectro de salida tiene armónicas de la forma  $m\omega_1 + n\omega_2$ , donde m y n son enteros, ya sea positivos o negativos, entonces el orden de un producto dado es igual a |m| + |n|, El término  $v_{in}^2$  producirá armónicas de frecuencias del orden de  $2\omega_1$ ,  $2\omega_2$ ,  $\omega_1 - \omega_2$  y  $\omega_1 + \omega_2$ , todos productos de segundo orden:

$$v_{in}^2 = (\cos \omega_1 t + \cos \omega_2 t)^2 = \cos^2 \omega_1 t + 2(\cos \omega_1 \cdot \cos \omega_2) + \cos^2 \omega_2 t$$

(2.7)

Todas estas frecuencias pueden filtrarse fácilmente debido a que están lejos de las frecuencias fundamentales  $\omega_1$  y  $\omega_2$ , pero el término  $v_{in}^3$  de la serie proporciona productos de tercer orden tales como  $3\omega_1$ ,  $3\omega_2$ ,  $2\omega_1+\omega_2$ , y  $2\omega_2+\omega_1$ , que pueden filtrarse, así como productos  $2\omega_1-\omega_2$  y  $2\omega_2-\omega_1$ , los cuales no se pueden filtrar fácilmente, cuando  $\omega_1$ y  $\omega_2$  son frecuencias muy cercanas, esos productos se conocen como distorsiones de intermodulación:

$$v_{ln}^{3} = (\cos \omega_1 t + \cos \omega_2 t)^{V} \qquad (2.8)$$

El mezclador en base a diodos genera una señal de salida en la cual el término de Ser, ordentiene valores que cuentan de manera importante, por lo que la intermodulación en los mezcladores que trabajan con tales dispositivos está presente ocasionando un aumento en el valor de las pérdidas de conversión. Cuando se utiliza un transistor en el mezclador, el transistor genera una salida con componentes de hasta 2° orden, y como ya se mencionó, genera componentes de frecuencia que pueden filtrarse, por lo que el transistor evita las distorsiones por intermodulación. En nuestro caso, para el doblador de frecuencias se presenta una señal más pura.

### 2.2 ARREGLO DEL CIRCUITO COMO DOBLADOR BALANCEADO.

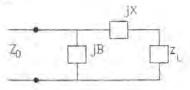

El arreglo básico de nuestro doblador de frecuencias, consiste de un elemento no lineal y un circuito acoplado que funciona como filtro, pero tiene el inconveniente de que no se pueden suprimir eficientemente las componentes de señales no deseadas en las terminales a la entrada y a la salida del circuito.

Una opción es la estructura balanceada, que aunque presenta valores de pérdidas de conversión mayores, divide la señal de entrada RF, y presenta un mejor manejo de la potencia, mejor aislamiento entre las señales de entrada y de salida, así como eliminación de respuestas no deseadas en las terminales.

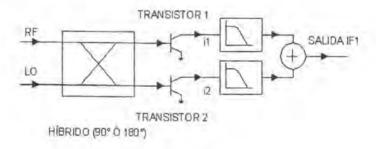

Un circuito doblador de frecuencias balanceado está formado por dos o más elementos no lineales representados por diodos o transistores con un hibrido de 3 dB, de 90° o 180°. Para separar en dos componentes a la señal LO en el doblador, sin la presencia de componentes no deseadas en los puertos de salida, y cancelación de ruido en las salidas del elemento hibrido, se necesita tener un efecto aislador entre las señales para un amplio rango de frecuencias, en el puerto de salida, con su circuito de acoplamiento funcionando como

filtro, o bien añadir un circuito divisor de potencia para eliminar un producto no deseado en el resultado del doblado de frecuencias, en una carga resistiva.

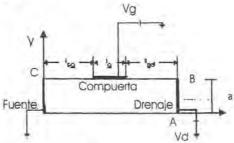

En el caso del doblador de frecuencias, separamos la señal LO en el elemento híbrido, para alimentar a los transistores con ambas partes en que dividimos la señal defasadas entre sí en 180°, con el mismo aislamiento entre ambas.

Para ajustar la fase de las terminaciones, se varía la longitud de la línea de transmisión entre el circuito de acoplamiento y el mezclador, con el fin de obtener las componentes de las frecuencias deseadas, y lograr un buen aislamiento entre las señales de entrada, sin que se presenten componentes de la entrada en la señal de salida.

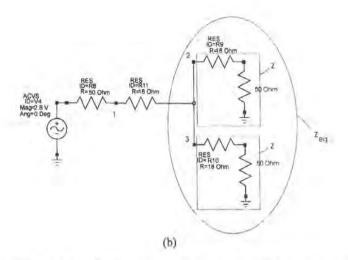

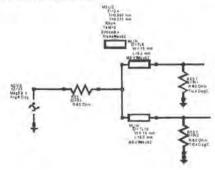

El arreglo que nos proporciona buenos resultados para el doblado de frecuencia de forma eficiente y con buenos valores de pérdidas de conversión, utilizando un circuito híbrido se muestra en la figura 11:

Fig. 11.- Diagrama del circuito doblador de frecuencias que utiliza un elemento híbrido a 90° ó 180° (Referencia: Microwave Engeneering, David Pozar W, 1986, [9], pág. 15).

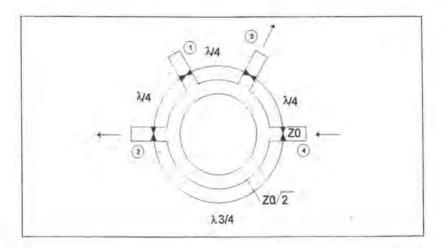

Para manejar más fácilmente la separación de las señales de entrada al híbrido LO, RF, sin la presencia de las componentes de la señal de salida IF, así como con la supresión de las componentes de las señales de entrada a la salida del arreglo, se hace uso de las estructura del anillo híbrido.

En el caso de nuestro doblador balanceado, se proporcionan distintos puertos para las señal de salida, en los que la señal de entrada se alimenta a un puerto, lo que evita que los rangos de frecuencia manejados se traslapen; si se presentara tal situación, no sería posible la filtración de las componentes de la señal resultante, de cualquier orden. Mediante el uso de un elemento híbrido se pueden obtener de 10 a 30 dB de aislamiento entre las señales de

salida del mismo, dependiendo de factores como la frecuencia con que se trabaje, ancho de banda y estructura del doblador.

En nuestro caso, los dobladores balanceados, como arreglos de circuitos de microondas permiten un acoplamiento correcto con el dispositivo, tanto en las armónicas de la señal con las que se alimenta a la entrada del circuito híbrido, como en el puerto de salida con las señales que se generan de su acción dobladora de frecuencias.

Los circuitos de acoplamiento trabajan como filtros, y separan las componentes de IF y LO que existen en las terminales del dispositivo, además ubican las componentes de las señales que corresponden a cada terminal.

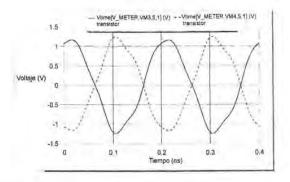

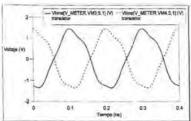

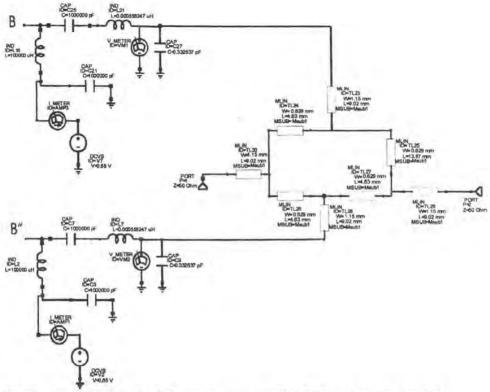

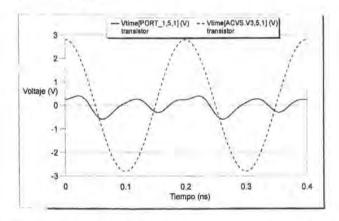

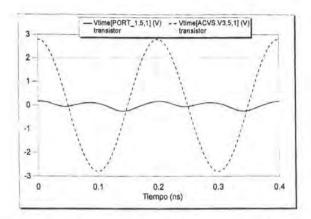

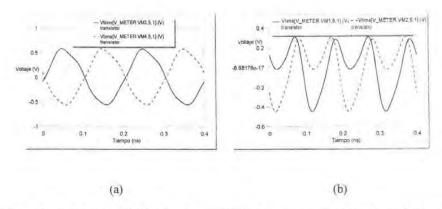

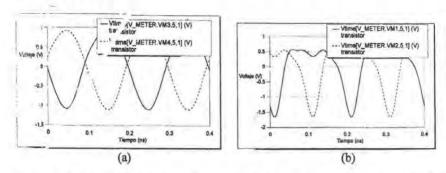

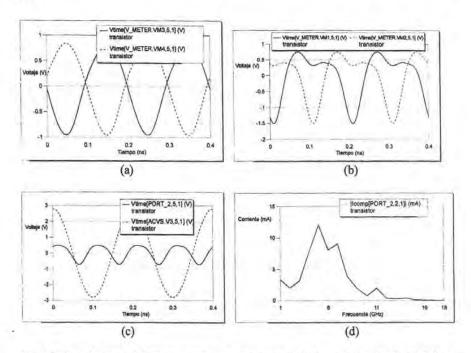

Las señales de salida del híbrido alimentan a las compuertas de los dos transistores con una diferencia de fases entre si de 180°, por lo tanto, las componentes fundamentales de las corrientes de salida en el drenaje de cada transistor también están en contrafase, entonces cada transistor efectivamente corto circuita al otro para la frecuencia fundamental y crea para dicha componente una "tierra virtual" en el drenaje.

Las señales de la frecuencia fundamental a la salida de los transistores, al estar defasadas en 180°, cuando se suman, se eliminan en tanto que las componentes de 2° orden se suman, obteniéndose como resultado una señal de frecuencia igual a la suma o diferencia de las frecuencias de las señales aplicadas a la entrada del circuito.

Otra ventaja que presenta este tipo de circuitos en comparación con un arreglo de un solo transistor es que el doblador o mezclador balanceado basado en FET tiene una potencia de salida 3 dB y es más fácil de acoplar.

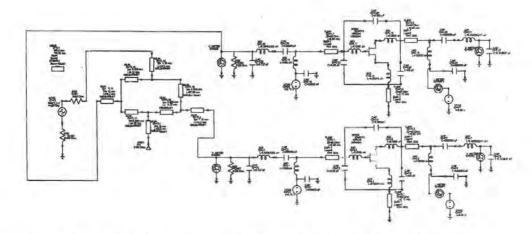

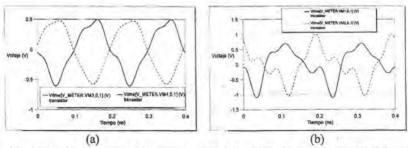

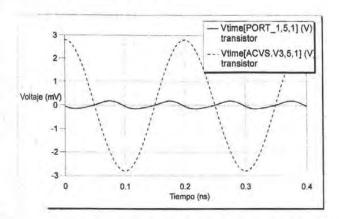

El arreglo propuesto en el presente trabajo, funciona como doblador de frecuencias y consiste en dos transistores del tipo HEMT, alimentados por señales defasadas en 180°. A la salida del híbrido, buscamos que las armónicas de frecuencia fundamental e impares se cancelen, y que las señales de segunda armónica se combinen constructivamente [8].

Existen también otros dobladores de frecuencia balanceados que utilizan transistores de GaAs, en construcción MMIC, que presentan arreglos compactos [7][8], con elementos prácticos y de sencilla construcción, con arreglos de dos transistores HEMT y su respectiva polarización, así como el circuito híbrido, como acoplador direccional que divide la potencia de entrada en dos partes iguales, alimentándose a la compuerta de cada transistor. Los trabajos que los presentan, desarrollan el análisis del balance de armónicas en la señal de salida [8].

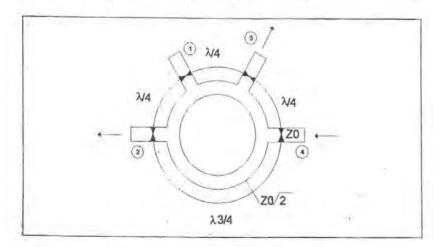

Con buenos níveles de potencia en cualquiera de los puertos de salida, el hibrido utilizado que funciona para frecuencias de microondas es el del tipo de "rat-race". Consiste en un arreglo formado por secciones de línea de transmisión de microcinta cuya circunferencia mide en total 1.5 veces la longitud de onda de la frecuencia en que se trabaja, los cuatro puertos de 50 ohms se conectan al anillo en una disposición tal que dos de sus puertos están separados  $0.75~\lambda$  ( $\lambda$  es la longitud de onda), con las demás separaciones de longitud igual a  $0.25~\lambda$ , como se muestra en la figura 12:

Fig. 12.- Anillo híbrido del tipo "rat race", utilizado en el arreglo propuesto del doblador de frecuencias, indicando el puerto 4 como puerto de entrada, y los puertos de salida, de donde se alimentan los transistores. (Referencia: Programa de simulación Microwave Office).

## 2.3 ANÁLISIS DE LAS SEÑALES EN EL DOBLADOR BALANCEADO.

Conociendo la característica I/V de los transistores, podemos representar mediante series infinitas de potencia la relación no lineal entre las corrientes de salida de los transistores y los voltajes provenientes de ambas ramas del híbrido o anillo, y tenemos que dichas corrientes se pueden representar como:

$$I_1 = aV_1 + bV_1^2 + cV_1^3 + dV_1^4 + \dots$$

(2.9)

$$I_2 = aV_2 + bV_2^2 + cV_2^3 + dV_2^4 + ...$$

(2.10)

Donde:

I<sub>1</sub> e I<sub>2</sub> son las corrientes a la salida de los transistores.

Los voltajes provenientes del circuito híbrido, V<sub>1</sub> y V<sub>2</sub>, que se aplican en la compuerta de los transistores, son iguales a:

$$V_1 = -V_L \cos(\omega_L t) + V_{RF} \cos(\omega_{RF} t)$$

(2.11)

$$V_2 = V_L \cos(\omega_L t) + V_{RF} \cos(\omega_{RF} t)$$

(2.12)

Donde:

V<sub>L</sub> y V<sub>RF</sub> son los voltajes aplicados, de las señales LO y RF, al circuito híbrido, para un mezclador.

La corriente total de la señal IF es:

$$IF = I_1 + I_2$$

(2.13)

En nuestro caso, al construir un doblador basado en transistores tipo HEMT, se puede aplicar la señal de entrada LO al circuito híbrido, en el cual se dividirá y cambiará de fase, aplicándose después a las compuertas de ambos HEMTs. Al entrar a las compuertas, ambas partes de la señal están defasadas en 180°, así como a la salida de los transistores. Las señales resultantes deben sumarse en fase usando otro circuito híbrido, para encontrar la señal IF desarrollada.

Los multiplicadores de frecuencia balanceados presentan un buen nivel de aislamiento entre las señales de los puertos de salida con respecto a las de entrada. Esta característica se presenta especialmente para señales de frecuencias fundamental e impares, también presentan la facilidad de trabajar en un amplio rango de frecuencias cuando se trabaja en circuitos monolíticos.

Los diferentes arreglos con anillos híbridos desarrollados en trabajos anteriores para llevar a cabo dobladores de frecuencia, estaban basados en diodos Schotky. Actualmente, al utilizar multiplicadores con transistores tipo FET se incrementa la eficiencia de conversión en este tipo de circuitos, con diferentes configuraciones que han demostrado las ventajas del uso de los transistores como elementos no lineales. El arreglo propuesto, que utiliza dobladores con transistores del tipo de alta movilidad de electrones (HEMT), también puede trabajar en una mayor banda de frecuencias, con mejor supresión de armónicas fundamentales e impares.

## 2.4 CIRCUITO DOBLADOR DE FRECUENCIA CON UN ELEMENTO HÍBRIDO.

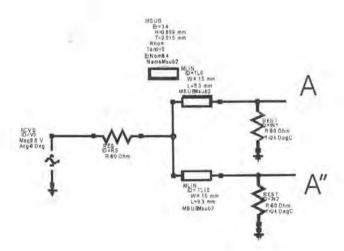

En el arreglo analizado este trabajo, se utiliza el circuito híbrido como divisor de la señal de entrada, ya que dicha señal se aplica al puerto 4 y las señales resultado de la división, defasadas 180° entre sí, se obtienen a la salida de los puertos 2 y 3, con éstas alimentamos a cada circuito doblador de frecuencias, para obtener después las señales de frecuencia duplicada.

El comportamiento de la señal dentro del anillo híbrido, genera un defasamiento de fases en las dos partes en las que se divide la señal de entrada, de la manera siguiente:

A la salida en el híbrido,  $V_1(t)$  y  $V_2(t)$ , se forman en función de la señal aplicada, así como de la señal de ruido. La señal de entrada, al ser dividida en dos partes, llega a los puertos de salida: 2 y 3, como se muestra en la figura 12, en cada trayectoria se tienen diferentes cambios de fase en su recorrido en el anillo.

Las partes en que se divide la señal, para llegar al puerto 2, tienen que recorrer, por un lado, una distancia igual a ¼ de longitud de onda, tomando en cuenta el recorrido directo desde el puerto 4 hasta el 2; la otra parte de la señal, que pasa por los segmentos que unen a los puertos 4 con 3, y el puerto 3 con el puerto 1, hasta llegar al puerto 2, también recorre la longitud equivalente a ¾ de la longitud de onda, por lo cual, en este puerto, las dos partes de la señal, que están defasadas en un ángulo equivalente a 270° se suman:

$$V_2(t) = (V_0 + V_n)Cos(\omega_0 t - 270^0) + (V_0 + V_n)Cos(\omega_0 t - 270^0)$$

(2.14)

Donde:

Vo= Voltaje aplicado al anillo híbrido.

V<sub>n</sub>= Magnitud del voltaje de ruido.

V<sub>2</sub>= voltaje de salida en el puerto 2.

V<sub>3</sub>= voltaje de salida en el puerto 3.

Por otra parte, al recorrer la señal dividida en el anillo, la ruta desde el puerto 4 hacia el puerto 3, recorre dos caminos: en el 1º se recorre una distancia equivalente a ¼ de la longitud de onda, por lo que al llegar al puerto 3 esa parte de la señal está defasada 90º; en el segundo camino, la señal recorre una distancia igual a 5/4 de la longitud de onda para llegar al mismo puerto 3, o sea, la longitud de la onda más ¼ de ésta, por lo que se encuentra en fase en este puerto con la otra parte de la señal, que llega al puerto por la primera ruta y por lo tanto pueden sumarse, y la señal del voltaje en ese puerto es:

$$V_3(t) = (V_0 + V_n)Cos(\omega_0 t - 90^\circ) + (V_0 + V_n)Cos(\omega_0 t - 90^\circ)$$

(2.15)

Son señales que se encuentran defasadas en  $180^{\circ}$  entre sí. Al trabajar con elementos no lineales como los transistores, podemos representar la corriente de salida en series de Taylor, y en función de los voltajes  $V_2(t)$  y  $V_3(t)$ :

$$V_2(t) = 2(V_0 + V_n)Cos(\omega_0 t - 270^0)$$

(2.16)

$$V_3(t) = 2(V_0 + V_n)Cos(\omega_0 t - 90^\circ)$$

(2.17)

Si desarrollamos la expresión de la corriente en cada transistor tenemos, a la salida de uno de ellos:

$$i_2 = aV_2 + bV_2^2 + cV_2^3 + dV_2^4 + \dots$$

(2.18)

Al estar defasados los voltajes que alimentan a cada transistor en 180°, el voltaje que llega al otro transistor queda como si estuviera alimentándose de manera opuesta, lo que resulta dentro de la expresión de la corriente del nodo 3, en un cambio de signo en los términos impares:

$$i_3 = aV_3 + bV_3^2 - cV_3^3 + dV_3^4 - \dots$$

(2.19)

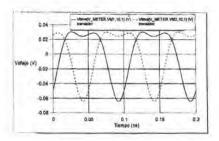

Para sumar ambas señales, necesitamos otro anillo, calculado para 10 GHz, que iguale en fase sus respectivas componentes de segundo orden, y finalmente, la señal de salida total i<sub>F</sub>:

$$i_{\mu} = i_2 - i_3$$

(2.20)

A la salida del segundo anillo se suman las componentes de segundo orden y se anulan las de orden impar.

Con lo que se demuestra que las componentes de frecuencia fundamental y tercera armónica se eliminan y las componentes de 2ª, armónica se suman constructivamente.

Al trabajar con multiplicadores de frecuencia en base a transistores del tipo FET, como ya se mencionó, se maneja un alto valor de ganancia pero se desarrolla el efecto de intermodulación en el doblador, por lo que el diseño propuesto se utilizó un transistor tipo HEMT, obteniéndose valores aceptables tanto de pérdidas de conversión, como de nivel de ruido, así como el anillo híbrido que facilita obtener las frecuencias deseadas, eliminando la intermodulación.

Conclusiones: Se hizo el desarrollo del manejo de las señales en los circuitos de microondas necesarias para eliminar componentes no deseados en el arreglo completo; el circuito híbrido sirve básicamente para dividir la señal de entrada, evitando componentes no deseadas a la entrada de los transistores HEMT.

# 3 DISEÑO DE UN DOBLADOR DE FRECUENCIAS

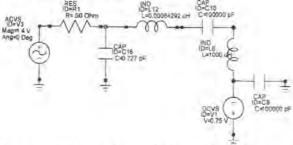

Objetivo: Encontrar el arreglo básico óptimo para funcionar como doblador de frecuencias con el transistor elegido, mostrando en primer lugar los datos técnicos del dispositivo, alimentados en el programa de simulación utilizado, en base al modelo del circuito equivalente y las ecuaciones empleadas en dicho programa, encontrando el arreglo básico y la polarización óptima.

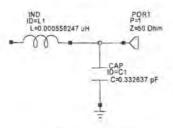

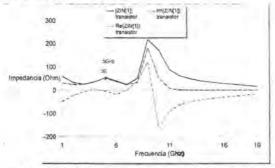

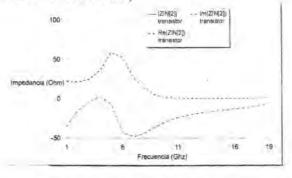

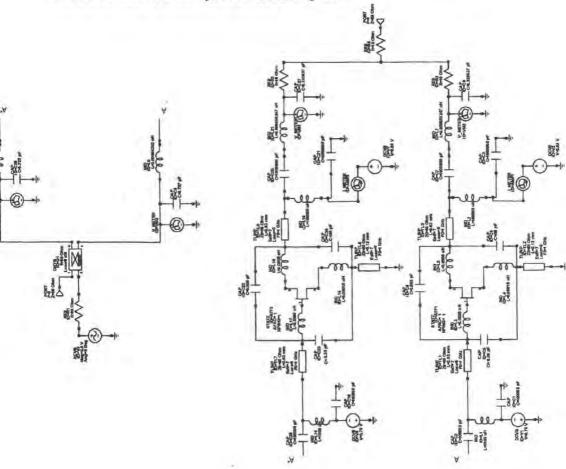

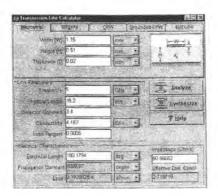

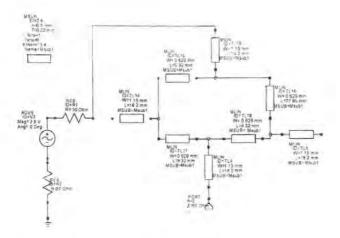

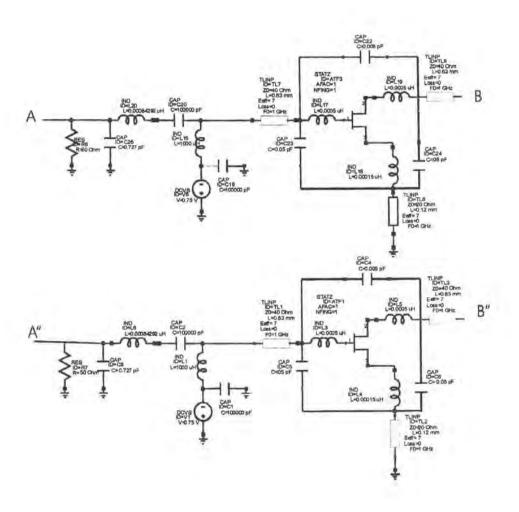

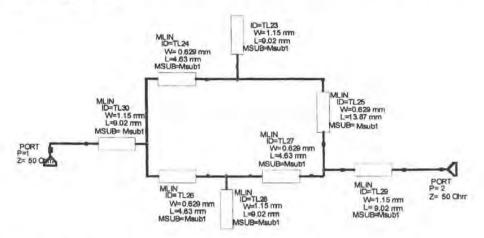

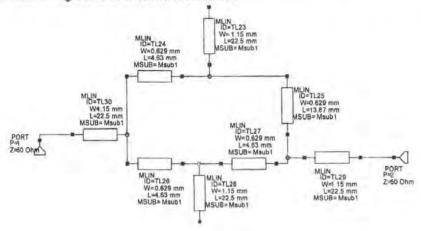

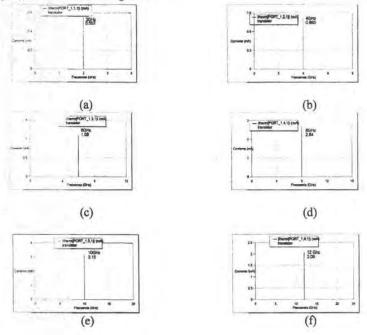

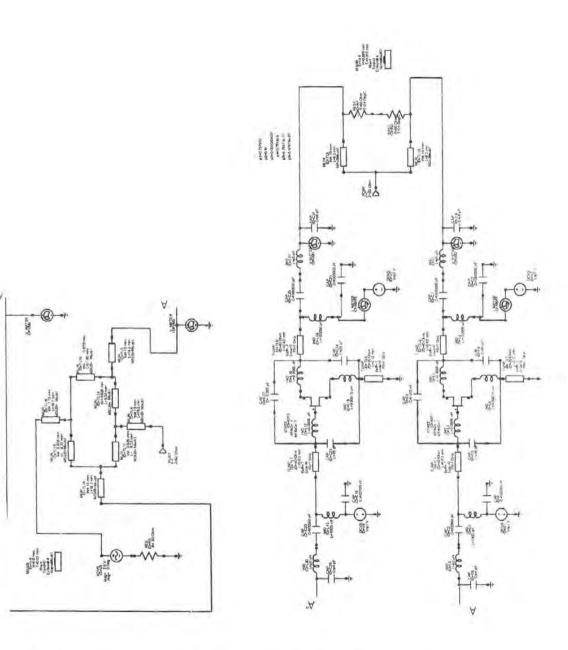

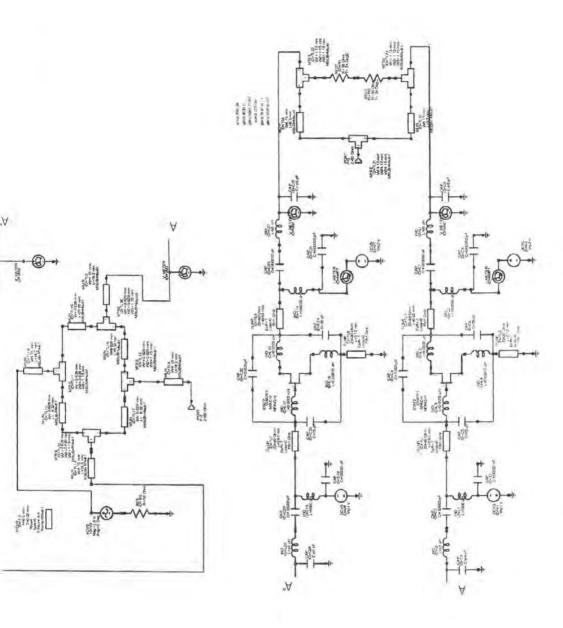

Tomando en cuenta los resultados y antecedentes presentados de trabajos de investigación anteriores, en este trabajo se utilizó un programa de simulación de circuitos (Microwave Office), para simular el comportamiento de los arreglos desarrollados, trabajando con un modelo de transistor HEMT ATF36077.

La aplicación práctica del doblador de frecuencias se encuentra en la transmisión de información, con la transconductancia como portadora de la información, misma que en su frecuencia y duración de pulsos depende de las señales de entrada LO.

El transistor elegido, de GaAs galio arsénico, como ya se mencionó, tiene características como una compuerta de unión tipo Schottky en lugar de una unión PN, de longitud suficientemente corta para arreglos de ondas milimétricas, lo que ocasiona una gran movilidad de los electrones del material de GaAs, con velocidad de saturación, resultando en un tiempo de tránsito del electrón de algunos picosegundos.

Al seleccionar el dispositivo correcto para un arreglo mezclador o multiplicador de frecuencias tomamos en cuenta factores como las pérdidas de conversión en los transistores, sus características de intermodulación, la potencia de alimentación de la señal LO, la frecuencia de operación, el medio de transmisión, así como el encapsulado del dispositivo. También se consideran los efectos de dicho encapsulado tanto en el arreglo como en el circuito equivalente proporcionado por el fabricante.

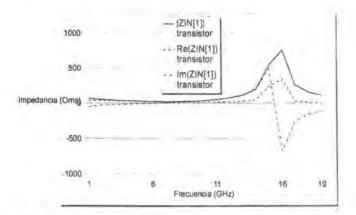

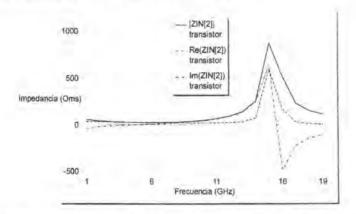

El transistor utilizado en el diseño del doblador de frecuencias propuesto, es un transistor HEMT de Agilent Technologies, modelo ATF-36077, empacado en una superficie con bajos valores de capacitancias e inductancias parásitas, cuyas características nominales son las siguientes: