308917

## UNIVERSIDAD PANAMERICANA

ESCUELA DE INGENIERIA CON ESTUDIOS INCORPORADOS A LA UNAM

# DISEÑO, CALCULO Y CONSTRUCCION DE UN AMPLIFICADOR DE ALTA EFICIENCIA CLASE "S"

T E S | S

QUE PARA OBTENER EL TITULO DE

INGENIERO MECANICO ELECTRICISTA

AREA: INGENIERIA INDUSTRIAL

P R E S E N T A

PABLO ACEVEDO ALVARADO

REVISOR: DR. STANISLAW RACZINSKI

MEXICO, D. F.

1997

TESIS CON FALLA DE ORIGEN

UNAM – Dirección General de Bibliotecas Tesis Digitales Restricciones de uso

### DERECHOS RESERVADOS © PROHIBIDA SU REPRODUCCIÓN TOTAL O PARCIAL

Todo el material contenido en esta tesis esta protegido por la Ley Federal del Derecho de Autor (LFDA) de los Estados Unidos Mexicanos (México).

El uso de imágenes, fragmentos de videos, y demás material que sea objeto de protección de los derechos de autor, será exclusivamente para fines educativos e informativos y deberá citar la fuente donde la obtuvo mencionando el autor o autores. Cualquier uso distinto como el lucro, reproducción, edición o modificación, será perseguido y sancionado por el respectivo titular de los Derechos de Autor.

Quiero agradecer: a mis padres y hermanos por haberme apoyado incondicionalmente durante toda mi carrera encontrándose siempre cerca de mi cuando los necesité. Agradezco a todos mis profesores por la paciencia, dedicación y conocimientos transmitidos a lo largo de mi carrera, en especial al Dr. Stanislaw por su disponibilidad, experiencia, sencillez y tolerancia.

> Por último, gracias a todos mis amigos por su amistad, su experiencia, su apoyo, etc. que sufrieron y disfrutaron junto conmigo todas las etapas de mi carrera.

# ÍNDICE

| INTRODUCCIÓN.                                                                     | 2  |

|-----------------------------------------------------------------------------------|----|

| CAPITULO 1. Marco Teórico.                                                        | 4  |

| CAPITULO 2. Diseño Teórico. Teoría de circuitos para el diseño de un amplificador |    |

| de alta eficiencia.                                                               | 22 |

| Capitulo 2.1. Amplificador clase "D".                                             | 23 |

| 2.1.1. Considereciones Prácticas del amplificador clase "D".                      | 33 |

| Capítulo 2.2. Amplificador clase "S".                                             | 38 |

| 2.2.1. Modulación de anchura de pulso.                                            | 42 |

| 2.2.2. Consideraciones sobre el filtro de salida y frecuencia de                  |    |

| conmutación.                                                                      | 46 |

| CAPITULO 3. Diseño Práctico. Diseño y cálculo de l amplificador clase "S".        | 48 |

| Capítulo 3.1. Diagrama de bloques y descripción general.                          | 49 |

| Capítulo 3.2. Descripción técnica de cada uno de los elementos.                   | 51 |

| CAPITULO 4. Resultados.                                                           | 62 |

| Capítulo 4.1. Cálculos de potencias y eficiencias.                                | 63 |

| CONCLUSIONES.                                                                     | 67 |

| APENDICE 1.                                                                       | 70 |

| BIBLIOGRAFÍA.                                                                     | 72 |

### INTRODUCCIÓN

Durante los cursos de electrónica en la licenciatura, se logran conocer varios tipos de amplificadores de potencia que generalmente manejan bajas frecuencias y que se clasifican de acuerdo con la parte del ciclo de la onda senoidal de entrada durante la cual circula la corriente de carga, observándose que para obtener una amplificación con baja distorsión de las señales, se pueden aplicar 4 clases de amplificadores de tipo push-pull básicamente:

El primer tipo de amplificación es el de clase A, en la cual, debido a que el valor de pico de corriente alterna no excede nunca del valor de la corriente de reposo del colector y en donde se selecciona el punto de operación de tal forma que la señal de salida fluye todo el tiempo (360°) con el inductor (obstrucción de estrangulamiento) en lugar de R<sub>c.</sub>, se conoce que tiene un rendimiento del 50%; el segundo tipo de amplificación que es el de clase B en donde la corriente continua del colector es menor que el valor de pico de la corriente alterna, seleccionándose el punto de operación en un extremo final de su característica, por lo que la amplificación ocurre en la mitad de un ciclo completo (180°), dando lugar a una menor disipación en el colector y un aumento del rendimiento; así el amplificador push-pull de clase B, tiene un rendimiento máximo del 78.5%.

En tercer lugar, se encuentra que dada la existencia de la distorsión de cruce, debida a que la tensión base-emisor es cero en ausencia de señal, se creo el amplificador de clase AB, polarizando aproximadamente a 0.65 V (que es la tensión de umbral para el silicio) las uniones base-emisor, logrando así una menor distorsión que para los amplificadores de clase B. Aunque en la práctica, a menudo, se permite la existencia de esta distorsión y se confia en el transformador y capacidades internas y parásitas para eliminarla, se cuenta también con una pérdida considerable en la eficiencia y un desperdicio de potencia.

Por último, surge el amplificador de clase C, en donde con la selección del punto de operación de tal forma que la corriente de salida fluya por menos de 180°, opera en el rango de corriente pico del transistor y por lo tanto disipa grandes cantidades de potencia en ellos, limitando así sus aplicaciones para banda estrecha en radiofrecuencia, es decir en frecuencias mayores de 20 kHz.

Ahora, después de haber visto todo esto, es lógico preguntarse, si no se han desarrollado amplificadores que suministren potencias similares y más elevadas, con mayor eficiencia, de la manera más económica posible, que no requieran de alta, cara y sofisticada tecnología, que puedan incluir limitaciones de tamaño, peso y tensión de alimentación de corriente continua, que proporsione una distorsión mínima, etc., creándose así el objetivo de este trabajo de tesis, el cual es comprobar y llevar a la práctica en cuanto a investigación, diseño y aplicación, un amplificador, que valiéndose de las herramientas teóricas adquiridas con los amplificadores mencionados, consultas bibliográficas y el trabajo en laboratorio, promete poseer una eficiencia de cerca del 100%, aplicando el modo de operación de amplificación en clase S.

Es importante recalcar que al final del desarrollo de este trabajo de tesis, se podrá concluir acerca de las propledades, aplicaciones, consideraciones y especificaciones del desarrollo de este amplificador.

par diament

# CAPITULO 1 MARCO TEÓRICO

Un amplificador de potencia de "alta frecuencia, es aquél que alcanza una eficiencia mayor que la que se logra normalmente con los amplificadores de potencia A, B o C en la misma aplicación. Hay una gran variedad de amplificadores de potencia de alta eficiencia y de técnicas para combinarlos y realizar objetivos específicos.

Las clases D, E, F, G, H y S se usan de acuerdo a la topología del circuito, así como el modo de operación o ambos para designar varios métodos de aplicación altamente eficientes. Cabe advertir al lector de esta tesis que estos términos no son universales; en particular, los términos "clase D" y "clase S" se invierten a menudo o se intercambian por otros autores.

La eficiencia incrementada de esos amplificadores de potencia proviene de las técnicas que reducen el producto promedio voltaje corriente de colector (es decir, la disipación de potencia). En los amplificadores de potencia en modo de conmutación (clases D, E y S) lo anterior se realiza empleando los dispositivos activos (BJT, FET o tubos de vacío) como conmutadores en lugar de usarlos como fuentes de corriente. Como un conmutador ideal tiene cero voltaje en sus terminales o cero corriente a través de él en todo tiempo, no disipa potencia. Otros amplificadores de potencia de alta eficiencia (clases F, G, y H) usan técnicas de circuito especiales, incluyendo resonadores armónicos y voltajes múltiples de alimentación, para reducir el producto voltaje-corriente de colector.

La técnica clase S se Inventó en 1932, aunque se popularizó sólo en la última década, por poder ya disponer de circuitos integrados, que permitieron se pusiera en práctica.

Esta técnica se puede usar tanto para amplificación, como para modulación de amplitud. Ambas configuraciones utilizan los transistores y diodos para formar un conmutador de dos posiciones, como en un amplificador clase D, el cual se explicará con detenimiento para así entender el principlo en el cual se basa esta clase de amplificadores y poder pasar a la sustitución por elementos integrados y otros procedimientos que permitan crear el amplificador de potencia que se quiere diseñar y crear en esta tesis.

Los amplificadores de "clase D" fueron analizados primeramente por Bexandall y han aparecido recientemente en transmisores de radiodifusión en AM y en transmisores HF de baja potencia. Un amplificador clase D emplea un par de dispositivos activos y un circuito de salida

sintonizado. Los dispositivos se energizan para operar como un conmutador de dos polos que define o una forma de onda de voltaje o de corriente rectangular.

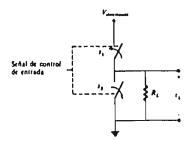

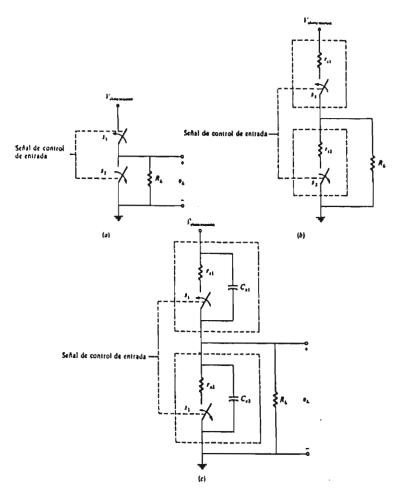

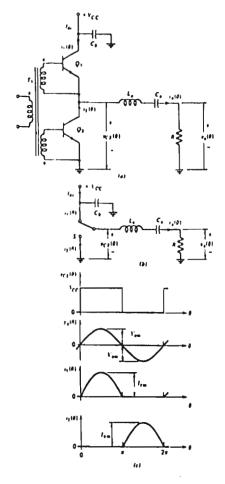

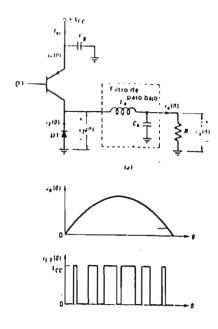

Tenemos por ejemplo el concepto básico del amplificador clase D que se ilustra en la figura 1.1 y el cual se compone de dos transistores complementarios, actuando sobre una resistencia de carga R<sub>L</sub>. En este amplificador, los transistores que se muestran, funcionan como interruptores en vez de fuentes de corriente. Así, la potencia suministrada por la alimentación es igual a la potencia disipada en la carga, haciendo estos factores del amplificador do clase D un amplificador ideal.

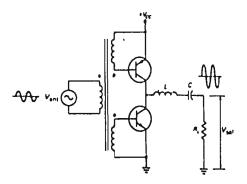

En la figura 1.2, puede verse otro diseño de amplificador clase D, formado por dos transistores complementarios conectados en configuración CE y push-pull. La señal de entrada se acopla a las bases mediante un transformador de RF. En el semiciclo positivo del voltaje de entrada, el transistor de arriba se corta, mientras que el de abajo se satura. En el semiciclo contrario, el transistor de arriba es el que se satura mientras el de abajo se corta. Debido a esto, en el circuito sintonizado se aplica un voltaje que varía entre 0 y +Vcc.

Al observar estos dos ejemplos, vale la pena recordar o conocer algunos conceptos que están involucrados y que sin duda se aplicarán más adelante en el capítulo dos.

Estos conceptos teóricos acerca de los elementos a los que se hace referencia y que se detallan a continuación son los siguientes:

- 1. Polaridad en los devanados.

- 2. Los transistores como interruptores.

- 3. Clases de transistores aplicables.

Fig. 1.1. Amplificador clase D con transistores funcionando como interruptores

Fig. 1.2. Amplificador de clase D formado por 2 transistores complementarios en configuración "push-puli"

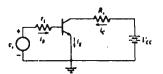

Fig. 1.3. El interruptor con transistor

#### 1. Polaridad en los devanados.

En el caso de que nunca antes se hayan visto transformadores como el de la figura 1.2, con puntos indicados en sus devanados, aquí se explica el significado de esta notación convencional.

El punto en el extremo de cada devanado, tiene la misma fase que los demás extremos con puntos. Así, en la figura 1.2, el extremo con punto del devanado primario es positivo durante el semiciclo positivo del voltaje de entrada y, en ese momento, el voltaje existente en el extremo con punto del devanado secundario superior, es también positivo, al igual que el del extremo con punto del devanado secundario inferior.

Esto hace que el transistor superior se corte y el inferior se sature en ese semiperiodo.

#### 2. Los transistores como interruptores.

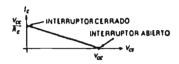

La forma más fácil de utilizar un transistor, es como un interruptor, esto implica que debe operarse en el punto de saturación o de corte y no en alguna otra parte de la trayectoria de la línea de carga. Cuando un transistor se satura, actúa como un interruptor cerrado entre el colector y el emisor. Cuando un transistor está en corte, actúa como un interruptor ablerto.

Observando la figura 1.3, tenemos que sumando los voltajes airededor de la malla de entrada, se obtiene:

$$I_{R}R_{R} + V_{RF} - v_{r} = 0 {1-1}$$

Despejando Is, se obtiene:

$$I_{s} = \frac{v_{t} - V_{sE}}{R_{s}} \tag{1-2}$$

Siendo la ley de Ohm para el resistor de base.

Entonces, si la corriente de base es mayor o igual a l<sub>a</sub>(sat), el punto de operación Q está en la parte superior de la línea de carga figura 1.4. En este caso, el transistor actúa como un interruptor cerrado. Por otra parte, si la corriente de base es cero, el transistor opera en la parte inferior de la línea de carga y actúa como un interruptor abierto.

Al hablar de saturación, se tiene una regla de diseño:

Saturación suave, que significa que el transistor debe saturarse ligeramente, esto es, que la corriente de base sea suficiente para operar el transistor en la parte superior de la línea de carga. La saturación suave no es muy confiable en la producción en serie por la variación en Bcc y en la (sat). No debe usarse saturación suave en un circuito de conmutación transistorizado.

<u>Saturación dura</u> significa lener suficiente corriente de base para saturar al transistor para todos los valores de βcc que se encuentren en la producción en serie. En el peor de los casos de temperatura y corriente, casì todos los transistores de silicio de pequeña señal tienen una βcc mayor a 10. Por lo tanto, una guía para el diseño en saturación dura es tener una corriente de base aproximadamente igual a la décima parte del valor de la corriente de saturación del colector; éste garantiza la saturación dura bajo todas las condiciones de operación.

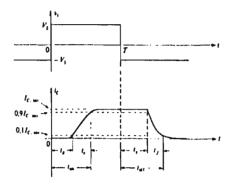

Como se pudo observar, el interruptor es controlado por la corriente aplicada a la base. En tal interruptor mostrado en la figura 1.3, su respuesta ante una tensión de entrada con forma de onda de impulso v, está representada en la figura 1.5.

Entonces se observan los siguientes tiempos que deben de considerarse en el diseño:

Fig. 1.4. Línea de carga.

Fig. 1.5. Respuesta de un interruptor con transistor a un impulso de tensión

Fig. 1.6. Tiempo de retardo de propagación

Tlempo de puesta en conducción. Hay un retardo entre el flanco anterior o de ataque del impulso de tensión de entrada y el instante en que la corriente de colector alcanza el 90 por ciento de su valor máximo. Este tiempo es el de puesta en conducción,  $t_{on}$ . Se le divide en dos intervalos de tiempo; el primero se denomina tiempo de retardo,  $t_{d}$ , y el segundo se denomina tiempo de subida,  $t_{c}$ .

Tiempo de retardo. El tiempo de retardo es el necesario para que la corriente de colector aumente hasta  $0.1I_{c.s.d}$ . Otra manera de describir  $t_d$  es hacer notar que es aproximadamente igual al tiempo necesario para que la tensión base-emisor (diodo) aumente desde -V, hasta aproximadamente +0.7 V.

Tiempo de subida. El tiempo de subida es el tiempo necesario para que la corriente de colector aumente desde 0.1 l<sub>c.sat</sub> hasta 0.9 l<sub>c.sat</sub>. Durante este intervalo, el transistor está funcionando en la región activa normal.

Tiempo de corte. El tiempo necesario para que la corriente de colector disminuya desde  $I_{cont}$  hasta 0.1  $I_{cont}$  cuando  $v_i$  disminuye (fig. 1.5) se denomina tiempo de corte,  $t_{cont}$ . El tiempo de corte es la suma del tiempo de almaconamiento,  $t_a$ , y el tiempo de calda,  $t_i$ , como muestra la figura 1.5.

Tiempo de almacenamiento. El tiempo de almacernamiento es el tiempo transcurrido desde el flanco de bajada del impulso de entrada (t=T) hasta el punto en que  $i_c$  comienza justamente a disminuir hacia cero.

Tiempo de caída. El tiempo de caída  $t_i$  es el tiempo que tarda la corriente de colector en disminuir desde  $l_{cast}$  hasta 0.1  $l_{cast}$ .

Los cálculos del tiempo de retardo, tiempo de subida, tiempo de caída y tiempo de almacenamiento implican varias aproximaciones y generalmente dan por resultado valores que difieren apreciablemente de los publicados por los fabricantes. Además, la mayorla de interruptores con transistor o puertas hoy en día en uso son circuitos integrados que contienen

muchos transistores que no admiten un análisis simple. Por tanto, el lector deberá consultar los catálogos de los fabricantes para estos tiempos de respuesta.

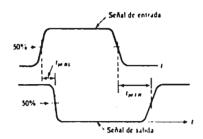

Tiempo de retardo de propagación. El tiempo que tarda un interruptor con transistor en responder a una señal de entrada es lo que se llama tiempo de retardo de propagación, t<sub>po</sub>. Este tiempo se define usualmente como el tiempo transcurrido entre los puntos medios de la tensión de transición de la señal de entrada y la tensión de transición de la señal de salida, como lo muestra la figura 1.6.

El retardo de propagación cuando la salida del interruptor disminuye desde el estado alto hasta el estado bajo se representa por  $t_{\rm pd,H}$  o  $t_{\rm pd}$ . Análogamente el retardo de propagación cuando la salida del interruptor aumenta desde el estado bajo hasta el estado alto se designa por  $t_{\rm pd,H}$  o  $t_{\rm pd}$ . Habitualmente  $t_{\rm pd}$ , es mayor que  $t_{\rm pd}$ , a causa de la inevitable capacidad en la salida del interruptor. Cuando la salida disminuye, la capacidad se descarga a través del transistor (véase figura 1.3), que actúa como baja impedancia; en cambio, cuando la salida aumenta, el condensador se carga a través de la carga, que tiene una impedancia mucho más alta y, por lo tanto, el tiempo de carga es más largo. Si se emplea una salida de simetría complementaria, los tiempos de retardo de propagación son, naturalmente, comparables.

#### 3. Clases de transistores aplicables.

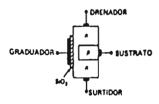

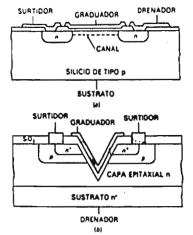

Los transistores que se pueden aplicar, debido a que se trata de un amplificador de potencia, son los transistores de la serie MOSFET (en inglés metal-oxide semiconductor FET) que cuenta con un surtidor o fuente, un graduador (o compuerta), y un drenador o drenaje. A diferencia del JFET, en el MOSFET, el graduador está aislado del canal, por lo que la corriente del graduador es extremadamente pequeña sin importar que el graduador sea positivo o negativo. Al MOSFET en algunas ocasiones se les denomina FET con graduador o compuerta aislada o IGFET (insulated-gate FET).

La figura 1.7 muestra un MOSFET de canal tipo n , una barra conductora de material tipo n con una región tipo p a la derecha y un graduador o compuerta aislada a la izquierda. Los electrones libres pueden fluir desde el surtidor o fuente al drenador a través del

Fig. 1.7. Transistor MOSFET de canal tipo "n"

Fig. 1.8. Transistor MOSFET, en modo de empobrecimiento (a) y en modo de enriquecimiento (b).

Fig. 1.9. Transistor VMOSFET (MOS vertical).

material tipo n. La región tipo p recibe el nombre de sustrato (o cuerpo); ésta reduce fisicamente la trayectoria de conducción a un canal angosto. Los electrones que fluyen del surtidor o fuente al drenador deben pasar a trayés de este canal angosto o estrecho.

A la izquierda del canal se deposita una capa delgada de óxido de silicio (SiO<sub>3</sub>). El óxido de silicio es lo mismo que el vidrio; un aislante. En un MOSFET el graduador o compuerta es metálica. Ya que el graduador está aislado del canal, la corriente en el graduador es despreciable aún cuando el voltaje del graduador sea positivo. El diodo po que existe en un JFET se ha suprimido en el MOSFET.

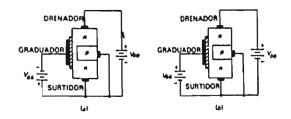

El MOSFET se presenta en dos modos: el modo de empobrecimiento y el modo de enriquecimiento. En el primero (figura 1.8a), contiene un graduador o compuerta polarizada negativamente. La alimentación V<sub>DO</sub> fuerza a los electrones libres a fluir del surtidor al drenador. Estos electrones fluyen a través del canal angosto a la izquierda del sustrato tipo p. Como antes, la tensión de graduador puede controlar el ancho del canal. Entre más negativo es el voltaje en el graduador, más pequeña será la corriente en el drenador. Cuando el voltaje del graduador, es lo suficientemente negativo, la corriente del drenador se corta. Por lo tanto, con un voltaje negativo en el graduador o compuerta, la operación de un MOSFET es similar a la de un JFET. Puesto que el efecto del voltaje negativo de graduador consiste en "empobrecer" de electrones libres el canal; se le llama a la operación con graduador negativo modo de empobrecimiento o de estrechamiento.

En el segundo, ya que el graduador de un MOSFET está aislado del canal, podemos aplicarle un voltaje positivo, como se muestra en la figura 1.8b. El voltaje positivo en el graduador incrementa el número de electrones libres que fluyen a través del canal. Cuanto más positivo sea el voltaje en el graduador, mejor será la conducción de surtidor a drenador. La operación del MOSFET con un voltaje positivo del graduador se basa en el enriquecimiento de la conductividad del canal. Por esta razón, la operación con graduador positivo recibe el nombre de modo de enriquecimiento o de ensanchamiento.

Por último se tiene el transistor MOS vertical VMOSFET (figura 1.9b), el cual como puede observarse, tiene dos fuentes en la parte superior, los que normalmente están interconectadas. Además, el sustrato ahora actúa como drenador. Cuando V<sub>os</sub> es mayor que el voltaje de umbral, los electrones libres fluyen verticalmente hacia abajo, de los surtidores fuentes al drenador.

Puesto que el canal de conducción es mucho más ancho a lo largo de ambos extremos del surco en V, la corriente puede ser mucho mayor. El efecto total es un MOSFET del tipo de enriquecimiento que puede manejar corrientes y voltajes mucho más grandes que un MOSFET convencional.

Antes de que se inventara el transistor VMOS, los MOSFET no podían competir con las potencias nominales de los transistores bipolares. Sin embargo, ahora los VMOS ofrecen un nuevo tipo de MOSFET que es mejor que el transistor bipolar para muchas aplicaciones que requieren alta potencia en la carga, incluyendo amplificadores de audio, amplificadores RF, etc.

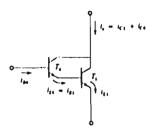

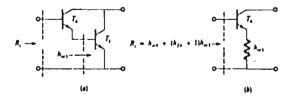

Observando los requerimientos de este tipo de amplificadores y trabajando en el laboratorio, se encontró que se podía utilizar otro tipo más de transistor, el transistor Darlington o también llamado amplificador compuesto, mostrado en la figura 1.10. Esta configuración se usa para aumentar la impedancia de entrada y conseguir una alta ganancia de corriente, ganancia que es igual al producto de las ganancias de los dos transistores  $h_{k1}$  y  $h_{k4}$ .

En este circuito el emisor de T<sub>4</sub> está conectado directamente a la base de T<sub>1</sub>. Normalmente, los dos colectores están también unidos como se indica, aunque esto no es necesario.

La ganancia de corriente del amplificador Darlington, mostrado en la figura 1.10, puede ser calculada a partir de:

Fig. 1.10. Amplificador Darlington (compuesto).

Fig. 1.11. Uso de la reflexión para determinar la impedancia de entrada del amplificador Darlington básico: (a) el amplificador Darlington; (b) T<sub>1</sub> reemplazando por h<sub>wl</sub>.

$$A_{i} = \frac{I_{0}}{I_{B4}} = \frac{I_{C1} + I_{C4}}{I_{B4}} = \frac{\alpha_{1}I_{B1}}{I_{B4}} + \frac{\alpha_{4}I_{B4}}{I_{B4}}$$

(1-3)

donde

$$\frac{I_{E1}}{I_{B4}} = \frac{I_{E1}}{I_{B1}} \cdot \frac{I_{B1}}{I_{E4}} \cdot \frac{I_{E4}}{I_{B4}} \tag{1-4}$$

$$= (h_{\mu_1} + 1)(1)(h_{\mu_4} + 1)$$

$$= (h_{\mu_1} + 1)(h_{\mu_4} + 1)$$

(1-5)

Asl,

$$A_i = \alpha_1(h_{h1} + 1)(h_{h4} + 1) + \alpha_4(h_{h4} + 1) \tag{1-6}$$

Si los dos transistores son idénticos,  $\alpha_1 = \alpha_4 = \alpha$  y  $h_{\mu_1} = h_{\mu_4} = h_{\mu}$ , de forma que

$$A_i \cong h_{h}^{-1} \tag{1-7}$$

Este resultado era de esperar, puesto que se necesitan "dos reflexiones" para ir del emisor de  $T_1$  a la base de  $T_4$ , y en cada reflexión tiene lugar una multiplicación por  $h_{fe}$ .

La impedancia de entrada vista entre la base de  $T_4$  y el emisor de  $T_1$  se calcula fácilmente, como se Indica en la figura 1.11, reflejando la impedancia base-emisor  $h_{in1}$  de  $T_1$  desde el circuito de emisor  $T_4$  al circuito de base de  $T_4$ . El resultado es (suponiendo  $h_{fel} = h_{fel}$ )

$$R_t = h_{m4} + (h_M + 1)h_{m1} ag{1-8}$$

No obstante,  $h_{\rm w} = (h_{\rm fe} + 1)V_T / I_{EQ}$ , luego

$$R_{i} = \frac{(h_{je} + 1)V_{T}}{I_{EO1}} + \frac{(h_{je} + 1)^{2}V_{T}}{I_{EO1}}$$

(1-9)

De la figura 1.10 podemos ver que

$$\frac{I_{EQ1}}{h_{\mu} + 1} = I_{EQ4} \tag{1-10}$$

Combinando las 2 ecuaciones anteriores se obtiene  $R_l$  en función de  $h_{le1}$  o  $h_{le4}$

$$R_i = 2(h_{in} + 1)h_{in} = h_{in} \tag{1-11}$$

De este modo se ha conseguido multiplicar la impedancia de entrada de  $T_1$  por el factor  $2(h_{fe}+1)$ .

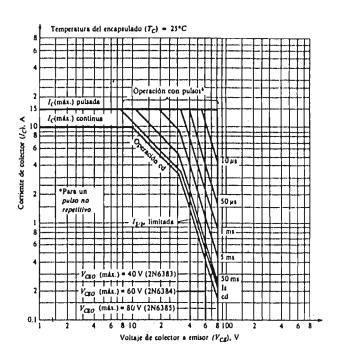

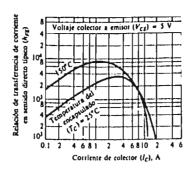

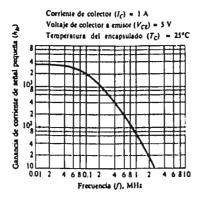

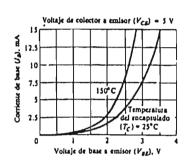

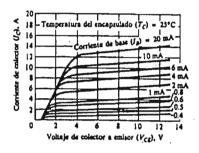

Algunas de las características aparecen en la figura 1.12 a la 1.17. Los datos que se muestran son para la configuración completa - (el valor individual de la  $\beta$  no se especifica). \(^1\) Cabe hacer notar que en las características, el nivel de  $V_{ac}$  se incrementa desde que sufre una calda a través de los dos transistores. Considere también que  $h_{fe}$  está sobre 3000 a 1kHz cayendo hasta únicamente 20 a 2 MHz. La frecuencia va a lener un variación pronunciada.

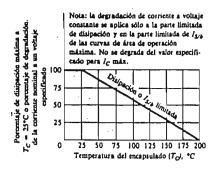

En la figura 1.12 la corriente del colector está en amperes y una operación de pulsos resulta en un incremento del nivel de la corriente - entre más grande (largo) es el pulso, menor es la corriente permitida. En la figura 1.13, se puede notar una caída en la potencia que comienza a la temperatura de 25°C y en la figura 1.14 la β es bastante sensible a la corriente del colector.

El efecto de la frecuencia en la ganancia en a.c. se detalla más en la figura 1.15, comenzando con una fuerte calda a aproximadamente 0.1 Mhz o 100 kHz. En la figura 1.16 se presenta un incremento en el nivel de voltaje  $V_{\rm T}$  (voltaje de corte) debido a los transistores y a la corriente de base en mA (fig. 1.17).

En este caso, se dan los parámetros híbridos y de admitancia.

<sup>&</sup>lt;sup>1</sup> Esto es,  $h_h = I_{C}/I_{B,t}$  por tratar a la combinación del transistor como un circuito unitario.

Fig. 1.12. Area de máxima operación para todos los tipos.

Fig. 1.13 Curva de degradación para todos los tipos.

Fig. 1.14. Características de la  $\beta$  típica para todos los tipos.

Fig. 1.15. Ganancia típica en pequeña señal para todos los tipos.

Fig. 1.16. Características de entrada típica para todos los tipos.

Fig. 1.17. Características de salida para todos los tipos.

# **CAPITULO 2**

# DISEÑO TEÓRICO

En este capítulo se analizarán los circuitos y funcionamientos de ambas técnicas, para así entonces profundizar con toda la teoría necesaria al diseño práctico final.

#### 2.1. El amplificador clase D.

Como se vio en la figura 1.1 del capítulo I, el amplificador se compone de dos transistores complementarios actuando sobre una resistencia de carga  $R_L$ . En esta figura, los transistores están modelados como interruptores ideales. Cuando la señal de control de entrada es negativa el interruptor  $S_1$  se cierra y el  $S_2$  se abre; cuando la señal de control es positiva  $S_1$  se abre y  $S_2$  se cierra. La tensión  $V_L$  en la resistencia de carga es, por tanto, una forma de onda que tiene dos valores posibles,  $V_{\text{abmentacton}}$  ó 0 V.

Nólese que los interruptores no disipan energía, puesto que o blen la corriente a través del interruptor o blen la tensión en él es cero. De ahí que el rendimiento del amplificador sea del 100 por 100 y que el factor de calidad, que es la relación entre la máxima potencia disipada en el interruptor y la máxima potencia disipada en la carga, sea cero.

Normalmente es necesario que la tensión  $V_L$  en la carga sea senoidal, en vez de una onda cuadrada y por eso se emplea usualmente un circuito sintonizado que consiste en una resistencia de carga  $R_L$  y un circuito LC, para eliminar mediante filtrado todos los armónicos de orden superior. Se puede observar que después de este filtrado la tensión en la carga es

$$v_L(t) = \frac{2V_{\text{alimeNaciOn}}}{\pi} \cos \omega_0 t \tag{2.1-1}$$

donde f<sub>e</sub> es la frecuencia de apertura y cierre del interruptor, es decir, la frecuencia de la señal de entrada. Así la potencia útil disipada en la carga es:

$$P_L = \frac{1}{2R_L} \left( \frac{2V_{\text{alimentación}}}{\pi} \right)^2 = \frac{2V^2 \text{alimentación}}{\pi^2 R_L} \approx 0.2 \frac{V^2 \text{alimentación}}{R_L}$$

(2.1-2)

Puesto que la fuente de energia entrega una potencia de  $V^2$  elimentation  $/2R_L$  (durante la mitad del tiempo la fuente no entrega corriente) el rendimiento de este amplificador es realmente sólo del 40 por ciento; el 60 por 100 restante está siendo almacenado en el circuito LC paralelo. Un transistor real no es un interruptor ideal sino que es una resistencia en la zona de saturación. Por tanto, se debería modelar el interruptor como un interruptor ideal incluyendo una resistencia, que denotamos como  $r_s$  en la figura 2.1.1b. Ahora la energía entregada por la fuente es

$$P_{\text{alumentacuou}} = \frac{V^2 \text{alimentación}}{2R_L} \left( \frac{1}{1 + r_s/R_L} \right)$$

Puesto que  $r_{\star} << R_{L}$

(2.1-3)

$$P_{\text{alumentación}} \approx \frac{V^2 \text{alimentación}}{2R_r}$$

(2.1-4)

como antes. Así el rendimiento permanece en aproximadamente el 40 por 100. Ahora, sin embargo, la energia disipada en el transistor (interruptor) no es cero puesto que la resistencia r<sub>s1</sub> disipa energia siempre que S<sub>1</sub> está cerrado. De aquí,

$$P_{\text{interreprise}} = \frac{1}{2} \left( \frac{V_{\text{alimentación}}}{R_I + r_{\text{st}}} \right)^2 r_{\text{st}} \approx \frac{V^2 \text{alimentación} r_{\text{st}}}{2R_I^2}$$

(2.1-5)

puesto que durante la mitad del ciclo no hay corriente en  $r_{s1}$  y también se tiene  $r_{s1} << R_L$ .

El factor de calidad, por lo tanto, es distinto de cero, pero

$$Fac.Cal. = \frac{P_{\text{interrepror}(\text{max})}}{P_L(\text{max})} = \frac{(V^2_{\text{alimentacion}} r_{\text{sl}}) / 2R^2L}{0.2V^2_{\text{alimentacion}} / R_L} = \frac{r_{\text{sl}}}{0.4R_L}$$

(2.1-6)

Fig. 2.1.1. (a) Amplificador de clase D básico empleando interruptores complementarios simétricos; (b) amplificador de clase D con pérdidas resistivas; (c) amplificador de clase D con capacidad además de pérdidas.

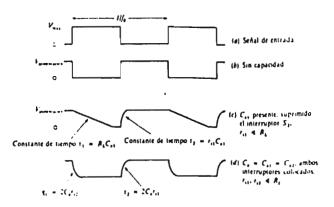

Las figuras 2.1.2a,b y c muestran las formas de onda de tensión en la carga para la señall de entrada que aparece en la figura 2.1.2a. En esta figura se parte de que cuando la tensión de entrada es positiva, S<sub>1</sub> abre y S<sub>2</sub> cierra y viceversa. La figura 2.1.2b muestra la forma de onda ideal de la tensión en la carga si no existiera la capacidad.

La figura 2.1.2c muestra la forma de onda en la salida si se suprime S<sub>2</sub> o está presente la capacidad de salida C<sub>01</sub>. Si la constante de tiempo τ<sub>1</sub>=R<sub>L</sub> C<sub>01</sub> es comparable al periodo de la señal de entrada (T<sub>0</sub>=1/I<sub>0</sub>) la tensión en la carga podría posiblemente no alcanzar los 0 V. Incluso para el caso mostrado en la figura 2.1.2d, vemos que la potencia disipada en la carga, P<sub>L</sub>, ha disminuido significativamente con respecto a la disipada en el caso ideal mostrado en la figura 2.1.2b. Este efecto es, por supuesto, directamente proporcional a la frecuencia de la señal a amplificar. Si

$$\tau_1 I_0 = R_L C_{01} I_0 <<1$$

(2.1-7)

entonces la disminución de P<sub>L</sub> no será significativa.

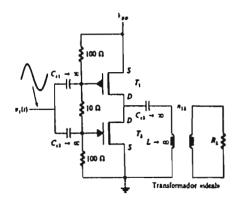

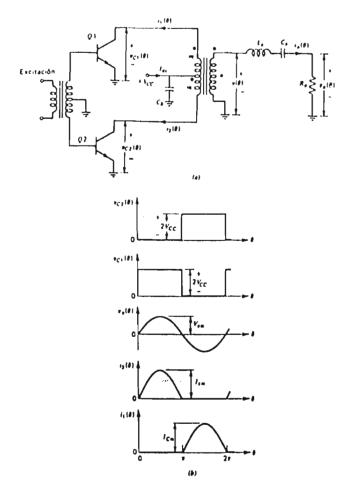

Un amplificador de clase D típico donde la entrada es senoidal se muestra en la figura 2.1.3. T1 y T2 son transistores VMOSFET complementarios simétricos de manera que cuando v(I) es positiva T1 está en corte y T2 está en conducción. La relación de espiras n se selecciona para que la resistencia de carga pueda recibir la tensión y la corriente necesarias.

Pero enfocando el análisis al amplificador clase D de la figura 2.1.4, puede verse un amplificador formado por dos transistores complementarios una vez más, conectados en configuración CE (colector-emisor) y push-pull. La señal de entrada se acopla a las bases mediante un transformador de RF. En el semiciclo positivo del voltaje de entrada, el transistor de arriba se corta, mientras que el de abajo se satura. En el semiciclo contrario, el transistor de arriba es el que se satura mientras el de abajo se corta. Debido a esto, en el circuito sintonizado, se aplica un voltaje que varía entre 0 y +Vcc que se puede representar como

$$v_{c2}(0) = V_{CC} \left[ \frac{1}{2} + \frac{1}{2} s(0) \right]$$

(2.1-8)

Fig. 2.1.2. Formas de onda de tensión en la carga.

Fig. 2.1.3 Amplificador clase D con transistores VMOSFET complementarios.

Donde  $s(\theta)$  es una función de onda cuadrada, cuya amplitud es +1 cuando sen  $\theta$  es positivo y -1 cuando sen  $\theta$  es negativo.

El análisis de Fourier da:

$$s(0) = \frac{4}{\pi} (\sin \theta + \frac{1}{3} \sin 3\theta + \frac{1}{5} \sin 5\theta + \cdots)$$

(2.1-9)

de donde

$$v_{e2}(\theta) = V_{ex}(\frac{1}{2} + \frac{2}{\pi} \sin \theta + \frac{2}{3\pi} \sin 3\theta + \frac{2}{5\pi} \sin 5\theta + \cdots)$$

(2.1-10)

Esta forma de onda representa un conjunto de voltajes que se aplican a la red formada por la resistencia de carga R y el circuito tanque de señe sintonizada ( L<sub>0</sub> y C<sub>0</sub> ). La corriente de salida se determina por la respuesta de esta red a las frecuencias presentes en la forma de onda de conmutación. El capacitor evita que cualquier componente de c.c. aparezca a la salida. Con un Q razonable, la impedancia de entrada del circuito serie sintonizado será muy alta para todas las armónicas de la frecuencia de conmutación; además, los voltajes armónicos en la forma de onda de conmutación son más pequeños que la componente de frecuencia fundamental. Las corrientes armónicas a la salida se reducen así a niveles despreciables, en los que concierne a la operación del amplificador. Sin embargo, se puede requerir un filtrado adicional para reducir corrientes armónicas en la carga y prevenir niveles inadmisibles e interferencia con otras transmisiones.

Si el circuito serie  $L_0$  -  $C_0$  está adecuadamente sintonizado, tendrá reactancia nula a la frecuencia de conmutación fundamental. Por consiguiente, la componente de frecuencia fundamental de la onda cuadrada es directamente aplicada a la carga. Como las corrientes armónicas son despreciables,

$$i_o(\theta) = \frac{2Vcc}{\pi R} \operatorname{sen}(\theta)$$

(2.1-11)

Esta salida de corriente sinusoidal fluye a través de cualquiera de los dispositivos ( $Q_1$  o  $Q_2$ ) que se encuentre encendido en determinado tiempo. En consecuencia, las corrientes de colector son medias sinusoides, con valores pico  $2Vcc/\pi R$ , como se ilustra en la figura 2.1.5c.

La amplitud  $V_{om}$  del voltaje de salida sinusoidal  $v(\theta)$  es  $2Vccl\pi$ , como se ve por inspección de las dos ecuaciones anteriores. La potencia de salida es por lo tanto,

$$P_0 = \frac{V^2_{om}}{2R} = \frac{2}{\pi^2} \frac{Vcc^2}{R} \approx 0.203 \frac{Vcc^2}{R}$$

(2.1-12)

La corriente de entrada en c.c. es el promedio de  $i_1(\theta)$ ; por consiguiente,

$$I_{sk} = \frac{I_{sm}}{\pi} = \frac{2}{\pi^2} \frac{Vcc}{R}$$

(2.1-13)

y la potencia de entrada es

$$P_{i} = VccI_{ik} = \frac{2Vcc^{2}}{\pi^{2}R}$$

(2.1-14)

La capacidad de salida de potencia normalizada se determina normalizando la potencia de salida por el voltaje pico de  $V_{cc}$  y la corriente pico de  $2V_{cc}/\pi R$ , obteniêndose una potencia máxima de  $P_{\rm salit}=1/\pi\approx0.318$ . Como la base de un transistor dado está normalmente polarizado en forma inversa cuando el voltaje de colector es  $V_{cc}$ ,  $BV_{car}$ , se puede usar como especificación de voltaje.

Al comparar la potencia de salida y la entrada, se ve que la eficiencia es del 100%. Esto no debe sorprender, pues los dispositivos tienen voltaje 0 cuando conducen corriente, y 0 corriente cuando tienen voltaje no nulo. La potencia de salida de la misma configuración de circuito, operado en clase B es del 78.5% de la salida de potencia en clase D y se puede pensar que un amplificador de potencia clase D entrega a la carga la potencia que disiparla un amplificador de potencia clase B.

Fig. 2.1.4. Amp. de Potencia clase D de conmutación de voltaje complementario. (a) Circulto; (b) circuito equivalente y (c) formas de onda.

Fig. 2.1.5. Amp. de Potencia clase D de conmutación de voltaje acoplado a transformador. (a) circuito y (b), formas de onda.

Deben observarse dos puntos al diseñar este tipo de amplificador clase D. En primer lugar, siempre se deben incluir un capacitor de puenteo como se ve en la figura 2.1.4a.

Puede emplearse una bobina serie en la línea de alimentación para filtrado adicional, aunque no puede conectarse a  $Q_1$  sin un capacitor de puenteo, pues la corriente que toma el  $Q_1$  es una parte de la corriente de salida sinusoidal. En segundo, un circuito de salida sintonizado serie ( o un equivalente, como una red T), se debe usar en lugar de un circuito de salida sintonizado paralelo ( o un equivalente, como una red  $\pi$ ). La acción conmutadora de  $Q_1$  y  $Q_2$  impone una forma de onda de voltaje cuadrado, mientras que un circuito sintonizado paralelo demandaría un voltaje sinusoidal. Para un circuito sintonizado serie simple, un Q de 5 representa buen compromiso entre evitar corrientes armónicas y la pérdida de la bobina. Se puede obtener una supresión adicional de armónicas (superior a la dada por el circuito serie sintonizada) insertando filtros normales (tales como los usados con los amplificadores de potencia clase B) entre el circuito serie sintonizado y la carga.

La eficiencia de este diseño como en el anterior radica en que cada transistor permanece saturado durante casi 180º en cada ciclo de señal. Los transistores no operan como fuentes de corriente, sino más bien como interruptores. Cuando un transistor está saturado, disipa una potencia Igual a:

$$P_{D} = V_{CE(SAT)}I_{C(SAT)}$$

(2.1-15)

Y este valor es muy bajo porque  $V_{\text{CE(SAT)}}$  es casi cero. Por otra parte, cuando el transistor está en corte  $P_D$  es idealmente cero. La disipación media del transistor durante el ciclo completo es, pues, muy pequeña y la eficiencia de la etapa se acerca al 100 por ciento.

#### II.1.1. Consideraciones prácticas sobre la amplificación en clase D.

En la sección anterior se estudió la operación de un amplificador de potencia clase D idealizado, dentro de un medio también ideal. En esta se examinan algunas consideraciones prácticas de diseño, incluyendo los efectos de reactancia de carga, requerimientos de alimentación y los efectos de capacitancia de derivación y voltaje de saturación y resistencia.

#### Cargas reactivas.

Un amplificador de potencia clase D complementario de conmutación de voltaje, cuya carga contenga una reactancia jX a la frecuencia fundamental (fig. 2.1.6a). Como antes, en lo que concierne a la operación del amplificador, el circuito serie sintonizado reducirá las corrientes de salida en frecuencias armónicas hasta niveles despreciables. La forma de onda de voltaje de colector queda sin modificar por la reactancia de carga, pero la corriente de salida (y el voltaje) se desplazan en fase relativa a la forma de onda de voltaje de colector, como se muestra en la figura 2.1.6b. En virtud del corrimiento de fase, las  $i_1(\theta)$  e  $i_2(\theta)$  de la figura 2.1.4b tenderán a ser negativas durante una porción del ciclo de RF.

Si se usan dispositivos VMOS para los Q1 y Q2, puede pasar la corriente de dren positiva sin daño. Sin embargo, los transistores bipolares no conducen, en general, en la dirección inversa. Si no se proporciona una trayectoria para la corriente de dirección inversa, cargará a la capacitancia parásita Cs. produciendo un impulso parásito de voltaje elevado que puede dañar a los transistores. Una trayectoria adecuada para la corriente inversa la dan los diodos D1 y D2 de la figura 2.1.6a. La corriente de salida, sinusoidal, pasará entonces por uno de los cuatro dispositivos (Q1, Q2, D1 y D2), como se ve en la figura 2.1.6b. Los BJT, usados en un amplificador de potencia clase D acoplado por transformador se pueden proteger en forma semejante mediante diodos conectados de los emisores a los colectores. Los dispositivos utilizados en estos amplificadores clase D en conmutación de corriente puede protegerse de los voltajes negativos de colector colocando diodos en serie con los colectores.

Fig. 2.1.6. Amplificador clase D con carga reactiva. (a) Circuito y (b), Iormas de onda.

Una reactancia en serie con la carga también reduce la amplitud de la corriente de salida. Si Z=R + jX, la potencia de salida de un amplificador de potencia complementario en conmutación de voltaje se reducirá a

$$P_a = \frac{2}{\pi^2} \frac{V^2_{cc}}{Z^2 / R} = \frac{2}{\pi^2} \frac{V^2_{cc}}{\rho R}$$

(2.1-16)

donde  $\rho=|Z|/R$ . La eficiencia de un amplificador clase D queda esencialmente sin cambio por la reaclancia de carga.

#### Excitación.

Los circuitos de excitación de un amplificador de potencia clase D tienen mucho en común con los de clase B. No obstante, como en un amplificador clase D no se requiere operación lineal de dispositivo ni corriente estable, rara vez se usa polarización de base o compuerta. La señal de excitación debe ser suficiente para asegurar que los dispositivos se saturen y se corten durante las partes adecuadas del ciclo de RF; los procedimientos de diseño generalmente suponen condiciones de caso peor en ganancia, temperatura y otros parámetros. Así, aunque un amplificador de potencia en conmutación de corriente se debe energizar con una señal de onda cuadrada, uno en conmutación de voltaje se puede excitar con una señal de onda cuadrada o con una sinusoidal. Esta última es por lo común la que se prefiere, pues toma menos potencia y reduce el tiempo relativo de almacenamiento del BJT con la relación al correspondiente cuando se usa excitación de onda cuadrada.

#### Resistencia y voltaje de saturación.

El voltaje de saturación de los BJT afecta a la amplificación clase D de la misma manera como lo hace con otras clases de operación. El voltaje de alimentación Vcc se sustituye por uno efectivo  $V_{\rm eff}$  en todos los cálculos, salvo para la potencia de entrada. Para las configuraciones clase D acopladas a transformador,  $V_{\rm eff} = V_{\rm CC} - V_{\rm sat}$ , mientras que para la

configuración complementaria, es  $V_{eff} = V_{cc} - 2V_{sat}$ . La eficiencia se reduce del 100 por ciento a  $V_{eff} / V_{cc}$ .

Las configuraciones complementarias y de conmutación de voltaje acoplado por transformador colocan la resistencia  $R_{on}$  de encendido del FET efectivamente en serie con la R de carga de dren. Por consiguiente, como para un amplificador de potencia en clase  $B = V_{eff} = V_{DO}R / (R + R_{on})$  se usa en lugar del  $V_{DO}$  en todos los cálculos, excepto para el voltaje de entrada y de dren de pico, que es  $2V_{DO}$  en vez de  $V_{DO} + V_{eff}$ . La última desviación del uso de  $V_{eff}$  con el amplificador clase B se presenta porque el voltaje de dren se lleva a cero cuando la corriente de dren es cero.

La configuración clase D en conmutación de corriente difiere de las configuraciones para conmutación de voltaje colocando  $R_{on}$  de encendido del FET efectivamente en la trayectoria de  $I_{oc}$  y np en la de  $I_{O}(0)$ . En consecuencia

$$V_{eff} = V_{DD} \frac{R_{sk}}{R_{sk} + R_{out}}$$

(2.1-17)

donde  $R_{\infty} = 8 R/\pi^2$  es la resistencia de un amplificador ideal que ve de la fuente de alimentación.

#### Capacitancia en paralelo o inductancia en serie.

La conmutación de una amplificador de potencia clase D se pone en derivación generalmente por una capacitancia pequeña  $C_s$ . Esta capacitancia está formada por la  $C_{ob}$  los transistores y la capacitancia de los circuitos parásitos. Cada vez que se enciende el Q1, el  $C_s$  en esencia se carga instantáneamente hasta  $V_{eff}$  (o hasta  $V_{DD}$  si Q1 es un FET). Cada vez que enciende Q2, se disipa la potencia almacenada en  $C_s$ . Como esto ocurre una vez cada ciclo de RF, la potencia consumida es

$$P_{i} = C_{i} V^{2}_{ig} f = \frac{1}{2\pi} B_{i} V^{2}_{ig}$$

(2.1-18)

configuración complementaria, es  $V_{\text{eff}} = V_{\text{cc}} - 2V_{\text{tel}}$ . La eficiencia se reduce del 100 por ciento a  $V_{\text{eff}} / V_{\text{cc}}$ .

Las configuraciones complementarias y de conmutación de voltaje acoplado por transformador colocan la resistencia  $R_{on}$  de encendido del FET efectivamente en serie con la R de carga de dren. Por consiguiente, como para un amplificador de potencia en clase  $B = V_{eff} = V_{D0}R / (R + R_{on})$  se usa en lugar del  $V_{D0}$  en todos los cálculos, excepto para el voltaje de entrada y de dren de pico, que es  $2V_{D0}$  en vez de  $V_{D0} + V_{eff}$ . La última desviación del uso de  $V_{eff}$  con el amplificador clase B se presenta porque el voltaje de dren se lleva a cero cuando la corriente de dren es cero.

La configuración clase D en conmutación de corriente difiere de las configuraciones para conmutación de voltaje colocando  $R_{\rm on}$  de encendido del FET efectivamente en la trayectoria de  $I_{\infty}$  y np en la de  $I_{0}(9)$ . En consecuencia

$$V_{eff} = V_{DD} \frac{R_{dc}}{R_{dc} + R_{dc}}$$

(2.1-17)

donde  $R_{oc}$  = 8  $R/\pi^2$  es la resistencia de un amplificador ideal que ve de la fuente de alimentación.

#### Capacitancia en paralelo o inductancia en serie.

La conmutación de una amplificador de potencia clase D se pone en derivación generalmente por una capacitancia pequeña C<sub>s</sub>. Esta capacitancia está formada por la C<sub>∞</sub> los transistores y la capacitancia de los circuitos parásitos. Cada vez que se enciende el Q1, el C<sub>s</sub> en esencia se carga instantáneamente hasta V<sub>eff</sub> (o hasta V<sub>DO</sub> si Q1 es un FET). Cada vez que enciende Q2, se disipa la potencia almacenada en C<sub>s</sub>. Como esto ocurre una vez cada ciclo de RF, la potencia consumida es

$$P_{i} = C_{i}V^{1}_{eff} f = \frac{1}{2\pi} B_{i}V^{1}_{eff}$$

(2.1-18)

donde B, representa la susceptancia de C, a la frecuencia de operación. Observar que C, produce un incremento en la potencia de entrada, pero no cambia la de la salida.

Si el amplificador de potencia clase D en conmutación de voltaje acoplado por transformador tiene una capacitancia C, en derivación con los dos Q1 y Q2, ambas capacitancias paralelo deben cargarse hasta 2 V<sub>ef</sub> una vez cada cicio, por lo que

$$P_{s} = C_{s} (2V_{eff})^{1} (2f) = 8C_{s} V^{1}_{eff} f = \frac{4}{\pi} B_{s} V^{1}_{eff}$$

(2.1-19)

Una comparación rápida de esta ecuación con la anterior parece indicar que la configuración complementaria es más eficiente que la acoplada por transformador. Sin embargo, como la segunda distribuye la misma capacitancia total de derivación a dos posiciones y opera a la mitad del voltaje de línea utilizado por la anterior (para las mismas especificaciones y salida) la pérdida de potencia total es casi la misma para ambas.

Una inductancia de L<sub>e</sub> (debida a la longitud de conductores y el transformador) en serie con las terminales de colector en un amplificador de potencia ciase D en conmutación de corriente, da lugar a una reducción análoga en la eficiencia. Dos veces durante cada ciclo de RF la corriente en una inductancia L<sub>e</sub> debe cambiar de 0 a L<sub>e</sub> instantáneamente, consumiendo

$$P_{i} = (\frac{1}{2} L_{i} I_{i}^{1})(2f) = L_{i} I_{i}^{1} f = \frac{1}{2\pi} X_{i} I_{i}^{2} = I_{i}^{2} R_{i}$$

(2.1-20)

donde X, es la reactancia de L, a la frecuencia f. Este hecho opera como una resistencia R, en serie con la fuente de c.c. y por consiguiente reduce las potencias de entrada y salida, así como la eficiencia.

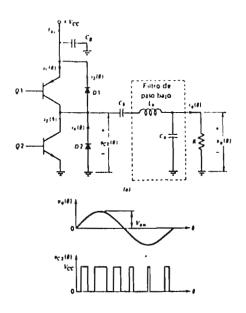

## 2.2. Amplificación en clase S.

En esta clase de amplificación, la forma de onda de voltaje rectangular se aplica a un filtro de paso bajo, que permite que sólo aparezca en la carga su componente de voltaje c.c. (de variación lenta) o su componente promedio de voltaje. Las anchuras de pulso de diferentes tasas de operación producen salidas promedio diferentes; la variación controlada de la anchura de pulso origina entonces que la salida varle para dar lugar a una señal deseada. La eficiencia de un amplificador clase S ideal es del 100 por ciento.

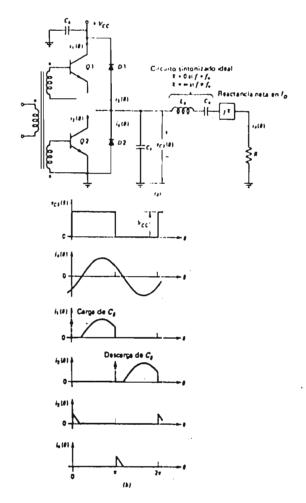

Las configuraciones de circuito para amplificadores clase S y modulares son muy semejantes. En cualquiera de ellas, la componente promedio de variación lenta o de c.c. de la forma de onda de voltaje  $v_{cr}(\theta)$  o  $v_{o}(\theta)$  se acopía a la carga R mediante un filtro paso bajo  $L_{o}$ - $C_{o}$ , originando el voltaje de salida  $v_{o}(\theta)$  y la corriente de salida  $i_{o}(\theta)$ . (El filtro de paso bajo tiene un inductor de entrada y por lo tanto una impedancia alta a la frecuencia de conmutación y sus armónicas, evitándoles generar corrientes importantes.) La corriente de salida  $i_{o}(\theta)$  se produce por la aplicación del voltaje de salida  $v_{o}(\theta)$  a la carga R; la  $i_{o}(\theta)$  se extrae mediante el filtro pasabajas y, en un tiempo dado, por uno de los transistores o diodos de conmutación. Un amplificador (figura 2.2.1) produce una corriente de salida que puede ser positiva o negativa; se requieren entonces de dos transistores y dos diodos, como se muestra. Un modulador (figura 2.2.2) produce sólo corriente de salida y, por lo tanto, necesita sólo un transistor y un diodo (como requiere un regulador de conmutación). El capacitor de bloqueo  $C_{\rm b}$  de c.c. en el amplificador se puede eliminar si se dispone de fuentes de poder positivas y negativas.

El voltaje de salida del modulador puede tener cualquier valor entre 0 y Vcc. En consecuencia, la salida pico de un modulador clase S es simplemente

$$P_{0(\text{mod})} \le \frac{Vcc^2}{R} \tag{2.2-1}$$

En el amplificador mostrado,  $V_{\text{out}} \le 1/2Vcc$  y para señales sinusoidales.

$$I_{0(\omega n p)}^{\prime} = \frac{V_{\omega n}^{-1}}{2R} \le \frac{V c c^{2}}{8R}$$

(2.2-2)

Fig. 2.2.1. Amplificador clase S. (a) Circuito y (b) , formas de onda.

En cualquier caso, los dispositivos activos no experimentan nunca voltaje y corriente no nulos simultáneamente; de tal suerte que el amplificador y el modulador son en teoria eficientes en un 100 por ciento.

El amplificador clase S, como otros de conmutación, tiene una eficiencia menor del 100 por ciento a causa de los efectos de voltaje y resistencia de saturación, de capacitancia en derivación y del tiempo nulo de transición. Los efectos de los tres primeros pueden tratarse de la misma manera en que se analizaron en el amplificador clase D. El voltaje de saturación se maneja usando  $V_{eff} = V_{CC} - V_{uu}$  y la resistencia de saturación es equivalente a un resistor en serie con la carga. Así,  $V_{eff} = V_{DD}R/(R+R_{un})$ . Cada transición del conmutador carga a la capacitancia de derivación y la (2.1-18) se puede usar directamente con amplificadores o moduladores clase S que tengan una fuente única de +  $V_{CC}$ . La operación de un amplificador clase S con  $\pm V_{CC}$  duplica el número de transistores para los que se saca corriente de carga de la fuente y requiere así duplicar la potencia disípada (y  $R_{\rm e}$ ) dada por (2.1-18).

Los efectos del tiempo de transición sobre la eficiencia pueden analizarse aproximadamente en forma semejante a la que se usó para el amplificador clase D. Sin embargo, como difieren las formas de onda de corriente, las fórmulas establecidas para el amplificador clase D no se aplican a la clase S. En general, la corriente de salida es esencialmente constante durante el tiempo de transición. Si se suponen voltajes y corrientes de transición lineal, la potencia disípada en una transición es

$$P_{dT} = \theta_1^2 V_{CC} i_0 / 4\pi, \qquad (2.2-3)$$

donde  $0_s$  es el tiempo de transición convertido a radianes (a la frecuencia de conmutación) e  $i_0$  es el valor de la corriente de salida en la transición que se estudia.

Como hay dos transiciones en cada ciclo de la frecuencia de conmutación, la potencia promedio disipada (sobre un ciclo de la señal que va a ser amplificada) es

$$P_{d} = \frac{\theta_{s}^{2}}{4\pi} V_{CC} A \tag{2.2-4}$$

Fig. 2.2.2. Modulador clase S. (a) Circuito y (b), formas de onda.

donde A indica el promedio del valor absoluto de la corriente de salida. Para un amplificador con una corriente sinusoidal,  $A=V_{cc}/\pi R$ ; para un modulador con salida sinusoidal rectificada de onda completa ( esto es,  $i_{\theta}(\theta)=V_{cc}|\sin\theta|/R$  ),  $A=2V_{cc}/\pi R$ . Para un modulador con una salida de onda senoidal elevada (  $i_{\theta}(\theta)=V_{cc}(1+\sin\theta)/2R$  ).

A= A=2  $V_{cc}/2R$ . Se puede usar un voltaje efectivo de  $V_{eg}=V_{cr}P_0/(P_0+P_d)$  - (2.2-4a) para incluir aproximadamente los efectos de  $P_d$ .

#### 2.2.1. Modulación de anchura de pulso.

La modulación de anchura de pulso (PWM: pulse-width modulation) requerida para la amplificación clase S, se puede realizar mediante tres técnicas. La primera usa un comparador de voltaje y se trata a continuación; la segunda utiliza un multivibrador astable, en el cual las corrientes de carga varían diferenciadamente (es decir, una aumenta mientras la otra decrece); la tercera técnica, que se usa en reguladoras de conmutación, compara la salida del filtro con la señal de entrada y activa al conmutador si la diferencia entre los dos voltajes excede de un valor establecido.

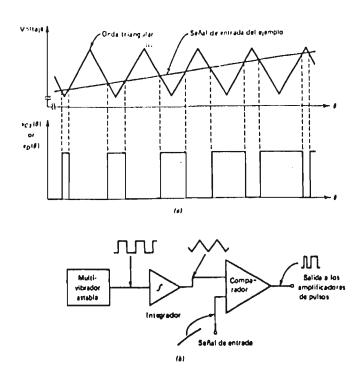

En la figura (2.2.3) se muestra el método de comparador para la producción de la PWM. La señal de entrada y onda triangular periódica a la frecuencia de conmutación se aplican a un comparador. El comparador produce una salida "alta" cuando la señal de entrada es mayor que la onda triangular y una salida "baja" en el caso contrario. El resultado es que la anchura de los pulsos "altos varía linealmente con la amplitud de la señal de entrada.

La linealidad de este método de PWM depende de la habilidad del comparador para reaccionar con rapidez frente a cambios en sus entradas y de la linealidad de la onda triangular. Esta onda triangular puede suministrarse directamente de un circuito integrado generador de funciones, u obtenerse por integración de la salida de onda cuadrada de un multivibrador astable. Un integrador activo es generalmente más lineal, pero un integrador RC simple es menos costoso y consume menos potencia.

Fig. 2.2.3. Generación de PWM con un comparador. (a) Formas de onda y (b), diagrama de bloques.

Si se usa un integrador RC, existirá un compromiso entre amplitud y la linealidad de la onda triangular. Una sección de ascenso de la onda triangular se puede describir por

$$v_r(t) = Vcc(1 - e^{\frac{-t}{RC}}) = Vcc(\frac{t}{RC} - \frac{t^3}{2!R^3C^3} + \frac{t^3}{3!R^3C^3} - \cdots)$$

(2.2-5)

Mientras t<< RC, el voltaje pico a pico de la onda triangular es simplemente el primer término en la ecuación anterior con *t*=1/2/s. De modo similar el segundo término representa la diferencia respecto a una onda triangular ideal y, consecuentemente, la distorsión. Es evidente que la razón de la distorsión del voltaje entre crestas mejora en la medida que el voltaje de salida decrece.

#### Distorsión inherente en la modulación por anchura de pulso.

La PWM produce inherentemente alguna distorsión de la señal moduladora (cuando se recupera con el filtrado de paso bajo) aun si el modulador produce pulsos perfectamente cronometrados. La razón de esto puede encontrarse en la serie de Fourier de la expansión e I tren de pulsos. Si y en radianes representa la anchura media del pulso ( $y = \pi/2$  representa un 50 por ciento de la razón de operación), entonces

$$v_{c_2}(0) = Vcc \frac{y}{\pi} + \sum_{k=1}^{\infty} \frac{\sin ky}{k} (\cos \frac{k\pi}{2} \sin k\theta + \sin \frac{k\pi}{2} \cos k\theta). \tag{2.2-6}$$

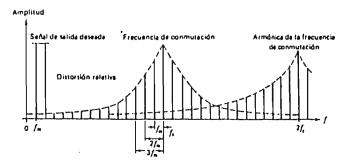

El modulador de anchura de pulso hace variar a y linealmente con la señal de entrada; en consecuencia, el primer término en la ecuación anterior varia linealmente con la señal de entrada. Sin embargo, la variación resultante (modulación) de la frecuencia de conmutación y sus armónicas es inherentemente no lineal, dando lugar a la generación de bandas laterales espurias, como se muestra en la figura (2.2.4). Como alguna de estas bandas laterales debe caer en la banda de paso de la señal, cierta distorsión es inherente al proceso de la PWM.

Fig. 2.2.4. Espectro de la señal PWM.

Fig. 2.2.5. Distorsión en PWM. Observar que las marcas se refieren a la frecuencia de producto en la figura 2.2.4

Si la señal de entrada es una sinusolde única, con la amplitud  $V_{\rm res} \le 1/2 Vcc$ , la magnitud del producto espurio *enésimo* asociado con la armónica k-ésima de la frecuencia de conmutación (ver la figura 2.2.4) será:

$$V_{1,n} = \frac{2V_{CC}}{k\pi} J_n(k\pi \frac{V_{om}}{V_{CC}})$$

(2.2-7)

Aquellos productos espurios, cuyas frecuencias ( $kf_s - nf_{ml}$ ) caigan dentro de la banda de paso del filtro de salida, aparecerán en la carga como distorsión. Las magnitudes de estos productos se pueden calcular usando las tablas de funciones de Bessel originarias y los valores seleccionados de la razón entre los productos de distorsión y la señal de entrada, como se muestra en la figura 2.2.5. En esta figura, es obvio de inmediato que la reducción del "Indice de modulación" (la razón entre  $V_{com}$  y  $V_{CX}$ ), mejora la razón de distorsión a señal aunque sólo puede usarse limitadamente este recurso para no desperdiciar las posibilidades de salida del dispositivo. (La mayoría de los amplificadores clase S usan variación del 10 al 90 por ciento o del 0 al 90 por ciento de ciclo de trabajo). Es también evidente que el incremento en la frecuencia de conmutación da lugar a un descenso rápido en la magnitud de la distorsión.

Aunque hay muchos productos de distorsión que pasan dentro de una banda de paso de salida dada, sólo debe de considerarse, en la mayoría de los diseños, el producto de más bajo orden debido a la frecuencia de conmutación (k=1). Esto puede justificarse suponiendo que  $f_3 = 3f_{m1}$  y comparando las magnitudes de los productos  $f_3 - 2f_{m2}$ ,  $2f_3 - 5f_{m2}$ , y  $3f_3 - 8f_{m3}$ , todos de la misma frecuencia  $f_m$ . En muchas aplicaciones de amplificadores de audio y modulares, donde es adecuado un nivel de distorsión de -40 dB, la  $f_3$  debe ser precisamente 5 veces la  $f_m$  (o la más alta frecuencia que vaya a amplificarse).

#### II.2.2. Consideraciones sobre filtro de salida y frecuencia de conmutación.

El filtro de salida debe pasar la señal de salida que no exceda magnitudes de amplitud y distorsión de fase especificadas. Al mismo tiempo, debe atenuar la frecuencia de conmutación y sus armónicas, hasta un nivel aceptable. Debe presentarse a estas frecuencias una alta impedancia de entrada (5 a 10 veces la R) para evitar que extraigan corrientes a través

de los dispositivos de conmutación; por esta razón, el filtro de salida debe tener un inductor en serie en su entrada. El filtro se puede diseñar usando técnicas ordinarias, teniendo presente que la impedancia de fuente es cero. Puede diseñarse un filtro de dos secciones ( $L_0$  -  $C_0$  en las figuras 2.2.1 y 2.2.2) mediante el uso de tres relaciones: primera, la frecuencia  $f_0$  en la cual  $L_0$  y  $C_0$  resuenan, es la frecuencia "esquina" o de corte en un diagrama de Bode de línea recta, segunda, un factor de atenuación de  $\zeta$ =0.707= $\sqrt{L_n/C_a}$  dará una banda de paso suave sin pico resonante y una atenuación de -3 dB con un corrimiento de fase de 90° en  $f_0$ . Tercera, la atenuación de filtro de dos polos es 40 dB por década de frecuencia arriba de  $f_0$ .

La distorsión máxima permisible, el Indice de modulación máximo y la componente de frecuencia máxima en la señal que se va a amplificar, determinan un mínimo para la frecuencia de conmutación. La atenuación requerida de la frecuencia de conmutación y el número de polos en el filtro de salida y su frecuencia de corte, determinan un segundo mínimo para la frecuencia de conmutación. En general, se deben hacer algunas modificaciones entre una frecuencia de conmutación más baja y más elementos en el filtro de salida.

# CAPITULO 3 DISEÑO PRÁCTICO

En este capítulo, se desarrolla práctica y fisicamente el amplificador clase S, con base en los dos capítulos anteriores, lo cual implica un constante reemplazo de materiales, ya que va dependiendo de los resultados y mediciones que se obtienen o de nuevos elementos que van apareciendo en el mercado a la fecha de la elaboración de cada etapa del amplificador.

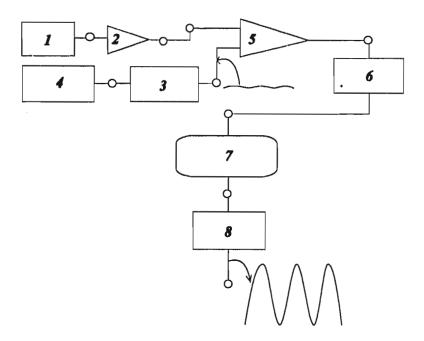

# 3.1. Diagrama de bloques y descripción general.

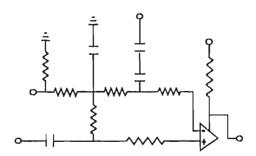

En el diagrama 3.1.1 se muestra el diagrama general de bloques del diseño del amplificador clase S que se realizará para este proyecto de tesis, explicándose posteriormente ta función de cada uno de los elementos de los bloques así como la justificación de su uso.

DIAGRAMA 3.1.1. Diagrama general de bloques del amp. clase S.

- Circuito generador de pulsos: tiene por objetivo como su nombre lo dice, generar una señal cuadrada, con una frecuencia de 50 kHz y lo más angulada posible.

- Circuito integrador: la función de éste es la de integrar la función cuadrada y dar origen a una señal triangular lineal.

- 3. Circuito preamplificador de baja potencia: este circuito únicamente amplifica de 5 a10 veces, la señal de entrada a amplificar, debido a su bajo voltaje (mV).

- 4. Filtro pasivo simple para frecuencias altas y bajas: Este filtro tiene el objetivo de controlar el paso de altas y bajas frecuencias no deseables a la salida, dependiendo de la aplicación, ya que al variar el grado de amplificación, en ocasiones se llega a un grado de saturación y/o deformación de la señal amplificada.

- 5. Circulto comparador: en esta etapa se comparan la señal triangular con la señal de entrada a amplificar, generando una señal de pulsos positivos (digital), con una cierta modulación proporcionada por la señal de entrada.

- 6. Preamplificador de media potencia: el objetivo de este amplificador es incrementar el voltaje de la señal de salida de la etapa anterior, ya que debido a los límites de voltaje de los circuitos integrados (5-12 V.), el voltaje es bajo para los requerimientos de entrada de la siguiente etapa.

- 7. Circuito amplificador principal de pulsos de alto voltaje: esta es la etapa principal de salida de todo el amplificador clase S, en la cual se encuentran los transistores de potencia.

- 8. Filtro pasivo de paso bajo: siendo ésta la última etapa, tiene la función de eliminar señales parásitas (altas frecuencias) y sus armónicas, que contiene la señal de salida amplificada.

# 3.2. Descripción técnica de cada uno de los elementos de los bloques del amplificador clase S.

#### 1. Circuito Generador de Pulsos - Multivibrador Astable,

Debido a la alta eficiencia que se desea obtener a la salida, se requiere de un generador de alta eficiencia a la entrada, que consuma poca potencia (que evite el consumo excesivo de corriente) y que soporte frecuencias de 50 kHz. o más sin llegar a la saturación o problemas físicos propios del circuito.

Es por lo que se utilizó el chip CMOS (complementary MOS) 4011 con la siguiente configuración.

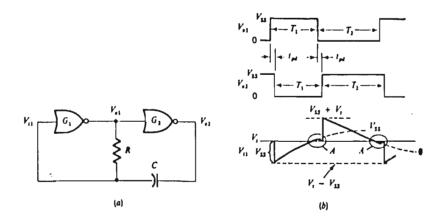

Entonces se requiere de un multivibrador astable, que se utiliza para generar un tren de impulsos de reloj y que consiste básicamente en un oscilador biestable sin estados estables. La figura 3.1.1a representa un multivibrador astable formado con compuertas NO·O. Las formas de onda de la figura 3.1.1b son para CMOS, pero también se pueden emplear puertas ECL.

El funcionamiento del reloj se explica más fácilmente partiendo de la tensión  $V_{01}$  que sube desde 0 V hasta  $V_{55}$ . Después de un retardo  $t_{pd}$ ,  $V_{07}$  disminuye y  $V_{11}$  cae instantáneamente a  $V_{55}$ . En este punto,  $V_{01} = V_{55}$ . Supongamos que  $V_{11}$  estaba inicialmente en la tensión de umbral por lo que después de haber disminuido en la cantidad  $V_{55}$ ,  $V_{11} = V_{1} - V_{55}$ . Seguidamente, se comprueba que esto es lo que ocurre. Ahora el condensador se carga para hacer que  $V_{11} = V_{55}$  por lo que la corriente en R se anula. La ecuación de carga es:

$$V_{i1} = (V_i - V_{SS}) + (2V_{SS} - V_i)(1 - \varepsilon^{\frac{-i}{RC}})$$

(3.2-1)

El ciclo de carga termina cuando  $V_0 = V_0$ , es decir, después de un tiempo

$$T_1 = RC \ln \frac{2V_{SS} - V_t}{V_{SS} - V_t}$$

(3.2-2)

En este estado, la puerta  $G_1$  pasa a conducción y al cabo de un tiempo  $\ell_{pd}$ ,  $V_{01}$  disminiuye hasta 0 V. Después de un retardo adicional  $V_{02}$  aumenta hasta  $V_R$ . La tensión en C salta ahora desde  $V_1$  hasta  $V_1 + V_{SS}$  y, puesto que  $V_{01} = 0$  V, el condensador se descarga y  $V_{11}$  disminuye hasta 0 V. La ecuación de esta descarga es

$$V_{t1} = (V_{SS} + V_T) e^{\frac{-t}{RC}} \tag{3.2-3}$$

Cuando  $V_{ij} = V_{ij}$ , es decir, cuando  $t = T_{2i}$ , donde

$$T_2 = RC \ln \frac{V_{SS} + V_t}{V_t}$$

(3.2-4)

la puerta  $G_2$  pasa a corte y al cabo de un tiempo  $t_{pd}$ ,  $V_{01}$  sube hasta  $V_{SS}$ . Después de un retardo  $t_{pd}$ ,  $V_{02}$  cae hasta  $0 \vee y V_{11}$  cae desde  $V_1 - V_{SS}$ , lo que verifica nuestro supuesto inicial.

Esta operación carga-descarga continúa indefinidamente y, por lo tanto, el periodo de oscilación es

$$T_p = V_1 + V_2 \tag{3.2-5}$$

Es importante considerar el comportamiento de  $V_{i1}$  durante el intervalo de tiempo  $2t_{pd}$  después de que alcanza el valor umbral. Estas regiones están marcadas por circulos y letras  $\mathcal{A}$  en la figura 3.1.1b. Durante un período de tiempo  $t_{pd}$ , el umbral  $V_{01}$  no cambia por lo que el condensador continúa cargándose o descargándose según el caso. Sin embargo, el intervalo  $t_{pd}$  a  $2t_{pd}$ ,  $V_{01}$  ha cambiado de estado, pero  $V_{02}$  todavía no lo ha hecho. En esta región el condensador invertirá su sentido de carga, como muestra la figura.

Fig. 3.1.1. (a) Multivibrador astable formado por compuertas NO-O, (b) formas de onda.

#### 2. Circuito integrador,

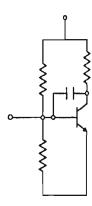

Después de obtenida la señal de pulsos cuadrada, con alta estabilidad y una frecuencia de 50 kHz., se requiere de un circuito integrador en el cual no se pierda la linealidad y no varle por causas externas como la temperatura o propiedades de los elementos que lo constituyen. En esta etapa se utilizó el transistor bipolar NPN 2N2222, para llevar a cabo la integración de la señal.

El circuito se muestra en la figura.

## 3. Circuito Preamplificador de Baja Potencia (mV).

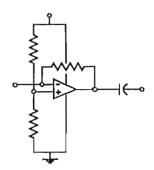

Esta etapa requiere de una amplificación sin pérdidas, es decir que no altere ni distorsione la señal de entrada (voltajes muy pequeños), por lo que se decidió usar un amplificador operacional (OP-AMP), que como se sabe es lo más estable y la ganancia (grado de amplificación), no depende de la fuente de alimentación.

Para esta etapa se empleó el OP-AMP 741 por sus características y los rangos a los cuales trabaja, lo cual se lista a continuación:

#### Características mínimas tipicas del 741:

+ Voltaje de offset a la entrada¹ : 2 a 6 mV.

+ Resistencia a la entrada: .3 a 2 MΩ.

+ Ganancia de voltaje: 20,000 a 200,000.

+ Radio de exclusión en modo común²: 70 a 90 dB.

+ Ancho de banda¹: .5 a 1.5 Mhz.

+ Grado de reacción<sup>4</sup>: 0.5 V/μs.

+ Alimentación de corriente: 1.7 a 2.8 mA.

+ Consumo de energía: 50 a 85 mW.

#### Rangos máximos del 741:

+ Alimentación de voltaje: +/- 18 V.

+ Disipación de energla: 500 mW.

+ Voltaje diferencial a la entrada: +/- 30 V.

+ Voltaje a la entrada<sup>5</sup>: +/- 15 V.

+ Tiempo de corto circuito a la salida: Indefinido.

+ Temperatura de operación: 0° C a 70° C

Para esta etapa fue necesario aplicar el 741 en alimentación positiva (una polaridad) y no en su forma simétrica (positiva y negativa), como es su forma común, con objeto de simplificar la etapa de alimentación general de todo el circuito amplificador.

¹ Voltaje de offset a la entrada: hace referencia al voltaje de salida del OP-AMP, en el momento en que no hay voltaje a la entrada, el cual debe ser idealmente 0.

<sup>&</sup>lt;sup>2</sup> Radio de exclusión en modo común: es una medida de la habilidad del OP-AMP para rechazar una señal simultáneamente aplicada a la entrada positiva y a la entrada negativa.

<sup>&</sup>lt;sup>3</sup> Ancho de banda: es el rango de frecuencias a por las cuales va a funcionar. La frecuencia a la cual la ganancia cae a 1 es la frecuencia de ganancia unitaria.

Grado de reacción (siew rate): es la razón de cambio en la salida del OP-AMP en volts por microsegundos cuando la ganancia es 1.

<sup>5</sup> El voltaje a la entrada no debe exceder la alimentación de voltaje cuando ésta es menor que +/- 15 volts.

C1 es aproximadamente  $1/(2\pi f_{BAJA}R1)$ . Donde  $f_{BAJA}$  es la frecuencia baja de corte o 300 Hz. para el circuito mostrado.

La salida de un OP-AMP alimentado simétricamente puede fluctuar arriba y abajo de 0 volts (tierra); pero en este caso que es de una polaridad, el divisor formado por las resistencias R3 y R4 fijan un voltaje V<sub>BALIDA</sub> en 1/2 +V. y por lo tanto la salida fluctuará entre 0.5 volts positivos.

En este diseño se utilizaron dos etapas de preamplificación de bajo voltaje, la primera amplifica 10 veces la entrada, proporcionando el suficiente voltaje para que sea filtrada por la etapa anterior, luego entonces, al ser filtrada necesitamos volver a amplificar 5 veces la señal a la salida del filtro, ya que en el filtrado se pierde voltaje, lo cual no nos conviene a la entrada directa al comparador.

### 4. Filtro Pasivo RL para el control de altas y bajas frecuencias:

Como su nombre lo dice, este filtro controla el paso de altas y bajas frecuencias haciendo uso de elementos pasivos como son capacitores y resistencias, proporcionando un control manual por medio de dos potenciómetros como se muestra en la figura.

#### 5. Circuito Comparador,

En este circuito, se van a comparar la señal triangular lineal con la señal de entrada externa, siendo una de las etapas más importante de toda la configuración del circuito amplificador, ya que aquí es donde se lleva a cabo la modulación de la señal cuadrada con la señal de entrada externa a amplificar, como se explicó en el capítulo anterior.

En primera instancia, se utilizó el circuito integrado 74LS132 (QUAD NAND SCHIMTT TRIGGER), el cual se componía de una compuerta "nand" con un umbrat de disparo, y así, cuando la señal comparada de entrada excedia de 1.7 volts o disminula de 0.9 volts se disparaba, proporcionando una señal modulada de pulsos restaurada con una amplitud de 5 volts ( ya que se trata de un circuito integrado ). Después de una serie de pruebas en el laboratorio, se concluyó que al usar este circuito se incrementaban las perdidas en la etapa de potencia, ya que la comparación se llevaba a cabo con un retraso considerable causado por el voltaje de disparo, es decir, cuando el impulso modulado se presentaba, lo hacía un tiempo considerable después y por lo tanto con una disminución en el voltaje que realmente se da al momento de la intersección de la señal a amplificar y la señal triangular que al momento de compararse se presenta.

Debido a esto se optó por utilizar el circuito comparador de voltaje LM311, el cual junto con el LM111 y el LM211, manejan un corriente interna muy pequeña, están diseñados para trabajar con un rango más amplio de voltaje de alimentación ( desde 15V hasta 5V ), la salida es

compatible con RTL, DTL y TTL, así como circuitos de la serie MOS, puede proporcionar impulsos por arriba de los 50V a corrientes de hasta 50 mA, y lo más importante, posee una respuesta de disparo de impulso de 40 ns y es mucho menos propenso a falsas oscilaciones.

## Especificaciones:

+ Corriente de entrada: 150 nA max.

+ Voltaje de operación: 5 V.

+ Voltaje de equilibrio: 7.5 mV.

+ Corriente de equilibrio: 20 nA max.

+ Rango de voltaje diferencial a la entrada: +/- 30 V.

+ Voltaje de saturación: 0.4 V.

+ Rango de temperatura de operación: 0 a 70

+ Consumo de potencia: 135 mW a +/- 15 V hasta 500 mW.

#### 6. Circuito Preamplificador de Medio Voltale (5-30).

Ya que la etapa anterior se trata de un circuito integrado, la señal de salida es de bajo voltaje (5 V), que no es suficiente para abrir y/o cerrar los transistores de potencia, para lo que se requiere de esta etapa, que consta de un transistor TIP130 con la siguiente configuración:

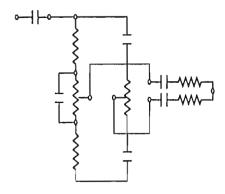

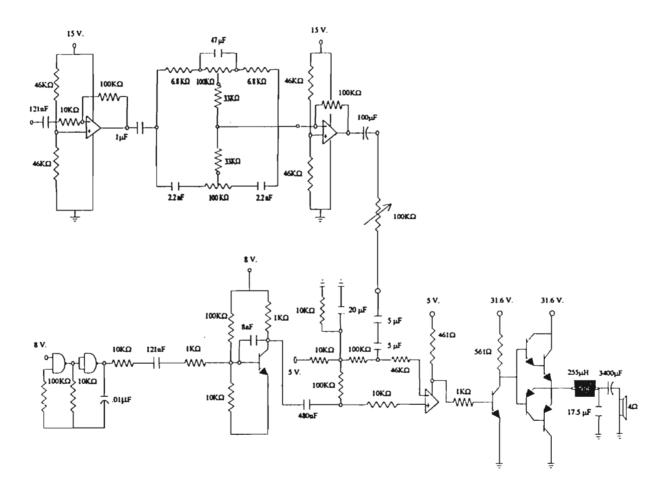

## 7. Circuito Amplificador Principal de Puisos de Alto Voltaje.

En esta etapa, que es otra de las fundamentales, se utilizan 2 transistores del tipo Darlingthon NPN - NTE249 y PNP - NTE250, conectados en base y emisor común de la siguiente forma:

Es importante comentar las características de estos transistores ya que son fundamentales para obtener la tan esperada alta eficiencia a la salida.

## Características de los transistores NTE249 y NTE250:

| + Energla disipada:          | 150 W.  |

|------------------------------|---------|

| + Corriente de colector:     | 18 A.   |

| + Corriente de base:         | 500 mA. |

| + Voltaje (colector-base):   | 100 V.  |

| + Voltaje (colector-emisor): | 100 V.  |

| + Voltaje (emisor-base):     | 5 V.    |

| + Voltaje de saturación:     | 0.7 V.  |

| + $h_{FE} = \beta$ ;         | 3500.   |

Estas características, nos permiten una alimentación de alto voltaje, estabilidad y alta sensibilidad en corriente como se vio en el capítulo I.

#### 8. Filtro Pasivo de Paso Bajo.

Ya que se tiene la señal amplificada, se debe de limitar el paso en amplitud y distorsión de fase, así como atenuar la frecuencia de conmutación y eliminar las armónicas de alta frecuencia.

El cicuito completo del amplificador que se propone con las especificaciones de cada uno de los elementos se observa en la siguiente figura.

# **RESULTADOS**

El objetivo de este capitulo es mostrar todos los resultados en cuanto a la relación de priencias, aproximación de las mediciones en el diseño real a la información bibliográfica, usando las ecuaciones ya exhaustivamente calculadas y analizadas en los dos capitulos anteriores, así como los esperados cálculos de la eficiencia de las secciones fundamentales y del circuito y las especificaciones de su uso en cuanto a su alimentación.

#### IV.1 MEDICIONES Y RATIFICACIONES.

#### Cálculos de Potencia.

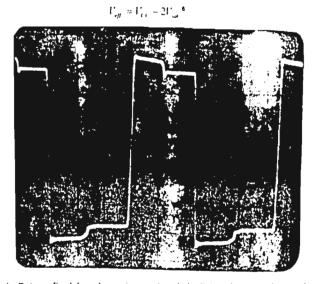

Primero, comenzaremos con el calculo teórico del voltaje efectivo que realmente es aprovechado por la carga del circuito amplificador, ya que existen pérdidas en los transistores al llegar al estado de saturación, teniendo así (ver figura 1)

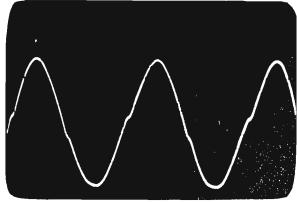

Figura 1. Fotografía del osciloscopio, mostrando la distorsión causada por el voltaje de saturación consumido en los transistores de potencia

<sup>&#</sup>x27;Por lo tanto la eficiencia se reduce del 100% a l'eff l'oc

el cual se aplica directamente a nuestra relación fundamental (2.2-2) para el cálculo de la potencia de salida, quedando de la siguiente forma:

$$P_0 \le \left[\frac{V_{eff}^{-2}}{8R}\right]$$

, entonces

$$P_0 \le \left[ \frac{\left(V_{CC} - 2V_{Na}\right)^2}{8R} \right] luego de la ecuación (2.1 – 12) tenemos que:$$

Si  $V_{Sin} \approx 0.7$  para el transistor del tipo Darlington, entonces:

$$V_{eff} = (31.6 - (2 \cdot 0.7)) = 30.2 Volts.$$

$$Y :: P_0 \le \frac{912.04}{32} = 28.50125 Watts.$$

A estos resultados, solo nos falta agregar los cálculos de la disipación de potencia en el tiempo de transición ( $P_{cl.}$ ) y en la reactancia de carga y resistencia parásita ( $P_{filtro}$ ) las cuales se calcularán a continuación:

De (2.2 - 4a) tenemos.

$$P_{d} = \frac{V_{CC} \cdot P_{0}}{V_{eff}} - P_{0} = \frac{31.6(28.50125)}{30.2} - 2850125 = 1.32125 Watts.$$

$P_{Filing} = I_{dc}^{2} R_{P}$ , en donde sustituyendo con (2.1.3) se tiene:

$$P_{filtro} = \left(\frac{2V_{CC}}{\pi^2 R}\right) \cdot R_F = (1.600874702) \cdot (0.154) = 0.3946711 Watts.$$

Por último, en cuanto a las pérdidas, se sabe que la forma de onda de voltaje de colector, queda sin modificar por la reactancia de carga, pero la corriente de salida ( y el voltaje ), se

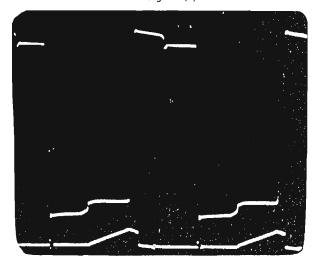

desplazan en fase relativa a la forma de onda del voltaje del colector, como se muestra en la figura 3.1 y en el apéndice I. Por lo tanto, las corrientes i1(0) e i2(0) tenderán a ser negativas durante una porción del ciclo RF.

También se tiene una reducción de la amplitud de la corriente de salida ya que si sabemos que Z=R+IX, entonces la potencia de salida será:

$$P_0 = \frac{2}{\pi^2} \frac{V_{\rm cc}^2}{\rho R}$$

donde

$$\rho = \frac{Z}{R}$$

Para el caso de cálculos se despreclarán estas pérdidas, ya que se utilizó una resistencia de carga puramente resistiva para minimizar al máximo estas pérdidas, pero se hicieron pruebas con bocinas, las cuales tienen cargas reactivas que generan claramente la amplitud indeseable de la corriente de salida ( ver apéndice 1).

Con estos cálculos teóricos, tenemos suficiente para hacer la comparación entre la teória y la práctica, concluyendo como sigue:

$$P_{\text{O(totalea)}} = P_{\text{o}} - P_{\text{d}} - P_{\text{Filtro}} = 28.50125 - 0.394711 - 1.32125 = 26.7853289 Watts$$

$$P_{\text{O(pylicitics maxima)}} = \frac{V_{\text{om}}^{-1}}{2R} = \frac{12^2}{2 \cdot 4} = 18 Watts. (medido en medias - altas frecuencias)$$

#### Cálculo de eficiencias.

Ahora si llegamos al cálculo de las eficiencias, tomando en cuenta los resultados de las ecuaciones teóricas y los resultados obtenidos en este prototipo.

Comenzaremos con el cálculo de eficiencias teóricas:

Sabemos que la potencia disipada en la fuente de alimentación es (2.1 - 14):