FACULTAD DE INGENIERIA

# LAS REDES NEURONALES ARTIFICIALES CONTEMPORANEAS EN HARDWARE

T E S I S

OUE PARA OBTENER EL TITULO DE

INGENIERO MECANICO ELECTRICISTA

P R E S E N T A

CESAR VELEZ ANDRADE

Director: DR. JOSE ISMAEL ESPINOSA ESPINOSA

TESIS CON

PALLA DE ORIGEN

MEXICO, D. F.

1996

UNAM – Dirección General de Bibliotecas Tesis Digitales Restricciones de uso

### DERECHOS RESERVADOS © PROHIBIDA SU REPRODUCCIÓN TOTAL O PARCIAL

Todo el material contenido en esta tesis esta protegido por la Ley Federal del Derecho de Autor (LFDA) de los Estados Unidos Mexicanos (México).

El uso de imágenes, fragmentos de videos, y demás material que sea objeto de protección de los derechos de autor, será exclusivamente para fines educativos e informativos y deberá citar la fuente donde la obtuvo mencionando el autor o autores. Cualquier uso distinto como el lucro, reproducción, edición o modificación, será perseguido y sancionado por el respectivo titular de los Derechos de Autor.

#### **DEDICATORIA**

A mis padres, César Vélez y de la R. y Haydeé Andrade D.:

Por el infinito amor, confianza y dedicación que me han brindado. Por criarnos, a mis hermanas y a mi, bajo una insustituible atmósfera de amor, principios y dedicación. Para ustedes este trabajo, que sin duda, sólo es una minúscula representación de lo mucho que les quiero y les agradezco.

A mis hermanas Haydeé, Verónica, Rubria y Ana Luisa:

Por estar siempre conmigo y ser parte de mi formación. Por haberme enseñado, con ejemplo vivo, el comportamiento de unión, honestidad y nobleza. Las quiero mucho.

#### A Gloria:

Por toda la confianza, amor y dedicación que depositas cada día en mí y por hacer todo lo posible para siempre estar conmigo.

A la memoria de mi tío Héctor A. Vélez y de la R.

A mis tíos Karina Vélez y de la R. y Armando Andrade D.

Por siempre apoyar a mis padres y estar pendientes de cada uno de nosotros, siempre con el único interés de nuestro bienestar. Los quiero mucho y gracias.

A la familia Espinosa Lara: Ismael, Ritaluz y Malors.

Por su atención, cariño e invaluable amistad. Especialmente al Dr. José Ismael Espinosa E. por haberme concedido el orgullo de ser su amigo y el enorme placer de haberle aprendido tantas cosas. Ismael, mil gracias.

# A todos mis amigos.

Especialmente a: Margarita A., Carlitos S., Eduardo Z., J. Carlos E., Rodrigo P. y Wilphen V. Por haber utilizado el paso de cada día para consolidar y demostrar su gran amistad.

#### **AGRADECIMIENTOS**

Al Prof. Jorge López S.

Por enseñarme la disciplina de la esgrima y a asociarla a mi vida profesional.

A mis compañeros del Laboratorio de Cibernética:

Irma, Alberto, Fidel, Javier, Jorge Q., Juan Carlos, Juan Manuel, Luis, Pepe, Roberto y los Rubenes.

A mis compañeros de trabajo:

Alejandro G., Alejandro Z., David V., Fernando B., Irving H., J. Carlos Z. y René Ch. Gracias a todos y en especial a René por su constante motivación y apoyo.

#### A la U.N.A.M.:

Por haberme brindado educación y conciencia de la realidad nacional. Por haberme permitido ser parte de ese singular mosaico social que la conforma, que de alguna manera, induce la responsabilidad que un profesional debe tener hacia un país tan complejo como lo es nuestro México.

Por mi Raza Hablará el Espíritu.

# ÍNDICE

| CAPÍTULO 1                                      |      |      |

|-------------------------------------------------|------|------|

| INTRODUCCIÓN, OBJETIVOS Y MÉTODOS               | Pág. | 1    |

| CAPÍTULO 2                                      |      |      |

| EL CEREBRO                                      | Pág. | 7    |

| 2.1 EL CEREBRO COMO UN SISTEMA COMPLEJO         | Pág. | 11   |

| CAPÍTULO 3                                      |      |      |

| REDES NEURONALES                                | Pág. | 13   |

| 3.1 LA CONECTIVIDAD ENTRE NEURONAS              | Pág. | 13   |

| 3.1.1 NEURONAS CON ACTIVIDAD INDEPENDIENTE      | Pág. | 15   |

| 3.1.2 NEURONAS CON CONEXIÓN DIRECTA: EXCITACIÓN | Pág. | 18   |

| 3.1.3 NEURONAS CON CONEXIÓN DIRECTA: INHIBICIÓN | Pág. | 20   |

| CAPÍTULO 4                                      |      |      |

| LAS REDES NEURONALES ARTIFICIALES (RNA)         | Pág. | 24   |

| 4.1 EL APRENDIZAJE DE UNA RED                   |      |      |

| 4.2 APRENDIZAJE NO SUPERVISADO                  | Pág  | . 29 |

| 4.3 APRENDIZAJE SUPERVISADO                     | Pág  | . 29 |

| 4.3.1 RETROPROPAGACIÓN                          | Pág  | . 30 |

| 4.4 APLICACIONES DE LAS RNA'S                                                                                                                                                                           | Pág.                               | 35                                     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|----------------------------------------|

| CAPÍTULO 5                                                                                                                                                                                              |                                    |                                        |

| REDES NEURONALES DESARROLLADAS EN HARDWARE                                                                                                                                                              | Pág.                               | 39                                     |

| CAPÍTULO 6                                                                                                                                                                                              |                                    |                                        |

| TÉCNICAS DE DISEÑO DE REDES NEURONALES EN HARDWARE                                                                                                                                                      | Pág.                               | 44                                     |

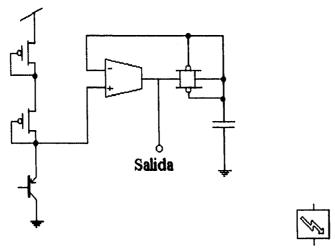

| 6.1 CIRCUITOS EQUIVALENTES A NEURONAS                                                                                                                                                                   | Pág.                               | 48                                     |

| 6.2 CIRCUITOS EQUIVALENTES A SINAPSIS                                                                                                                                                                   | Pág.                               | 52                                     |

|                                                                                                                                                                                                         |                                    |                                        |

| CAPÍTULO 7                                                                                                                                                                                              |                                    |                                        |

|                                                                                                                                                                                                         |                                    |                                        |

| EJEMPLOS DE REDES NEURONALES DESARROLLADAS EN HARDWARE                                                                                                                                                  | Pág.                               | 61                                     |

| 7.1 ESPECIFICACIONES DE HARDWARE                                                                                                                                                                        | . •                                |                                        |

|                                                                                                                                                                                                         | Pág.                               | 61                                     |

| 7.1 ESPECIFICACIONES DE HARDWARE  7.2 RED CON PESOS FIJOS  7.3 REDES CON PESOS VARIABLES                                                                                                                | Pág.<br>Pág.<br>Pág.               | 61<br>62<br>63                         |

| 7.1 ESPECIFICACIONES DE HARDWARE  7.2 RED CON PESOS FIJOS  7.3 REDES CON PESOS VARIABLES                                                                                                                | Pág.<br>Pág.<br>Pág.               | 61<br>62<br>63                         |

| 7.1 ESPECIFICACIONES DE HARDWARE  7.2 RED CON PESOS FIJOS  7.3 REDES CON PESOS VARIABLES  7.4 TECNOLOGÍA DIGITAL                                                                                        | Pág.<br>Pág.<br>Pág.<br>Pág.       | 61<br>62<br>63<br>66                   |

| 7.1 ESPECIFICACIONES DE HARDWARE  7.2 RED CON PESOS FIJOS  7.3 REDES CON PESOS VARIABLES                                                                                                                | Pág.<br>Pág.<br>Pág.<br>Pág.       | 61<br>62<br>63<br>66                   |

| 7.1 ESPECIFICACIONES DE HARDWARE  7.2 RED CON PESOS FIJOS  7.3 REDES CON PESOS VARIABLES  7.4 TECNOLOGÍA DIGITAL  7.4.1 ARQUITECTURA DE CAPAS                                                           | Pág. Pág. Pág. Pág. Pág. Pág.      | 61<br>62<br>63<br>66<br>66<br>67       |

| 7.1 ESPECIFICACIONES DE HARDWARE  7.2 RED CON PESOS FIJOS  7.3 REDES CON PESOS VARIABLES  7.4 TECNOLOGÍA DIGITAL  7.4.1 ARQUITECTURA DE CAPAS  7.4.2 CI'S CON MULTIPROCESADORES                         | Pág. Pág. Pág. Pág. Pág. Pág.      | 61<br>62<br>63<br>66<br>66<br>67<br>68 |

| 7.1 ESPECIFICACIONES DE HARDWARE  7.2 RED CON PESOS FIJOS  7.3 REDES CON PESOS VARIABLES  7.4 TECNOLOGÍA DIGITAL  7.4.1 ARQUITECTURA DE CAPAS  7.4.2 CI'S CON MULTIPROCESADORES  7.4.3 ARQUITECTURA RBF | Pág. Pág. Pág. Pág. Pág. Pág. Pág. | 61<br>62<br>63<br>66<br>66<br>67<br>68 |

# CAPÍTULO 8

| SISTEMAS NEUROMÓRFICOS                                   | Pág. | 78  |

|----------------------------------------------------------|------|-----|

| 8.1 EL CONCENTRADOR SEGUIDOR                             | Pág. | 79  |

| 8.2 LA RETINA NEUROMÓRFICA                               | Pág. | 82  |

| 8.3 EL SISTEMA VISUAL-AUDITIVO                           | Pág. | 82  |

| 8.3.1 PSICOFISIOLOGÍA DE LA AUDICIÓN                     | Pág. | 84  |

| 8.3.2 SISTEMA VISUAL BIOLÓGICO                           | Pág. | 87  |

| 8.3.3 DISEÑO DEL SISTEMA VISUAL                          | Pág. | 89  |

| 8.3.4 DISEÑO DEL SISTEMA AUDITIVO                        | Pág. | 89  |

| 8.3.5 LA OPERACIÓN GLOBAL                                | Pág. | 93  |

| 8.3.6 MODELO DE LA RETINA                                | Pág. | 94  |

| 8.3.7 MODELO AUDITIVO                                    | Pág. | 96  |

|                                                          |      |     |

| CAPÍTULO 9                                               |      |     |

| DISEÑO, ENTRENAMIENTO Y PRUEBAS EN SOFTWARE CON DYNAMIND | Pág. | 99  |

|                                                          |      |     |

| CAPÍTULO 10                                              |      |     |

| DISCUSIÓN Y CONCLUSIONES                                 | Pág. | 114 |

|                                                          |      |     |

| GLOSARIO                                                 | Pág. | 123 |

| REFERENCIAS                                              | Pág. | 125 |

| RIRI IOGRAFÍA DE DED                                     | Dán  | 120 |

# CAPÍTULO 1: INTRODUCCIÓN, OBJETIVOS Y MÉTODOS

La creciente preocupación vivida actualmente por optimizar el tiempo abarca todo tipo de actividades: desde planear una ruta para cumplir cierto itinerario en el menor tiempo posible, hasta la generación de códigos de programación que demanden poco tiempo del procesador en la realización de operaciones. En todas las formas de vida humana se hace manifiesta la "variable reina", el tiempo. Es en función de ésta que se define que tan bien o mal van las cosas.

La economía, la política, la mecánica, la astronomía y cada una de las disciplinas que ha desarrollado el ser humano tienen como parámetro al tiempo. Actualmente la capacidad de las empresas prestadoras de servicios como las de computación, bancos, comunicaciones, salud, etc. se catalogan a partir del tiempo de respuesta que puedan ofrecer, mientras éste sea más reducido y evidentemente el resultado sea correcto, la empresa tendrá mayor reconocimiento en su rama.

La automatización es un hecho en nuestro tiempo, toda actividad que quiera rendir en operación tiende a ser automatizada, lo que significa adaptar a su mecánica laboral un sistema autónomo capaz de realizar en el menor tiempo posible el mayor número de tareas. Actualmente estas tareas han crecido notablemente tanto en número como en complejidad, lo que exige optimizar tiempo y, por lo tanto, las características de dichos sistemas han tenido que mejorarse continuamente. Esto es fácil de comprobar poniendo como ejemplo una computadora personal (PC): los requerimientos mínimos de hardware para poder utilizar paquetería de actualidad, que es la demandada por el ritmo de vida actual, rebasan hasta en un 200% lo que era el mínimo necesario hace 1 año. Si en algo tan simple como una PC para trabajar en casa se requiere de

mayores velocidades en el procesamiento, es fácil imaginarse como se incrementan los requerimientos de este tipo en instituciones o empresas que atienden a mas de 60 personas.

La capacidad de realizar un gran número de operaciones en períodos cortos de tiempo está relacionada con las características del procesador utilizado y la forma en la que se programa su operación. Aún cuando el mejor programador realice las rutinas de trabajo del procesador optimizando tiempos, existen infinidad de procesos que demandan mayor velocidad de cálculo que la que nos pueda entregar incluso, una supercomputadora. Para conocer este tipo de procesos no es necesario ser un experto en programación o en el uso de computadoras, basta con dedicarle un poco de tiempo a razonar cada una de la cosas que hacemos día con día. Imaginemos que leemos un libro u observamos un programa de T V, no resultaría dificil tomar una taza que esté junto y dar un sorbo de café sin perder detalle alguno de la actividad primaria, o bien podemos modificar por completo la posición de nuestro cuerpo mientras seguimos atendiendo la TV o la lectura. Esto, aún tratándose de una actividad intrascendente por su aparente "simplicidad" para llevarse a cabo, engloba una enorme cantidad de datos y procesamientos previos y durante cada movimiento, para que cada uno de éstos se pueda realizar al mismo tiempo, sin desatender la operación de los demás procesos. Si algo tan común como acomodarse mientras se lee un libro involucra un número de operaciones hasta ahora desconocido, imaginemos la complejidad en la realización de operaciones y la distribución de éstas para un bateador de base-ball que en un período de décimas de segundo debe identificar la bola del resto del campo visual, definir si abanica o no a una bola que se aproxima a una velocidad cercana a los 160 Km./hr, sincronizar brazos, piemas, cadera, muñecas y aplicar la máxima fuerza en un preciso instante. Qué se puede decir cuando la tarea es procesar información de naturaleza abstracta como la música o las

matemáticas, cuánta complejidad hay en estos casos en los que no se trata de coordinar el movimiento del cuerpo, sino de asociar, procesar y dar secuencia a ideas.

Si este tipo de procesos no se ha podido igualar en ningún sistema diferente al cuerpo humano, se debe a que la operación y leyes que rigen a la unidad encargada de asociar, almacenar y coordinar información que controla nuestro cuerpo o sea el cerebro, es prácticamente desconocido en lo que se refiere a la constelación de redes neuronales que lo constituyen.

## **Objetivos**

Esta tesis tiene como objetivo desarrollar una aplicación en hardware de redes neuronales para clasificación de señales neuro-eléctricas y, en general, para reconocimiento de patrones generados por sensores.

En este trabajo no se pretende, de ninguna manera, repetir con tecnologías contemporáneas, modelos ya realizados en los años sesentas y setentas. En otras palabras, el objetivo no es desarrollar un modelo electrónico de neurona, ni siquiera un modelo electrónico de una red neuronal pequeña. Todo lo contrario, se trata de aplicar las propiedades emergentes de las redes neuronales artificiales que poseen masividad tanto en el número de procesadores (neuronas) como en el de conexiones. Tal masividad puede implicar cientos de procesadores y cientos de miles de conexiones.

Aún cuando no deja de ser interesante reproducir un modelo básico de sinapsis o de neurona con dispositivos actuales, desde el punto de vista de la ingeniería no resulta muy práctico debido a que en las aplicaciones contemporáneas se hacen manifiestas las propiedades emergentes que han tenido las RNA's en los últimos años, como por ejemplo, el procesamiento en paralelo,

esta característica no se contemplaba como representativa de las estructuras neuronales hace 20 o 30 años y actualmente es un comportamiento característico con enorme relevancia para los procesos en que se aplican.

Actualmente las aplicaciones de las RNA en hardware son procesos complejos que engloban diferentes disciplinas, es casi imposible encontrar un CI comercial con una estructura neuronal que opere únicamente como oscilador. Por esta razón, el reproducir modelos clásicos de sinapsis o de neuronas individuales no pone en evidencia las capacidades de un RNA, por el contrario, proyecta un sistema extremadamente complejo y con capacidades reducidas para atacar problemas contemporáneos. Como ejemplo representativo de esto se puede utilizar una aplicación muy conocida en el campo de las RNA's: La asignación de rutas para el "vendedor viajero". En este problema se pretende obtener el mayor provecho en la visita de 6 ciudades, cada una con "X" prioridad. Para la solución de este problema a través de una RNA se necesitan al menos 36 neuronas y 360 interconexiones (Hopfield, 1987). Este ejemplo da una idea de la enorme cantidad de neuronas y sinapsis que debe contener un CI para una aplicación más compleja como reconocimiento de patrones, o reconocimiento de imágenes.

Como podrá verse, el hardware contemporáneo de redes neuronales no está desarrollado para ejecutar tareas simples, la justificación de recursos para el diseño y fabricación de un CI neuronal depende de la aplicación a la que se dirija, por lo que es de esperarse que las tareas para las cuales se desarrolle un CI con estructura neuronal sean bastante complejas. Desafortunadamente una industria muy interesada en el desarrollo de esta tecnología es la industria militar, el infortunio no sólo se refiere a lo funesto de las tipicas aplicaciones de esta

industria, sino también a la dificultad para obtener información referente a las tecnologías aplicadas y a las tareas específicas donde las RNA's son utilizadas.

El estudio y aplicación de las redes neuronales en hardware es un tema desconocido pero de reconocida importancia debido a que sólo logrando desarrollar este tipo de estructuras se podrá obtener todo el beneficio que ofrece esta tecnología y hablar de la generación real o cuando menos de una aproximación cercana a un sistema biológico, lo que proporcionaría una sólida plataforma para el desarrollo científico.

Mostrando el potencial de estos dispositivos se busca también hacer manifiesta la necesidad de señalar la importancia y trascendencia del estudio interdisciplinario así como de impulsarlo para poder comprender, aportar y equilibrar el mundo que nos rodea.

#### Métodos

En primer lugar, se realizará una revisión de la literatura sobre el tema.

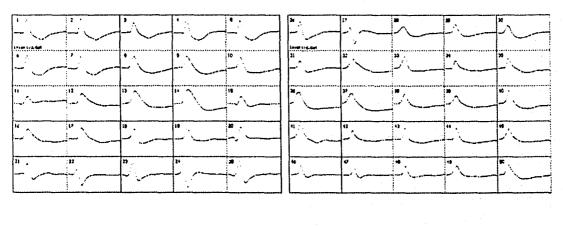

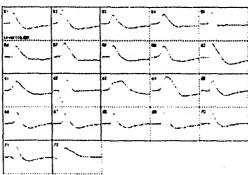

En segundo lugar, se hará la clasificación de una base de señales neuro-eléctricas (potenciales de acción que son pulsos con una cierta forma de onda y una duración aproximada de 2 ms) simulando con DynaMind v3.0 una red neuronal en cascada entrenada con el algoritmo de retropropagación.

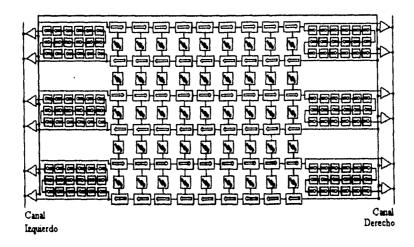

En tercer lugar, utilizando DynaMind v3.0 y NeuroLink v2.0 se emularán el neurochip Intel 80170NX y la tarjeta multineurochip EMB de Intel.

Por ultimo, la red clasificadora de señales se transportará al emulador de la red de neurochips 80170NX y se hará una verificación de la capacidad de generalización de la red neuronal propuesta.

En las etapas en que se presenten dudas, se utilizará INTERNET y correo electrónico para consultar con INTEL y con quien sea necesario.

En este trabajo se presenta en el capítulo 2 una breve descripción de la operación del cerebro desde el punto de vista funcional y como sistema de control. En el capítulo 3 se aborda el tema de las redes neuronales artificiales estableciendo, primero, la definición de una RNA a partir de los tres posibles casos de relación que existen entre las neuronas, es decir: excitación, inhibición e independencia. En el capítulo 4 se habla acerca de las características de operación de una red neuronal artificial y acerca del algoritmo de retropropagación y se mencionan algunas aplicaciones de las RNA's. El capítulo 5 trata algunas de las RNA's desarrolladas en hardware. En el capítulo 6 se mencionan y comentan las técnicas de desarrollo de circuitos para RNA's, modelos tanto de neuronas como de sinapsis. El capítulo 7 habla acerca de las diferentes tendencias en lo que a la elaboración de RNA's en hardware se refiere, esto es, a partir de los modelos y tecnologías aplicadas en el desarrollo de RNA's se han identificado diferentes modelos que obedecen a la aplicación de determinada tecnología en un punto determinado de la red (pesos o neuronas). El capítulo 8 hace referencia a los sistemas neuromórficos y se dedica también a dar una explicación del sistema, desarrollado en base a esta tecnología, llamado el "visor- auditivo". El capítulo 9 presenta el comportamiento, así como las técnicas aplicadas para el entrenamiento de una RNA en software, todo esto realizado con el sistema Dynamind. En el capítulo 10 se vierten las recomendaciones emanadas de este trabajo y se discute lo que realmente se pudo hacer con los recursos disponibles y de acuerdo con los objetivos propuestos. Finalmente, se presentan un glosario de abreviaciones utilizadas en el texto y una lista de referencias consultadas y mencionadas, así como una lista de URL's consultados por medio de NETSCAPE.

# CAPÍTULO 2: EL CEREBRO

"El hombre debería saber que del cerebro, y no de otro lugar vienen las alegrías, los placeres, la risa y la broma, y también las tristezas, la aflicción, el abatimiento y los lamentos. Y con el mismo órgano, de una manera especial, adquirimos el juicio y el saber, la vista y el oído y sabemos lo que está bien y lo que está mal, lo que es trampa y lo que es justo, lo que es dulce y lo que es insípido, algunas de estas cosas las percibimos por costumbre y otras por su utilidad. Y a través del mismo órgano nos volvemos locos y deliramos, y el miedo y los terrores nos asaltan, algunos de noche y otros de día, así como los sueños y los delirios indeseables, las preocupaciones que no tienen razón de ser, la ignorancia de las circunstancias presentes, el desasosiego y la torpeza. Todas estas cosas las sufrimos desde el cerebro" (Hipócrates: Sobre la Enfermedad Sagrada) (Smith, 1970)

Siendo esta porción del cuerpo de apenas 1.350 Kg., en promedio, la región más misteriosa del ser humano parece increíble saber que desde hace aproximadamente 2,500 años ya se consideraba como un elemento excepcionalmente complejo según lo muestra Hipócrates en sus escritos.

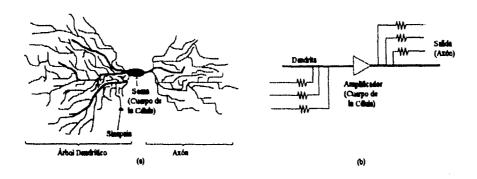

Existen muchas razones y principios que nos permiten suponer que la unidad básica de la vida es la célula, esto puede comprobarse făcilmente echando un vistazo a través del microscopio a cualquier organismo o tejido vivo. Pero resulta mucho más sorprendente el pensar que no sólo los tejidos como la piel o los que conforman los diferentes órganos del ser humano están compuestos por células, sino que también el sistema nervioso central, el encargado de interconectar todo nuestro cuerpo y damos conciencia de qué y quiénes somos, está compuesto

también por estas unidades. Las células que componen al Sistema Nervioso Central (S.N.C.) corresponden básicamente a dos tipos: las células nerviosas o neuronas y las células neurogliales o gliales. En lo que respecta a las neuronas, es a éstas a las que se les atribuye todo el funcionamiento del S.N.C: conducción de los impulsos nerviosos, elaboración de la información sensitiva, determinación de los patrones apropiados a estímulos específicos, etc. En lo que respecta a las células gliales que, aunque se imponen en número, sólo se consideraba que su función era de soporte en la operación de las neuronas y tal vez alguna relación con su nutrición, sin embargo hay evidencias recientes de que juegan otros papeles.

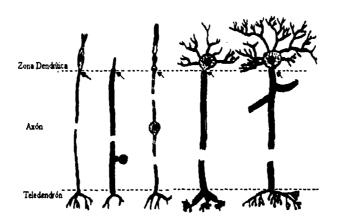

Las células neuronales o neurosensitivas pueden clasificarse en diferentes tipos dependiendo de su morfología la cual se determina a partir de la función en la que está involucrada. En otras palabras, podemos considerar que todas las células nerviosas son células neurosensoriales altamente especializadas. En los mamíferos las células neurosensoriales se encuentran en la mucosa nasal, en los músculos y en muchos órganos internos. Esto nos lleva a pensar que cada célula neurosensorial responde a un tipo específico de estímulo: presión, color, olor, etc. Pero a pesar de la diversidad de funciones que llevan a cabo este tipo de células y a la enorme variedad de estímulos a los que pueden responder, en cualquier caso podremos hablar de ciertas especializaciones anatómicas:

- La Zona Dendritica que es sensible ante la presencia de cualquier actividad extracelular.

- El Cuerpo de la Célula o Pericarión.

- El Axón, que emerge desde el pericarión y permanece sin dividirse hasta:

- El Teledendrón, que es capaz de segregar sustancias químicas específicas.

La figura siguiente muestra diferentes clases de células nerviosas que van desde el tipo más primitivo de célula conductora hasta la motoneurona y la interneurona.

FIGURA 1.-. Morfología de neuronas y células neurosensoriales (tomado de Smith, 1970 p. 82)

De esta forma se tiene que en los diferentes tipos de células nerviosas y neurosensitivas es posible ver que la terminología presentada puede generalizarse. Esta generalización fue propuesta en 1963 por D. Bodian (Tresguerres, 1992), quien lo estableció asignando nombres similares a regiones con funciones también similares.

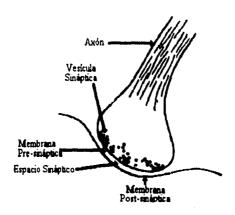

Aún con la diferencia considerable que a simple vista se percibe en la morfología de estas células se tiene que en cualquier caso, la zona dendrítica responde a alguna forma de estimulación (esta estimulación es un impulso eléctrico producto del potencial producido por el intercambio de iones entre interior y exterior de la membrana de la célula, dicho potencial tendrá una intensidad determinada), la unión entre el pericarión y el axón (colina axónica) es el lugar donde se genera el potencial de acción o impulso nervioso (este potencial es el que indica la activación de una célula neuronal), el axón conduce el impulso sin decremento y el teledendrón o

botón sináptico segrega una determinada cantidad de sustancia neurotransmisora al llegar dicho impulso que genera la reacción correspondiente, excitación o inhibición dependiendo de la sustancia neurotransmisora involucrada, en la siguiente célula. Este proceso se lleva acabo a través de la llamada sinapsis.

El funcionamiento del cerebro ha sido a lo largo de la historia una de las grandes interrogantes del ser humano. Hasta hoy la investigación sólo ha logrado encontrar explicación de algunas características particulares y otras tantas generales. Si bien el conocimiento de la operación del cerebro humano a nivel anatómico está considerablemente avanzado, la investigación de esta porción del cuerpo humano en lo que se refiere a su operación en la generación de sentimientos, estados de ánimo, personalidad, conductas agresivas y en general como centro de asociación de ideas sigue teniendo grandes incógnitas.

Actualmente es sabido que cada movimiento del cuerpo humano encuentra su origen en el cerebro y es controlado por impulsos eléctricos, impulsos que varían en intensidad y tipo de reacción (excitación o inhibición) en la o las células incidentes. La razón por la cual un impulso eléctrico puede terminar siendo excitación o inhibición depende fundamentalmente de la sustancia neurotransmisora que se libere ante la presencia de éste. La ausencia o presencia no correcta de cualquiera de estas dos reacciones (excitación e inhibición) dan como resultado un comportamiento inadecuado del cuerpo humano o de alguna de sus regiones que le impedirá al individuo interactuar con toda su capacidad con el medio que le rodea.

#### 2.1 El cerebro como un sistema complejo

Una de las grandes interrogantes que se tienen y que su respuesta sería de gran ayuda no sólo para la medicina sino para todos los campos que estudian al cerebro es conocer la función de la red de interconexión que existe, si no entre los 300 millones de células nerviosas que tiene el cerebro humano en su totalidad, sí al menos en alguna de las regiones que lo conforman.

La gran diversidad de tareas y funciones que puede realizar el cerebro, van desde la aparente sencillez del movimiento de un pequeño músculo o algún miembro del cuerpo hasta la conformación y manejo de conceptos tan complejos como lo es la personalidad. Los conocimientos, los sentimientos, la capacidad de razonar, la creatividad y todas las funciones que hacen al ser humano una especie intelectual muy superior a las demás no se podrían realizar si no existiera el arreglo de conectividad que tiene el cerebro humano, una neurona por si sola no podría servir para realizar ni la tarea más básica de un ser humano.

De hecho lo que somos y como somos está en función de la operación del cerebro, por ende, definido a través de la red que se forma entre las neuronas que componen al más complejo elemento del universo, el cerebro humano.

La red de comunicación existente en el cerebro de cada ser humano es precisamente la orquestadora de todos los elementos que integran al cuerpo humano, es decir gracias a esta podemos movernos, hablar, diferenciar sabores, formas, colores y olores. Aparte de permitimos conocer el mundo, esta red hasta ahora desconocida es la generadora de todas y cada una de las herramientas que la tecnología pone a nuestro servicio y, creando un círculo, utilizamos estas para entender o aproximarnos a la operación de su creador, el cerebro.

Resulta que el organismo animal realmente comunica sus distintas partes por medios eléctricos, sin embargo el método adoptado difiere substancialmente del empleado en la transmisión de datos o de telefonía. Esto tiene que ser así porque los "hilos telegráficos" del organismo son conductores de electricidad del tipo cable submarino. Hodgkin calculó que un metro de axón humano normal tiene la resistencia eléctrica equivalente a la de 16<sup>10</sup> kilómetros de hilo de cobre (Hodgkin, 1958; Smith 1970).

#### CAPÍTULO 3: REDES NEURONALES

Actualmente es claro que el comportamiento individual de la neurona no entrega información suficiente para pretender encontrar respuesta a interrogantes como la conducta, la memoria, los gustos, etc. Esto es sabido desde años atrás y de profundo interés no sólo para las áreas biológicas o neurofisiológicas, sino también para las matemáticas, la física y la ingeniería. Gracias a los experimentos en preparaciones biológicas del axón gigante del calamar se logró hacer por primera vez la inserción de electrodos en una fibra nerviosa y obtener así un potencial de membrana (Young, 1936, Smith, 1970) esto demostró la presencia de niveles de electricidad en el impulso nervioso y permitió entrar a mas detalle en su investigación permitiendo que se desarrollaran modelos matemáticos para tratar de representar una neurona y posteriormente tratar de desarrollara con componentes eléctricos.

#### 3.1 La conectividad entre neuronas

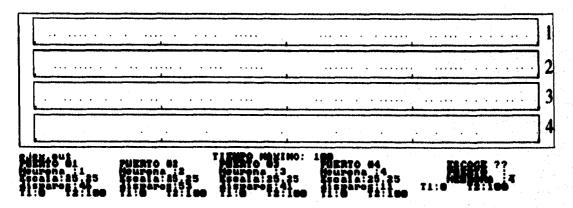

Con la intención de aclarar un poco mas el concepto de red neuronal y la importancia de las características de su sinapsis en el comportamiento de ésta, se presentan a continuación los tres casos más importantes en una configuración de red simple que involucra un par de neuronas. Para ilustrar este ejemplo se utilizará el paquete de software NEURORED (Alcántara, 1992) desarrollado en el laboratorio de Cibernética. En este paquete es posible simular configuraciones de redes neuronales pequeñas y es una poderosa herramienta para el estudio de las mismas. La simulación de una red con NEURORED va desde la definición de la estructura de la red (numero de neuronas, interconexiones, tipo de interconexiones, etc.), la representación en el tiempo de la

ocurrencia de actividad de las neuronas (para facilitar dar una idea de la posible dependencia entre neuronas), hasta la obtención de un gráfico de correlación entre las neuronas que se deseen estudiar. La correlación cruzada es una herramienta altamente utilizada en la fisiología debido a que a través de esta técnica es posible determinar si existe dependencia temporal en la operación de células. Esta técnica consiste en un análisis de la actividad celular la cual es representada en un histograma bidimensional (para el caso de dos neuronas) en el que el eje de las abcisas representa el tiempo y el de las ordenadas el número de ocurrencias de intervalos temporales entre neuronas.

El interés de la fisiología en esta técnica se debe a que a través de ésta es posible conocer qué células están relacionadas con cuáles y qué tipo de relación guardan entre sí: excitatoria o inhibitoria. La correcta interpretación del histograma que entrega la correlación cruzada puede dar una imagen aproximada de la estructura que guarda el arreglo celular en estudio, es decir, permite conocer un poco más la conectividad funcional de la red celular en cuestión.

La interpretación del histograma consiste en determinar dentro de un intervalo de tiempo determinado la característica de dependencia o independencia en la activación de las neuronas a través de la forma de la gráfica que genera la actividad celular. Cuando el histograma tiene una forma plana, es decir, sin espigas que sobresalgan del resto de las activaciones, esto representa independencia de operación entre las neuronas involucradas. Si por el contrario, en la gráfica existe una espiga sobresaliente o bien una ausencia de disparos se habla de una relación excitatoria e inhibitoria, respectivamente (Espinosa, 1977). En las figuras de este capítulo se presentan gráficas de correlación en las cuales se aprecia y comprueba claramente el fenómeno mencionado.

#### 3.1.1 Neuronas con actividad independiente

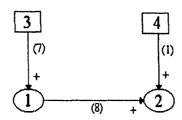

En primer lugar se presenta un ejemplo para un par de neuronas con actividad totalmente independiente:

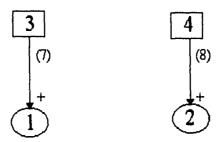

FIGURA 2.- Configuración para dos neuronas independientes. Donde 1 y 2 son neuronas; 3 y 4 son fibras activadoras y la conexión va de 3 a 1 y de 4 a 2 para producir actividad "eléctrica" independiente en 1 y 2 .Los números 7 y 8 indican los pesos sinápticos.

En el diagrama de la figura 2 se representan dos fibras (3 y 4) que excitan a las neuronas 1 y 2 respectivamente. La conexión entre las fibras y neuronas está representada por líneas que unen a los elementos involucrados, en esta línea está establecida la "intensidad o influencia" (peso) de esta conexión en la operación de las neuronas, en este caso particular los pesos son 7 para la conexión "3 a 1" y 8 para la conexión "4 a 2". Para este ejemplo no existe conexión entre neuronas con la idea de representar un comportamiento independiente entre éstas. En este caso en las fibras se estableció una probabilidad de disparo de 50 % para la 3 y 15 % para la 4. Esa probabilidad se verá reflejada en la actividad de las neuronas independientes tal como se muestra en la figura 3, donde la neurona 1 se dispara 53 veces y la neurona 2 sólo 25 veces.

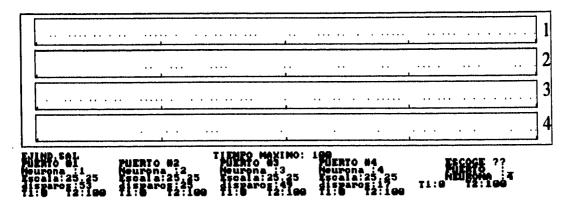

FIGURA 3.- Diagrama de puntos de fibras y neuronas para el caso de neuronas independientes.

Cada elemento, tanto neuronas como fibras, será identificado con el número que se le asigne en el diagrama inicial. En esta representación gráfica el tren de potenciales de acción o impulsos nerviosos de cada elemento se representan por puntos en función del tiempo (para este caso un período de 100 ms). Cada punto significa la activación (un disparo) del elemento correspondiente en el momento indicado, con este diagrama es posible darse una idea de la dependencia existente entre los diferentes elementos de la red. Este diagrama puede, en un momento dado, indicar que elementos están relacionados en lo que se refiere a su activación; en este caso se conoce de antemano qué elementos dependen de cuáles. Suponiendo que se desconoce el conexionamiento de la red es posible determinar esta dependencia funcional a través del histograma de correlación cruzada. (Espinosa, 1977)

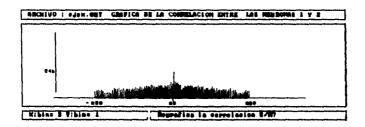

En las cuatro gráficas siguientes se presenta la correlación cruzada entre los elementos de la red de la figura 2. El eje de las abcisas representa el tiempo y el de las ordenadas el número de ocurrencias. Con este tipo de histogramas es posible determinar si existe dependencia, y de qué tipo (excitación o inhibición), o no entre la activación de los elementos en estudio.

Para el caso de la figura 4 el histograma es prácticamente plano, es decir no existe una presencia o ausencia súbita de ocurrencias en determinado tiempo, lo que representa que no existe relación alguna entre la operación de ambas. Esto era de esperarse debido a que la actividad de cada fibra es completamente independiente una de la otra.

FIGURA 4.- Gráfica de correlación para las fibras 3 y 4.

En el caso de la figura 5 la gráfica presenta una espiga a la derecha del origen lo que representa un número mayor de ocurrencia en ese instante, es decir en determinado momento, a la activación de la fibra le sucede la activación de la neurona, esto es, que 3 excita a 1. Esto toma sentido al recordar que la fibra 3 está conectada directamente a la neurona 1 y esa sinapsis tiene características excitatorias.

FIGURA 5.- Gráfica de correlación para la fibra 3 y la neurona 1.

El comportamiento en la gráfica 6 presenta el mismo comportamiento que la inmediata anterior pero no es igual la densidad de disparos debido a que la actividad no es la misma, esta

diferencia se debe a que las fibras que excitan a las neuronas no tienen la misma probabilidad de disparo y que el peso en las conexiones es diferente.

FIGURA 6.- Gráfica de correlación para la fibra 4 y la neurona 2.

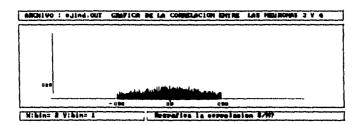

Por último, en la gráfica de la figura 7 se presenta la correlación cruzada de las neuronas l y 2, como era de esperarse esta gráfica no arroja ninguna información que pueda indicar dependencia entre estas neuronas, al igual que en la figura 4 la correlación se hace entre elementos que operan de manera totalmente independiente por lo que el resultado es una gráfica casi paralela al eje de abcisas.

FIGURA 7.- Gráfica de correlación para las neuronas 1 y 2.

#### 3.1.2 Neuronas con conexión directa: Excitación

Ahora se presenta una red con la misma morfología que la anterior pero con características excitatorias entre las neuronas 1 y 2.

FIGURA 8.- Configuración para dos neuronas dependientes con excitación de 1 a 2.

Los valores de los pesos y de la probabilidad de disparo de las fibras se modificaron de acuerdo a lo indicado en la figura 8 con la idea de que las gráficas sean representativas del fenómeno, las probabilidades de disparo de las fibras 3 y 4 son 40% y 10%, respectivamente. Además, a diferencia del diagrama presentado en la figura 2, en este caso si existe una conexión directa entre las neuronas y se representa por la línea que va de 1 a 2, esta tiene características excitatorias con un peso de 8; las demás conexiones permanecen con las mismas características del ejemplo anterior. Una vez hecha la simulación se utilizan las herramientas de NEURORED (diagramas de puntos y correlación) para verificar el comportamiento de la red. Primeramente se obtiene el diagrama de puntos de la figura 9:

FIGURA 9.- Diagrama de puntos de fibras y neuronas para el caso de neuronas con excitación.

A diferencia de la figura 3 en este diagrama de puntos (fig. 9) se nota una activación diferente sobre todo en la neurona 2, esto debido a que ahora no sólo recibe excitación de la fibra 4 sino también de la neurona 1. Como se mencionó anteriormente, las características de las conexiones de la red (con excepción de la excitación) no han cambiado, por lo que el comportamiento entre los demás elementos permanece igual, por esta razón sólo se presenta la gráfica que permite comprobar el efecto excitatorio entre las neuronas.

FIGURA 10.- Diagrama de correlación entre las neuronas 1 y 2.

En la figura 10 es claro que existe una dependencia en la operación de las neuronas 1 y 2. La espiga, ligeramente corrida a la derecha del centro del histograma indica que existe una excitación de la neurona 1 hacia la neurona 2. En otras palabras, la neurona 1 intentará mantener activa a la neurona 2 independientemente de que algún otro elemento, en este caso la fibra 4, lo influya.

#### 3.1.3 Neuronas con conexión directa: Inhibición

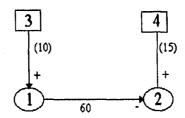

A continuación se presenta un tercer caso en el cual la relación entre las neuronas 1 y 2 es inhibitoria y las probabilidades de disparo para las fibras 3 y 4 son de 70% y 85%, respectivamente y con las intensidades indicadas en la figura 11.

FIGURA 11.- Configuración para dos neuronas dependientes con inhibición de 1 a 2.

Es claro que la topología es la misma que para el caso de la figura 9. Sólo que ahora la sinapsis entre las neuronas 1 y 2 tiene características inhibitorias con un peso de -60 (el signo menos indica que es inhibición), esto se establece en la edición del archivo generado al dar de alta la red. A continuación se presenta el diagrama de puntos de esta simulación:

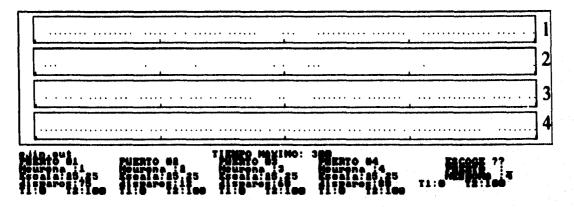

FIGURA 12.- Diagrama de puntos de fibras y neuronas para el caso de neuronas con inhibición.

La presencia de la activación de las neuronas debe cambiar obligadamente ya que a la neurona 2 no le llega el mismo tipo de información que en el caso de la excitación. Para comprobar la dependencia entre estas neuronas se muestra a continuación el diagrama de correlación entre 1 y 2.

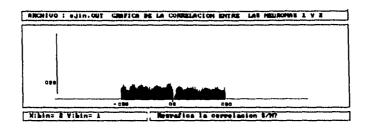

FIGURA 13.- Diagrama de correlación entre las neuronas 1 y 2.

En contraparte al ejemplo de la figura 10 ahora se presenta un hueco ligeramente corrido a la derecha del origen, este caso la correlación indica que existe una inhibición de 1 hacia 2, motivo por el cual la gráfica toma esta forma.

La trascendencia de los pulsos eléctricos y, por lo tanto, de la excitación e inhibición se debe no sólo a su presencia como tales, sino a la sincronización en su ocurrencia y la intensidad con que se presente cada una, es decir, que una excitación puede ser sucedida por otra excitación, un tren de excitaciones o bien por una inhibición o un tren de inhibiciones; en cada caso el impulso puede tener mayor, igual o menor intensidad. Esta secuencia, hasta ahora desconocida, varía para cada tarea que realiza el cuerpo humano, pero es un hecho que ocurre en la ejecución de cualquier tipo de operación desde una tarea común que demande el movimiento controlado de un brazo hasta una tarea abstracta como la realización de un modelo matemático. El equilibrio entre excitación e inhibición en regiones muy específicas del cerebro humano permite la operación ordenada del cuerpo. Por ejemplo, el sistema motor del cuerpo humano se comporta desordenadamente cuando no existen las inhibiciones debidas en el momento adecuado, este desorden se manifiesta por el movimiento involuntario de los músculos del cuerpo como ocurre con el mal de Parkinson o la epilepsia en el peor de los casos. Por el contrario, existen casos de parálisis en los que la movilidad de algún miembro o alguna región del cuerpo no existe aún

cuando se tenga la voluntad de hacerlo, esto debido a que no se generan o reciben la excitaciones en las regiones correspondientes. Así como es posible tener deficiencias motoras pueden ocurrir fallas en la percepción visual, espacial, asociación de ideas, etc. Todas producto de una incorrecta secuencia o intensidad en la excitación o la inhibición en una red neuronal.

Con los tres ejemplos mostrados anteriormente queda clara cual es la idea y la importancia de las características de la conectividad de una red neuronal. Evidentemente para redes neuronales complejas, las neuronas y fibras involucradas son mucho mas que dos, pero el principio de interacción es exactamente el mismo.

## CAPÍTULO 4: LAS REDES NEURONALES ARTIFICIALES

En 1943 Mc Culloch y Pitts (Grey, 1961) publican algunos teoremas de modelos neuronales que establecen:

- La actividad de una neurona se define como un proceso "todo o nada".

- Cierto número de sinapsis se activan, durante un período de adición, con el fin de excitar una neurona. Este número de sinapsis es independiente de la actividad previa de dicha neurona.

- La estructura de las redes es invariante con el tiempo.

El resultado de estos teoremas fue el primer modelo matemático de neurona, que se llamó "Neurona Formal".

A partir de la aceptación de que la actividad de una neurona obligadamente involucra a otras, el concepto de red empieza a tomar fuerza. Este concepto se refiere a la conexión, con características muy específicas en la sinapsis que determinan el grado de dependencia y tipo de influencia que tiene la activación o inhibición de una neurona con la neurona vecina, de al menos un par de neuronas entre las cuales existe cierta interdependencia operacional. En 1949, Donald.

O. Hebb (Hebb, 1949) define por primera vez un método para la asignación de esta "influencia" (que posteriormente llamará "peso sináptico") de acuerdo a la actividad neuronal. A este método se le conoce como "Sinapsis Hebbiana" y se rige por el siguiente postulado neurofisiológico:

"Cuando el axón de una neurona A está en contacto con las dendritas de una neurona B y la excita repetidamente, algún proceso metabólico toma lugar en ambas células. De tal manera

que la eficiencia de la neurona A como una de las neuronas que excita a la neurona B, se incrementa."

La consideración de elaborar sólo una aproximación del comportamiento de la sinapsis y de la neurona biológica en hardware a través de componentes electrónicos es obligada debido a la gran cantidad de factores y la compleja operación que existe entre ellos antes, durante y después de cada sinapsis. Para poder generar una RNA es necesario saber que elementos involucrados en el caso de la sinapsis biológica son imprescindibles y cuales no para la aproximación a la cual se pretende llegar. Es sabido que la estructura del cerebro se establece a partir de una muy alta densidad de interconexión (conexiones hechas a través de las dendritas), entre las neuronas que lo componen lo que significa que existe un gran número de canales de comunicación entre neuronas a través de los cuales viaja información.

Para definir el concepto de Red Neuronal Artificial (RNA) se retomará el esquema básico de red es decir, la conexión entre dos neuronas, sin importar ahora si se excitan o inhiben, como en el ejemplo mostrado en la figura 8. A partir de que existe una conexión entre dos neuronas se puede hablar de una Red Neuronal. En nuestro caso una RNA se obtiene al sustituir a la neurona y la sinapsis por componentes electrónicos configurados de tal modo que su comportamiento sea similar al de los casos mostrados en el capítulo 3, debido a que a partir de ahora la unidad básica de la red no es una neurona como tal, nos referiremos a estas como procesadores. Evidentemente la mayoría de las RNA contienen mucho más que dos procesadores con la idea de que el trabajo se distribuya entre todas en cuanto se le encomiende un proceso a la red. El número de neuronas, tipos de interconexión, algoritmo de operación y, en general, las características fisicas de la red definen lo que se conoce como la arquitectura de la RNA. Cuando se diseña una RNA, definir que

arquitectura deberá tener va a depender fundamentalmente de dos factores: del algoritmo de aprendizaje y del tipo de tarea para la cual sea desarrollada la RNA, a partir de estos parámetros se definen casi automáticamente el resto de los elementos que definen completamente a la red.

## 4.1 El aprendizaje de una red

El aprendizaje, para el caso de una RNA, considerada como un sistema entrada-salida, es la capacidad de "Asociar" las características de una serie de datos presentados a la entrada de la red con una salida o respuesta específica. El aprendizaje de una RNA no comprende únicamente a la capacidad de identificar los patrones con los que se llevó a cabo el entrenamiento, sino también a la capacidad de clasificar una entrada con características diferentes a las que la red "ya conoce" en la categoría que le corresponda. Esto proceso se conoce como la capacidad de generalizar.

Para entender cuando una RNA ha aprendido consideremos lo siguiente:

Sea un conjunto  $U_X$  de "n" vectores "P" con dimensión "E" donde cada vector representa un patrón de entrada:  $(U_X = P_1, P_2, ..., P_{n-1}, P_n)$  a cada patrón  $P_n$  le corresponde un vector  $V_n$  con dimensión "S" que indica el tipo o clase a la que  $P_n$  pertenece. Por ejemplo: Suponiendo que se tienen 4 caracteres diferentes representados en una matriz de 4x4 y nos interesa clasificarlos en 4 diferentes clases, una para cada uno, necesitaremos 2 bits para obtener estas 4 posibilidades de clasificación  $(2^2 = 4)$  y 16 bits para representar cada dígito. Por lo tanto los vectores  $P_n$  y  $V_n$  contienen 16 y 2 componentes respectivamente (E=16 y S=2).

Se dice que la RNA ha aprendido cuando al presentarle un patrón  $P_n$ , la red entrega a la salida la correspondiente clase  $V_n$ , es decir, cuando asocia correctamente  $P_n$  con  $V_n$ . Y que,

además generaliza, cuando al presentarle a la red un patrón P que no pertenezca al conjunto Ux, la RNA entregue una clase V<sub>n</sub> que indique que el patrón de entrada tiene características de él o los patrones que corresponden a dicha clase, es decir, cuando se logre cumplir la generalización.

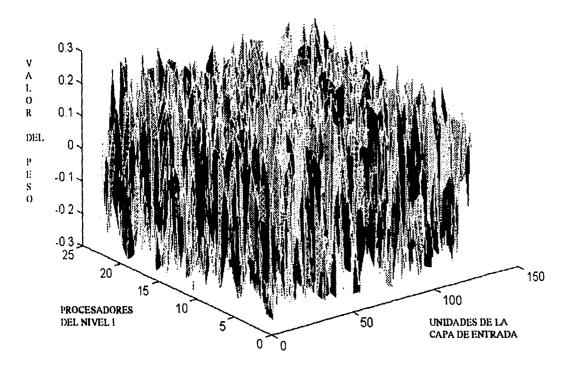

El proceso fundamental para conseguir que la red aprenda es la asignación del valor de cada uno de los pesos sinápticos de los procesadores que conforman la RNA. El proceso de búsqueda de estos valores es propiamente el "entrenamiento de la red" y consiste en ejecutar un determinado algoritmo de aprendizaje, este algoritmo busca mediante iteraciones el valor para cada peso tal que al iniciarse la operación de la RNA se activen o desactiven algunos procesadores de tal forma que la operación global de la RNA permita obtener la respuesta esperada, es decir, la asociación que define al aprendizaje. La decisión de qué algoritmo utilizar depende del tipo de datos que se procesen y del tipo de tarea que se quiera realizar.

Cuando a una RNA se le presentan por primera vez los patrones de entrenamiento y se ejecuta un algoritmo de aprendizaje, se dice que la red está en entrenamiento, es decir, el algoritmo empezará a operar en función de los datos de los patrones de entrenamiento hasta que se obtengan las condiciones establecidas por el algoritmo. En este momento el valor del peso para cada sinapsis estará asignado por lo que se considerará que la RNA está entrenada. A continuación se presenta una clasificación de redes hecha a partir de los parámetros mencionados (tipo de tarea y de datos), indicando en cada caso cual es el algoritmo adecuado para las RNA's en cuestión.

FIGURA 14.- Agrupación de las seis redes clasificadoras más conocidas. (Lippmann., 1987)

En la figura 14 se puede observar que la primera división se establece a partir del tipo de datos con que se trabaje, es decir, que los vectores de entrada que representan los patrones a estudiar pueden estar compuestos por valores digitales (binarios o bipolares) o analógicos, esto dependerá de la representación que se quiera dar al fenómeno. La segunda división se hace a partir del tipo de entrenamiento que recibe cada red, éste puede ser de dos formas: una en la cual la red asocia un conjunto de patrones de entrada a una salida que se conoce de antemano, conocido como aprendizaje supervisado. O bien cuando la red sólo recibe patrones de entrada sin que tengan una salida asociada, conocido como aprendizaje no supervisado.

Las redes de Hamming, Hopfield y Carpenter / Grossberg se han utilizado típicamente en casos en los cuales los fenómenos pueden representarse fielmente como entradas dígitales (Lippmann, 1987), por ejemplo imágenes en blanco y negro en donde la entrada es el valor de los pixeles o bien cuando se trata de textos ASCII en los que la entrada puede representarse por 8 bits. Estas redes resultan poco eficientes para procesos en los cuales el fenómeno se manifiesta con valores analógicos debido a que el patrón original debe ser convertido a digital. Por otra

parte, el resto de las redes mencionadas pueden operar satisfactoriamente con valores de entrada tanto digitales como analógicos (Lippmann, 1987), por ejemplo para procesar señales biológicas o reconocimientos de patrones auditivos entre otros.

#### 4.2 Aprendizaje no supervisado

A diferencia del aprendizaje supervisado, en este caso no se tiene una salida predeterminada para el patrón de entrada a la red, la red recibe sólo las entradas e intenta agruparlas o clasificarlas por si sola. En las redes con este tipo de aprendizaje se lleva a cabo una competencia entre los procesadores de la última capa con el fin de que uno sólo sea el ganador. La adaptación de los pesos y otros parámetros de la red se hace en función de características simbólicas del conjunto de patrones de entrada para que así la red los clasifique en categorías similares. Las redes mas conocidas que operan con este tipo de aprendizaje son: Las basadas en la Teoría de Resonancia Adaptiva (ART) y los mapas organizativos de Kohonen.

## 4.3 Aprendizaje supervisado

Este tipo de aprendizaje depende de la asociación de una entrada a una salida que de antemano se conoce, es decir, para un patrón de entrada (P<sub>n</sub>) debe existir un vector de salida (V<sub>n</sub>) el cual representa su clase o tipo. Este aprendizaje se utiliza principalmente en redes que tendrán una aplicación de memoria asociativa o bien como clasificador de patrones.

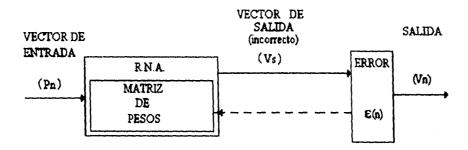

Este proceso de aprendizaje opera, grosso modo, de la siguiente manera: El vector de entrada (P<sub>n</sub>) es presentado a la RNA, ésta genera un vector de salida (V<sub>S</sub>) el cual es comparado con el vector deseado (V<sub>n</sub>) para el patrón de entrada, la diferencia entre estos vectores genera un

error determinado, los pesos de la red son modificados de acuerdo a un algoritmo específico buscando disminuir dicho error. Este procedimiento es repetitivo y el número de veces que se realiza es proporcional a la longitud del vector que representa el patrón de entrada y al número de patrones con que se entrena la RNA. El cálculo del error se hace hasta lograr que éste sea aceptable para cada uno de los patrones de entrada de la red.

Es inadecuado el tratar de determinar que tipo de RNA es mejor, la eficiencia de cada una depende del tipo de aplicación para el que se utiliza, de lo significativo de los datos con que una red se entrene y sobre todo de la interpretación que se tenga de los resultados que la red entrega. Para el caso de este proyecto el algoritmo de retropropagación resulta idóneo aparte de que se cuenta con las herramientas necesarias para hacer una buena representación de una RNA operando bajo esta arquitectura y algoritmo de entrenamiento.

# 4.3.1 Retropropagación

El algoritmo de retropropagación resulta una perfecta herramienta académica, además de sus cualidades en la práctica, para mostrar el proceso de aprendizaje de una red neuronal. La aplicación de este algoritmo se puede hacer en prácticamente cualquier problema que involucre un mapeo de patrones.

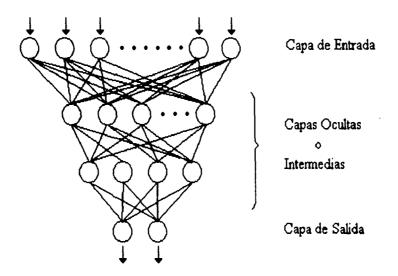

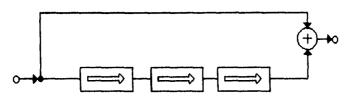

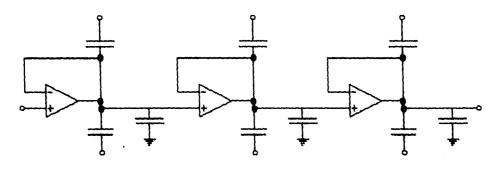

El algoritmo de retropropagación fue propuesto por Paul Werbos en 1974, en forma independiente por Y. Le Cun y D. Parker. La arquitectura de redes que utilizan retropropagación consiste de una capa de procesadores de entrada (con tantos procesadores como elementos tenga el patrón de entrada), una o más "capas ocultas" y una capa de salida. Como se muestra en la figura 15.

FIGURA 15.- Arquitectura para una red con retropropagación.

La conexión se hace sólo entre capas, no existen conexiones entre procesadores de un mismo nivel. Cada procesador debe estar conectado con cada uno de los procesadores del nivel siguiente y nunca se conectan con el nivel anterior, es decir tienen una conexión en cascada.

En las redes que utilizan retropropagación se consideran como niveles de procesadores las capas intermedias y la capa de salida; la capa de entrada queda excluida debido a que su operación no es propiamente la de un procesador, sino que sólo toma el valor del elemento del vector de entrada para entregarlo a la siguiente capa, por lo tanto el número total de procesadores "m" será igual a la suma de procesadores de las capas ocultas y las de la capa de salida.

El peso de la conexión entre las unidades i y la unidad j se denota como Wij. La operación del algoritmo se basa en el principio del gradiente decreciente y se logra de la siguiente manera: Primero se asignan valores arbitrarios a los pesos Wij, una vez establecidos estos valores se presenta a la RNA el patrón de entrada Pn, el cual es propagado por todas las capas

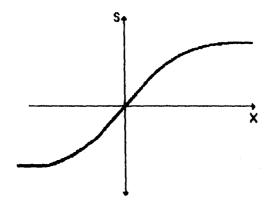

intermedias hasta la capa de salida para poder definir el nivel de activación de cada uno de los procesadores. Para lograr esto cada procesador realiza la suma de todas sus entradas y el resultado lo aplica a una función no lineal, típicamente en una sigmoide, aunque puede utilizarse cualquier no linealidad, para así generar el nivel de activación. La ecuación representativa de la función sigmoidal es la siguiente:

$$S = \frac{1}{1 + e^{-x}}$$

La representación gráfica es:

Si denotamos como Tj a la suma total de las entradas que tiene la unidad j entonces tendremos:

$$T_j = \sum_i U_i * W_{ij}$$

Donde Ui es el nivel de activación de la unidad i y Wij representa el peso sináptico entre el procesador i y el j. La asignación del umbral de activación para el procesador j se obtiene entonces por:

$$U_{j} = \frac{1}{1 + e^{T_{j}}}$$

para lograr que la red converja en el menor tiempo se incorpora un procesador más en cada nivel el cual tiene por definición un umbral igual a uno, este parámetro es conocido como "umbral de bias".

Al presentar un patrón a la entrada de la red, ésta generará una salida Vs la cual será comparada con el valor deseado Vn y de esta comparación surgirá un error denotado por  $\varepsilon$ . Este proceso se hace para cada uno de los patrones de entrada y en forma repetitiva. El proceso de cálculo de error se representa esquemáticamente en la figura 16.

FIGURA 16.- Esquema básico de aprendizaje por retropropagación.

El valor para cada peso es calculado de la siguiente manera:

$$W(t+1) = Wij(t) + \alpha \delta j Ui$$

donde Wij(t) representa el peso de la sinapsis de la neurona i a la neurona j en el instante t.  $\alpha$  es un factor de ganancia.  $\delta$  es el error de j y Ui es el nivel de activación. El valor del peso converge mas rápidamente si se le agrega un término conocido como momentum, por lo que tendremos:

$$W(t+1) = Wij(t) + \alpha \delta j Ui + \beta (Wij(t) - Wij(t-1))$$

donde  $0 \le \beta \le 1$  (Lippmann, 1987).

El error para cada unidad de la capa de salida se calcula de la siguiente manera:

$$\varepsilon_s = (y_s - U_s) f'(T_s)$$

donde  $y_S$  es el valor del patrón deseado para la unidad S,  $U_S$  es el umbral de activación del procesador S y f'(x) es la derivada de la función no lineal. La cantidad de error la da la diferencia ( $y_S$ -  $U_S$ ) en tanto que la derivada de la función sigmoidal escala el error para una corrección más significativa.

El error para cualquier unidad de las capas intermedias se calcula como:

$$\varepsilon_i = \left(\sum_{j} \varepsilon_j * W_{ij}\right) f'(T_i)$$

en este caso se realiza la suma de  $\varepsilon$  para todos los procesadores que reciben salida de la unidad i, con sus respectivos pesos. La derivada de la función cumple el mismo propósito que en la capa de salida.

La evaluación de la red se hace realizando el cálculo del error cuadrático, el cual tiene una tendencia a cero, aplicando siguiente método:

$$\varepsilon = \sum_{i=1}^{n} \varepsilon(t) = \sum_{i=1}^{n} \sum_{i=1}^{m} \left(\frac{1}{2}\right) \left(V_{i}(s) - V_{i}(c)\right)^{2}$$

que resulta ser un caso particular del método de mínimos cuadrados donde se realiza la sumatoria del error de cada uno de los procesadores para cada uno de los patrones.

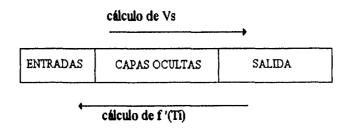

La figura 17 indica en que dirección se realizan los procesos mencionados dando una justificación clara del porque recibe este método el nombre de retropropagación.

FIGURA 17.- Flujo de información en una red con retropropagación

Investigaciones acerca de las iteraciones del cálculo del error (Werbos, 1990) establecen que si el número de patrones de entrenamiento excede el número de pesos en la red es muy probable que el error oscile y no tienda a converger en cero.

### 4.4 Aplicaciones de las RNA

Las RNA han adquirido mucha importancia debido a la gran capacidad de procesamiento que prometen operando en paralelo, esto implica que la velocidad en los procesos encargados a una RNA, aunque sean muy complejos, es muy alta.

La investigación contemporánea sobre RNA se ha enfocado principalmente al desarrollo de algoritmos y simulaciones de redes a nivel teórico, mostrando una gran eficiencia en tareas como clasificación de patrones o memorias asociativas, por ejemplo.

Las simulaciones en software de procesos a muy alta velocidad está obligada a realizarse por pasos regidos por ciclos de reloj, lo que hace de este proceso algo demasiado lento para cumplir con los objetivos. Además de que para implementar un modelo neuronal es necesario trabajar en un gran sistema de ecuaciones paralelas y este modelo es simulado en procesos seriales, esto provoca que la ejecución sea demasiado lenta cuando se compara con estructuras

elaboradas directamente en hardware. Se han realizado simulaciones de grandes redes interconectando computadoras convencionales obteniendo como resultado un proceso ineficiente debido a la gran lentitud de procesamiento (Graf, 1988).

Evidentemente la manifestación del gran potencial que tienen las redes sólo se logrará cuando se implementen los modelos neurales desarrollados teóricamente en un hardware específico y concretamente en Circuitos Integrados (C.I's) especializados para este tipo de arreglos.

Este comportamiento de las redes lleva a pensar en el desarrollo necesario de nuevas arquitecturas de sistemas computacionales.

Actualmente existen aceleradores digitales que ayudarían a disminuir el tiempo de procesamiento pero aún con estos elementos no se logra acelerar significativamente. Varias investigaciones (Graf, 1988) han demostrado que implementando estos modelos con componentes discretos es posible estudiar ciertas características importantes de estos arreglos como por ejemplo su comportamiento dinámico, pero la ejecución con esta técnica arroja un sistema voluminoso y dificilmente útil para un aplicación real.

Los llamados sistemas neuromórficos son el resultado de una red neuronal inspirada en formas biológicas y que contienen software para realizar integración y clasificación visual, síntesis de lenguaje, reconocimiento de caracteres y análisis de riesgos. La elaboración en hardware de sistemas neuromórficos es una gran necesidad para aplicaciones en tiempo real como robótica, reconocimiento de patrones y diferentes tareas de control y aplicaciones de procesamiento de señales. Esta fabricación debe ser ideada de tal forma que cubra tanto la velocidad en la generación de los sistemas de ecuaciones y la utilización de arquitecturas paralelas.

La alta interconectividad que requiere una red neuronal permite pensar en utilizar medios ópticos de conexión para poder realizarla ya que así se pueden hacer un bloque tridimensional. Esto presenta una gran ventaja sobre las conexiones en dos dimensiones a las que orilla una superficie común para C.I., desgraciadamente la tecnología óptica está aún en una etapa muy temprana de desarrollo por lo que no puede pensarse en una aplicación inmediata con estas características (Graf, 1988).

¿Por qué es tan importante la velocidad en los procesos que involucran redes neuronales? La respuesta la ofrecen los sistemas en los que se fundamenta esta filosofía de desarrollo, los sistemas biológicos. Como ejemplo podemos tomar la información visual. Esta información tarda en ser procesada unos cuantos milisegundos. La velocidad de esta respuesta tiene ventajas obvias en cuanto a las posibilidades de adaptación y supervivencia que exige un ambiente dinámico. La técnica que más se aproxima a la realización de estos modelos es la fabricación de dispositivos de propósito especial con una muy alta escala de integración (un Chip V.L.S.I.). Los sistemas neuronales sintéticos (SNS) basados en la tecnología VLSI, pueden entregar tiempos de respuesta similares a los mencionados, lo que los hace útiles para este tipo de aplicación. Por lo tanto sólo con el desarrollo de un hardware específico podremos obtener las velocidades de respuesta suficientes para implementar SNS.

En un sistema biológico, el proceso de aprendizaje y memorización de las células incluye modificaciones continuas en las características de comunicación entre ellas (sinapsis) atribuibles a la liberación y detección de sustancias conocidas como neurotransmisores, a la modificación de la modificación de la modificación de la membrana celular que permiten intercambios selectivos de sustancias con el exterior, entre otros procesos. Algunos de los

mecanismos celulares involucrados en el proceso de aprendizaje mencionados anteriormente no sugieren una elaboración de estos con dispositivos electrónicos convencionales, sin embargo pueden realizarse sistemas, no tan robustos, que logren retener determinada información.

La necesidad de tomar como parámetro a los cerebros biológicos para el desarrollo de sistemas neuronales artificiales es obligada debido a que todo arreglo robusto que involucre procesamiento paralelo está inspirado en ellos. Esta comparación permite conocer datos que si bien indican lo lejano que se está de crear sistemas similares al cerebro, también motiva a implementar mejoras substanciales en las técnicas de generación de SNS. Por ejemplo, en términos de disipación de energía, la comunicación sináptica que es un proceso esencial del Sistema Nervioso Central (SNC), es aproximadamente 100 veces mas efectivo que cualquier computadora actual (Faggin and Mead, 1990). Esta diferencia se atribuye principalmente a que los arreglos operacionales del cerebro minimizan la longitud de las conexiones por sinapsis. Aunque numerosos axones conectan regiones distantes del cerebro, al final de cada axón existe una "ramificación axonal" utilizada para distribuir señales axonales a miles de sinapsis. La longitud de cada axón atribuible a cada sinapsis es entonces reducida por este factor de "fan-out". Esta división de "cable" y la minimización de cables locales dedicados es posible debido a que la mayoría de operaciones son concentradas en zonas cercanas.

### CAPÍTULO 5: REDES NEURONALES DESARROLLADAS EN HARDWARE

Gracias al gran avance que ha existido en las últimas décadas de dispositivos y técnicas de encapsulado, la elaboración de hardware para RNA tiene un campo muy extenso. Estas pueden ir desde la elaboración de un circuito simple que genere una función no lineal (como se considera la operación de una neurona) hasta el diseño o fabricación de una RNA con arquitectura específica y con posibilidad de modificar su estructura. El objetivo en el trabajo de las RNA en hardware puede ser tan ambicioso como el tratar de generar un circuito capaz de reproducir alguna tarea básica del SNC con todos los factores externos que en este se involucran. La gran utilidad de una RNA no depende directamente de la fidelidad con la que represente al sistema biológico en el que esté inspirado, si así fuera aún no existiría aplicación alguna ya que en esta rama el SNC es prácticamente desconocido, sino de lograr obtener aproximaciones a las estructuras ya trabajadas en las que está visto que una correcta manipulación de la información permite optimizar infinidad de tareas.

La atención en este caso se centra en buscar configuraciones que permitan ser diseñadas y posteriormente aplicadas en un circuito integrado a gran escala VLSI. Ya que sólo este nivel, o uno superior de integración, pueden ofrecer una alta velocidad de procesamiento, bajo consumo de potencia, alta densidad de conexión y una aceptable aproximación al sistema biológico. O sea que haría de una RNA un elemento con características que lo colocan como una perfecta herramienta de aplicación y desarrollo.

Existen dos diferentes tendencias en lo que a la elaboración de un SNS se refiere, la primera que busca la ejecución de las ecuaciones de un sistema neuronal y la segunda que persigue la obtención del comportamiento de un sistema biológico en el hardware. La definición

de cual es la tendencia correcta depende de la rama de investigación para la cual se quiera elaborar la RNA, evidentemente para algún neurofisiólogo sería mucho mejor tener una representación de un sistema biológico para modificarlo a placer sin preocuparse por entender o comprobar el cumplimiento de ciertos algoritmos.

El principal problema de diseñar en VLSI un sistema biológico es que el mismo diseño limita en aspectos como la capacidad de conectar elementos a la salida y a la entrada de los dispositivos (fan-in /fan-out). Los sistemas biológicos imponen un alto requerimiento de conectividad que para tan sólo aproximarlos se debería pensar en una técnica de ultra escala de integración (ULSI).

Uno de los retos más grandes en el diseño de hardware de redes neuronales de propósito general es, como ya se ha mencionado, el nivel de interconexión requerido. La interconexión presenta problemas aún cuando se implementa en software. La limitante en este caso es la memoria disponible y la velocidad requerida para hacer tangible el beneficio de estos algoritmos.

Debido al panorama que se presenta con los requerimientos para el diseño de hardware es importante definir la técnica de acoplamiento del sistema en VLSI. Un factor fundamental en el diseño de dispositivos y de sistemas es que exista la capacidad de aislar cada dispositivo del ambiente de los demás componentes excepto de aquellos con los que esté prevista la ocurrencia de determinados efectos planeados a través de la interconexión de la red. Este problema llega a ser serio en el diseño de microsistemas en los que los componentes se empacan demasiado juntos.

La elaboración en VLSI se busca por tres principales razones: Primero, el tamaño de los dispositivos puede ser reducido a través de las técnicas de fabricación y con métodos de litografía. Segundo, el área necesaria para implementar una RNA con esta técnica es mínima. Tercero, la

"habilidad" del circuito puede reducir el número de componentes necesario para el diseño. Existe como limitante el antecedente de que el número de niveles de interconexión sólo se ha elevado un poco en los últimos 28 años, esto es, ha tenido un incremento de dos a cinco veces, lo que representa un gran compromiso para la aceleración en el estudio de técnicas de encapsulado.

La aceptación de que exista un grado de error o tolerancia en la elaboración del diseño de sistemas. VLSI es una buena consideración para poder diseñar e implementar este tipo de sistemas. En circuitos que operan como memorias existen tolerancias para el ahorro de renglones y columnas y aun así son extensamente utilizados, lo mismo ocurre con microprocesadores y controladores.

El problema de utilizar arreglos de dispositivos con alto nivel de integración y acoplarlos con otros no radica en la elaboración de los arreglos sino en introducir un control jerárquico que logre ejecutar completamente los algoritmos necesarios, esto lo podremos ver en algunos ejemplos de fabricación.

En 1982 Hopfield publica una serie de fascinantes características y posibilidades del diseño y arquitectura en VLSI, muchas de sus ideas y aproximaciones habían sido ya expuestas por diferentes investigadores, pero Hopfield fue el primero en presentar esta información con tendencias claras hacia su ejecución en un chip (Hopfield, 1987). Este chip compuesto de elementos analógicos no lineales altamente interconectados podría generar procesos muy eficientes, pero no necesariamente óptimos, en la solución de problemas computacionales complejos.

Existen diferentes métodos para lograr un acoplamiento entre los dispositivos que componen a un C.1, uno de los más promisorios es el autómata celular. En este arreglo cada

elemento tiene una conexión bidireccional con el resto de los elementos vecinos. Cuando se aplica un estímulo al arreglo, el estado de todos los elementos afectados evoluciona hasta lograr estabilizarse. La respuesta del autómata celular a una entrada dada puede ser predicha a través del acoplamiento entre los "vecinos" más cercanos y así obtener el comportamiento de una memoria asociativa, similar a una red neuronal. La diferencia entre un autómata celular y una red neuronal es que la segunda está densamente interconectada en distancias largas, lo que implica un serio problema para la disposición de espacio dentro del chip.

Actualmente los C.I. digitales disipan cerca de 108 veces mas energía por operación que lo que utiliza el cerebro (10<sup>-7</sup> con 10<sup>-15</sup> J por operación) (Zornetzer, 1990). De esta energía un factor de 100 se atribuye a la energía irreducible para la operación de la compuerta de los dispositivos, un factor de 10<sup>4</sup> al número de dispositivos involucrados durante una operación y un factor de 100 optimizando el uso de cable. Es posible disminuir en un factor de 100 la potencia disipada por operación utilizando tecnología de silicio para reducir los niveles de alimentación y compactando las dimensiones de los dispositivos. También se puede mejorar el factor de cableado adoptando patrones de conectividad local en arquitecturas de VLSI. Esto se puede lograr a través de la técnica "escala-oblea". El diámetro de las obleas en producción actual son de aproximadamente 14.5 cm. En un futuro cercano el diámetro de estas obleas podrá ser de 25 a 30 cm. Durante este mismo periodo de tiempo se podrá disminuir el grosor de las líneas de conexión que actualmente van de 1.0 a 1.2 µm podrá ser de 0.3 a 0.4 µm. Estos avances implican que el nivel de integración pueda crecer de 500 millones de componentes por oblea (con 200 um<sup>2</sup> por componente) a 10 mil millones de componentes en una oblea de 25 cm. con un diámetro de líneas de conexión de 0.35 um.

Es claro que la gran importancia que tiene el realizar redes con componentes analógicos radica principalmente en dos cosas: en la velocidad y capacidad de almacenamiento y en la fidelidad en la representación de una red biológica en comparación con lo que puede entregar un circuito puramente digital. También es claro que las ventajas en el estudio de características dinámicas es mas factible en sistemas con componentes digitales ya que para implementar estas se tienen más herramientas

Es muy importante entender que el realizar un método analógico de resolución de problemas no necesariamente implica una técnica de diseño analógica. Es posible tener un diseño de bloques digitales (pueden ser elementos procesadores) para realizar operaciones elementales como sumas, multiplicaciones e integraciones y entonces conectarlo a un bloque analógico capaz de resolver ecuaciones diferenciales.

# CAPÍTULO 6: TÉCNICAS DE DISEÑO DE REDES NEURONALES EN HARDWARE

Gracias a la interconexión y al procesamiento espacio-temporal que se hace en el cerebro al total de la información que recibe cada neurona a través de cada una de sus dendritas, se logra que esta información (visual, auditiva, sensorial, etc.) se procese bajo un esquema distribuido obteniendo así la inmediata capacidad de respuesta, hasta ahora inigualable por cualquier sistema artificial, que ofrece el cerebro en condiciones normales.

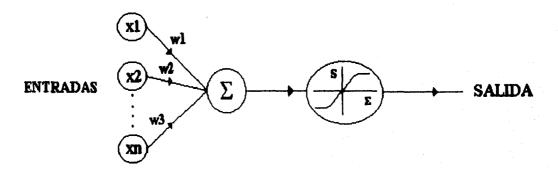

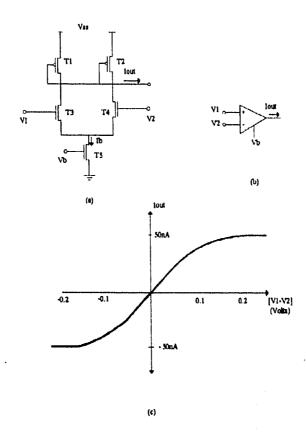

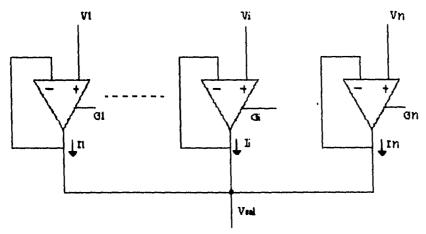

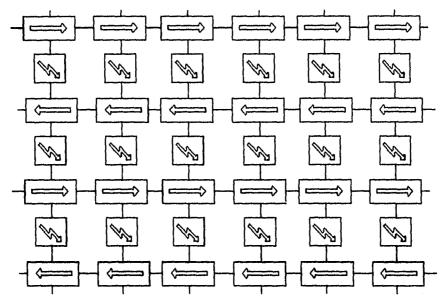

Una aproximación del procesamiento descrito anteriormente que, aunque es muy limitada en relación al comportamiento biológico, es aceptable para las disciplinas que se ocupan del estudio y diseño de redes neuronales y ha sido de mucha utilidad tanto para la investigación como para la industria se presenta en la figura 18.

FIGURA 18.- Diagrama del modelo artificial de neurona.

En la figura 18 las entradas a la neurona están representadas por  $x_1, x_2, ... x_n$ , en el caso de los sistemas neuronales artificiales el valor de cada entrada se multiplica por el valor del peso sináptico Wn que corresponde a esa unión, la consideración del total de la información que recibe la neurona se hace a través de la sumatoria de cada uno de los productos y este resultado se

somete a la no linealidad de la función de transferencia que se aplique a la red; sigmoidal, binario o de umbral (cap. 4), una vez aplicada la no linealidad se define si la neurona se activa o no con excitación o inhibición.

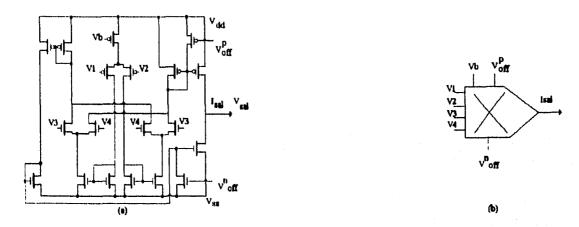

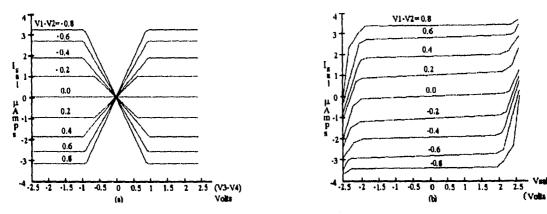

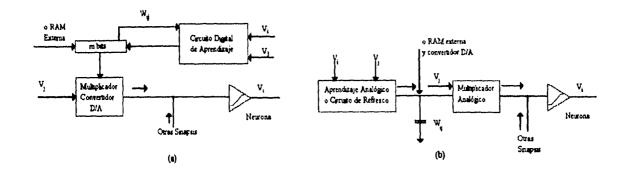

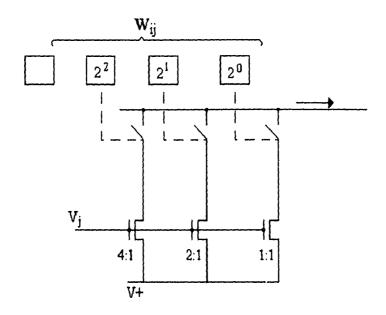

A partir de este modelo de neurona es que la gran mayoría, si no es que el total, de grupos interesados en el desarrollo de RNA's, tanto de software como de hardware, han trabajado.