86 Zejouy

#### UNIVERSIDAD NACIONAL AUTONOMA DE MEXICO

#### FACULTAD DE INGENIERIA

DISEÑO DE UN CONTROLADOR DIGITAL

CON UNIDAD DE DISCO

T E S I S

Que para obtener el Título de

INGENIERO MECANICO ELECTRICISTA

P r e s e n t a n

ABEL GONZALEZ CANCELA

JAIME ALBERTO GASPAR ELIZONDO HUERTA

JOSE ANTONIO MAZA MAGNUSSEN

Director de Tesis: M. I. Lauro Santiago Cruz

MEXICO, D. F.

1995

FALLA DE ORIGEN

UNAM – Dirección General de Bibliotecas Tesis Digitales Restricciones de uso

#### DERECHOS RESERVADOS © PROHIBIDA SU REPRODUCCIÓN TOTAL O PARCIAL

Todo el material contenido en esta tesis esta protegido por la Ley Federal del Derecho de Autor (LFDA) de los Estados Unidos Mexicanos (México).

El uso de imágenes, fragmentos de videos, y demás material que sea objeto de protección de los derechos de autor, será exclusivamente para fines educativos e informativos y deberá citar la fuente donde la obtuvo mencionando el autor o autores. Cualquier uso distinto como el lucro, reproducción, edición o modificación, será perseguido y sancionado por el respectivo titular de los Derechos de Autor.

# DISEÑO DE UN CONTROLADOR DIGITAL CON UNIDAD DE DISCO

Agradecemos el apoyo y la amistad siempre brindados por:

Ing. Rodolfo Peters L.

е

Ing. Lauro Santiago C.

A mi mamá por el ejemplo que me dejó,

Con mucho cariño para mi papá por su enorme apoyo,

A Claudia, con todo mi amor, por su apoyo, comprensión y empuje,

A mis hermanos,

A Samuel.

Alberto Elizondo

Diseño de un Controlador Digital con unidad de disco Facultad de Ingeniería UNAM

3

A ti papá, porque nunca has dejado de estar conmigo.

A mi mamá por su amor.

A mi fiel esposa Gaby.

A Tabé, Mábel y Lenchita.

A Beto, Claudia, Jorge y Pepe por su amistad.

Abel González

A Gabriela por su amor y apoyo, por tu ayer, tu hoy y tu mañana,

A Maria Isabel,

A mi padres por su ejemplo, cariño y consejo,

A Bestemor y Bestefar por sus consejos,

A mis hermanos y amigos.

Jose Antonio Maza

## INDICE

#### INTRODUCCION

#### CAPITULO I PLANTEAMIENTO Y CONFIGURACION DEL SISTEMA

- I.1) Planteamiento

- 1.2) Características del controlador

- 1.3) Enlace con dispositivos de medición

- 1.4) Interfaz con una unidad de discos flexibles

- 1.4.1) Conceptos Generales de la Interfaz

- 1.4.2) Requerimientos de la Interfaz

- 1.4.3) Control de la Interfaz

- 1.5) Interfaz con el usuario

- I.6) Diagrama general de bioques

#### CAPITULO II MANEJO DE ARCHIVOS EN MS DOS

- II.1) Conceptos generales de la estructura de un disco

- II.2) Estructura en MS-DOS

- II.2.1) Area de "Boot"

- II.2.2) Area de "Fat"

- II.2.3) Area del Directorio Raiz

- II.2.4) Area de Archivos

#### CAPITULO III DISEÑO DEL CONTROLADOR

- III.1) Descripción general del controlador

- III.2) Principales componentes del controlador

- III.3) Diagramas de la tarjeta controladora

#### CAPITULO IV PROGRAMACION DEL CONTROLADOR

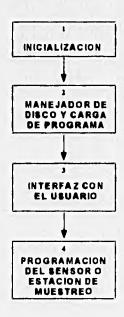

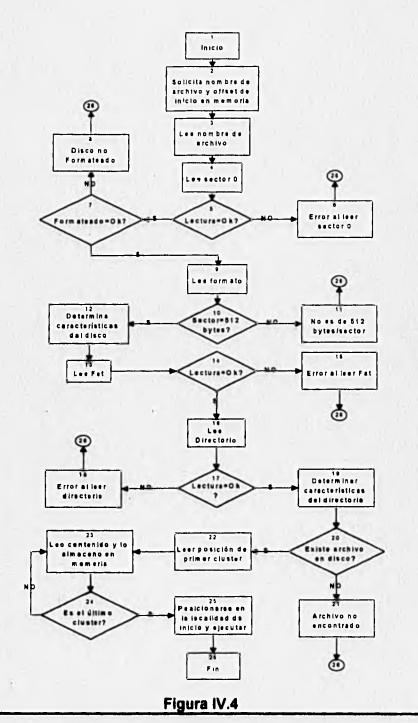

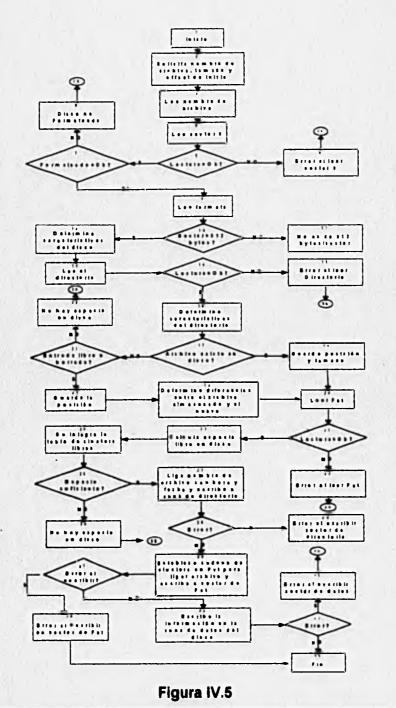

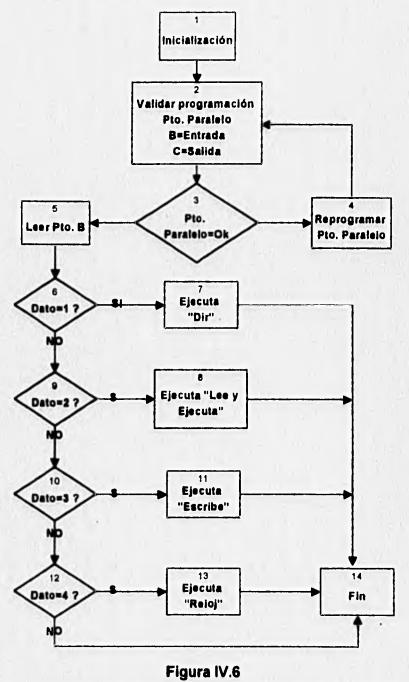

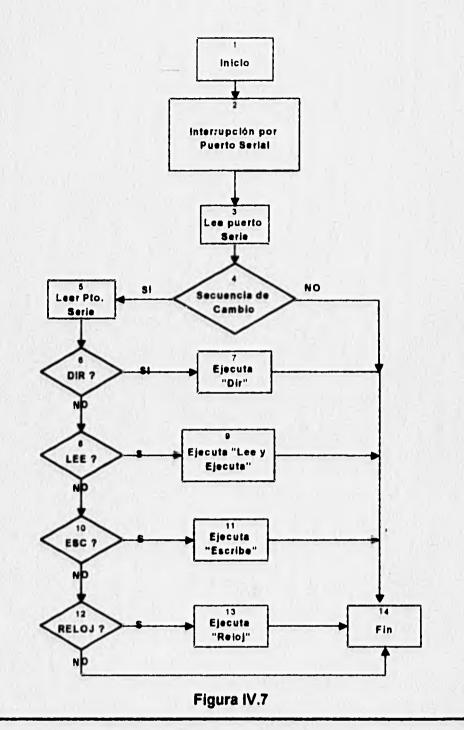

- IV.1) Diagrama general de flujo

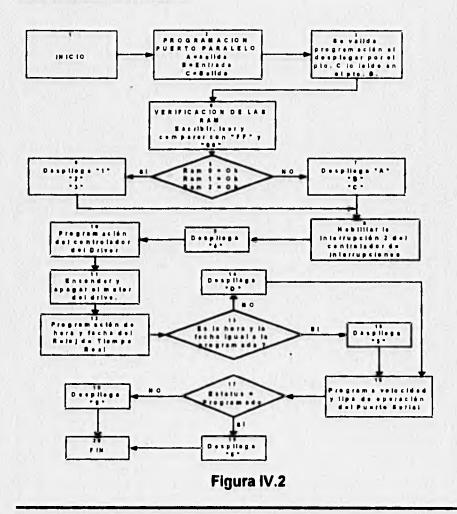

- IV.2) Rutina de inicio

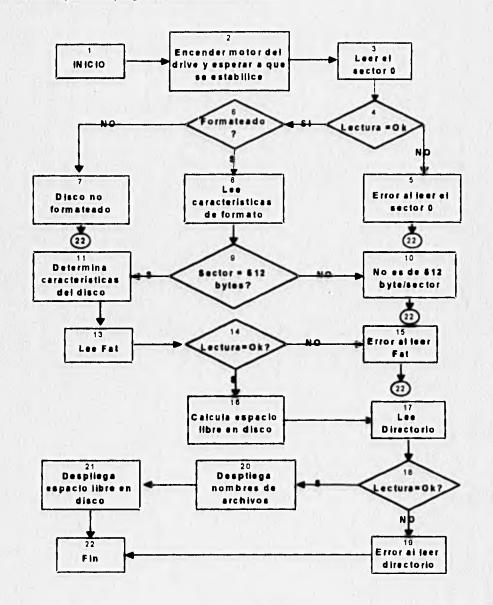

- IV.3) Manejador de disco y carga de programa

- IV.3.1) Rutina de despliegue de directorioIV.3.2) Rutina para leer y ejecutar un archivoII.2.3) Rutina para escribir a disco

- IV.4) Interfaz con el usuario

- IV.5) Lineamientos para la programación del sensor

CONCLUSIONES

BIBLIOGRAFIA

**ANEXOS**

## INTRODUCCION

El origen de esta tesis fue la necesidad de desarrollar un controlador digital flexible que controlará desde un sensor hasta una estación de muestreo almacenando los datos recabados por ésta.

Este trabajo surgió debido a que en el Instituto de Ingeniería de la UNAM se diseñan y desarrollan sistemas digitales de control con una finalidad específica, que al no ser flexibles no son aprovechados en proyectos nuevos.

El objetivo principal de este proyecto es el hacer una tarjeta flexible de bajo costo, con independencia en cuanto a capacidad de almacenamiento y por otro lado, compatible con los estándares del mercado para permitir el procesamiento de la información almacenada.

Este trabajo no intenta desarrollar los elementos para el control del sensor o estación de muestreo en específico ni para la captura de la información, que dependerá directamente del diseño de dicho dispositivo, sino más bien, crear la infraestructura de hardware y software necesarias para poder implementar el software de control y procesamiento que se desee en función de las necesidades particulares del sistema de medición y muestreo de que se trate.

La principal característica de este controlador será el poder almacenar información en un medio magnético (floppy disk) con formato MS-DOS y recibir información del mismo. Esto permitirá darle flexibilidad al diseño, ya que se podrá procesar la información almacenada en cualquier PC compatible y por otro lado, el hecho de que el controlador posea un medio magnético, permitirá hacer manejable su programación.

El "Device Driver" para el manejo de disco, será incluido en la ROM del sistema y se podrá tener acceso a él mediante una rutina de interrupción, de tal forma que para los desarrollos del software de control de un sensor o estación de muestreo, solamente será necesario llamar a dichas interrupciones para lograr el acceso a disco.

### **CAPITULO I**

## PLANTEAMIENTO Y CONFIGURACIÓN DEL SISTEMA

#### 1.1) PLANTEAMIENTO

Los sistemas de adquisición de datos de bajo costo que operan autónomamente son los instrumentos más eficientes y precisos de obtener información del medio ambiente que nos rodea.

Dado que el uso de estos sistemas autónomos de adquisición se ha multiplicado mucho en los últimos años, el Instituto de Ingeniería de la UNAM ha desarrollado controladores para la obtención de perfiles de distribución de agua y estaciones de muestreo para registrar información sísmica y climatológica.

Estos sistemas se adecuan a las necesidades específicas de estos proyectos pero carecen de flexibilidad al no poder ser utilizados para otro fin.

Todos los proyectos tienen en común la necesidad de controlar algún dispositivo externo que sense el entorno, así como almacenar esta información para poder ser analizada posteriormente.

A su vez, todos estos diseños tienen la limitante de no poder almacenar grandes cantidades de información y que el proceso de recuperación de la misma se realiza suspendiendo la obtención de datos.

La información obtenida por estos sensores era traducida y enviada vía serial hacia un PC., lo que implicaba transportar una PC al lugar de la adquisición y desarrollar y ejecutar un programa en la PC para la recepción de la información.

Por lo anterior, se planteó la necesidad de desarrollar un controlador flexible que pudiera adecuarse a las características de estos y otros proyectos permitiendo el almacenamiento y recuperación de grandes volúmenes de información.

#### 1.2) CARACTERISTICAS DEL CONTROLADOR

La idea básica de este diseño es contar con los elementos de salida para controlar el movimiento de sensores o estaciones de muestreo, tener la capacidad de recibir datos del mismo, y poder procesar y finalmente almacenar la información en un medio magnético con formato compatible con MS-DOS. También se prevee la posibilidad de recibir o enviar información vía serie a través de un puerto.

Además, el controlador contará con un teclado y un "display" que permita la comunicación elemental con el usuario, de tal manera que se pueda accesar un archivo y desplegarlo en el "display" o pedirle que tome instrucciones de algún archivo en disco.

La posibilidad de almacenar información en un medio magnético le da flexibilidad al sistema. Por un lado, le da independencia al permitir almacenar grandes cantidades de información, y por otro, ser versátil en su programación, ya que puede programársele en cualquier momento.

Diseño de un Controlador Digital con unidad de disco Facultad de Ingeniería UNAM

14

Se pensó en darle la característica de guardar la información en formato MS-DOS, ya que esto facilitaría el procesamiento de la información almacenada en una PC compatible a través de cualquier hoja de cálculo comercial, lo que haría aun más versátil su funcionalidad.

#### 1.3) ENLACE CON DISPOSITIVOS DE MEDICION

El controlador debe contar con elementos de enlace que le permitan controlar un dispositivo de medición o sensor. El diseño del controlador contempla elementos comunes de hardware para el control del uno o varios sensores diferenciándolos entre sí por software.

De esta forma, el controlador no sólo podrá determinar cuando mover o no un sensor, sino cuando efectuar una lectura a través de este dispositivo.

Esta tesis no contempla en su alcance, el desarrollo del software para controlar un sensor o estación de muestreo en específico, ya que esto depende de las características particulares de estos dispositivos.

#### 1.4) INTERFAZ CON UNA UNIDAD DE DISCOS FLEXIBLE

El punto más importante de esta tesis es la interfaz con una unidad de disco flexible en formato compatible con el sistema operativo MS-DOS.

Diseño de un Controlador Digital con unidad de disco Facultad de Ingeniería UNAM

15

Se consideraron dos alternativas para darle solución a esto. La primera de ellas es la opción de desarrollar todo el hardware necesario para hacer interfaz con una unidad de disco flexible. Esta opción además de resultar cara, implica alcances no contemplados en este proyecto, así como el limitar severamente la posibilidad de actualización de dicha interfaz, ya que se tendría que modificar lanto hardware como software.

La segunda opción, por la cual se decidió, es utilizar una tarjeta controladora de disco flexible para PC XT compatible, de tal forma que sólo se desarrolle el software de interfaz con dicha tarjeta controladora. Esto permite la posibilidad de reemplazar dicha tarjeta con la unidad de disco en caso de querer hacer una actualización al sistema.

#### 1.4.1) CONCEPTOS GENERALES DE LA INTERFAZ

A continuación se describen los requerimientos para hacer la interfaz con una tarjeta controladora de unidades de disco flexible de baja densidad (5 ¼ in.). Estos requerimientos son iguales para cualquier controladora de discos utilizada en una PC XT. Adicionalmente, se describirán las características de interfaz para una tarjeta controladora que maneje discos de alta densidad (3 1/2 in.) normalmente utilizados en las PC AT dejando la posibilidad en un futuro, si así lo requiere las necesidades del proyecto, de utilizar un medio magnético de mayor capacidad de almacenamiento.

#### 1.4.2) REQUERIMIENTOS DE LA INTERFAZ

Las tarjetas controladoras de discos flexibles basadas en el 82072 ocupan un "slot" sobre los canales de Entrada/Salida (E/S) de las computadoras personales.

Como es sabido, el canal de E/S de una PC AT difiere del canal de una PC XT, pero el conjunto de señales utilizado por la tarjeta controladora es el mismo en ambos casos.

La tarjeta controladora de disco requiere los recursos del procesador central, del DMA y del controlador de interrupciones.

El sistema de control de unidades de disco consiste en 5 elementos funcionales:

- 1) Interfaz entre la tarjeta controladora y el canal de E/S.

- 2) Generación de "Chip-Select"

- 3) Generación de Reloj para el 82072

- 4) Interfaz con el DMA

- 5) Interfaz con la unidad de discos

Los puntos 3 y 5 no son del interés de este trabajo, ya que internamente dentro de la tarjeta controladora se encuentra todo el hardware necesario para el manejo de la unidad de disco flexible así como la generación del reloj para el 82072.

La interfaz con el canal de E/S requiere de las siguientes líneas:

- 10 líneas de direcciones (A0 hasta A9)

- 8 líneas de datos (D0 hasta D7)

- 4 líneas para el control de escritura/lectura que son: MEMW^,

MEMR^, IOW^, IOR^.

- 6 líneas para el control que son: RESET, T/C, AEN, DRQ2, DACK2^, IRQ6.

Las señales que tengan un " ^ " significa que son verificadas en estado bajo.

La interfaz con el DMA requiere de tres señales básicas que son T/C

· (Terminal Count), DRQ2 (Data Request en el canal 2 del DMA) y DACK2^ que es

la línea de reconocimiento para dicho canal.

Cabe hacer notar que en un ambiente de PC, la transferencia de información de disco o hacia disco tiene que hacerse en modo byte-byte. Sin embargo en la tarjeta controladora como en otro tipo de sistemas se puede realizar transferencias de bloques completos de información (modo "burst").

La señal IRQ6, es utilizada por la tarjeta controladora para interrumpir al microprocesador. Más adelante veremos la función específica de dicha interrupción.

Para soportar las diferentes capacidades de "drivers" y los diferentes tiempos de transferencia de datos, existen 3 registros incorporados en la tarjeta controladora de discos flexibles. Estos tres registros son los siguientes:

- DRR (Data Rate Register)

- DIR (Digital Input Register)

- + DOR (Digital Output Register)

#### **DRR (Data Rate Register)**

(Controladoras de diskette de alta densidad exclusivamente).

Este registro de sólo escritura y seleccionado en la dirección 3F7H especifica la unidad de disco y el tipo de disco utilizado. El valor de este registro es utilizado por la tarjeta controladora de alta densidad para seleccionar la velocidad de transferencia de datos y la velocidad de giro de la unidad de disco. A continuación se muestra una tabla con la decodificación para este registro.

| D1       | D0 | DESCRIPCION          |

|----------|----|----------------------|

|          |    | RESERVADO            |

|          | •  | DD DRIVE DD DISKETTE |

| > •      |    | QD DRIVE DD DISKETTE |

| <b>P</b> | •  | QD DRIVE QD DISKETTE |

DD = Doble Densidad y QD = Cuádruple Densidad

Tabla I.1

#### **DOR (Digital Output Register)**

Este registro es de sólo escritura y se encuentra en la dirección 3F2H. A continuación se presenta una tabla con el significado de cada uno de los bits que conforman este registro

| BITS . | DEFINICION                                                                                                                                                                                                                                                      |  |  |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|        | Selección de Drive: 0 en este bit indica que el drive A está seleccionado, 1 indica que el drive B está seleccionado.                                                                                                                                           |  |  |

|        | Reservado: Puede ser 0 ó 1                                                                                                                                                                                                                                      |  |  |

| 2      | Función de Reset: Cuando este bit es puesto a 1, la función de reset es deshabilitada                                                                                                                                                                           |  |  |

|        | Habilita DMA e Interrupción: Cuando este bit es puesto a 1, las<br>lineas para DMA y la de Interrupción son habilitadas                                                                                                                                         |  |  |

|        | Habilitador del Motor del Drive A: Cuando este bit es puesto a 1, la<br>señal de habilitar el motor A es activada. Un "timer" es dedicado a<br>realizar la función de deshabilitar el motor. El "timer" es inicializado<br>en función del comando seleccionado. |  |  |

|        | Habilitador del Motor del Drive B: Igual que el bit anterior                                                                                                                                                                                                    |  |  |

| 90     | Reservado: Igual que el bit 1                                                                                                                                                                                                                                   |  |  |

| 7 (1)  | Reservado: Igual que el bit 1                                                                                                                                                                                                                                   |  |  |

Tabla I.2

#### **DIR (Digital Input Register)**

(Controladoras de diskette de aita densidad exclusivamente).

Este registro es de sólo lectura y el único bit usado por la tarjeta controladora de discos flexibles es el 7.

Este bit es utilizado exclusivamente cuando se está manejando un drive de alta densidad. La función primordial de este bit es informar al sistema que un

diskette ha sido cambiado (cuando está puesto a 1). Este bit es automáticamente puesto a 0 cuando se realiza una operación de búsqueda (Seek).

A continuación se presenta una tabla mostrando el mapa de direcciones con los registros mencionados.

| DIRLCCION   | TIPO DE ACCESO | REGISTRO            | MODELO |

|-------------|----------------|---------------------|--------|

| <b>CONT</b> |                | NO USADO            |        |

| <b>**</b>   |                | NO USADO            | 5      |

| * ##        | ESCRITURA      | DIGITAL OUTPUT REG. | XT/AT  |

| 97.94       |                | NO USADO            |        |

| 7.6         | LECTURA        | MAIN STATUS REG.*   | FDC    |

|             | ESC./LEC.      | DATA REGISTER *     | FDC    |

|             |                | NO USADO            |        |

| 471         | ESCRITURA      | DATA RATE REGISTER  | AT     |

| en.         | LECTURA        | DIGITAL INPUT REG.  | AT     |

FDC = Floppy Disk Controler

Tabla 1.3

#### 1.4.3) CONTROL DE LA INTERFAZ

El FDC (Floppy Disk Controler) controla los motores de la unidad de discos y las cabezas, además de manejar el flujo de datos de y hacia los sectores del disco. Una tarjeta controladora puede manejar hasta 4 unidades de disco.

<sup>\*</sup> Estos registros son utilizados tanto en una XT ó AT

El FDC maneja 15 operaciones en total, de las cuales utilizaremos 8 :

- SPECIFY

- SENSE DRIVE STATUS

- SENSE INTERRUPT STATUS

- . SEEK

- RECALIBRATE

- \* READ DATA

- \* WRITE DATA

- READ ID

**SPECIFY**: Este comando coloca los valores iniciales para cada uno de los tres temporizadores o timers. El "Head Unload Time" (HUT), el "Step Rate Time" (SRT) y el "Head Load Time" (HLT).

SENSE DRIVE STATUS: Este comando se utiliza cuando el procesador desea obtener el estado de las unidades de disco.

SENSE INTERRUPT STATUS: Una señal es generada por el Floppy Disk Controler dependiendo de situaciones específicas que pueden ser de utilidad para el programador.

**SEEK**: Este comando permite posicionar la cabeza en un "track" ó cilindro determinado.

RECALIBRATE: Este comando es utilizado para colocar la cabeza de la unidad de discos al "track 0" y tener un punto de inicio.

WRITE DATA: Comando utilizado para escribir información a disco.

READ DATA: Comando utilizado para leer información de disco.

**READ ID**: Este comando es utilizado para dar la posición actual de la cabeza en función del agujero índice que traen todos los discos.

Las operaciones en el Floppy Disk Controler se realizan en tres fases: la fase de comando, la de ejecución y la de resultado.

En la fase de comando, uno o más bytes son enviados al "Data Register" del FDC. La secuencia de bytes es estricta y varia dependiendo del comando. El FDC reconoce el comando e inicia la fase de ejecución. Finalmente, durante la fase de resultado, un número de bytes se genera para informarle al procesador el estado de la operación. Es imperativo que no exista error en el número de bytes enviados o leídos a o del "Data Register".

El número de bytes enviados o leídos depende de la operación que realice el FDC. Para el caso de lectura o escritura a un sector, se necesitan 7 bytes adicionales al comando en sí. Estos siete bytes indican track, cabeza, sector y cuatro bytes adicionales. El primero de los cuales es el número de bytes por sector (en el caso más utilizado es 2 para 512 bytes por sector). El segundo indica el número de sectores por track (9 para un floppy de 360 kbytes). Los

últimos dos bytes indican el "Gap Lenght" y el "Data Lenght" (Normalmente 2AH y FFH respectivamente).

A continuación se describe los pasos a seguir por el procesador para leer un sector determinado en un disco.

- Enviar la señal para encender el motor y esperar a que estabilice su velocidad.

- 2) mover la cabeza del drive a la posición de inicio de lectura mediante la operación de búsqueda ("seek").

- 3) Monitorear el fin de la operación de búsqueda a través del cambio de estado del bit 7 del byte de "status" de la operación seek.

- 4) Inicializar al DMA para mover los datos a memoria.

- 5) Enviar las instrucciones al FDC.

- 6) Leer la información del FDC.

- 7) Apagar el motor.

En páginas anteriores mencionamos que la tarjeta controladora de discos flexibles utiliza la interrupción No.6 (IRQ6) para indicarle al procesador que terminó la operación de búsqueda a través de modificar el estado del bit 7 del byte de "status" de la operación seek en la BIOS DATA AREA localidad 0040:003E.

La IRQ6 es utilizada para evitar que el procesador esté continuamente leyendo el "Status Register" del FDC, ya que la operación de búsqueda es la que más tiempo ocupa en el acceso a disco y además su tiempo varía dependiendo

de donde se encuentre posicionada la cabeza,. Esto le permite al procesador realizar actividades síncronas en paralelo al movimiento de la cabeza del drive.

#### INTERFAZ CON EL USUARIO

La interfaz contemplada para este diseño consta de un "display" alfanumérico de cristal líquido y un teclado estándar de matriz. Estos tienen la función de permitir la comunicación elemental entre el usuario y la tarjeta controladora de tal manera que se pueda realizar las siguientes operaciones:

| 1) | DIR                                       | -Desplegar nombres de archivo en disco- |  |

|----|-------------------------------------------|-----------------------------------------|--|

| 2) | LEE Y EJECUTA                             | -Pasar información de disco a memoria y |  |

|    |                                           | ejecutar a partir de esa localidad-     |  |

| 3) | ESCRIBE                                   | -Pasar información de memoria a disco-  |  |

| 4) | RELOJ -Programar el reloj de tiempo real- |                                         |  |

-Programar el reloj de tiempo real-

Para lograr la máxima flexibilidad en el diseño, la interfaz con el usuario no se limitan al teclado y al "display", sino que abarca la comunicación vía serial con una computadora personal.

Si es que se requiere, se puede sustituir el teclado y "display" local de este controlador por el monitor y el teclado de la PC. Esto nos permite graficar y procesar la información en el lugar y en el momento de la adquisición de la misma.

#### 1.6) DIAGRAMA GENERAL DE BLOQUES

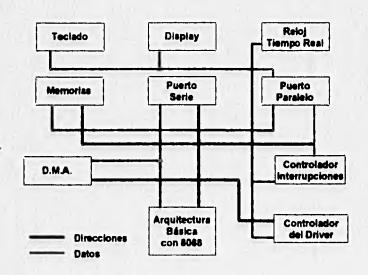

Integrando los elementos presentados en este capítulo, el diagrama general de bloques del controlador digital tiene las siguientes caracterísiticas.

#### CONTROLADOR DIGITAL

FIGURA 1.1

Diseño de un Controlador Digital con unidad de disco Facultad de Ingeniería UNAM

26

## **CAPITULO II**

## MANEJO DE ARCHIVOS EN MS-DOS

#### II.1) CONCEPTOS GENERALES DE LA ESTRUCTURA DE UN DISCO

El almacenamiento en disco está basado en dos cosas principalmente: tecnología de grabado y un esquema de rápido acceso.

La tecnología utilizada es el grabado magnético. El grabado digital magnético es hecho en una superficie de material magnéticamente sensible, usualmente de una forma de óxido de cobre, lo cual le da su color característico café. El recubierto magnético es muy delgado y usualmente cubre a un material de soporte plástico de tipo "mylar".

La superficie del disco es tratada como una matriz de puntos. Cada uno de estos puntos son caracterizados como bits y podrán ser puestos a su equivalente magnético "0" ó "1". Debido a que la localización de estos puntos no está precisamente determinada, los esquemas de almacenamiento involucran marcas para reconocer posiciones. Esta es una de las razones por las cuales los discos tienen que ser "formateados" previamente antes de ser usados.

En lo que respecta al esquema de rápido acceso, existe una diferencia entre el concepto de cinta magnética, -que es escencialmente lineal porque la información tiene que ser almacenada en ésta del frente hacia atrás y no hay manera sencilla de saltar al centro de la misma-, y un disco rotatorio.

El disco rotatorio tiene dos características importantes que hacen posible el llegar a cualquier parte de su superficie rápidamente.

Diseño de un Controlador Digital con unidad de disco Facultad de Ingenlería UNAM

28

La primera es la rotación del disco. El disco gira sobre sí mismo a 300 R.P.M., es decir que cada 120 milésimas de segundo se tendrá acceso al mismo lugar en sentido circunferencial.

La segunda es el movimiento de la cabeza grabadora, la cual atraviesa el disco en forma radial de la parte más externa hasta la parte más interna del disco y viceversa. Este movimiento se realiza en un promedio de 100 milisegundos. Utilizando estos dos factores es como se puede llegar a cualquier parte del disco en un tiempo muy corto. Esta es la razón por la cual los discos son llamados unidades de almacenamiento de acceso aleatorio, ya que podemos accesar cualquier dato directamente sin necesidad de pasar a través de toda la información de manera secuencial como lo haríamos en una cinta magnética.

Para el uso en una computadora personal, el disco es dividido en anillos concéntricos, llamados cilindros o "tracks". El número de "tracks" varía dependiendo del tipo de disco.

Independientemente del número de "tracks" que posea un disco, estos son siempre identificados por un número, empezando por el "0" que es el track más alejado del centro del disco.

Al igual que la superficie del disco es dividida en anillos concéntricos, cada anillo concéntrico es dividido a su vez en partes llamadas "sectores" que son de un tamaño fijo.

Diseño de un Controlador Digital con unidad de disco Facultad de Ingeniería UNAM

29

Todas las lecturas o escrituras a disco son hechas en términos de sectores completos. Los sectores son identificados mediante números asignados a ellos.

Para los propósitos particulares de este proyecto, se utilizarán discos de doble densidad, es decir, el grabado al disco se realiza alternamente en ambas caras. Lo que implica contar con dos cabezas lectoras.

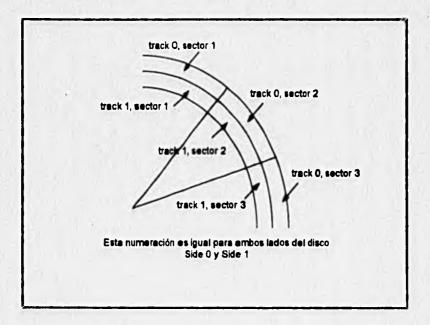

Los discos de doble densidad cuentan con 40 "tracks" por lado, 9 sectores por "track" y cada sector es de 512 bytes (figura II.1)

Figura II.1

#### II.2) Estructura en MS-DOS

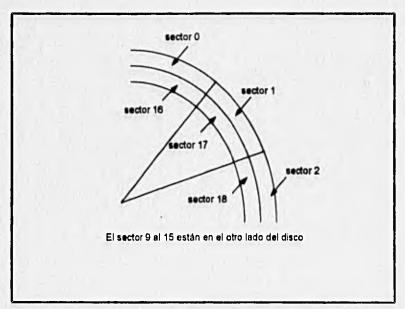

Como ya mencionamos anteriormente, el sector en un disco es la unidad fundamental para las operaciones del mismo. Para el sistema operativo MS-DOS, no existen tracks, ni lados, solamente sectores. DOS numera los sectores de un disco de manera secuencial empezando con "0" para el primer sector del track 0 del lado 0 y continuando con el segundo sector del mismo track y del mismo lado, cuando termina un track continua con el mismo track pero del otro lado del disco (figura II.2).

Figura II.2

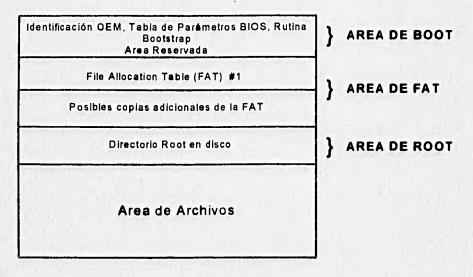

Para organizar la información en un disco, DOS divide a éste en dos partes: Una parte pequeña, la cual DOS utiliza para mantener registro de información clave acerca del disco, y la zona mayor para los datos en sí. La primera es conocida como área del sistema y a su vez es dividida en tres partes: área de "boot", área de "FAT" y área del directorio Raíz (Root).

Figura II.3

#### H.2.1) AREA DE BOOT

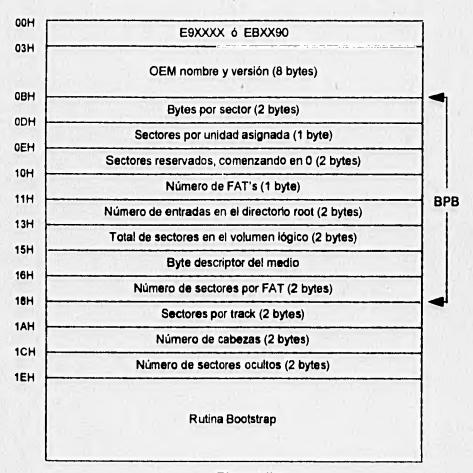

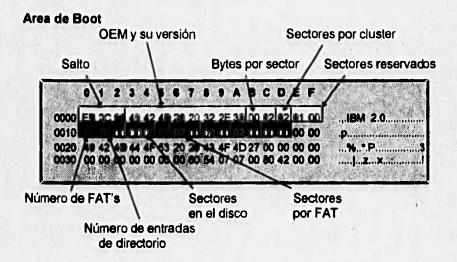

El área de "boot", contenida en el sector lógico "0", contiene toda la información indispensable acerca de las características del medio magnético (ver figura II.4).

El primer byte en el sector es siempre una instrucción de salto, que puede ser dentro del segmento (opcode 0E9H) seguida de un desplazamiento de 16 bits o un salto corto (opcode 0EBH) seguido de un desplazamiento de 8 bits y después por un NOP (opcode 90H). Si ninguno de estos dos saltos está presente implica que el disco no está formateado.

Figura II.4

Después de la instrucción inicial de salto, en el byte 03h, encontramos un campo de 8 bytes reservado para la identificación del programa que formateó el disco.

El tercer componente de esta sección es el Bios Parameter Block (BPB) localizada entre los bytes OBH y el 17H. Esta estructura describe las características físicas del disco y permite al "device driver" calcular las direcciones físicas para un sector lógico dado. También el BPB contiene información que es usada para calcular la dirección y tamaño de cada una de las áreas de control del disco (área de FAT y área del directorio Raíz).

Después de BPB se encuentran tres palabras (offset 18H, 1AH y 1CH) que le especifican al "device driver" el número de secotres por FAT, de cabezas y de sectores ocultos.

El último elemento que compone el sector de boot (offset 1EH) es el programa de "bootstrap" que se encarga primitivamente de transferir el control al Basic Input Output System "BIOS" de máquinas compatibles con MS-DOS.

El sector de boot es parte del área reservada que puede ser de varios sectores. El tamaño de esta área reservada está escrito en el BPB en el desplazamiento 0EH.

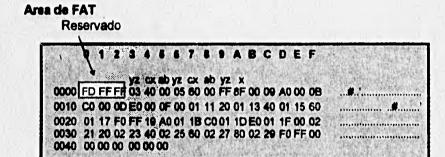

#### 11.2.2) AREA DE "FAT"

Esta área debe sus siglas a "File Allocation Table", y es de suma utilidad para que el sistema operativo mantenga información acerca del área de datos. Esta área es simplemente una tabla de números, donde se relacionan para cada archivo, los sectores del área de datos asociados a éste.

Un archivo, al ser creado o modificado, se le asignan o reasignan sectores del disco en potencias de 2 conocidas como "allocation units" o clusters. El número de sectores por cluster está definido en el BPB en el byte ODH.

La FAT está dividida en campos que corresponden directamente a clusters asignados en el disco. Estos campos son de 12 bits o de 16 bits según la versión del sistema operativo y de la capacidad del medio magnético de que se trate (12 bits si es disco flexible y 16 bits para discos duros).

Los primeros dos campos en la FAT son reservados, en el caso de discos flexibles donde la FAT es de campos de 12 bits, serán los tres primeros bytes. Para discos duros cuya FAT es de 16 bits, los dos primeros campos ocupan cuatro bytes. En ambos casos, los primeros 8 bits del primer campo reservado contiene una copla del "media descriptor byte" que también se encuentra en el BPB. El resto de los bits del primer campo y del segundo campo son 1.

Por el número almacenado en cada entrada de la FAT, se determina el estado que tienen cada uno de los clusters, que a su vez corresponden a sectores del disco. En la tabla II.1 se describe el posible contenido de los campos.

| VALOR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | SIGNIFICADO                   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | CLUSTER DISPONIBLE            |

| A ALLES ALLES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | CLUSTER RESERVADO             |

| erial) de la                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | CLUSTER DAÑADO                |

| Carlotte and The                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ULTIMO CLUSTER DEL ARCHIVO    |

| CONTRACT CON | SIGUIENTE CLUSTER DEL ARCHIVO |

Tabla II.1

Cada entrada de archivo en el directorio del disco contiene su cluster de inicio. Este cluster inicial nos indica la posición dentro de la tabla de la FAT donde está almacenado el siguiente cluster del archivo. Esto se repite hasta localizar el cluster que señala el fin de archivo.

La forma en como se interpreta el contenido del área de Boot y de la File Allocation Table (FAT) se muestra a continuación.

Figura II.5

Del Bios Parameter Block (BPB) se obtiene:

- 512 Bytes por sector (0200h)

- 2 sectores por cluster (02h)

- 2 sectores por FAT (0002h)

- 2 FAT's (02h)

- 112 entradas de directorio (0070h)

Diseño de un Controlador Digital con unidad de disco Facultad de Ingeniería UNAM De esta información podemos calcular el número del sector de inicio lógico de cada una de las áreas de control del disco y del área de archivos contruyendo una tabla como sigue:

| AREA                  | LONGITUD   | NÚMERO DE SECTOR  |

|-----------------------|------------|-------------------|

| And the second second | 1 sector   | 00                |

|                       | 2 sectores | 01 - 04           |

|                       | 7 sectores | 05 - 0Bh          |

|                       |            | 12 sectores (0Ch) |

Por lo tanto, el primer sector del área de archivos es el 12 (0Ch)

Tabla II.2

Al leer el disco en el sector correspondiente al inicio de la FAT (sector 01) obtenido en la tabla anterior se puede observar la secuencia de los cluster de algunos archivos (Figura II.6)

Figura II.6

Diseño de un Controlador Digital con unidad de disco Facultad de ingeniería UNAM En la figura anterior se observa que los primeros dos clusters (formados por los 3 primeros bytes) son reservados. El primer archivo inicia a partir de ellos en el cluster 2, y siguendo la secuencia "xyz" y "abc" se relacionan los siguientes clusters como se muestra en la siguiente tabla:

| GLUSTER   | 02        | 03        | 04        | 05        | 006       |

|-----------|-----------|-----------|-----------|-----------|-----------|

| CONTENIDO | 003 (xyz) | 004 (abc) | 005 (xyz) | 006 (abc) | FFF (xyz) |

Tabla II.3

#### II.2.3) AREA DEL DIRECTORIO RAIZ

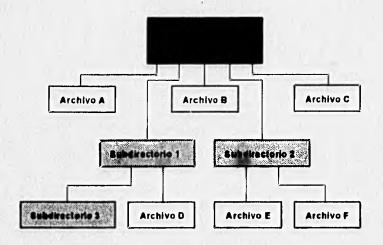

El- directorio raíz puede ser visto como un catálogo que describe el contenido de un disco. Esta área lleva los nombres de los archivos dentro del área de datos, así como el nombre de los archivos especiales llamados subdirectorios.

El tamaño y la posición del directorio raíz es fija y está determinada por el formato del disco. El número de entradas en el directorio raíz y la localización del mismo pueden ser determinados mediante la información del BPB como se mostró con el ejemplo anterior.

Cada disco tiene un único directorio raíz, en el cual puede haber desde ningún subdirectorio hasta tantos como el disco pueda almacenar. Estos

subdirectorios a su vez pueden contener tantos subdirectorios como se deseen (figura II.7)

Figura II.7

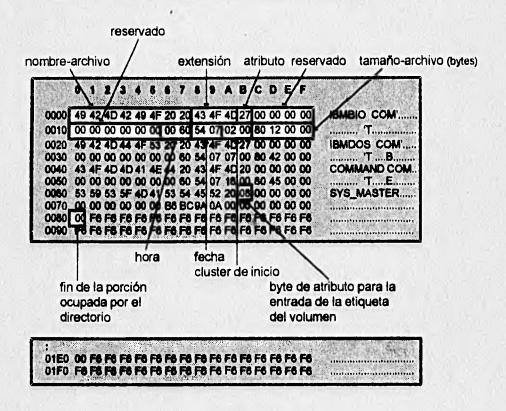

Cada entrada del directorio raíz, ya sea nombre de archivo o nombre de subdirectorio, tiene un espacio único de 32 bytes. En la siguiente figura vemos las características de esta entrada.

| BYTE  | DESCRIPCION        | COMENTARIOS |

|-------|--------------------|-------------|

|       | NOMBRE DEL ARCHIVO | NOTA 1      |

|       | EXTENSION          |             |

|       | ATRIBUTOS ARCHIVO  | NOTA 2      |

|       | RESERVADO          |             |

|       | TIEMPO             | NOTA 3      |

|       | FECHA              | NOTA 4      |

|       | CLUSTER INICIAL    | NOTA 5      |

| OOLCH | TAMAÑO ARCHIVO     | 4 BYTES     |

Tabla II.4

#### Notas a la Tabla II.4:

NOTA 1: El primer byte del campo del nombre de archivo puede contener la siguiente información:

| VALOR      | SIGNIFICADO                                                                                                                                                                                                                      |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 00H        | LA ENTRADA A ESTE DIRECTORIO NUNCA HA SIDO USADA, FIN DEL DIRECTORIO                                                                                                                                                             |

| <b>06H</b> | EL PRIMER CARACTER DEL NOMBRE DE ARCHIVO ES ACTUALMENTE E5H                                                                                                                                                                      |

| 2EH        | LA ENTRADA ES UN ALIAS PARA EL ACTUAL SUBDIRECTORIO. SI EL SIGUIENTE BYTE ES 2EH, ENTONCES EL CAMPO DEL CLUSTER CONTIENE EL NUMERO DE CLUSTER DEL DIRECTORIO PREDECESOR (CERO SI EL DIRECTORIO PREDECESOR ES EL DIRECTORIO RAIZ) |

| te:        | EL ARCHIVO HA SIDO BORRADO                                                                                                                                                                                                       |

NOTA 2: El byte de atributos es codificado como sigue:

| BIT                                    | SIGNIFICADO                                         |  |  |  |  |

|----------------------------------------|-----------------------------------------------------|--|--|--|--|

|                                        | SOLO LECTURA                                        |  |  |  |  |

|                                        | ARCHIVO OCULTO                                      |  |  |  |  |

|                                        | ARCHIVO DEL SISTEMA                                 |  |  |  |  |

|                                        | ETIQUETA DEL VOLUMEN                                |  |  |  |  |

|                                        | SUBDIRECTORIO                                       |  |  |  |  |

|                                        | ARCHIVO (ENCENDIDO CUANDO EL ARCHIVO ES MODIFICADO) |  |  |  |  |

| ************************************** | RESERVADO                                           |  |  |  |  |

|                                        | RESERVADO                                           |  |  |  |  |

NOTA 3: El campo del tiempo se codifica como sigue:

| BITS     | CONTENIDO '                                                                   |  |  |  |

|----------|-------------------------------------------------------------------------------|--|--|--|

| oon ogh  | NUMERO BINARIO DE MULTIPLOS DE 2 SEGUNDOS (0-29, CORRESPONDE A 0-58 SEGUNDOS) |  |  |  |

| OCEH-CAH | NUMERO BINARIO DE MINUTOS (0-59)                                              |  |  |  |

| dell     | NUMERO BINARIO DE HORAS (0-23)                                                |  |  |  |

NOTA 4: La codificación del campo de la fecha es:

| BITS    | CONTENIDO             | * 2 |

|---------|-----------------------|-----|

| COLOCAL | DIA DEL MES (0-31)    |     |

|         | MES (1-12)            |     |

|         | AÑO (ASOCIADO A 1980) |     |

NOTA 5: El campo del tamaño del archivo es interpretado como un entero de 4 bytes, con los dos bytes menos significativos almacenados primero.

Si el disco es utilizado para cargar el sistema operativo, las dos primeras entradas en el directorio raíz siempre son para los archivos del MS-DOS BIOS y del MS-DOS KERNEL.

También el directorio raíz puede contener una entrada especial llamada etiqueta del volumen, la cual da el nombre a todo el disco.

Diseño de un Controlador Digital con unidad de disco Facultad de Ingeniería UNAM En la figura II.8 se muestra el primer sector de un directorio raíz:

Figura II.8

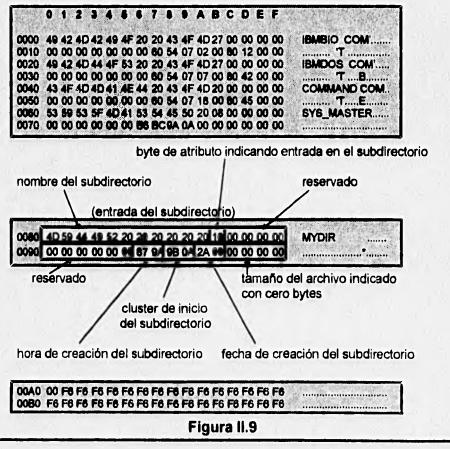

Como mencionamos, los subdirectorios son un tipo de archivo especial que pueden contener descriptores de archivos de datos o apuntadores a otros subdirectorios. Una entrada de este tipo de archivo se caracteriza por tener el bit 4 puesto en 1 del byte de atributos y 0 en el tamaño de archivo. El campo del número de cluster apunta al primer cluster que implementa el subdirectorio.

Los cluster adicionales sólo pueden ser encontrados siguiendo la cadena de clusters a través de la FAT. En la siguiente figura se muestra la entrada a un subdirectorio.

Diseño de un Controlador Digital con unidad de disco Facultad de Ingeniería UNAM Dentro de un subdirectorio, el formato de entrada para un archivo o para otro subdirectorio es exactamente igual que en el directorio raíz, es decir que las entradas son únicas y de 32 bytes.

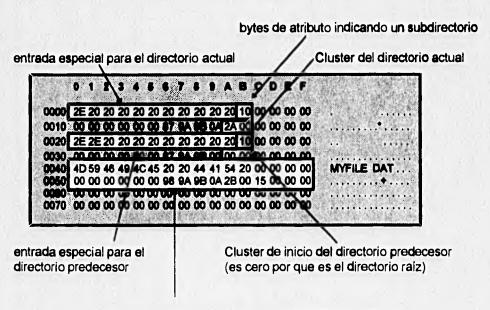

Existen dos entradas especiales "." y "..", que todos los subdirectorios tienen y que se generan al momento de su creación y no pueden ser borradas. El punto se refiere al subdirectorio actual con la característica de que el campo de cluster apunta al cluster en el cual el subdirectorio se encuentra. El doble punto se refiere al subdirectorio predecesor donde el campo del cluster apunta al primer cluster del directorio predecesor. Si el directorio predecesor es el raíz, este campo es cero. A continuación se muestra el primer block de un subdirectorio.

Primer archivo del subdirectorio (MYFILE.DAT)

Figura II.10

Diseño de un Controlador Digital con unidad de disco Facultad de Ingeniería UNAM

# **CAPITULO III**

# DISEÑO DEL CONTROLADOR

# III.1) DESCRIPCION GENERAL DEL CONTROLADOR

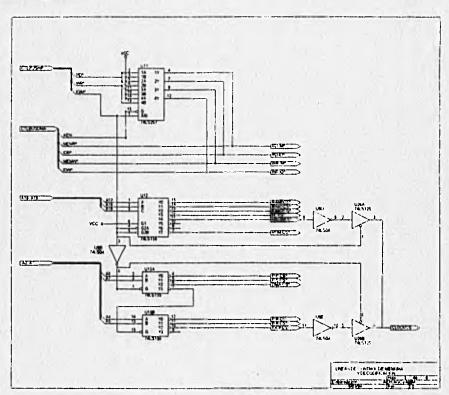

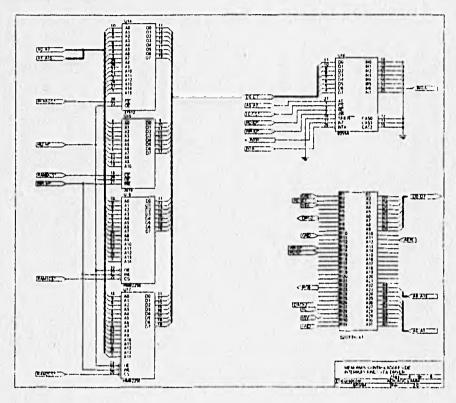

El controlador está compuesto por un procesador 8088, controladores de acceso directo a memoria, controladores de interrupciones y del "driver". Además cuenta con dispositivos de entrada y salida en serie y paralelo, memorias ROM y RAM y un reloj de tiempo real. Así como elementos para interactuar con el usuario: un "display" de cristal líquido y un teclado de matriz.

En la figura III.1 se muestra un diagrama de bloques del controlador:.

Figura III.1

Aunque en la figura III.1 no se muestra una computadora personal, se puede utilizar ésta para sustituir al "display" y al teclado de matriz en la interacción con los usuarios.

El controlador se diseñó usando básicamente integrados de los denominados "LSI" (Integración en gran escala) y complementando con integrados de menor complejidad, encargados de "adaptar" las señales provenientes de integrados de familias distintas.

En contraste con los componentes mayores, que son integrados LSI o VLSI construidos típicamente con tecnología MOS, o alguna pequeña variación de ésta, los integrados que realizan la "adaptación" suelen ser constituidos con tecnología bipolar TTL, con baja o media escala de integración (SSI o MSI).

Gracias a esta tecnología, el sistema puede codificar y decodificar las señales de control y separar y combinar señales de direcciones y de datos provenientes de los chips procesadores y controladores.

En los sistemas actuales se hace imprescindible el poder combinar estas señales (control, datos y direcciones) debido a que, en general, hay más señales necesarias que líneas para transportarlas.

# III.2) PRINCIPALES COMPONENTES DEL CONTROLADOR

#### Microprocesador 8088

El microprocesador que se escogió para desarrollar este sistema fue el 8088 ya que es de bajo costo, está ampliamente disponible en el mercado nacional y reúne las características necesarias para el diseño.

Diseño de un Controlador Digital con unidad de disco Facultad de Ingeniería UNAM

El 8088 es un microprocesador con atributos tanto de procesadores de 8 como de 16 bits. Está diseñado para operar autogenerando sus señales del bus de control (modo mínimo) o para depender de un controlador de buses externo como el 8288 (modo máximo).

La configuración que se utiliza es la mínima, porque ésta soporta los requerimientos del controlador además de simplificar el diseño.

Entre las principales características de este procesador es que tiene un bus de direcciones de 20 bits, lo que le permite accesar hasta un millón de bytes direccionándolos de 00000(H) a FFFFF(H) divididas en segmentos de 16 bits (64 kbytes).

Todos los accesos a un segmento de memoria están referenciadas a la dirección base donde inicia dicho segmento y a incrementos tomados a partir de la base.

Otra característica es que este procesador comparte el bus de direcciones con el bus de datos (A0-A7 con D0-D7), esto se hace mediante un multiplexado en el tiempo, es decir, se envian señales distintas en tiempos diferentes por las mismas líneas. Por ejemplo, durante el acceso a memoria, la dirección se envia en el primer ciclo de reloj y los datos en los ciclos posteriores.

Sin embargo, como las memorias requieren que la dirección y el dato se presenten simultáneamente, es necesario contar con lógica intermedia que separe y guarde temporalmente tanto el dato como la dirección, y usar

Diseño de un Controlador Digital con unidad de disco Facultad de Ingeniería UNAM

determinadas señales del procesador para diferenciar a las direcciones de los datos y si estos se leen o escriben a un puerto o memoria. Estas señales de control que genera el procesador son seis y se agrupan en el bus de control del procesador.

De estas señales: Address Latch Enable (ALE) y Data Enable (DEN) se utilizan para que la lógica intermedia pueda determinar si la información enviada es una dirección o un dato. Gracias a ellas, parte de la circuitería externa al CPU puede trabajar con las direcciones e ignorar los datos, mientras que otra parte de la misma circuitería ignora las direcciones para guardar la información sobre los datos.

Las otras señales que componen el bus de control son: Data Transmition/Reception (DT/R^), Input Output/Memory (IO/M^), Read (RD^) y Write (WR^). Todas ellas utilizadas para controlar el flujo de datos y direcciones de y hacia el procesador.

Las señales que utiliza el procesador para ceder ordenadamente el control del bus del sistema al DMA ante una solicitud de éste son HOLD y HLDA.

El microprocesador reconoce dos tipos de interrupciones, las de software y las de hardware. Esta última, se clasifica en mascarables y no mascarables. La no mascarable está ligada a la señal NMI y tienen una prioridad superior a las mascarables que se reciben a través de la señal Interrup Request (INTR).

Diseño de un Controlador Digital con unidad de disco Facultad de Ingeniería UNAM

Las interrupciones por software se reciben a través de código máquina, relacionándolas con una tabla de hasta 256 elementos de 4 bytes cada uno, que contienen el apuntador a la dirección donde se localiza el programa de servicio a esa interrupción. Esta tabla se localiza en las localidades absolutas de 0 a 3FFH que es el primer kbyte de memoria.

### Generador de Pulsos de Reloj 8284

El Generador de Pulsos de Reloj 8284 genera cuatro señales importantes para el controlador.

La primera, CLK, que son los pulsos de reloj que determinan la velocidad de funcionamiento del sistema (los pulsos generados tienen un ciclo de trabajo de 33%). Esta señal es generada a una frecuencia de 4.77 MHz por medio de un cristal de 14.318 MHz conectado al generador.

La de RESET, que inicializa al procesador, y ejecuta las instrucciones empezando con la localidad de memoria predeterminada (FFFF0H). En algunos casos, permite interrumpir un programa que ha entrado en un bucle infinito.

La tercera, READY, que sincroniza al procesador con los dispositivos de más lento acceso.

Y la de PCLK (Reloj Periférifo), cuya frecuencia es la mitad de la de CLK, con un ciclo de trabajo de 50% del período.

Diseño de un Controlador Digital con unidad de disco Facultad de Ingeniería UNAM

# Controlador Programable de Acceso Directo a Memoria 8257

El 8257 es un controlador programable de cuatro canales de acceso directo a memoria, que permite la tranferencia de bloques de información de hasta 64 kbytes entre la memoria y un dispositivo periférico (un puerto o el controlador del "driver") sin la intervención del procesador.

Este componente recibe las solicitudes del dispositivo periférico a través de las señales de entrada DRQ (0-3). El 8257 solicita el control del bus del sistema al procesador con la señal HRQ, que el procesador recibe vía HOLD, y espera respuesta de éste a través de HLDA.

El dispositivo periférico es avisado de que su solicitud será atendida con las señales DACK (0-3).

El 8257, atiende las solicitudes en base a su programación inicial, que establece la forma en que serán atendidas las solicitudes. Estas pueden ser de una manera cíclica o de modo fijo, es decir, asignando siempre mayor prioridad al canal 0 y menor prioridad al canal 3.

En base a la prioridad predefinida, suministra al sistema la dirección base de la memoria que cada canal tiene asignado y genera las señales de control de escribir o leer tanto a memoria como al periférico para que la transferencia directa de información se lleve a cabo.

Diseño de un Controlador Digital con unidad de disco Facultad de Ingeniería UNAM

El 8257 mantiene el control del bus del sistema y repite la sequencia de transferencia de información mientras el periférico mantenga su solicitud o hasta que se hallan transmitido un número específico de bytes, que es cuando activa la señal TC (Terminal Count), informándole al periférico que la transferencia ha sido realizada.

Para programar este circuito, primero hay que activar su CS<sup>^</sup>, lo que lo habilita para trabajar en modo programación o "esclavo". Después, hay que inicializar el registro de dirección y de cuenta terminal para el canal que se va a utilizar y por último enviar la palabra de control que establece el modo de operación del canal. Esto se realiza en el programa de inicialización del controlador.

Los tres posibles modos de operación de cada canal son: lectura del DMA (transfiere datos de memoria a un periférico), escritura (transferencia del periférico a memoria), y verificación (validación de cualquiera de las operaciones anteriores). El modo de operación es selecccionado a través de los bits más significativos del registro de cuenta terminal del canal.

Cabe aclarar que para facilitar la programación de la tarjeta, se puede activar el AUTO LOAD a través de la palabra de control. Esto permite que el canal 2 sea utilizado en repetidas operaciones sin necesidad de volver a programar el registro de dirección. Esto lo hace internamente el DMA guardando las referencias del canal dos en el tres.

El 8257 mantiene el control del bus del sistema y repite la sequencia de transferencia de información mientras el periférico mantenga su solicitud o hasta que se hallan transmitido un número específico de bytes, que es cuando activa la señal TC (Terminal Count), informándole al periférico que la transferencia ha sido realizada.

Para programar este circuito, primero hay que activar su CS^, lo que lo habilita para trabajar en modo programación o "esclavo". Después, hay que inicializar el registro de dirección y de cuenta terminal para el canal que se va a utilizar y por último enviar la palabra de control que establece el modo de operación del canal. Esto se realiza en el programa de inicialización del controlador.

Los tres posibles modos de operación de cada canal son: lectura del DMA (transfiere datos de memoria a un periférico), escritura (transferencia del periférico a memoria), y verificación (validación de cualquiera de las operaciones anteriores). El modo de operación es selecccionado a través de los bits más significativos del registro de cuenta terminal del canal.

Cabe aclarar que para facilitar la programación de la tarjeta, se puede activar el AUTO LOAD a través de la palabra de control. Esto permite que el canal 2 sea utilizado en repetidas operaciones sin necesidad de volver a programar el registro de dirección. Esto lo hace internamente el DMA guardando las referencias del canal dos en el tres.

Diseño de un Controlador Digital con unidad de disco Facultad de Ingeniería UNAM

Este circuito también comparte el bus de direcciones con el bus de datos mediante un multiplexado en el tiempo. A diferencia del procesador, que comparte A0-A7 con D0-D7, el DMA lo hace en A8-A15 con D0-D7. También se utiliza lógica externa y las señales del bus de control del DMA para reconocer el tipo de información que está enviando.

Las señales de control son: Input/Output Read (I/OR), I/O Write (I/OW), Memory Read (MEMR), Memory Write (MEMW), Address Enable (AEN) y Address Strobe (ADSTB).

### Memorias RAM 2016 y HM62256

El controlador utiliza memorias de acceso aleatorio de tipo estático, es decir, que no requieren de un proceso de reescritura (refresco) para asegurar la integridad de la información.

Entre las características de la tarjeta controladora, se consideró el uso de memorias de acceso aleatorio de dos capacidades diferentes. Una de 1 kbyte por 8 bits utilizada para almacenar información propia del funcionamiento de la tarjeta controladora o de los dispositivos de medición. De esta forma el programador del sistema de adquisición, no necesita mezclar datos procedente de los dispositivos de medición, con información necesaria para su control.

Diseño de un Controlador Digital con unidad de disco Facultad de Ingeniería UNAM

Adicionalmente, se contemplan dos memoria de 32 kbytes por 8 bits para almacenar temporalmente la información proveniente de los sensores o estaciones de muestreo mientras ésta es guardada en el disco flexible.

Ambas memorias son de rápido acceso (100 ns), lo que asegura que no se requieran señales para su sincronización.

#### Memoria EEPROM 27512

La memoria de sólo lectura tiene una capacidad de 64 kbyte por 8 bits, para almacenar el programa de inicialización y control básico de toda la tarjeta, así como el "device driver" para el manejo del controlador de disco. Esta memoria es el único elemento de la tarjeta controladora que debe reprogramarse en el caso de que se cambie el medio magnético de almacenamiento.

# Controlador de Interrupciones 8259

El diseño de este sistema requiere que los dispositivos de entrada salida como el teclado, "display", los puertos serie y paralelo y el controlador del drive sean atendidos eficientemente por el procesador, es decir, que el procesador minimice el tiempo de atención a estos dispositivos.

El método más común para atender este tipo de necesidades es el poleo. En este enfoque el procesador debe recorrer secuencialmente a todos los

Diseño de un Controlador Digital con unidad de disco Facultad de Ingeniería UNAM

dispositivos preguntándoles si alguno requiere ser atendido. Es fácil observar que al aumentar el número de dispositivos conectados a la tarjeta aumenta el tiempo que el procesador debe dedicar a barrer todos los dispositivos, disminuyendo, en la misma proporción, la velocidad de ejecución del programa principal.

Un método más deseable es aquel que permite que el procesador esté ejecutando su programa principal y que sólo lo suspenda para ejecutar la rutina de servicio de un dispositivo cuando el mismo dispositivo así lo solicita, volviendo posteriormente, a la rutina principal en el punto donde suspendió su ejecución. De esta manera, el número de dispositivos a atender puede aumentar sin afectar el tiempo de respuesta del sistema y sólo requiere que a todos los dispositivos se les asigne un orden con el cual serán atendidos por el procesador. Este método es llamado interrupción.

En la tarjeta utilizamos el controlador programable de interrupciones 8259 que puede operar y priorizar hasta 8 interrupciones solicitadas al procesador. Internamente esta compuesto de dos registros: el registro de solicitudes de interrupción (IRR) sobre el que se determina la prioridad de las interrupciones y el registro de atención de interrupciones (ISR) que informa al procesador de las interrupciones que están siendo atendidas

Este integrado opera de la siguiente manera: recibe la solicitud de interrupción de uno de los dispositivos activándose su bit del IRR, lo analiza y envia la señal de INTR al procesador, éste, a su vez, al reconocerlo responde con un pulso de INTA^ activando el bit que le corresponde en el registro ISR del

Diseño de un Controlador Digital con unidad de disco Facultad de Ingeniería UNAM dispositivos preguntándoles si alguno requiere ser atendido. Es fácil observar que al aumentar el número de dispositivos conectados a la tarjeta aumenta el tiempo que el procesador debe dedicar a barrer todos los dispositivos, disminuyendo, en la misma proporción, la velocidad de ejecución del programa principal.

Un método más deseable es aquel que permite que el procesador esté ejecutando su programa principal y que sólo lo suspenda para ejecutar la rutina de servicio de un dispositivo cuando el mismo dispositivo así lo solicita, volviendo posteriormente, a la rutina principal en el punto donde suspendió su ejecución. De esta manera, el número de dispositivos a atender puede aumentar sin afectar el tiempo de respuesta del sistema y sólo requiere que a todos los dispositivos se les asigne un orden con el cual serán atendidos por el procesador. Este método es llamado interrupción.

En la tarjeta utilizamos el controlador programable de interrupciones 8259 que puede operar y priorizar hasta 8 interrupciones solicitadas al procesador. Internamente esta compuesto de dos registros: el registro de solicitudes de interrupción (IRR) sobre el que se determina la prioridad de las interrupciones y el registro de atención de interrupciones (ISR) que informa al procesador de las interrupciones que están siendo atendidas

Este integrado opera de la siguiente manera: recibe la solicitud de interrupción de uno de los dispositivos activándose su bit del IRR, lo analiza y envia la señal de INTR al procesador, éste, a su vez, al reconocerlo responde con un pulso de INTA^ activando el bit que le corresponde en el registro ISR del

Diseño de un Controlador Digital con unidad de disco Facultad de Ingenieria UNAM

controlador de interrupciones y borrando el del IRR. Al mismo tiempo el 8259 determina la interrupción con la más alta prioridad.

Cuando el procesador genera el segundo pulso INTA<sup>^</sup>, el 8259 libera una palabra de 8 bit que contiene la dirección de inicio de la rutina de servicio al bus de datos de donde lo lee el procesador. Esto completa el ciclo de interrupción entre el procesador y el controlador de interrupciones, que borra el bit del registro ISR de la interrupción atendida. El procesador, por su parte, guarda la posición del programa que estaba ejecutando e inicia la ejecución del programa de la interrupción solicitada.

Para programar este integrado se debe habilitar la señal de CS^ y enviarle de dos a cuatro bytes con los comandos de inicialización (ICW).

El comando de inicialización uno (ICW1) le informa al controlador la forma de operar al sambio de las señales de solicitud de interrupción (nivel o transición), si operará en cascada con otros 8259's y si requiere identificar al procesador que lo controla. En nuestro caso, operará al cambiar el nivel de la señal de solicitud de interrupción (y no por transición), no se le enviará la palabra ICW3 por no operar en cascada con otros 8259 y que debe esperar el comando ICW4 para identificar al procesador como 8088.

El comando de inicialización dos (ICW2), le indica al controlador la dirección de inicio de las rutinas de servicio de cada interrupción. En cada palabra los 5 bits más significativos son las dirección (A15-A11) y los tres bits menos significativos identifican a la interrupción.

El cuarto comando (ICW4), le informa al controlador que el procesador del sistema es un 8088, que active la terminación automática de interrupciones (AEOI) en vez de esperar que la rutina de servicio genere la señal de interrupción terminada (EOI).

El controlador permite a través del uso de las palabras de control de operación (OCW) que se inhiban determinadas interrupciones, en nuestro caso habilitamos la interrupción 6 que permite que el controlador del "driver" interrumpa al procesador y la interrupción 7 que se efectua cuando el puerto serie recibe la secuencia de cambio de interfaz con el usuario.

# Interfaz programable Serie 8251

En el diseño del sistema se incluyó un interfaz programable para la transmisión en serie, ya que resulta la manera más sencilla de conectarlo con una computadora. Normalmente se utiliza la transmisión en serie pues requiere un menor número de cables, permite transmisiones a grandes velocidades con menos errores debidos al ruido.

El 8251 es un receptor/transmisor con operación síncrona o asíncrona (USART) que acepta los datos en paralelo que le envía el procesador y los convierte en una secuencia de datos para su transmisión en serie o viceversa, recibir en serie para transformarlos a paralelo. Este circuito le avisa al procesador cuándo puede recibir otro dato en paralelo para su transformación y transmisión en serie o cuándo ya convirtió un dato recibido en serie a paralelo.

Puede operar en dos modos: en el modo síncrono, donde una vez iniciada la comunicación continuamente existe intercambio de información protocolaria entre el emisor y el receptor en bloques que se envían como una unidad a una frecuencia de transmisión dada. Cabe aclarar que en el caso de que no haya dato disponible a transmitirse, el 8251 automáticamente genera y transmite caracteres de sincronia.

En el modo asíncrono, se envían unidades de hasta 10 bits (bit de inicio, bits de datos, bit de paridad y bit de fin), únicamente cuando existe información a ser transmitida. La ventaja de este modo de transmisión es que sólo se distrae al procesador para la recepción de información y no para procedimientos de sincronización.

Para simplificar la conexión entre el controlador y la PC, se decidió trabajar con el modo de transmisión asíncrono.

Antes de inciar la recepción o transmisión de información, el 8251 debe ser programado por dos palabras de control generadas por el procesador. Estas dos palabras definen completamente el modo de operación. Las palabras de control están divididas en dos formatos: la de instrucción y la de comando.

El formato de instruccion define las caracterísitcas generales de operación, es decir, si opera en modo síncrono o asincrono, si generará y verificará bits de paridad, la longitud de la palabra y sincronía externa para el modo síncrono y el número de bits de stop para el modo asíncrono.

Diseño de un Controlador Digital con unidad de disco Facultad de Ingeniería UNAM

En el formato de comando se controla la operación del modo de comunicación seleccionado, a través de las funciones para habilitar la transmisión/recepción, el reset de errores y el control del modem.

Para que este integrado pueda interrumpir al procesador a través del controlador de interrupciones 8259 es necesario conectar la señal de RxD (Receiver Ready) al pin de la interrupción 7 del 8259.

#### Generador de Baud Rate MC14411

Para generar la velocidad de transmisión serial se utiliza un Generador de Baud Rate MC 14411. Este integrado es un generador de bases de tiempo programable. Tiene 16 salidas que nos proporciona una determinada frecuencia dependiendo de la selección del rango deseado. Este circuito tiene cuatro rangos a escoger dependiendo del factor a multiplicar la frecuencia del cristal (1.8432MHz) y hasta 35 diferentes frecuencias. En nuestro caso se optó por tomar el primer rango de frecuencias por ser estas las normalmente utilizadas.

#### Interfaz programable Paralelo 8255

Las transmisiones en paralelo son útiles en todas aquellas aplicaciones que requieren una gran velocidad y utilicen dispositivos no demasiado alejados entre sí (requiere de un mayor número de líneas para la transmisión de información).

Diseño de un Controlador Digital con unidad de disco Facultad de Ingeniería UNAM

No hay ninguna sincronización especial en las transmisiones en paralelo. La velocidad máxima de transmisión está limitada por la rapidez con que el sistema pueda operar los datos.

Este integrado consta de tres puertos paralelos (A, B y C), cada uno de 8 bits. El puerto C se puede dividir en dos puertos de 4 bits cada uno.

Existen tres modos de operación que pueden ser seleccionados por software para definir el funcionamiento de los puertos: Modo 0 (Basic Input/Output), Modo 1 (Strobed Input/Output) y Modo 2 (Bi-Directional Bus).

En el Modo 0, los puertos A, B y C pueden funcionar como entradas o salidas donde las salidas son "latched" y las entradas no. Como el puerto C puede ser dividido en dos puertos de cuatro bits, este modo de operación genera 16 posibles combinaciones.

En el Modo 1, se tienen dos grupos de operación 1 o 2. Cada uno de ellos contiene un puerto de 8 bits de datos (A ó B) que puede ser programado como entrada o salida donde ambas son "latched" y otro de 4 (la mitad de C) para la información de control y estatus en forma bidireccional.

El modo 2 se establece al puerto A como un bus bidireccional de 8 bits y ocupa 5 líneas del puerto C para control del mismo.

En el diseño se utiliza el modo de operación 0, donde A y C son puertos de salida y B es un puerto de entrada.

Diseño de un Controlador Digital con unidad de disco Facultad de Ingeniería UNAM

### Reloj de tiempo real RTC 58321

El reloj de tiempo real proporciona la fecha y la hora para la grabación de los archivos de información proveniente de los dispositivos de medición.

Este reloj tiene la ventaja de contar con un oscilador integrado, por lo que no requiere un cristal externo para su base de tiempo.

Entre sus características primordiales está el poder multiplexar su bus de direcciones con el de datos.

Durante su programación se le habilita como memoria para leer o escribir un dato que puede ser la fecha o la hora y como dispositivo de entrada/salida para identificar el dato a utilizar.

Es posible programar segundos, minutos, horas, dia, semana, mes y año (lleva el control de años bisiestos).

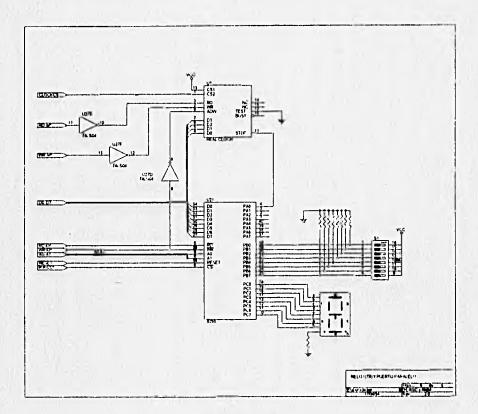

# HI.3) DIAGRAMAS DEL CONTROLADOR

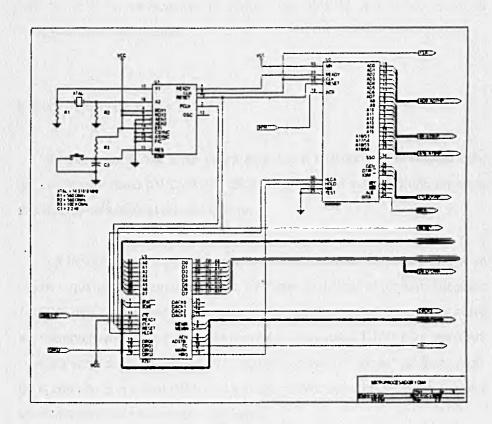

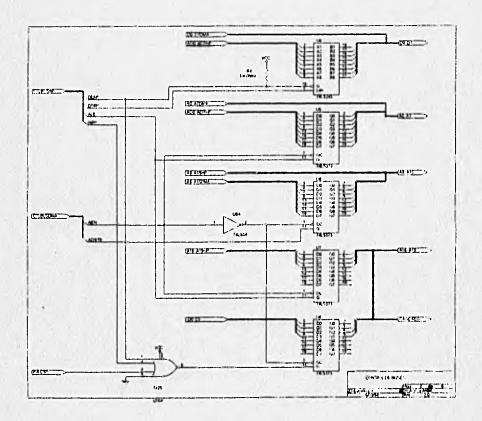

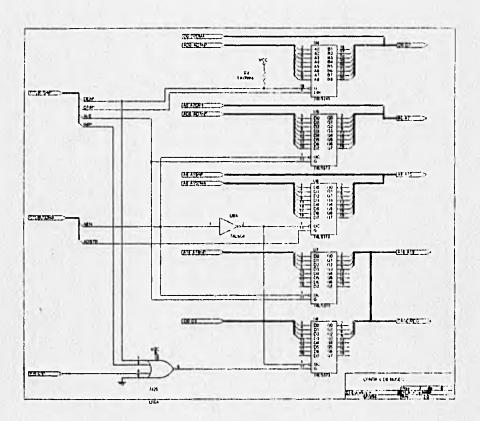

#### III.3.1) Arquitectura básica con 8088 y DMA

En la figura III.2 se muestra el diagrama de conexión entre el procesador 8088, el generador de pulsos de reloj 8284 y el DMA 8257.