## FACULTAD DE INGENIERIA

"MUESTREADOR DIGITAL DE DATOS SINCRONIZA-BLE CON SOFTWARE PARA REALIZAR FUNCIONES DE OSCILOSCOPIO UTILIZANDO UNA COMPUTA-DORA PERSONAL."

# TESIS PROFESIONAL

QUE PARA OBTENER EL TITULO DE INGENIERO MECANICO ELECTRICISTA P R E S E N T A HECTOR MEJIA VAZQUEZ

Director de Tesis: Ing. Daniel Pineda Cortés

## UNAM – Dirección General de Bibliotecas Tesis Digitales Restricciones de uso

## DERECHOS RESERVADOS © PROHIBIDA SU REPRODUCCIÓN TOTAL O PARCIAL

Todo el material contenido en esta tesis está protegido por la Ley Federal del Derecho de Autor (LFDA) de los Estados Unidos Mexicanos (México).

El uso de imágenes, fragmentos de videos, y demás material que sea objeto de protección de los derechos de autor, será exclusivamente para fines educativos e informativos y deberá citar la fuente donde la obtuvo mencionando el autor o autores. Cualquier uso distinto como el lucro, reproducción, edición o modificación, será perseguido y sancionado por el respectivo titular de los Derechos de Autor.

#### TNDTCE

Capitulo 1. MEDICION AUTOMATIZADA Y LOS SISTEMAS DE ADQUISICION

| DE DATOS                                            | 기교 교육 기관은 이 전 기계 교육 가수 가                    |

|-----------------------------------------------------|---------------------------------------------|

|                                                     | Instrumentos de<br>: Instrumentos de<br>:al |

| 1.2 Caracteristicas Genera<br>Adquisición de Datos. | ales de los Sistemas de                     |

| 1.3 Teoria de Muestreo                              |                                             |

| 1.4 Técnicas de Conversión                          | n Analogica a Digital A/D27                 |

| 1.5 El Osciloscopio. Part                           | es funcionales30                            |

| 1.6 El Software como apoy                           | o. Paquetes de Programa41                   |

| Capitulo 2. ESPECIFICACIONES Y MUESTREO             | MODELO BASICO DEL OSCILOSCOPIO D            |

| Introducción                                        |                                             |

| 2.1 Objetivos y Necesidad                           | es43                                        |

| 2.2 Justificación del Dis                           | eño del Sistema43                           |

| 2.3 Especificaciones                                | .,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,     |

| 2.4 Limitaciones                                    | 46                                          |

| Capitulo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 3. DISEÑO DEL SISTEMA                                                     |      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|------|

| The state of the s | roducción                                                                 |      |

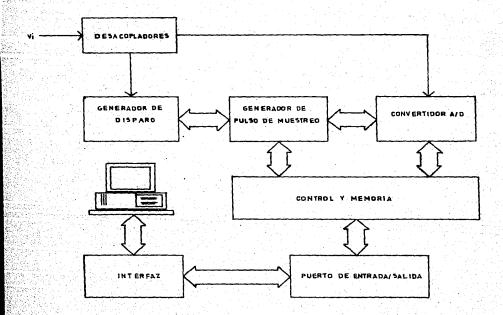

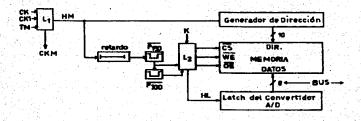

| 3.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Estructura General a Bloques                                              | . 48 |

| 3.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Breve Descripción del Sistema                                             | .50  |

| 3.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Diseño.                                                                   | . 53 |

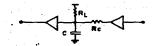

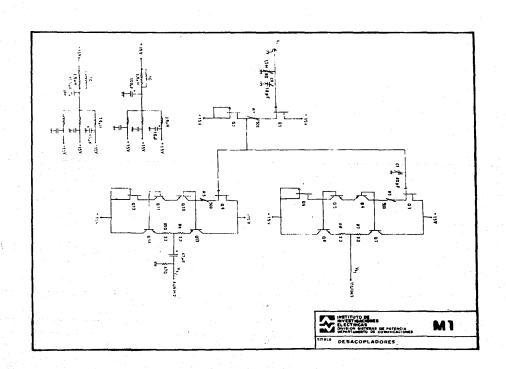

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3.3.1 Desacopladores                                                      | . 53 |

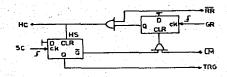

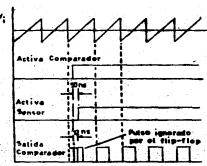

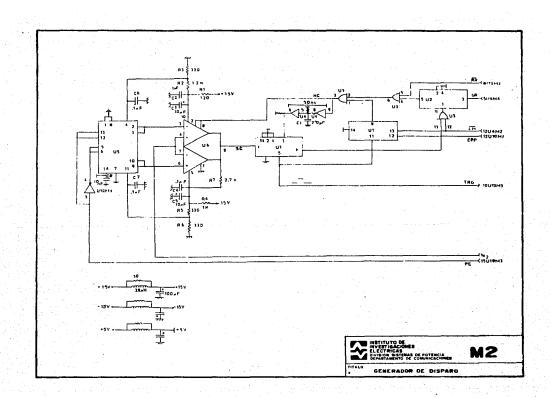

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3.3.2 Generador de Disparo                                                | .66  |

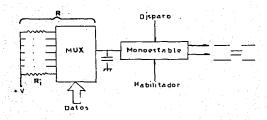

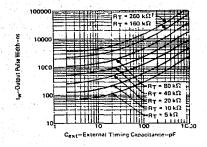

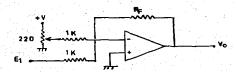

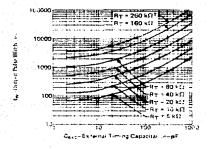

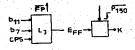

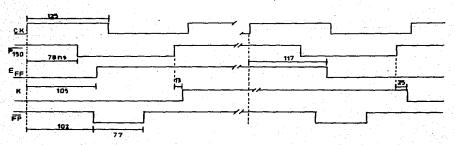

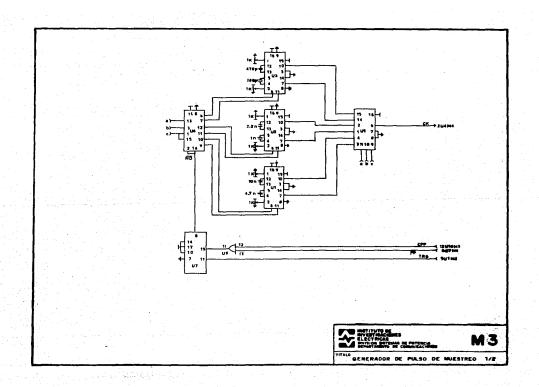

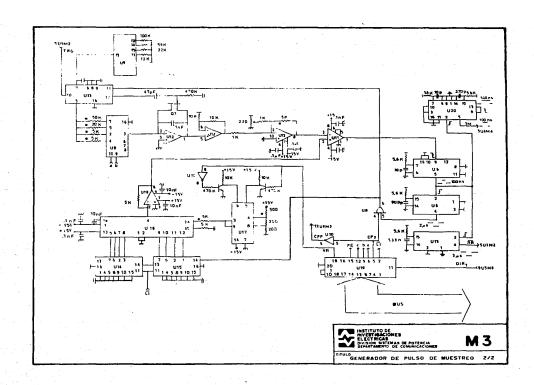

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3.3.3 Generador de Pulso de Muestreo                                      | . 73 |

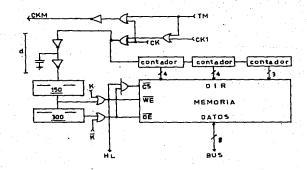

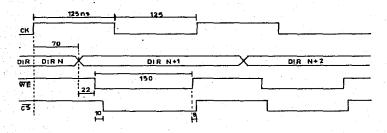

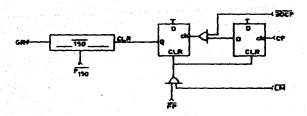

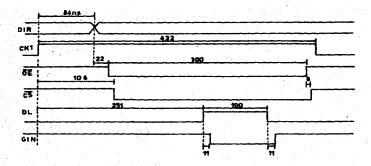

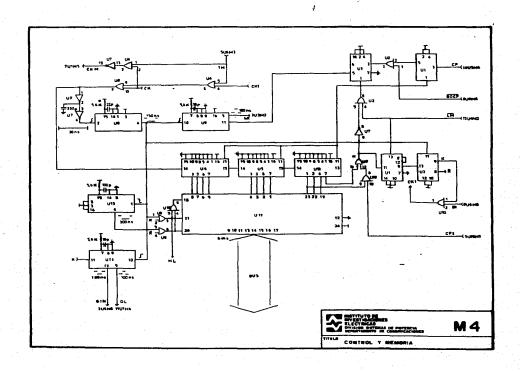

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3.3.4 Control y Memoria                                                   | . 95 |

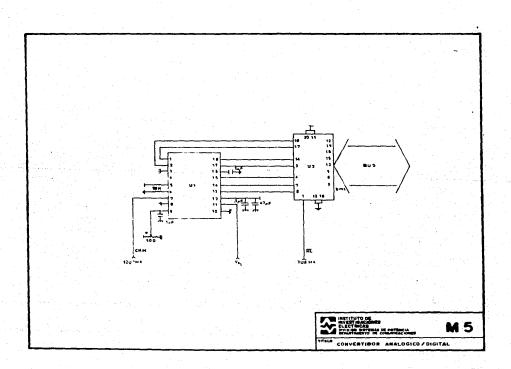

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3.3.5 Convertidor Analógico a Digital                                     | 113  |

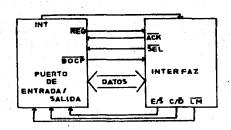

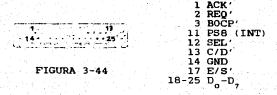

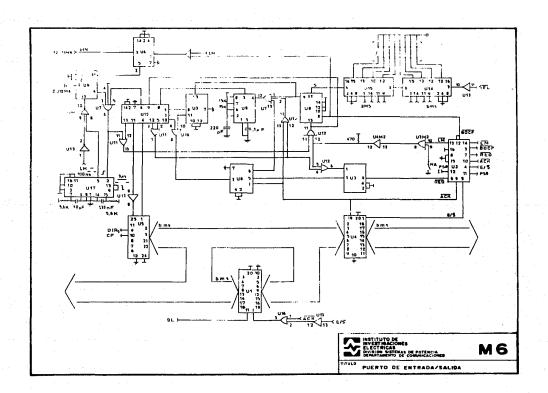

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3.3.6 Puerto de Entrada/salida                                            | 119  |

| Capituo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4. RESULTADOS SOBRE EL DESARROLLO DEL SISTEMA<br>DE ADQUISICION DE DATOS. |      |

| Int                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | roducción                                                                 | 137  |

| 4.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Especificaciones                                                          | 138  |

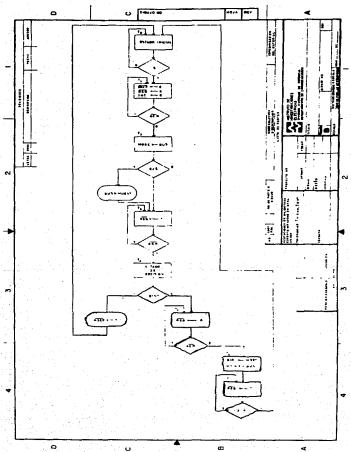

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Programación del Sistema                                                  |      |

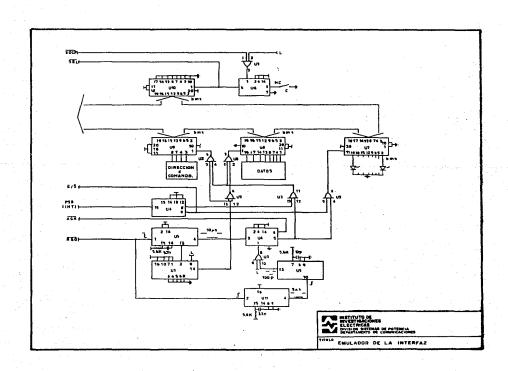

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Diagramas Eléctricos                                                      |      |

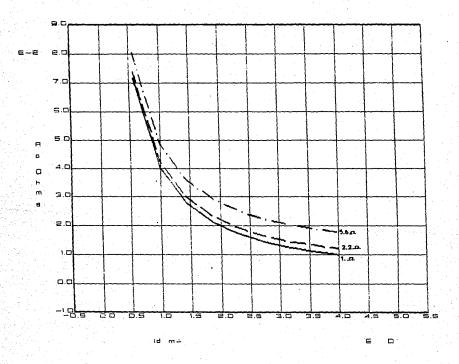

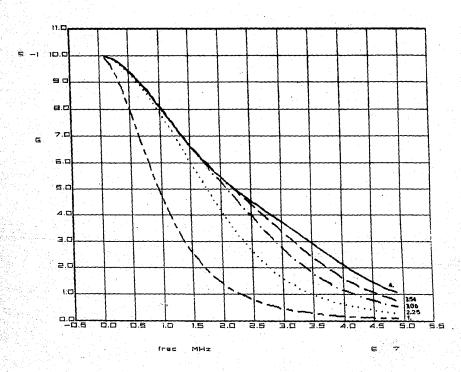

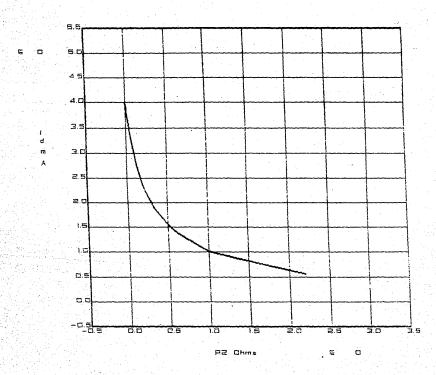

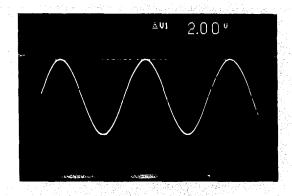

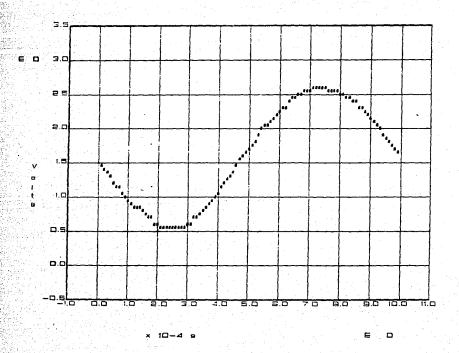

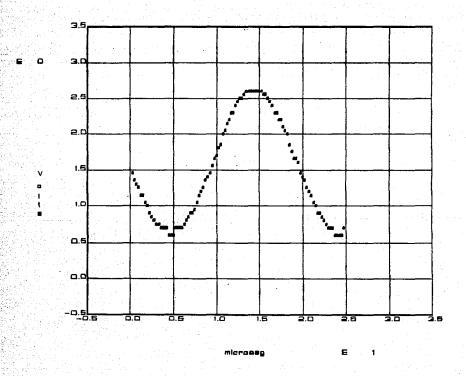

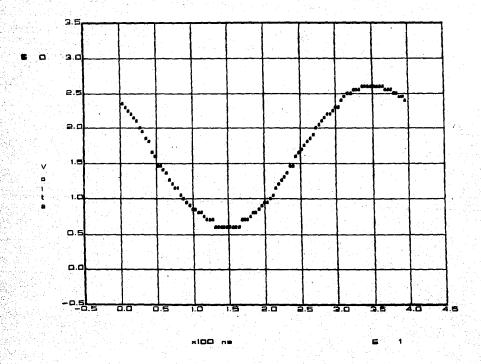

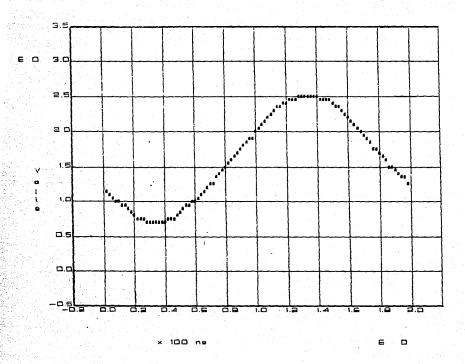

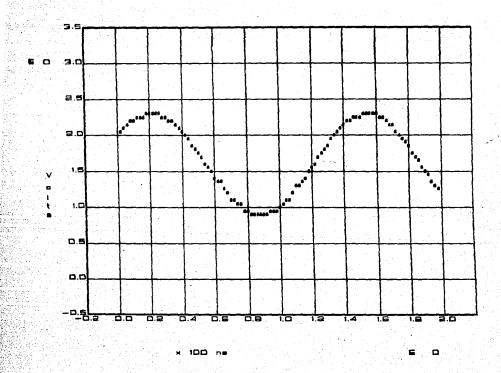

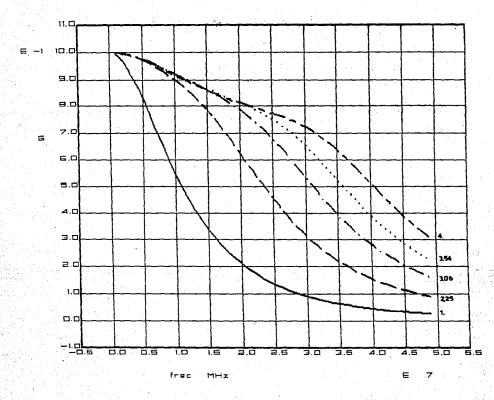

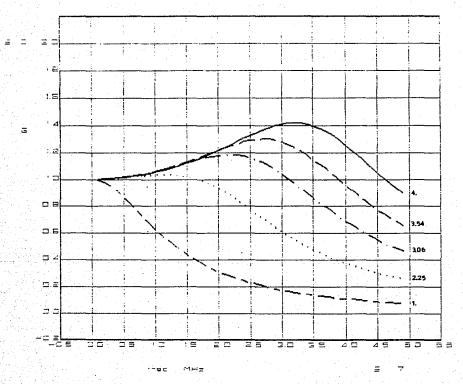

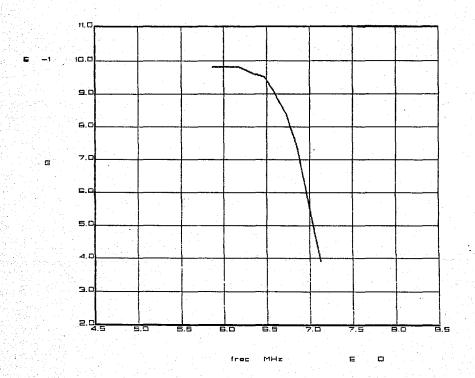

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Graficas                                                                  |      |

| 4.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Problemas Encontrados                                                     | 153  |

| CON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | CLUSIONES                                                                 | 156  |

| APE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | NDICE A                                                                   | 158  |

| APE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | NDICE B                                                                   | 160  |

| APE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | NDICE C                                                                   | 165  |

| BIB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | LIOGRAFIA                                                                 | 173  |

## CAPITULO I

## MEDICION AUTOMATIZADA Y LOS SISTEMAS DE ADQUISICION DE DATOS

1.1 MEDICION AUTOMATIZADA. INSTRUMENTOS DE INTERACCION REMOTA E INSTRUMENTOS DE INTERACCION REMOTA/LOCAL.

#### INTRODUCCION

El uso de microprocesadores en los equipos de instrumentación aplicada a la medición de parametros eléctricos, como elementos de control y análisis de la información, ha logrado incrementar su eficiencia y confiabilidad.

Equipos integrados por medidores y analizadores de señal pueden ser controlados y/o sus funciones implementadas mediante programas, lo que logra hacer que cada instrumento de medición sea mas versatil y fácil de manejar. De ello la importancia de crear sistemas automáticos de medición que faciliten la labor de diseño y prueba. Este es uno de los objetivos que persigue el presente trabajo, tratando de integrar un prototipo que reuna dos finalidades. La primera, observar los problemas inherentes al desarrollo de un instrumento de medición para laboratorio y la segunda, mostrar la metodología y ventajas de diseño (dentro de

este tipo de instrumentos), en base a la interacción software-hardware. Para ello, dividiremos el trabajo en 4 Capítulos. En el primero, se dará una introduccón teórica de los conceptos involucrados, en el segundo, se plantearán los objetivos y requerimientos del sistema, en el tercero se hablará del dimeño, y, finalmente, en el capítulo cuarto se tratará de hacer una evaluación planteando tanto los objetivos cumplidos como los problemas encontrados.

## LA MEDICION AUTOMATIZADA

Medición Automatizada es el procedimiento mediante el cual se compara una variable fisica con un patrón sin intervención humana.

Una de las mayores aplicaciones de la medición automatizada son los Equipos Automáticos de Pruebas (ATE) que consisten de diversos instrumentos conectados a diferentes puntos de medición de la \*Unidad bajo Prueba (UUT) por medio de una Matriz de Conmutación (CPS) controlada por un microprocesador. Mediante esto se logra obtener en diversos puntos de la UUT toda la información deseada sobre parámetros eléctricos tales como voltaje, frecuencia, forma de onda, etcétera, así como las conexiones necesarias de los excitadores para lograr las pruebas (fuentes de voltaje, generadores de señal, etc.).

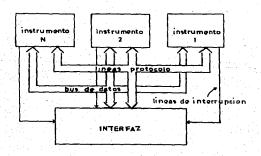

El manejo de la información proveniente de los instrumentos es canalizada a través de buses e interfaces adecuadas a este propósito. Una interfaz muy utilizada es la basada en la norma IEEE-488 que liga a los instrumetos con la Computadora.

Los instrumentos a los que hacemos mención son de dos tipos: Instrumentos de Interacción Remota (IIR) e Instrumentos de Interacción Remota/Local (IIRL).

Un IIR es diseñado para interactuar con la computadora en lugar de hacerlo con una persona.

Los IIRL están diseñados para ser manejados tanto por usuarios como por una computadora central.

La principal ayuda que aportan los instrumentos IR es el de minimizar la cantidad de circuitos utilizados. Cuando un instrumento es creado para ser compatible únicamente con una computadora en lugar de con una persona, gran número de circuitos físicos son implementados por medio de programas.

## PERSPECTIVAS DE LA MEDICION AUTOMATIZADA.

El futuro de la medición automatizada es bastante promisorio. Mediante una Computadora Personal (PC) el usuario puede adquirir un equipo de prueba y medición de tipo automático.

Existen dos formas en las que las PC entran dentro del contexto. La primera es la de ligar a la computadora con diversos instrumentos de medición independientes tales como voltimetros, osciloscopios, generadores de patrones, etc. mediante interfaces.

La segunda es hacer que la computadora sea el control central y el panel de los instrumentos, es decir la pantalla de la PC viene a ser el panel de control de cada instrumento. El costo del paquete-módulo es significativamente inferior al de los instrumentos a los cuales sustituyen ya que gran cantidad de hardware es eliminado o reducido, lo que se traduce en una buena aceptación de estos dispositivos.

Los paquetes de programación no solo realizan las funciones del instrumento sino que constituyen analizadores de la información según las necesidades del usuario con la facilidad de almacenarla y reproducirla en el momento deseado.

En ambos casos se obtiene una acción estimulo-respuesta entre el instrumento y la PC; sin embargo la segunda forma es más versátil y económica.

Compañías como Hewlett-Packard e IBM están creando computadoras personales con ranuras de expansión para conectar tarjetas de interfaz compatibles con la norma IEEE-488 de manera de controlar instrumentos producidos por otras empresas especializadas en medición como Fluke, Tektronix, Wandel &

Goltermann e incluso a los propios.

Existen varios tipos de interfaces para ligar los instrumentos con la PC. Dentro de ellos se encuentra la ya nombrada norma IEEE-488 para transmisión paralelo, con velocidad de transmisión máxima de l MHz, la RS-232-C para transmisión serie (muy baja velocidad) y la VMEbus para transmisión de datos a 50 MHz.

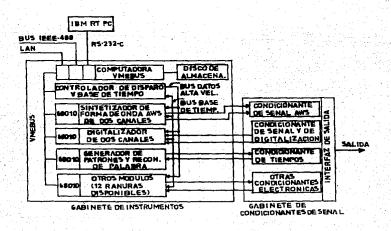

Un ejemplo de un equipo de Instrumentación Basado en Computadora (CBI), el cual utiliza la interfaz VMEbus es el de Tektronix mostrado en figura 1-1. En dicho sistema se conjuga versatilidad y manejo de equipo que puede ser disparado a gran velocidad.

FIGURA 1-1. EQUIPO BASADO EN COMPUTADORA.

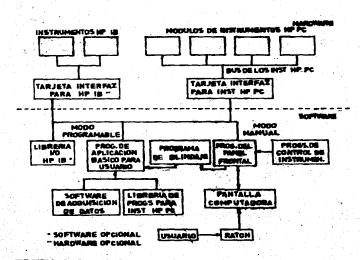

La Hewlett-Packard desarrolla una serie de instrumentos modulares conectados a través de una interfaz propia, de manera de reducir el costo asociado con el uso de la IEEE-488.

FIGURA 1-2. EQUIPO DE LA COMPANIA HEMLETT-PACKARD

CON DISENO DE INTERFAZ PROPIO.

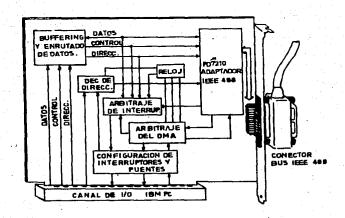

Existe una gran demanda de tarjetas que hagan compatible a la PC con la norma IEEE-488. Una tarjeta de este tipo es mostradm en la figura 1-3. El circuito integrado en el cual se basa es el µPD 72110 de NEC u otro análogo (68488 de Motorola, TMS 9914A de Texas Instr. ó el 8292 de Intel, etc.), que son microprocesadores especializados en cumplir con el protocolo de la norma.

FIGURA 1-3. TARJETA PARA LOGRAR COMPATIBILIDAD

ENTRE LA NORMA IEEE-488 Y LA COMPUTADORA PERSONAL.

En forma conjunta compañías dedicadas a la creación de software ponen a disposición del usuario paquetes especializados en el manejo, análisis y presentación de los datos. A los lenguajes que en un principio se utilizaban como BASIC y Ensamblador o paquetes de aplicación (LOTUS 1-2-3), se añaden ahora FORTRAN, C, y Turbo Pascal de manera de abarcar un mayor mercado.

1.2 CARACTERISTICAS GENERALES DE LOS SISTEMAS DE ADQUISICION DE DATOS

Los sistemas de instrumentación se dividen en dos clases: Sistemas Analógicos y Sistemas Digitales. Los Sistemas Analógicos tratan con información medida en forma analógica como la de un graficador. Los Sistemas Digitales manejan información en forma digital la cual describe la naturaleza de la cantidad medida.

Los Sistemas de Adquisición de Datos son usados para medir y grabar señales obtenidas basicamente de dos formas:

- a) Señales originadas de mediciones directas de cantidades eléctricas.

- b) Señales originadas de transductores, tales como piezoeléctricos o termopares.

## SISTEMA DE ADQUISICION DE DATOS ANALOGICOS.

Un sistema de adquisición de datos analógico consisten de todos o algunos de los siguientes elementos:

(a) Transductores para convertir los parametros en señales eléctricas.

- (b) Acondicionadores de señal para amplificar, modificar o seleccionar ciertas porciones de esta.

- (c) Dispositivos de desplegado visual para continua observación de la señal de entrada (Tubos de rayos catódicos, medidores tipo panel, desplegados numéricos, etc.).

- (d) Instrumentos para grabación en cinta magnética y graficación.

## SISTEMA DE ADQUISICION DE DATOS DIGITAL.

Un sistema de adquisición de datos digital incluye todos o algunos de los bloques mostrados en la figura 1-4:

FIGURA 1-4. DIAGRAMA GENERAL DE UN SISTEMA

DE ADQUISICION DE DATOS.

Las funciones de cada uno de los elementos es listado a continuación:

- (a) Transductor. Convierte parametros físicos en señales eléctricas reconocibles por el sistema.

- (b) Acondicionador de señal. Generalmente incluye la circuitería que apoya al transductor (fuente um excitación, circuitos de compensación y elementos de calibración).

- (c) Multiplexor. Acepta entradas analógicas y las conecta secuencialmente a un instrumento de medición.

- (d) Normalizador de señal. Traslada la señal analógica

- \* a un estandar aceptable por el convertidor A/D.

- (e) Convertidor A/D. Convierte la señal analògica en forma digital para su posterior despliegue y almacenamiento.

- (f) Equipo Auxiliar. Esta sección incluye funciones de programación del sistema y procesamiento digital de datos.

- (g) Equipo de Grabación. Traslada la información digital a una forma que sea aceptada por el tipo particular de grabación (papel, cinta,tarjetas).

Los sistemas de adquisición de datos son usados en muchas areas cientificas e industriales. En forma general, los sistemas de adquisición de datos analógicos son usados cuando se requiere un gran ancho de banda o cuando se puede tolerar una baja exactitud. Los sistemas de adquisición de datos digitales son usados en procesos físicos de lenta variación (ancho de banda angosto), y cuando gran exactitud a bajo costo es requerido.

Los sistemas de adquisición de datos de tipo digital son más complejos que los de tipo analógicos en términos de la instrumentación involucrada en el manejo de datos.

## 1.3 TEORIA DE MUESTREO

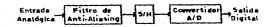

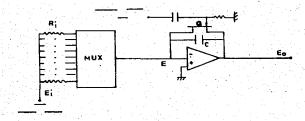

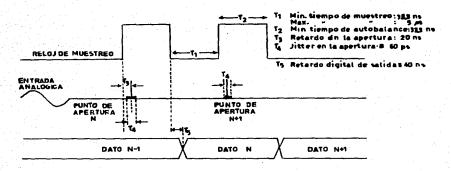

Un Muestreador de Datos de tipo Digital contiene a los elementos mostrados en la figura.

FIGURA 1-5. MUESTREADOR DE DATOS DE TIPO DIGITAL.

El filtro de anti-aliasing. Es usado para limitar la banda de la señal de entrada antes de que sea muestreada. Esto minimiza la posible distorsión (ruido de aliasing) debido a componentes de alta frecuencia que son mayores que la frecuencia de muestreo.

Sample/Hold. La entrada filtrada es entonces muestreada a una razón de muestreo. Cada amplitud muestreada es sostenida momentaneamente para su procesamiento subsecuente.

Convertidor A/D. El voltaje analógico sostenido es convertido a una palabra digital. Dicha palabra representa el voltaje de la señal de entrada.

## EFECTOS DEL MUESTREO.

Asumiendo un espectro de entrada F(jw) y una frecuencia de muestreo  $f_s$ , el espectro de salida oara un muestreo de tope plano  $F_{st}(jw)$  es:

$$F_{ST}(j\omega) = \frac{\tau}{T} \frac{sen(\omega t/2)}{\omega t/2} \sum_{n=-\infty}^{\infty} F \left| j(\omega - n\omega_s) \right|$$

Para esta ecuación la ganancia es una función continua de la frecuencia y se define por:

$$\frac{\tau}{T} \frac{\text{sen}(\omega t/2)}{\omega t/2}$$

donde  $\tau$  es el ancho del pulso de muestreo, T es el período de muestreo y  $\omega$  es la frecuencia en radianes sobre segundo.

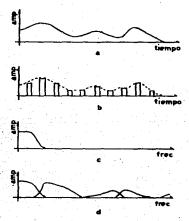

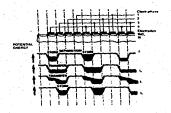

Las gráficas en el dominio del tiempo y de la frecuencia son mostradas en la figura 1-6. La figura 1-6 a y b muestra la señal antes y después de ser muestreada. Los correspondientes espectros son mostrados en la figura 1-6 c y d respectivamente.

La figura 1-6 d es una gráfica de la ecuación antes citada donde múltiplos del espectro original están formados en los múltiplos de la frecuencia de muestreo. Entre más separación exista entre los espectros (es decir, un menor traslape), la señal continua podrá representarse por muestras discretas a la frecuencia de muestreo.

FIGURA 1-6. GRAFICAS EN EL DOMINIO DEL TIEMPO Y LA FRECUENCIA

DE UNA SENAL ANTES Y DESPUES DE SER MUESTREADA.

La calidad de la representación de una señal continua por medio de señales muetreadas y digitalizadas está determinada por varios factores:

(a) Razón de muestreo.

- (b) Ancho del pulso de muestreo.

- (c) Exactitud en la digitalización.

Los correspondientes terminos de distorsion son:

- (a) Ruido de Aliasing.

- (b) Ruido de Jitter.

- (c) Ruido de Cuantización.

Los anteriores factores pueden causar distorsión inaceptable si no son reducidos y controlados.

## RUIDO DE ALIASING.

Teorema de muestreo.

"Si una señal f(t), una función real del tiempo, es muestreada a intervalos regulares con una razón mayor o igual a dos veces el ancho de banda de la señal, entonces la señal muestreada contiene toda la información significativa de la señal original."

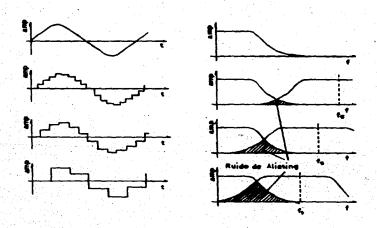

La figura 1-7 muestra los efectos de la razón de muestreo sobre la separación de los espectros que representan a la señal. cuando la razón de muestreo es reducida, los espectros adyacentes se traslapan. La energía espectral traslapada no puede ser separada de la señal deseada generándose una distorsión de la información original, a esto es llamado ruido de Aliasing.

El traslape puede ser reducido ya sea aumentando la frecuencia de muestreo ó aumentando la caida (rolloff) en la frecuencia de corte de la señal de entrada usando un filtro de anti-aliasing antes de muestrear.

FIGURA 1-7. EFECTOS DEL TRASLAPE ENTRE ESPECTROS.

RUIDO DE ALIASING.

La figura 1-8 ilustra el efecto del filtrado sobre el ruido de Aliasing.

Figura 1-8. EFECTO DEL FILTRAJE ANTES DEL MUESTREO.

## RUIDO DE JITTER

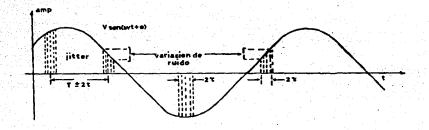

Un muestreo ideal asume que las muestras son tomadas a intervalos periódicos, y que el valor de la amplitud de cada muestra es igual al valor de la señal en el instante de muestreo. Si la forma de onda de muestreo no es estable, entonces la señal será muestreada a otro tiempo al cual fue especificado con un error correspondiente a la razón de cambio de la señal de muestreo.

FIGURA 1-9. INCERTIDUMBRE EN EL MOMENTO DE MUESTREO. JITTER.

El ruido de Jitter puede ser estimado examinando una señal de entrada sinusoidal que es muestrada con un periodo promedio T' y una desviación pico a pico del periodo de  $2\tau$ , (figura 1-9). Usando sen( $\mathrm{ut}_{j}$ ) como el valor de la senoide exactamente al instante del muestreo y sen $\mathrm{Eu}(\mathrm{t}_{j}+\tau_{j})$  como el valor del i-esimo instante actual de muestreo, donde  $\tau_{j}$  es el error de tiempo en el punto, entonces el error o ruido de Jitter en  $\mathrm{t}_{j}$  es la diferencia entre el valor exacto y el valor muestreado de la señal de voltaje, esto es:

$$\begin{aligned} \mathbf{N}_{\mathbf{J}}(\mathbf{T}_{\mathbf{j}}) &= \operatorname{sen}(\omega \mathbf{t}_{\mathbf{j}}) - \operatorname{sen}(\omega \mathbf{t}_{\mathbf{j}} + \omega \mathbf{T}_{\mathbf{j}}) \\ &= (1 - \cos(\omega \mathbf{T}_{\mathbf{j}}))(\operatorname{sen}(\omega \mathbf{t}_{\mathbf{j}}) + \\ &= \operatorname{sen}(\omega \mathbf{T}_{\mathbf{j}})\cos(\omega \mathbf{t}_{\mathbf{j}}) \end{aligned}$$

La potencia del ruído es la suma de los cuadrados de sus componentes en cuadratura

$$N_{J}^{2} = \mathbb{C}1 - \cos(\omega \tau_{j}) J^{2} + \sin^{2}(\omega \tau_{j})$$

$$= 2 - 2\cos(\omega \tau_{j})$$

Asumiendo que los errores son independientes de una muestra a otra y que se encuentran uniformemente espaciados entre ±1, la potencia del ruido esperado es:

$$\begin{split} \mathbf{E} \left\{ \mathbf{N}_{\mathbf{J}}^{2} \right\} &= \int_{-\tau}^{\tau} -2 \cos(\omega \tau_{\mathbf{j}}) \, \mathbf{J} \frac{1}{2\tau} d\tau_{\mathbf{j}} \\ &= 2 -2 \frac{\sin \omega \tau}{\omega \tau} \end{split}$$

Para ωτ(π/2 una expansión en serie de Taylor de sen(ωt) produce una aproximación para el valor cuadrático medio o potencia del ruido de

$$E\left\{N_{J}^{2}\right\} = \frac{\left(\omega\tau\right)^{2}}{3}$$

Lawrelación S/R de una señal senoidal muestreada sen $(\omega \tau)$  debido al Jitter uniformemente distribuido sobre un rango de  $-\tau <=\tau_0 <=+\tau$  segundos es

$$\left(\frac{S}{R}\right)_{J} = \frac{\text{Valor Cuadratico Medio de la Se}^{2}al}{\text{Valor Cuadratico Medio del Ruido}} = \frac{1}{2} = \frac{3}{(\omega\tau)^{2}}$$

$$\left(\frac{S}{R}\right)_{J} = 0.038 \left(\frac{T}{\tau}\right)^{2}$$

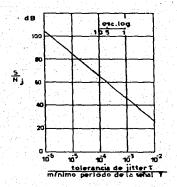

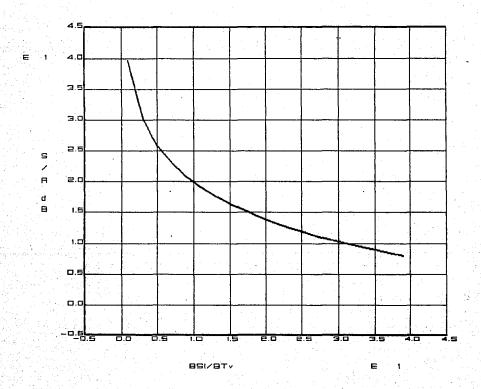

donde T es el período de la señal muestreada. La relación S/R de Jitter es graficada en la figura 1-10 como una función de la razon de tolerancia del Jitter  $\tau/T$ .

FIGURA 1-10

## RUIDO DE CUANTIZACION

Cuantización.

La cuantización puede ser de dos tipos: Uniforme y No Uniforme. En la distribución uniforme los niveles de cuantización están espaciados uniformemente. La cuantización no uniforme se utiliza para mejorar el desempeño de la señal frente al ruido. El espaciamiento entre niveles se reduce en donde aparecen pequeñas amplitudes de la señal.

Ruido de cuantización.

La discrepancia entre una forma de onda y su aproximación cuantizada se conoce como ruido de cuantización.

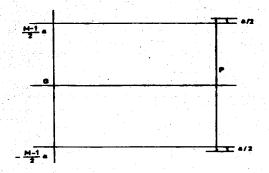

Considere una señal f(t) cuyo valor medio es cero. Sea P volts la excursión máxima de la señal. Si se utiliza un total de M niveles de cuantización espaciados uniformemente a "a" volts entonces

Una distribución razonable de los niveles de cuantización es la que se muestra en la siguiente figura:

FIGURA 1-11. DISTRIBUCION UNIFORME DE LOS NIVELES DE CUANTIZACION.

Los niveles de cuantización tomarán valores dados por

$$A_j = \pm \left(\frac{2j+1}{2}\right)a$$

Volts

donde

$$j = 0, 1, 2, \ldots, \left(\frac{M-2}{2}\right)$$

Las muestras cuantizadas cubren un intervalo dado por: A=(M-1)a Volts.

En el proceso de cuantización cualquier voltaje de la señal continua entre el intervalo  $A_j$ -a/2 a  $A_j$ +a/2 se ajusta al nivel de cuantización  $A_j$  es decir que existirá un error, de cuantización, que está limitado a la excursión de a/2 volts.

FIGURA 1-12. ERRORES INTRODUCIDOS POR EL PROCESO DE CUANTIZACION.

Suponiendo que en un largo intervalo de tiempo todos los valores de voltaje en cualquier región de incertidumbre aparecen el mismo número de veces, los valores de  $\varepsilon$  estarán distribuidos uniformemente de -a/2 a +a/2, asi:

$$P(\varepsilon) = \begin{cases} \frac{1}{a} & |\varepsilon| < \frac{a}{2} \\ 0 & |\varepsilon| > \frac{a}{2} \end{cases}$$

La potencia media del ruido de cuantización e disipada en una carga resistiva de un ohm quedaria dada por

$$E(\varepsilon^{2}) = \frac{1}{a} \begin{cases} \frac{a}{2} \\ \varepsilon^{2} d\varepsilon = \frac{a^{2}}{12} \end{cases}$$

La potencia media de la señal, después de la cuantización, puede calcularse considerando que la señal varía de tal manera que hace a todos los niveles de cuantización agrupables

$$E\{A_{j}\} = 2 \sum_{j=0}^{\frac{M-2}{2}} \left[ \left( \frac{2j+1}{2} \right) a \right]^{2} \frac{1}{M} = (M-1) \frac{a^{2}}{12}$$

Por lo que la relación S/R resultante es

$$\left(\frac{S}{R}\right)_{Cuant} = M^2$$

para M>>1.

expresado en dB

Como M=nm

$$\left(\frac{S}{R}\right)_{Cuant} = 20\log M$$

$$\left(\frac{S}{R}\right)_{Cuant} = 6m$$

o sea 48 db para un código binario de 8 bits y 36 db para uno de 6 bits.

## 1.4 TECNICAS DE CONVERSION ANALOGICA A DIGITAL A/D

La parte medular de un Sistema de Adquisición de Datos Digital es su convertidor de señal analógica a digital. Para este tipo de conversión existen varias técnicas y la elección de alguna de ellas depende del compromiso entre resolución, velocidad de conversión y precio.

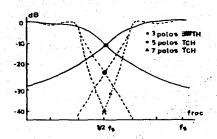

Los convertidores con velocidades de conversión menores de l MHz emplean dos técnicas fundamentales: Aproximaciones sucesivas para una buena resolución a velocidad moderada y el de Integración para alta resolución a bajas velocidades.

El convertidor de Aproximaciones Sucesivas compara la entrada desconocida con la suma de fracciones binarias de la escala total comenzando con la más significativa (2<sup>-1</sup>) y rechazando a cualquiera de las fracciones que altere el estado del comparador. Al final de la conversión, la salida del convertidor es una palabra digital representando la razón de la entrada a la escala total mediante un código binario fraccional.

El de tipo Integrador cuenta pulsos de un periodo que es proporcional al nivel de la señal de entrada. Dentro de los de esta clase se encuentra el de Doble Pendiente, el cual cuenta pulsos durante el periodo que requiere para que la integral de la referencia sea igual al valor promedio del nivel de la señal de entrada (en un periodo preestablecido).

Dentro de los convertidores de mayor velocidad se encuentran los siguientes:

Conversion analogica en serie/digital en paralelo. En este tipo de conversión existe un número de etapas en cascada, cada una teniendo una ganancia de +2 para señales menores medio de la referencia y una ganancia de -2 para señales entre un medio de la referencia y la escala total. En cada etapa selecciona "l" o "0" dependiendo si la señal es mayor o menor que la referencia. La salida analógica de la etapa es 1a para la siguiente. El tiempo de conversión es determinado por el retardo de propagación de la señal analógica a través de las etapas. Dado que la decisión de cada etapa ("1" o "0") puede ser almacenada (y una conversión puede, en principio, comenzada tan pronto como el primer bit ha sido almacenado), la razón a la cual las conversiones salen de la considerablemente más rápida que el tiempo para que una muestra pase a través de todo el proceso de conversión. Aunque rapido, el proceso es dificil de implementar con exactitud para más de 5 bits debido al mezclado de ganancia resultante lo que trae como consecuencia errores.

Convertidor tipo Flash o Paralelo. En la conversión Flash, la señal analógica es comparada contra  $2^N-1$  niveles de voltaje usando un número igual de comparadores (N es el número de bits en la palabra digital a la salida del proceso). Los niveles lógicos a la salida de los comparadores son procesados por un codificador

de prioridad el cual proporciona la salida en código binario o Gray. Dado que la conversión ocurre en forma simultanea, este es el tipo de convertidor más rápido; sin embargo, requiere de un gran número de comparadores, resistencias de precisión y compuertas.

Convertidor que utiliza PPCCD. El PPCCD EProfiled Peristaltic Charge Coupled Devicel es una combinación, en estado sólido, de un dispositivo track-and-hold rápido como circuito de entrada y un registro de corrimiento analógico. Basicamente permite almacenar datos hasta una frecuencia de 125 Megamuestras/seg y después digitalizarlas a una frecuencia mucho más baja (78 KHz) por un convertidor Analógico/Digital.

Para lograr lo anterior, obtiene réplicas de la señal en forma analógica cargando hasta 256 microcapacitores semiconductores en el dispositivo, denominados "pozos". Los dispositivos CCD realizan tres funciones básicas: almacenamiento, transferencia y separación.

La señal es muestreada a la frecuencia del reloj (125 MHz) y cada muestra es convertida en un paquete de carga. El primer paquete se introduce al primer pozo y aplicando pulsos de reloj apropiados a los cuatro grupos de electrodos es posible mantener separación y transferencia de carga entre pozos. La siguiente muestra se introduce al dispositivo y el proceso se repite hasta que todo el dispositivo se llena. Así, se obtiene una replica de la señal, la cual puede ser mantenida el suficiente tiempo para

lograr una conversión Analógica a Digital de baja frecuencia.

FIGURA 1-13. SISTEMA PPCCD.

Cualquiera que sea la técnica, los convertidores A/D comprenden: una sección analógica, una sección de generación de datos digitales, salida de datos y controles digitales.

## 1.5 EL OSCILOSCOPIO

## INTRODUCCION

El Osciloscopio de Rayos Catódicos, CRO, es un instrumento de laboratorio extremadamente útil y poderoso utilizado para mediciones y análisis de formas de onda y otros fenómenos en circuitos eléctricos y electrónicos. Los Osciloscopios son basicamente graficadores muy rápidos que despliegan una señal contra otra o contra el tiempo.

Cualquier fenómeno físico que pueda, mediante un transductor, convertirse a una señal de voltaje podrá ser observado en el CRO, ya sea corriente, presión, tensión, temperatura, aceleración, etcétera.

El CRO puede ser utilizado para analizar respuestas temporales de señales desde rangos de muy baja frecuencia hasta altas frecuencias con ayuda de camaras especiales o de muestreadores digitales.

Los principios sobre los cuales opera el CRO serán discutidos en forma general en las siguientes secciones.

## OPERACION BASICA DEL CRO

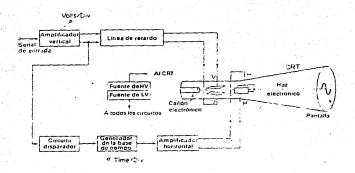

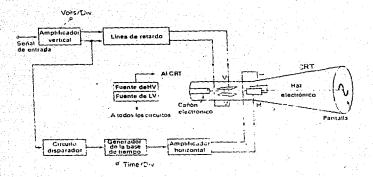

El CRO de propósito general se muestra en el diagrama simplificado de la figura 1-14. En él podemos observar:

- (a) Tubo de rayos catódicos o CRT

- (b) Amplificador vertical

- (c) Linea de retardo

- (d) Generador de base de Tiempo

- (e) Amplificador Horizontal

- (f) Circuito de Disparo o Trigger

- (g) Fuente de Poder

FIGURA 1-14. DIAGRAMA SIMPLIFICADO DE LAS PARTES

QUE COMPONEN A UN OSCILOSCOPIO DE RAYOS CATODICOS.

TOMADO DE LA REFERENCIA [1].

El tubo de rayos catódicos o CRT, es el corazón del osciloscopio, la circuiteria restante del CRO solo sirve para operarlo. Basicamente, el CRT produce un fino haz de electrones afocados y acelerados a muy alta velocidad. Este haz viaja desde su fuente, ("electron gun"), hasta el frente del CRT donde hace contacto con el material fluorescente depositado en la cara interior del CRT con suficiente energia para causar un punto luminoso sobre la pantalla. Mientras viaja de la fuente a la pantalla, el haz de electrones pasa a través de una serie de placas de deflexión horizontal y vertical.

FIGURA 1-14. DIAGRAMA SIMPLIFICADO DE LAS PARTES

QUE COMPONEN A UN OSCILOSCOPIO DE RAYOS CATODICOS.

TOMADO DE LA REFERENCIA [1].

El tubo de rayos catódicos o CRT, es el corazón del osciloscopio, la circuiteria restante del CRO solo sirve para operarlo. Basicamente, el CRT produce un fino haz de electrones afocados y acelerados a muy alta velocidad. Este haz viaja desde su fuente, ("electron gun"), hasta el frente del CRT donde hace contacto con el material fluorescente depositado en la cara interior del CRT con suficiente energia para causar un punto luminoso sobre la pantalla. Mientras viaja de la fuente a la pantalla, el haz de electrones pasa a través de una serie de placas de deflexión horizontal y vertical.

Voltajes aplicados a las placas de deflexión vertical pueden mover al haz de electrones en el plano vertical de arriba hacia abajo sobre la pantalla. Voltajes aplicados sobre las placas de deflexión horizontal mueven el haz en el plano horizontal y el punto luminoso se mueve de un lado al otro de la pantalla.

La forma de onda a observarse en la pantalla del CRT es aplicada al amplificador vertical de entrada. La ganancia de este amplificador es fijada por un atenuador de entrada calibrado, usualmente marcado con VOLTS/DIV. La salida "push-pull" del amplificador alimenta a las placas de deflexión vertical via una linea de retardo.

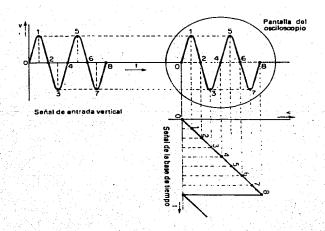

El generador de base de tiempo, o generador de barrido, desarrolla una onda "diente de sierra" que es usada como voltaje de deflexión horizontal. El tiempo de subida es fijado por un control en el panel frontal marcado con TIME/DIV. El voltaje "diente de sierra" alimenta al amplificador horizontal. Este amplificador incluye un inversor de fase y produce dos formas de onda de salida en forma simultánea: un "diente de sierra" de pendiente positiva y otro "diente de sierra" de pendiente negativa. La de pendiente positiva es aplicada al plato de deflexión horizontal derecho y la de pendiente negativa a la del plato horizontal izquierdo. Lo anterior causa que el haz de electrones vaya de izquierda a derecha a través de la pantalla en unidades de tiempo establecidas por el control TIME/DIV.