### UNIVERSIDAD DE IXTLAHUCA CUI, A. C.

# LICENCIATURA EN INGENIERÍA EN TELECOMUNICACIONES, SISTEMAS Y ELECTRÓNICA

INCORPORADA A LA

UNIVERSIDAD NACIONAL AUTÓNOMA DE

MÉXICO

Clave 8968-66

# DISEÑO Y CONSTRUCCIÓN DE UN INVERSOR MULTINIVEL PARA EL ANÁLISIS DE DISTORSIÓN ARMÓNICA

### **TESIS**

QUE PARA OBTENER EL TÍTULO DE

INGENIERO EN TELECOMUNICACIONES, SISTEMAS Y ELECTRÓNICA

**PRESENTA**

SALVADOR SARMIENTO SÁNCHEZ

ASESOR: M. EN C. JORGE EDMUNDO MASTACHE MASTACHE

IXTLAHUACA, ESTADO DE MÉXICO. MARZO 2022

UNAM – Dirección General de Bibliotecas Tesis Digitales Restricciones de uso

#### DERECHOS RESERVADOS © PROHIBIDA SU REPRODUCCIÓN TOTAL O PARCIAL

Todo el material contenido en esta tesis esta protegido por la Ley Federal del Derecho de Autor (LFDA) de los Estados Unidos Mexicanos (México).

El uso de imágenes, fragmentos de videos, y demás material que sea objeto de protección de los derechos de autor, será exclusivamente para fines educativos e informativos y deberá citar la fuente donde la obtuvo mencionando el autor o autores. Cualquier uso distinto como el lucro, reproducción, edición o modificación, será perseguido y sancionado por el respectivo titular de los Derechos de Autor.

#### REVISORES

M. EN C. JORGE EDMUNDO MASTACHE MASTACHE KSESOR M. EN A.T.I. KARINA BALDERAS PÉREZ REVISOR

ING. E. JOSÉ JESÚS RAMÍREZ MORQUECHO REVISOR M. EN E.A.E. BERNARDO JUÁREZ GONZÁLEZ REVISOR

M. EN TE ROGELIO LOVERA OLIVERA REVISOR

### **CONTENIDO**

| Índice de tablas                                                                    | <u>i</u> |

|-------------------------------------------------------------------------------------|----------|

| Índice de ecuaciones                                                                | ii       |

| AGRADECIMIENTOS                                                                     | iii      |

| RESUMEN                                                                             | 1        |

| CAPÍTULO 1                                                                          | 2        |

| PLANTEAMIENTO DEL PROBLEMA Y PROPUESTA DE SOLUCIÓN                                  | 2        |

| 1.1 Introducción                                                                    | 3        |

| 1.2 Problemática                                                                    | 4        |

| 1.3 Propuesta                                                                       | 5        |

| 1.4 Justificación                                                                   | 6        |

| 1.5 Antecedentes                                                                    | 7        |

| 1.6 Hipótesis                                                                       | 8        |

| 1.7 Objetivo General                                                                | 8        |

| 1.7.1 Objetivos específicos                                                         | 9        |

| 1.8 Metodología                                                                     | 9        |

| CAPÍTULO 2                                                                          | 11       |

| MARCO TEÓRICO                                                                       | 11       |

| 2.1 Electrónica de potencia                                                         | 12       |

| 2.2 Transformación energía                                                          | 12       |

| 2.3 Tipos de inversores                                                             | 13       |

| 2.3.1 Topologías de los inversores binivel                                          | 14       |

| 2.3.1.1 Inversores de medio puente                                                  | 15       |

| 2.3.1.2 Inversor de puente completo                                                 | 15       |

| 2.4 Filtros                                                                         | 16       |

| 2.5 Inversores multinivel                                                           | 17       |

| 2.5.1 Topologías de los inversores multinivel                                       | 19       |

| 2.5.1.1 Inversor multinivel con diodos enclavados (DCMLI)                           | 19       |

| 2.5.1.1.1 Características principales del inversor multinivel con diodos enclavados | 22       |

| 2.5.1.1.2 Desventajas del inversor multinivel con diodos enclavados                 | 22       |

| 2.6 Inversor con capacitores flotantes                                              | 22       |

| 2 6 1 Características de los inversores con canacitores flotantes                   | 22       |

| 2.6.1.1 Control para un inversor multinivel de capacitores flotantes | 22 |

|----------------------------------------------------------------------|----|

| 2.6.1.2 Desventajas en inversor multinivel de capacitores flotantes  | 24 |

| 2.7 Inversor multinivel conectado en cascada                         | 24 |

| 2.8 Definición de armónicos                                          | 26 |

| 2.8.1 Indicadores esenciales de la distorsión armónica               | 26 |

| 2.8.2 Factor de potencia                                             | 26 |

| 2.8.3 Factor de cresta                                               | 27 |

| 2.8.4 Potencia activa                                                | 27 |

| 2.8.6 Potencia reactiva                                              | 27 |

| 2.8.6 Tasas de distorsión armónica                                   | 28 |

| 2.8.7 Distorsión armónica total (THD)                                | 28 |

| 2.9 Esquemas de modulación                                           | 29 |

| 2.9.1 Modulación por ancho de pulso único                            | 29 |

| 2.9.2 Modulación por ancho de pulso multiple                         | 30 |

| 2.9.3 Modulación por ancho de pulso senoidal                         | 30 |

| 2.9.4 Modulación para inversores multinivel                          | 31 |

| 2.9.4.1 Modulación por corrimiento de fase                           | 31 |

| 2.9.4.2 Modulación por oposición y disposición de fase               | 32 |

| 2.9.4.3 Modulación por disposición de fase                           | 32 |

| 2.9.5 Desempeño de los inversores                                    | 33 |

| 2.9.6 Pérdidas                                                       | 33 |

| CAPÍTULO 3.                                                          | 35 |

| DISEÑO Y SIMULACIONES                                                | 35 |

| 3.1 Diseño de inversores multinivel en simulación                    | 36 |

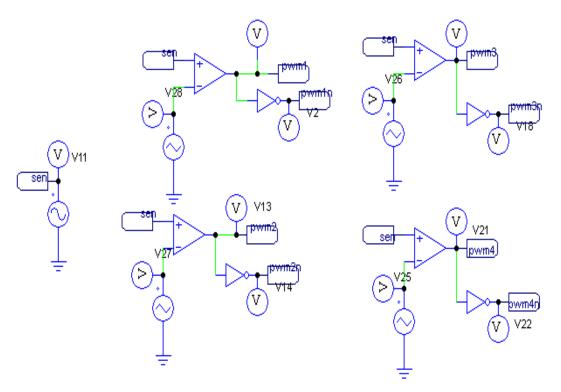

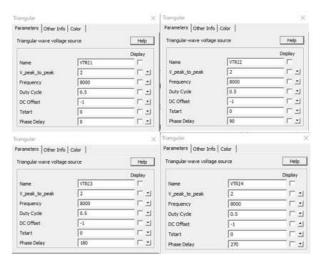

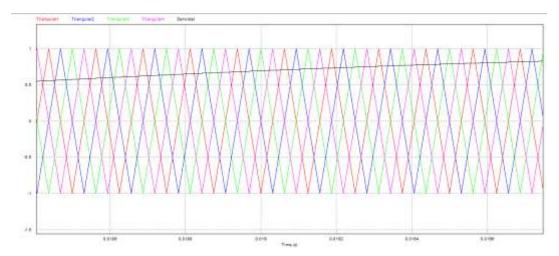

| 3.2 Modulación de corrimiento de fase                                | 37 |

| 3.3 Modulación por oposición y disposición de fase                   | 39 |

| 3.4 Modulación por disposición de fase                               | 42 |

| 3.5 Seleccionar la técnica de disposición de fase THD                | 46 |

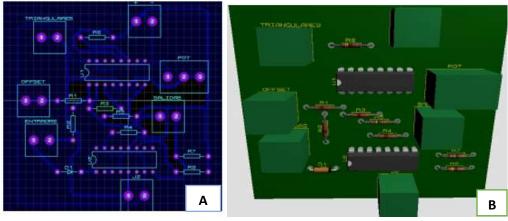

| 3.6 Diseñar circuitos impresos del banco de pruebas                  | 46 |

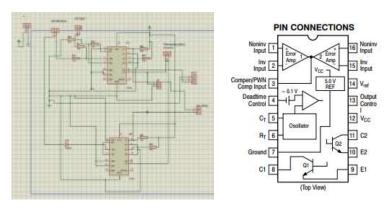

| 3.7 Etapa de control                                                 | 47 |

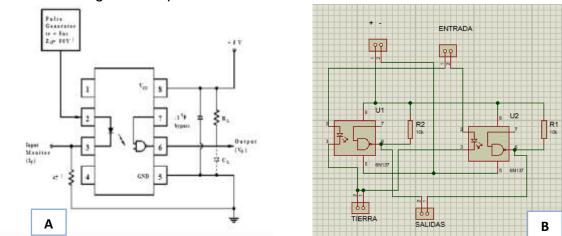

| 3.8 Etapa de aislamiento                                             | 48 |

| 3.9 Acondicionamiento de señales                                     | 49 |

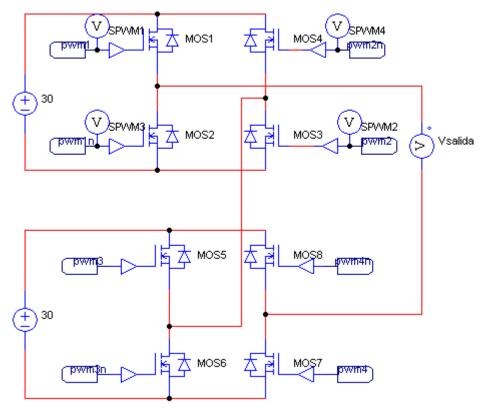

| 3.10 Etapa de potencia                                               | 51 |

| CAPÍTULO 4                                 | 53 |

|--------------------------------------------|----|

| RESULTADOS                                 | 53 |

| 4.1 Construcción de módulos                | 54 |

| 4.2 Evaluación y pruebas de funcionamiento | 54 |

| 4.3 Etapa de potencia                      | 62 |

| CAPÍTULO 5                                 | 65 |

| CONCLUSIONES Y TRABAJOS FUTUROS            | 65 |

| Referencias                                | 66 |

# Índice de figuras

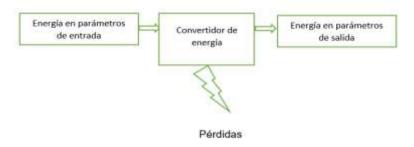

| Figura 1. Estructura básica de un convertidor eléctrico de energía            | 12 |

|-------------------------------------------------------------------------------|----|

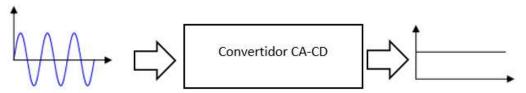

| Figura 2. Estructura básica de convertidor CA-CD                              | 13 |

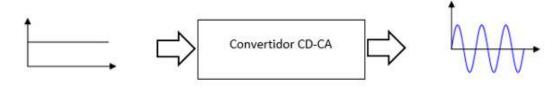

| Figura 3. Estructura básica de un convertidor CD-CA                           | 13 |

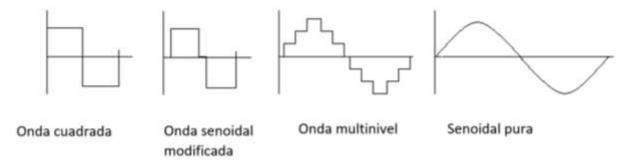

| Figura 4. Inversores de señal senoidal cuadrada, modificada o pura            | 14 |

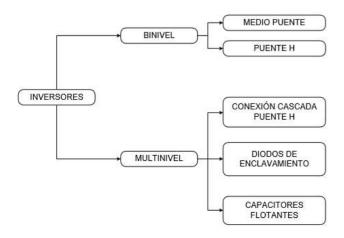

| Figura 5. Clasificación de las topologías de los inversores                   | 14 |

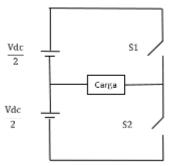

| Figura 6. Configuración de inversor medio puente                              | 15 |

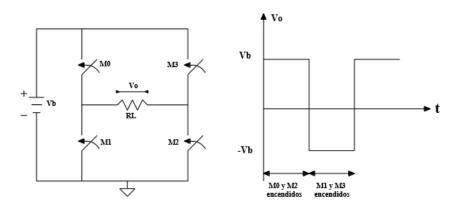

| Figura 7. Inversor monofásico en configuración puente H o puente completo.    | 15 |

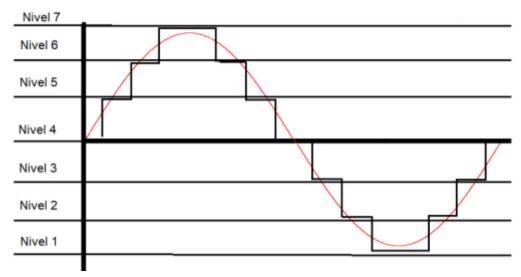

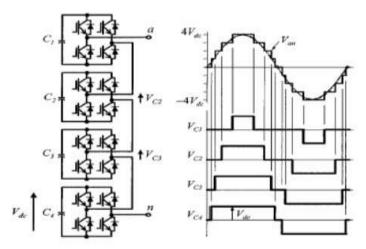

| Figura 8. Salida de un inversor multinivel                                    | 17 |

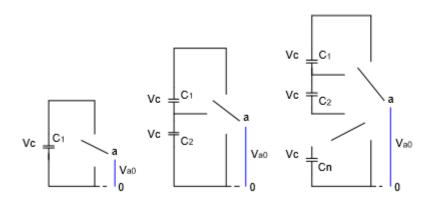

| Figura 9. Convertidor de dos, tres y n niveles                                | 18 |

| Figura 10. Inversor multinivel de tres niveles monofásico                     | 19 |

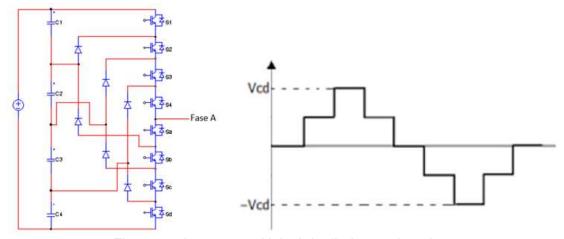

| Figura 11. Inversor multinivel de cuatro niveles trifásico                    | 20 |

| Figura 12. Inversor multinivel de diodos enclavados 7 niveles                 | 21 |

| Figura 13. Inversor multinivel de diodos enclavados con salida de voltaje CA. | 21 |

| Figura 14. Inversor multinivel de capacitores flotantes de tres niveles       | 23 |

| Figura 15. Síntesis de los modos de operación del inversor multinivel de      |    |

| capacitores flotantes                                                         |    |

| Figura 16. Inversor multinivel conectado en cascada                           | 25 |

| Figura 17. Inversor multinivel de cinco niveles y grafica de VCA              |    |

| Figura 18. Modulación por ancho de pulso único                                |    |

| Figura 19. Modulación por ancho de pulso múltiple                             | 30 |

| Figura 20. Modulación por ancho de pulso senoidal                             | 31 |

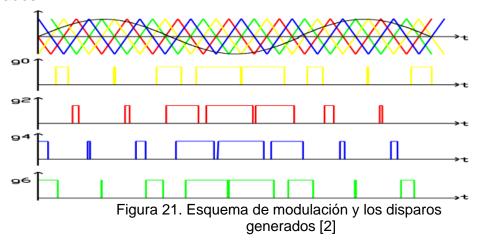

| Figura 21. Esquema de modulación y los disparos generados                     | 31 |

| Figura 22. Modulación por oposición y disposición de fase                     | 32 |

| Figura 23. Modulación por disposición de fase                                 | 32 |

| Figura 24. Pérdidas                                                           | 33 |

| Figura 25. Etapa de control                                                   | 36 |

| Figura 26. Inversor multinivel de cinco niveles                               | 37 |

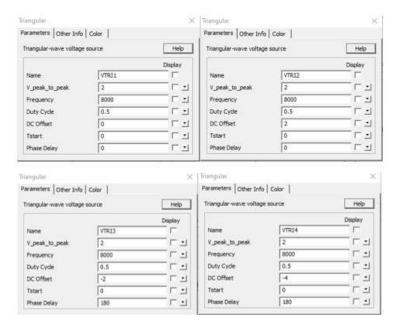

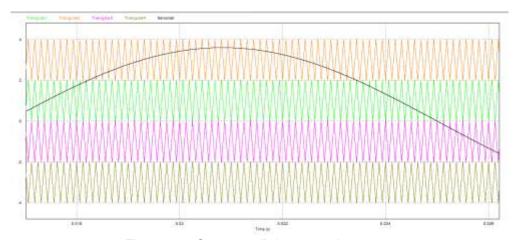

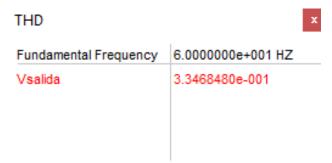

| Figura 27. Configuración de señales triangulares                              | 37 |

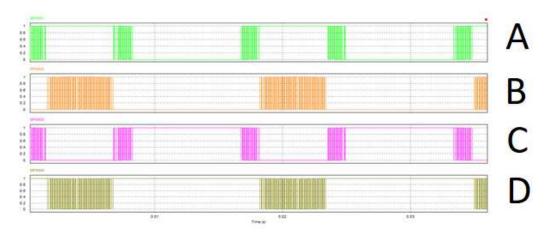

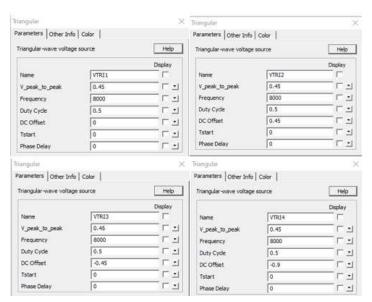

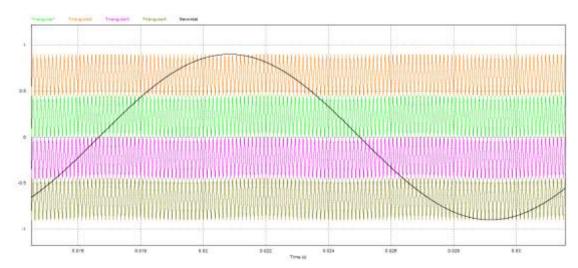

| Figura 28. Portadoras y moduladora                                            | 38 |

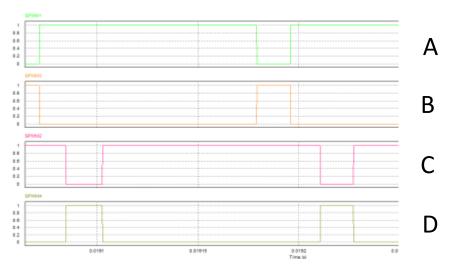

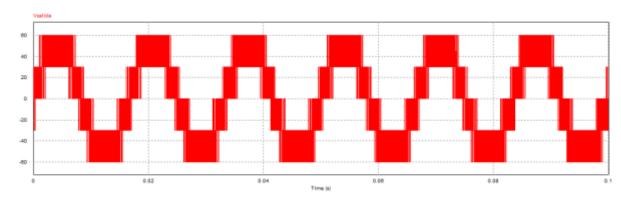

| Figura 29. Demodulación señales SPWM                                          | 38 |

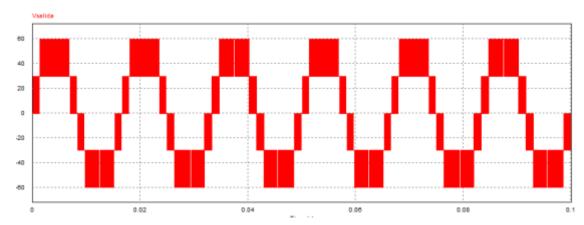

| Figura 30. Voltaje de salida CA aplicando técnica corrimiento de fase         | 39 |

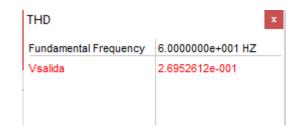

| Figura 31. Resultado THD de la técnica corrimiento de fase                    | 39 |

| Figura 32. Configuración de señales moduladoras                                          | 40 |

|------------------------------------------------------------------------------------------|----|

| Figura 33. Cuatro señales portadoras con respecto a una moduladora                       | 40 |

| Figura 34. Señales de activación SPWM modulación oposición y disposición fase            |    |

| Figura 35. Voltaje de salida en modulación oposición y disposición de fase               | 41 |

| Figura 36. Resultado THD técnica oposición y disposición de fase                         | 42 |

| Figura 37. Configuración de señales portadoras en disposición de fase                    | 42 |

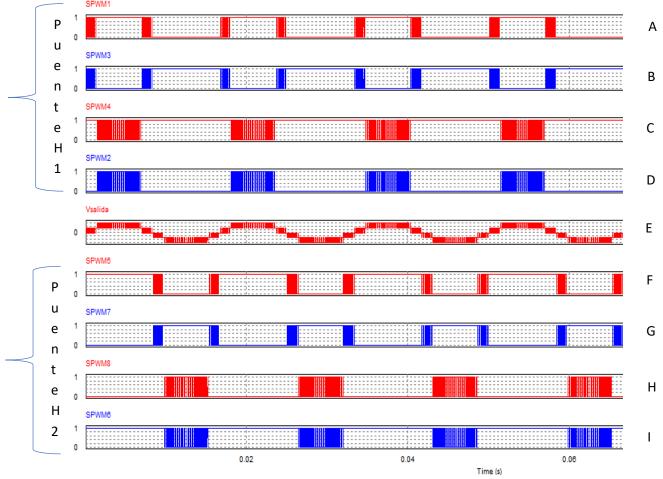

| Figura 38. Cuatro señales portadoras y moduladora en disposición de fase                 | 43 |

| Figura 39. Señales de activación SPWM modulación disposición de fase                     | 43 |

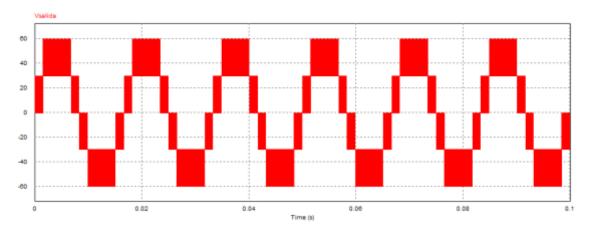

| Figura 40. Voltaje de salida en modulación disposición de fase                           | 44 |

| Figura 41. Señales de activación SPWM                                                    | 45 |

| Figura 42. Resultado THD técnica disposición de fase                                     | 45 |

| Figura 43. Diagrama esquemático inversor multinivel                                      | 46 |

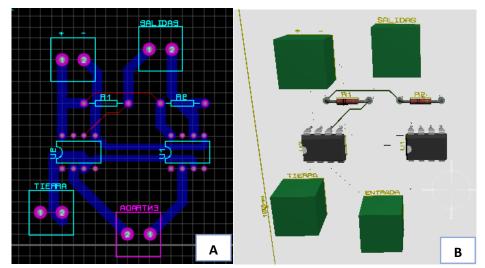

| Figura 44. A. Diagrama esquemático etapa de control B. Diagrama circuito integrado TL494 | 47 |

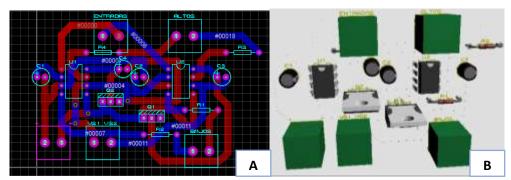

| Figura 45. A) PCB Layout Etapa de control B) Modelado 3D                                 | 47 |

| Figura 46. A) Diagrama de optoacoplador 6N137 B) Diseño esquemático                      | 48 |

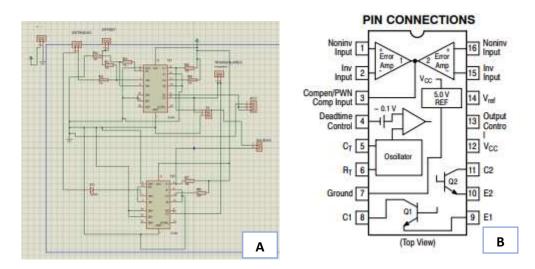

| Figura 47. PCB Layout 6N137 B) Modelado 3D                                               | 48 |

| Figura 48. A) Diagrama esquemático etapa de control B) Diagrama TL494                    | 49 |

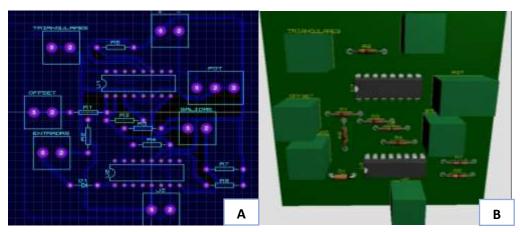

| Figura 49. A) PCB Layout TL494 B) Modelado 3D                                            | 49 |

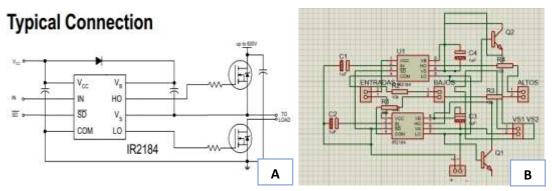

| Figura 50. A) Diagrama interno IR2184 B) Diagrama esquemático                            | 50 |

| Figura 51. A) PCB Layout IR2184 B) Modelado 3D                                           | 50 |

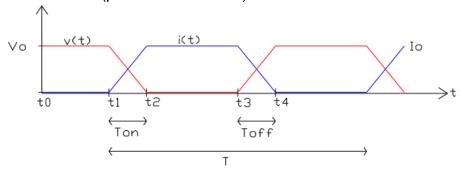

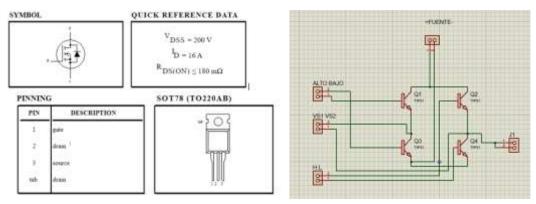

| Figura 52. Conmutación superior e inferior                                               | 51 |

| Figura 53. A) MOSFET IRF640 B) Diagrama esquemático                                      | 51 |

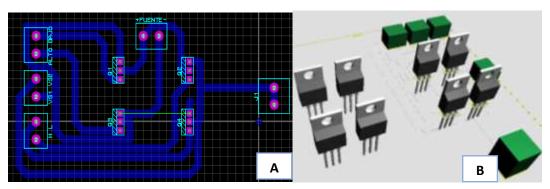

| Figura 54. A) Diseño layout B) Modelado 3D                                               | 52 |

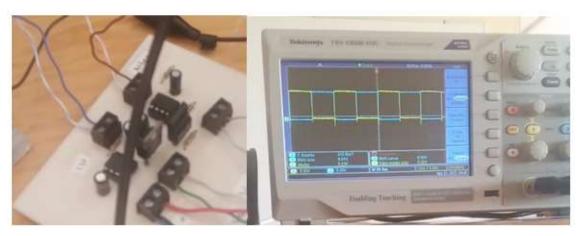

| Figura 55. Módulos de inversor multinivel                                                | 54 |

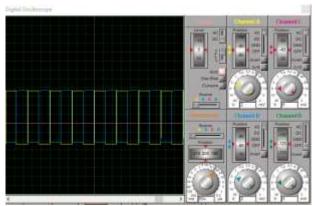

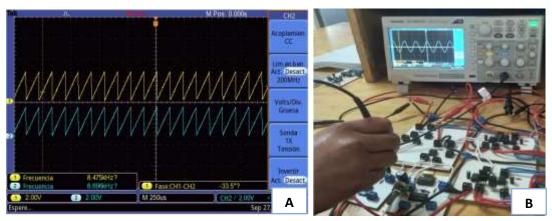

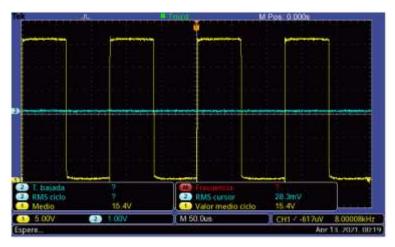

| Figura 56. A) Señales portadoras B) Señal moduladora                                     | 55 |

| Figura 57. Portadora con respecto a una senoidal                                         | 55 |

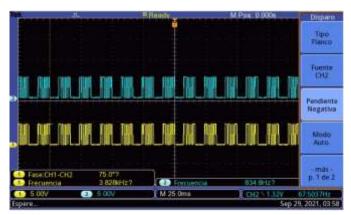

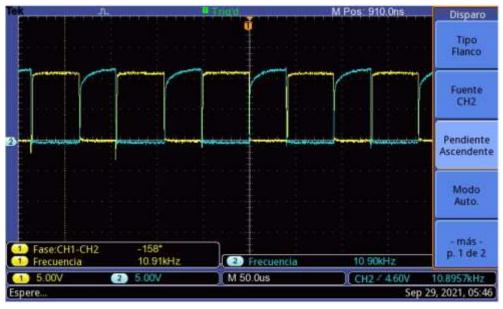

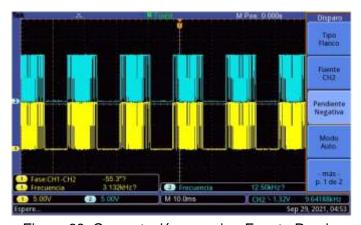

| Figura 58. Señales SPWM etapa de control                                                 | 56 |

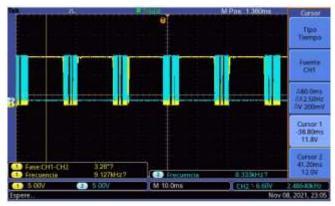

| Figura 59. Señales SPWM asilamiento óptico                                               | 56 |

| Figura 60. Testeo etapa de aislamiento óptico                                            | 56 |

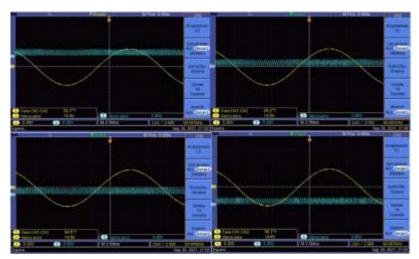

| Figura 61. Señales de conmutación superior                                               | 57 |

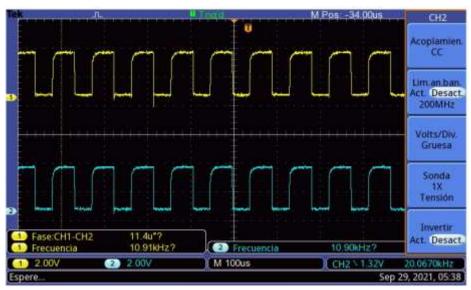

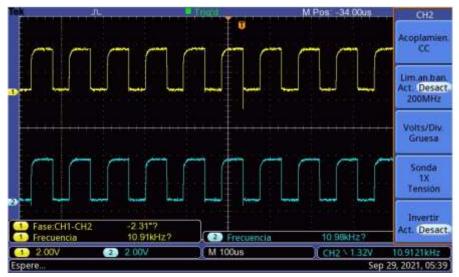

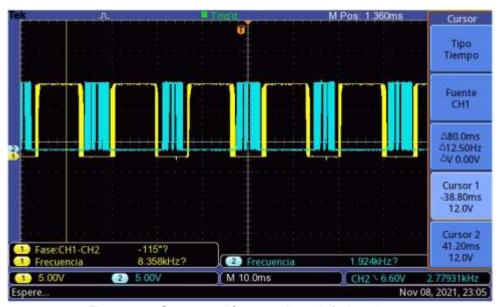

| Figura 62. Señales de conmutación inferior                                               | 57 |

| Figura 63. Señales de conmutación superior e inferior                                    | 58 |

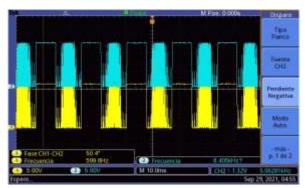

|                                                                                          |    |

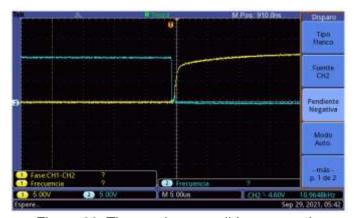

| Figura 64. Señales de conmutación superior inferior pierna uno         | . 58 |

|------------------------------------------------------------------------|------|

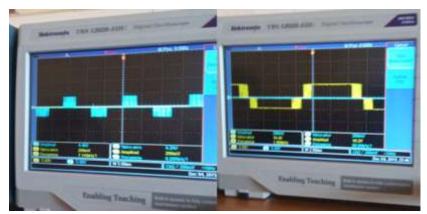

| Figura 65. Testeo módulo de acoplamiento de señales                    | . 59 |

| Figura 66. Tiempo de encendido y apagado                               | . 59 |

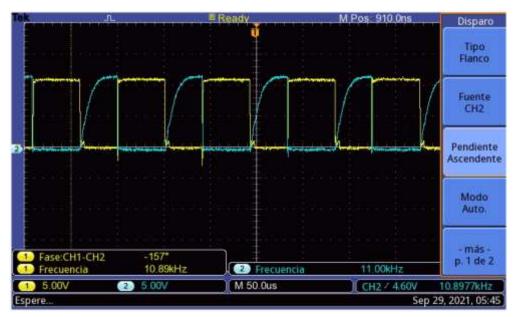

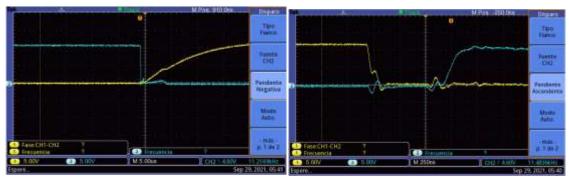

| Figura 67. Tiempo muerto                                               | . 60 |

| Figura 68. Conmutación superior                                        | . 60 |

| Figura 69. Testeo físico en conmutación superior                       | . 60 |

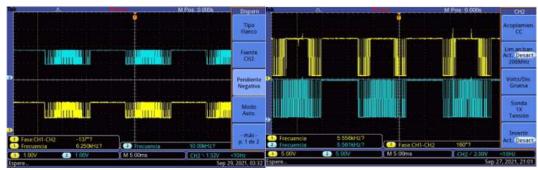

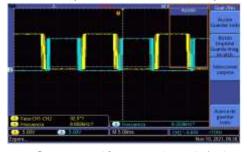

| Figura 70. Conmutación superior                                        | . 61 |

| Figura 71. Pruebas de testeo físico conmutación superior               | . 61 |

| Figura 72. Conmutación superior e inferior pierna uno puente H         | . 61 |

| Figura 73. Inversor multinivel 3 niveles                               | . 62 |

| Figura 74. Conmutación superior e inferior SPWM pierna uno             | . 62 |

| Figura 75. Conmutación superior e inferior pierna dos                  | . 63 |

| Figura 76. Señales de voltaje de salida de dos inversores de 3 niveles | . 63 |

| Figura 77. Inversor multinivel                                         | . 64 |

|                                                                        |      |

## Índice de tablas

| Tabla 1. Combinaciones posibles                                                                | 16 |

|------------------------------------------------------------------------------------------------|----|

| Tabla 2. Combinaciones posibles de inversor de diodos enclavados                               | 21 |

| Tabla 3. Estados de conmutación para inversor multinivel de capacitores flotantes en 3 niveles | 23 |

| Tabla 4. Combinaciones posibles para inversor multinivel conectado en cascada                  | 25 |

| Tabla 5. Tabla de técnicas y THD                                                               | 46 |

### Índice de ecuaciones

| Ecuacion 1. Número de niveles                          | 24 |

|--------------------------------------------------------|----|

| Ecuacion 2. Factor de potencia                         | 26 |

| Ecuacion 3. Coseno phi                                 | 26 |

| Ecuacion 4. Factor de cresta                           | 27 |

| Ecuacion 5. Potencia activa                            | 27 |

| Ecuacion 6. Potencia reactiva                          | 27 |

| Ecuacion 7. Potencia reactiva con armónicos            | 27 |

| Ecuacion 8. Potencia aparente                          | 27 |

| Ecuacion 9. Voltaje y Corriente armónico               | 28 |

| Ecuacion 10.Voltaje armónico                           | 28 |

| Ecuacion 11. Corriente armónica                        | 28 |

| Ecuacion 12. Resultado de voltaje                      | 28 |

| Ecuacion 13. Resultado de la corriente                 | 28 |

| Ecuacion 14. Distorsión armónica total                 | 29 |

| Ecuacion 15. Angulo de disparo                         | 31 |

| Ecuacion 16. Perdidas por conducción                   | 33 |

| Ecuacion 17. Potencia disipada                         | 34 |

| Ecuacion 18. Potencia disipada con interruptor apagado | 34 |

### **AGRADECIMIENTOS**

A mi familia y todas las personas que siempre estuvieron presentes a lo largo de mi formación académica, especialmente a mi madre y padre por el apoyo incondicional brindado a lo largo de todo este tiempo, así como las enseñanzas y valores que me enseñaron para ser la persona quien soy.

A mi asesor de tesis por su apoyo durante la realización del presente trabajo.

A la universidad de Ixtlahuaca CUI y a todos los docentes que formaron parte de mi ciclo, brindado las herramientas necesarias para el mundo laboral.

### **RESUMEN**

La presente tesis tiene como objetivo diseñar y construir un inversor multinivel dos etapas y cinco niveles como banco de pruebas que tenga la capacidad de recibir distintas técnicas de modulación para la evaluación de la distorsión armónica total (THD).

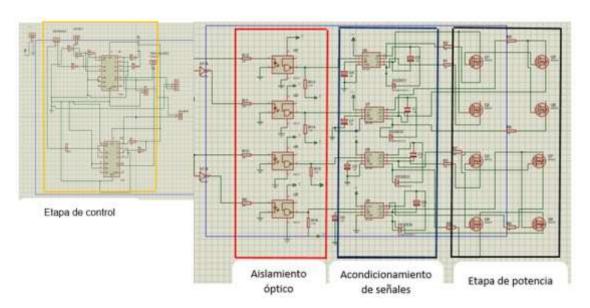

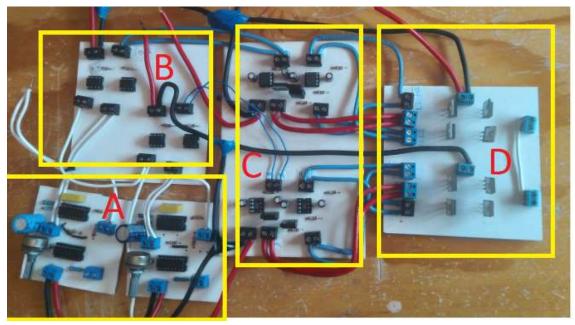

El trabajo consta de cuatro módulos, control, aislamiento óptico, acoplamiento de señales y potencia, las cuales se desglosan en el documento.

Las técnicas de modulación utilizadas no son de uso convencional por lo cual al testearlas o compararlas requiere de una base que en este caso será nuestro banco de pruebas del inversor multinivel, debido a que actualmente no existen en el mercado un dispositivo para la evaluación de estas técnicas de modulación, esto debido a que en casi todos los convertidores comerciales la modulación es por ancho de pulso (PWM). Uno de los problemas es que no generan una onda de voltaje y corriente de salida de voltaje perfecta. Los inversores multinivel son una tecnología que puede generar corrientes e incluso voltajes senoidales y con mucho menos contenido armónico. Esto debido a que se puede modular en amplitud en vez de un solo pulso (PWM). Un inversor multinivel es un circuito de potencia formado por la conexión en cascada de convertidores tipo puente H completo, que sincronizando la activación de los semiconductores asociados proporciona una señal senoidal de salida para aplicaciones de control de motores y cargas no capacitivas. Si el número de niveles es lo suficiente alto se puede obtener un voltaje lo más parecido a una senoidal de línea y con un índice de THD cercano a cero.

### CAPÍTULO 1.

### PLANTEAMIENTO DEL PROBLEMA Y PROPUESTA DE SOLUCIÓN

Actualmente los convertidores comerciales de corriente directa (CD) a corriente alterna (CA) consiguen mejores formas de onda de voltaje y corriente de salida al aumentar la frecuencia de conmutación. En aplicaciones de medio y alto voltaje estos convertidores presentan limitaciones a causa de las perdidas por conmutación y los valores elevados de distorsión armónica y distorsión armónica total (THD). Si bien para reducir estos efectos se utilizan filtros pasivos que presentan limitaciones debido a que para tener un bajo contenido armónico se requieren filtros sumamente grandes, pesados y costosos.

El desarrollo de los convertidores multinivel se debe al incremento de la demanda de potencia, con conexión a mayor voltaje, por parte de las aplicaciones, y se posibilita gracias al progreso de la tecnología de los semiconductores de potencia (IGBT, MOSFET, IGCT, etc.) y los sistemas de control digital (DSP).

Los interruptores de potencia, tales como los transistores, diodos, Ibas, Rosets, etc., usados en dispositivos electrónicos como fuentes de alimentación interrumpidas, reguladores, equipo de cómputo, etc., actúan como cargas no lineales y al estar conectadas a la red u otros sistemas, generan armónicos y potencia reactiva, los cuales producen efectos negativos en el sistema de distribución de la energía.[13]

Uno de los principales objetivos de la electrónica de potencia es mejorar la calidad de la energía, la cual busca controlar y mitigar los efectos generados por las perturbaciones en las líneas de transmisión. Los convertidores multinivel han ganado popularidad ya que permiten trabajar con frecuencias bajas de conmutación, lo que facilita el uso de semiconductores de baja velocidad reduciendo perdidas por conmutación al sintetizar formas de onda de voltaje por medio de la suma de varios niveles mucho menores. De esta manera el trabajo presenta el diseño y construcción de un inversor multinivel dos etapas y cinco niveles para el análisis de la distorsión armónica total como solución al alto contenido armónico presente en la señal de salida del inversor, se presentan tres técnicas de modulación para el encendido y apagado de los interruptores electrónicos en simulación con el software PSIM versión 9. Para reducir el contenido armónico THD presente en el inversor multinivel.

### 1.1 Introducción

De acuerdo con el escenario de planeación el consumo de energía eléctrica del Sistema Eléctrico Nacional (SEN) proyecta un crecimiento anual de 3.4% entre 2016 y 2030. Las regiones del país de mayor crecimiento en su consumo serán Baja California Sur, Noroeste, Noreste y Peninsular, con base al crecimiento medido de todo el sistema. Para la región de control central (Ciudad de México y Zona Metropolitana), durante los meses de diciembre y enero, se registra la demanda anual máxima de la región, la cual se caracteriza por contar con redes eléctricas de alta densidad de carga y un déficit en el balance carga-generación. Por lo tanto, es necesario utilizar fuentes de energías renovables con sistemas de recuperación de energía [1]. Parte importante de un sistema de recuperación de energía es la transformación de la corriente directa (CD) proveniente de la naturaleza a través de energía solar, eólica, hidroeléctrica etc.

Para utilizar la energía proveniente de estos sistemas es necesario transformar de corriente directa (CD) a corriente alterna (CA), con inversores, un inversor es un dispositivo electrónico que se encarga de transformar la corriente directa a corriente alterna. Actualmente existen en el mercado distintos tipos de inversores comerciales como son convertidores inversores de corriente de onda modificada, inversores de corriente de onda pura e inversores de corriente multifunción. Para la transformación de la energía generalmente este tipo de convertidores tienen un alto índice de contenido armónico.

En un inversor multinivel se puede conectar diferentes cargas para alimentar los puentes H, los puentes se conectan en cascada lo que a su vez provoca la suma de voltajes, es decir, si dos puentes H se alimenta con Vin de corriente directa (CD), la salida del inversor multinivel tendrá un voltaje de 2 veces V<sub>in</sub> en corriente alterna (CA). La señal de salida generada por el inversor es alterna no senoidal y con un alto índice de contenido armónico, los armónicos son voltajes o corrientes senoidales que poseen múltiplos enteros de la frecuencia a la cual el sistema de alimentación está diseñado para operar. La distorsión armónica se origina debido a las características no lineales de los equipos y cargas de un sistema de potencia, un alto contenido armónico puede generar problemas tales como son: sobrecalentamiento de conductores de neutro, disparo inesperado de saturación interruptores termo-magnéticos, de transformadores. repentinas en equipos de cómputo y caída drástica de factor de potencia.

El factor de potencia está íntimamente ligado a la distorsión armónica. A mayor distorsión armónica mayor es la corriente total respecto a la componente fundamental, de modo que el factor de potencia disminuye. Por lo tanto, la presencia de armónicos tiene un efecto negativo a la eficiencia del inversor. Para reducir el contenido armónico en muchos casos se utilizan filtros pasivos a la salida del inversor y esquemas de modulación para el encendido y apagado

de los interruptores electrónicos. Los inconvenientes de usar filtros pasivos es que son grandes, pesados y con un costo altamente elevado lo cual no resulta ser tan eficiente.

Durante el desarrollo de la tesis se evaluó distintas técnicas de modulación para el encendido y apagado en simulación de los interruptores electrónicos como son: modulación por oposición y disposición de fase, corrimiento de fase y disposición de fase con el fin de establecer la técnica de modulación adecuada para el funcionamiento del inversor con menos contenido armónico de acuerdo a la norma IEEE 519-1999 la cual indica que un inversor multinivel debe tener un THD menor a 5%.

El prototipo y trabajo desarrollado podrá ser utilizado como banco de pruebas y será una base fundamental para futuros proyectos e investigaciones para evaluar las técnicas simuladas en este trabajo, así como técnicas de control relacionados con el tema.

El desarrollo para la implementación se divide en dos etapas:

1er Etapa: Control mediante un generador de señales de modulación para el encendido y apagado de los interruptores electrónicos del inversor.

2ª Etapa: Un circuito compuesto por la conexión en cascada de convertidores tipo puente H completo para la potencia.

Donde se evaluará la técnica de disposición de fase para el encendido y apagado de los interruptores electrónicos del inversor multinivel de dos etapas y cinco niveles.

### 1.2 Problemática

Los inversores tipo puente convencionales y comerciales presentan una solución simple para la transformación de energía de CD-CA, pero estos tienen deficiencias considerables en su construcción y en la eficiencia de los mismos, debido a que sus interruptores tienen que soportar normalmente todo el voltaje del bus de corriente directa de la fuente, para aplicaciones de potencia esto es un problema ya que se tiene que utilizar componentes más robustos, así mismo se debe considerar las perdidas por conmutación y conducción al cual operar con técnicas de modulación por ancho de pulso (PWM) convencionales y con un alto contenido de distorsión armónica total (THD) a la salida de voltaje del inversor.

Las nuevas tecnologías basadas en convertidores multinivel cada vez son más utilizadas en el campo de las aplicaciones fotovoltaicas con conexión a red y actualmente se presenta en el área de las medias y altos voltajes.

Uno de los problemas más comunes que afectan a la calidad de la energía en sistemas eléctricos de voltaje es la deformación de onda producida en gran medida por un fenómeno denominado "distorsión armónica" problema que afecta tanto a las redes de distribución como a los consumidores finales.

La aparición de armónicos en corrientes y voltajes en el sistema crea problemas tales como el aumento de pérdidas de potencia activa, sobrevoltaje en los capacitores, errores de medición, mal funcionamiento de protecciones, daño en los aislamientos, disminución de la vida útil de los equipos, además de reducir el factor de potencia lo cual reduce drásticamente la eficiencia del inversor multinivel.

El comportamiento de los filtros pasivos es ser sensitivos a la impedancia del sistema para los cuales han sido ajustados, para aplicaciones donde la impedancia del sistema puede llegar a cambiar a lo largo del tiempo, se corre el riesgo de que quede obsoleto y habrá cambiado el espectro armónico de las cargas. Los filtros pasivos con frecuencia no proporcionan un comportamiento satisfactorio, bajo ciertas circunstancias pueden causar problemas de resonancia sobre el sistema donde está conectado.

Actualmente en el mercado no existe como tal un banco de pruebas para evaluar diferentes técnicas de modulación o control en este tipo de convertidores es por eso que es necesario generar un prototipo que sea capaz de probar distintas técnicas de modulación a nivel simulación, para posteriormente probar la mejor técnica de manera física y así analizar la técnica de modulación que mejor se adapta en el inversor mejorando su desempeño y reduciendo el THD.

### 1.3 Propuesta

Durante el desarrollo de la presente tesis se inició realizando el diseño del inversor multinivel, en simulación con el programa PSIM Versión 9.0, donde se validaron los componentes para el funcionamiento del inversor multinivel de dos a cinco niveles, el inversor está compuesto por cuatro interruptores electrónicos (MOSFET) a esto se le denomina puente H.

Durante la simulación se evaluaron tres técnicas de modulación que consisten en una cantidad n de señales portadoras y una moduladora representada por una onda senoidal de 60Hz, la comparación de las señales del encendido y apagado de los interruptores electrónicos que se generan, para dar paso a una señal de voltaje de salida en forma escalonada, entre más niveles tenga el inversor multinivel la señal de voltaje de salida será más parecida a una onda senoidal, una vez comparando los resultados de THD. Durante la simulación se eligió la técnica de modulación por disposición de fase, la cual presentó un menor índice de THD.

Una vez establecido el diseño del inversor y la técnica de modulación, con el programa PROTEUS Versión 9, se construyó un banco de pruebas de forma

modular de circuitos impresos para el inversor multinivel, cada módulo con su fuente de voltaje independiente, se testearon los diseños de control de los drivers para empezar la construcción de las etapas de control y potencia, durante esta etapa de control fue necesario agregar un sistema de protección óptico para la protección del circuito, así mismo en la etapa de potencia se dividió la parte de acoplamiento de señales y el puente H, dejando esta manera los módulos independientes, y en conjunto se genera el inversor multinivel.

Se desarrollaron pruebas de testeo en cada etapa utilizando una señal cuadrada de apoyo visualizar las señales de entrada y salida de cada circuito integrado, durante el proceso se agregaron capacitores en la entrada de voltaje para corregir la señal de salida si el moduló lo requería. Al finalizar la construcción del inversor se deja como banco de pruebas y se puede utilizar para probar distintas técnicas de modulación en inversores multinivel y a través de la conexión en cascada se puede utilizar el inversor desde tres a cinco niveles haciendo la conexión en cascada de los dos puentes H.

### 1.4 Justificación

Uno de los problemas más comunes que afecta a la calidad de la energía en los sistemas eléctricos de baja tensión es la deformación de onda, producida por la distorsión armónica.

Los sistemas eléctricos tienen sistemas denominados no lineales los cuales se generan a partir de ondas senoidales a la frecuencia de la red, otras ondas de diferentes frecuencias ocasionan el fenómeno conocido como generador de armónicos. Los armónicos son voltajes o corrientes senoidales que poseen frecuencias que son múltiplos enteros de la frecuencia a la cual el sistema de alimentación está diseñado para operar. Para los inversores multinivel el THD afecta principalmente en el voltaje de la salida es por eso que en la presente tesis se busca probar distintas técnicas de modulación para bajar el THD en el inversor. El inversor multinivel que se desarrolló en este trabajo servirá como banco de prueba para futuros proyectos e investigaciones similares a la misma.

En proyectos de investigación y desarrollos tecnológicos para la evaluación de técnicas de control en los circuitos integrados, es necesario contar con un hardware de base, el cual de la seguridad de igualar las condiciones del testeo de la técnica de modulación, es por esto que se desarrolló un banco de pruebas es para evaluar diferentes técnicas de modulación o control en este tipo de convertidores es necesario generar un prototipo que sea capaz de probar distintas técnicas de modulación a nivel simulación, para posteriormente probar la mejor técnica de manera física y así analizar la técnica de modulación que mejor se adapta en el inversor mejorando su desempeño y reduciendo el THD.

### 1.5 Antecedentes

A continuación, se muestran diferentes trabajos reportados en el estado del arte de la implementación de inversores multinivel de los cuales se utilizaron como base para el desarrollo y construcción de este trabajo.

En el artículo de Diego A. Toledo O. se presenta un diseño de un convertidor DC/AC de baja potencia para el aprovechamiento de energías provenientes de fuentes renovables. El convertidor utiliza un inversor monofásico con topología H5, acoplado a un filtro LC para reducir la distorsión armónica. La topología que se utiliza es un puente H de cuatro interruptores, más un quinto interruptor, de ahí el nombre H5. Generalmente el quinto interruptor va conectado al panel solar que lo separa de la etapa de potencia. Esta topología se fundamenta en el puente completo y la técnica de modulación PWM unipolar y es probado experimentalmente a lazo abierto utilizando el microcontrolador dlPIC30F4011 [2]. Con esta técnica se permite obtener una corriente de salida conmutada cuya componente de baja frecuencia es obtenida por un filtro de segundo orden LC.

Derivado de este articulo podemos hacer una comparación en cuanto a la modulación para el inversor del articulo y la del inversor multinivel propuesto por la tesis.

El presente trabajo propuesto por Chauca F. De la escuela politécnica nacional muestra los resultados de la construcción de un inversor multinivel (81 niveles) en base a inversores de tres niveles conectado, mediante transformadores en serie. Se usa una fuente de corriente directa para la entrada de los inversores y transformadores con distinta relación de transformación a la salida. El control es diseñado en base a algoritmos implementados en microcontroladores.

Los circuitos de potencia son diseñados con MOSFET de potencias adecuadas en función de cada inversor [3]. Después de leer y comprender el artículo se observó que a medida en que las etapas del convertidor multinivel aumentan se eleva el número de niveles y en consecuencia el THD se acerca más al nivel ideal cero.

El artículo publicado por Jesús Aguayo Alquicira presenta una estrategia generalizada relativa a tolerar fallas en los dispositivos semiconductores de un inversor multinivel en cascada de siete niveles y se incluyen los resultados en simulación y experimentales para la validación del método. en este artículo se presenta una técnica de modulación similar al propuesto por la tesis la diferencia es que los resultados obtenidos de este trabajo se presentan en simulación y los resultados de la presente tesis se presentaran de manera real. [4]

El artículo de la revista pistas educativas presenta una nueva técnica de control para la regulación de tensión de salida para esta familia de inversores multinivel, la cual fue implementada mediante una máquina de estados. El control propuesto fue implementado en el inversor multinivel con capacitores flotantes (FCMLI).

La principal ventaja que ofrece el control propuesto es que se modela al inversor multinivel como un conjunto de estados con sus respectivas condiciones con la finalidad de generar una máquina de estados, por lo que su implementación resulta fácil de comprender y desarrollar. Por último, se presentan las pruebas realizadas al inversor multinivel en las que se resalta la baja distorsión armónica obtenida en la tensión de salida, la respuesta que tiene el control para ajustarse eficazmente ante alteraciones de amplitud-frecuencia en la señal de referencia y además brinda buena regulación de tensión al momento de realizar un cambio de carga [5]. Con el artículo de la revista se puede observar que al desarrollar un inversor multinivel con capacitores flotantes resulta ser más tedioso a la hora de desarrollar es por eso que la opción de realizar el inversor multinivel en cascada resulta ser la mejor opción para el desarrollo de la tesis.

J. Arrillaga dice que el análisis de las señales armónicas en los sistemas eléctricos de potencia ciertamente no es un tópico moderno, antiguamente la inyección de armónicas al sistema eléctrico solo consideraba a los circuitos rectificadores y los transformadores saturados como fuente de las señales armónicas.

Actualmente gracias a una serie de estudios realizados sobre 17 armónicos, se conoce que cualquier carga no lineal produce armónicos, es decir, es una verdadera fuente de corriente armónica. En los sistemas eléctricos de potencia A.C, las corrientes armónicas fluirán por el camino de menor impedancia. Estas armónicas se dividirán de acuerdo a la razón de impedancia de las ramas. Normalmente la fuente de potencia es el camino de baja impedancia, por lo tanto, la mayoría de las corrientes armónicas fluirán hacia ella, sin embargo, si existen instalaciones de capacitores de potencia, un problema podría ocurrir cuando la reactancia capacitiva de los capacitores de potencia es igual a la reactancia inductiva equivalente del sistema [6].

En resumen, cada uno de los artículos mencionados se utilizan como guía para el desarrollo de la tesis propuesta, así mismo se presentan distintas aplicaciones donde se puede ocupar un inversor multinivel. Cada autor utiliza distintos métodos, pero al final todos llegan a la conclusión de que entre más niveles se tengan menor será el contenido armónico a la salida de voltaje del inversor.

### 1.6 Hipótesis

Se puede diseñar y construir un inversor multinivel como banco de pruebas, mismo que tiene la capacidad de evaluar diferentes técnicas de modulación con el fin de analizar el comportamiento del THD.

### 1.7 Objetivo General

Diseñar y construir un inversor multinivel de tres a cinco niveles para el análisis de distorsión armónica total THD.

### 1.7.1 Objetivos específicos

- Diseñar inversores multinivel en simulación.

- Evaluar técnicas de modulación en inversores multinivel para reducir THD.

- Seleccionar la técnica de disposición de fase THD.

- Diseñar circuitos impresos del banco de pruebas.

- Construir módulos de control y potencia.

- Evaluar y probar el funcionamiento del inversor multinivel.

- Probar distintas técnicas de modulación para la validación de los inversores.

### 1.8 Metodología

La siguiente sección se describirá una serie de pasos para poder desarrollar el objetivo general descrito en este trabajo.

Fase 1 Estado del arte: Se hizo la investigación de los trabajos previos sobre inversores multinivel, esto para definir la estructura para el desarrollo y construcción del inversor multinivel de dos etapas cinco niveles, en este proceso se juntó toda la investigación de los últimos diez años, y de esta manera se empezó a analizar la estructura del inversor con los criterios generales de construcción en un sistema de potencia. Dentro de la investigación se buscaron técnicas de control para la disminución de distorsión armónica en inversores multinivel, así como sobredimensionar los elementos de potencia que componen un inversor multinivel es así que se eligió adecuadamente los elementos que soporten las pruebas de sobre esfuerzo al momento de desarrollar el banco de pruebas.

Fase 2 Simulación de etapa de potencia: Pasando a la etapa de simulación con ayuda del software PSIM versión 9 se buscaron los dispositivos electrónicos para el armado del inversor multinivel en simulación, para ello se avaluaron las técnicas de modulación mencionadas en el planteamiento del problema y así se observó el comportamiento en la salida de voltaje del inversor, así como la cantidad de THD que presento el sistema virtual.

Fase 3 Selección de la técnica de modulación: Dentro de la etapa de simulación se evaluaron las técnicas de modulación para inversores multinivel con el fin de reducir el THD, se desarrolló una comparativa de las técnicas de modulación de corrimiento de fase, oposición y disposición de fase, así como disposición de fase.

Fase 4 Construcción y Armando de la etapa de potencia: El inversor está compuesto por dos etapas la primera de ellas es la etapa de control, donde a través de amplificadores operacionales y elementos electrónicos generaran un arreglo de señales moduladoras y portadoras, que al compararlas generaran una

modulación por ancho de pulso senoidal (SPWM), posteriormente fueron acopladas de manera óptica con opto-acopladores de esta manera se pasó a la etapa de potencia donde se desarrollaron los puentes h con interruptores semiconductores de potencia que estarán encendiendo y apagando en distintos tiempos para generar señales de voltaje de salida en forma escalonada.

Fase 5 Pruebas y testeo de la parte física: Una vez armado el inversor multinivel se comenzó con las pruebas de los dispositivos que integran el sistema de control con el fin de dejar la etapa de potencia como un banco de pruebas para futuros proyectos e investigaciones. Se analizaron los resultados obtenidos durante el desarrollo de la tesis, presentando un inversor multinivel como banco de pruebas, así como el testeo de técnicas de modulación para el accionamiento de los inversores del banco.

### CAPÍTULO 2.

### MARCO TEÓRICO

En este capítulo se presenta la teoría básica de electrónica de potencia, así como la transformación de energía a través de todos los tipos de convertidores que existen actualmente.

Se presenta la definición de los inversores multinivel, tipos de inversores multinivel, topologías, técnicas de modulación. Así como el desarrollo para la evaluación de las técnicas de distorsión armónica y distorsión armónica total (THD).

### 2.1 Electrónica de potencia

La electrónica de potencia es la parte de la electrónica encargada del estudio de dispositivos, circuitos, sistemas y procedimientos para el procesamiento, control y conversión de la energía eléctrica. [7]

Hoy en día la electrónica de potencia es una de las ramas de la ingeniería eléctrica fundamental para procesar y controlar el flujo de corriente de una fuente de alimentación a carga. Su finalidad es controlar y reducir los efectos generados por las perturbaciones en las líneas de transmisión, en estos casos se utilizan filtros activos, estos se encargan de generar e inyectar las señales de tensión y corriente armónicas de carga conectada en la red eléctrica, evitando que genere tales armónicos.

La base fundamental de la electrónica de potencia está en el uso de dispositivos semiconductores que funcionan como interruptores electrónicos, en consecuencia, la energía que se disipa en el interruptor (pérdidas) es considerablemente menor a la que se disipa cuando éste opera en la zona lineal. Por ejemplo, mientras que con un divisor de tensión logra alcanzar una eficiencia de tan sólo el 30 %, con la tecnología de conmutación se llega a alcanzar una eficiencia de hasta el 90% [8].

### 2.2 Transformación energía

El objetivo de los circuitos electrónicos de potencia consiste en adaptar los requisitos de voltaje o corriente al dispositivo en el que se desee trabajar. Estos circuitos electrónicos de potencia convierten la forma de voltaje y corriente de un determinado nivel a otro es por eso que se les denomina "convertidores", y se clasifican dependiendo de la relación que existe entre la entrada y salida.

Un convertidor de energía es un sistema o equipo electrónico que tiene por objetivo la transformación de la energía. El concepto inicial de convertidor puede extenderse para incluir aspectos como eficiencia, reversibilidad, grado de idealidad, fiabilidad, volumen o tecnología. Dentro de los convertidores de energía se encuentran los convertidores CD-CA, CA-CA, DC-CD, CD-CA. En la figura 1 se muestra la estructura básica de un convertidor.

Figura 1. Estructura básica de un convertidor eléctrico de energía. Fuente Propia

Los convertidores se agrupan de acuerdo al formato de las energías de entrada y salida.

#### Entrada (CA)- Salida (CD) Rectificadores

Su topología básica se integra por un diodo y un filtro, la cual se complica al querer tener una mejor calidad en la señal de salida. Producen una salida continua a partir de una entrada alterna. La potencia media se transfiere desde un generador de alterna a una carga de corriente directa. A los convertidores cacd se les llama específicamente rectificadores, por ejemplo, un convertidor cacd permite que los circuitos integrados operen a partir de un voltaje alterno de una determinada frecuencia, convirtiendo la señal alterna en una señal directa del voltaje apropiado.

La estructura básica de este tipo de convertidores se muestra en la figura 2 donde se representan también las formas de onda ideales de entrada y salida.

Figura 2. Estructura básica de convertidor CA-CD. Fuente Propia

#### Entrada (CD)- Salida (CA) Inversores

El convertidor CD-CA se denomina específicamente como inversor. Es un dispositivo electrónico que se encarga de transformar la corriente directa en alterna. En el inversor, la potencia media fluye desde el lado de corriente directa hacia el lado de corriente alterna figura 3.

Figura 3. Estructura básica de un convertidor CD-CA. Fuente Propia

### 2.3 Tipos de inversores

Los inversores se pueden clasificar en inversores con tensión de salida de señal cuadrada, senoidal modificada, onda multinivel y tensión de salida de señal senoidal pura. Figura 4.

Figura 4. Inversores de señal senoidal cuadrada, modificada o pura. Fuente Propia

Los inversores que obtienen una onda cuadrada de voltaje o senoidal modificada, se utilizan principalmente para conectar cargas del tipo resistivo. Algunas aplicaciones las usan fuentes de energía de respaldo para aparatos electrónicos como son: computadoras y televisiones. Pero no sirven para cargas inductivas como los refrigeradores o bombas de agua. Los inversores de onda multinivel o senoidal pura son menos conocidos y de costo elevado, la gran ventaja es que estos inversores si permiten conectar cargas inductivas que son más comunes en la industria y en el uso residencial.

Los inversores generan una salida de corriente alterna (CA) a partir de una fuente de corriente directa (CD). Se puede clasificar en función del número de niveles en la onda de salida como se muestra en la figura 5.

Figura 5. Clasificación de las topologías de los inversores [2]

### 2.3.1 Topologías de los inversores binivel

Un convertidor binivel está formado por dos semiconductores que tienen órdenes de encendido puestas (con complementarias). Al conjunto de dos semiconductores que trabajan de esta manera se denomina célula de conmutación. Para ello existen dos topologías como medio puente y puente completo (puente h).

### 2.3.1.1 Inversores de medio puente

Está formado por dos fuentes de voltaje y dos interruptores figura 6. Cuando se cierra el interruptor S1, la carga tiene un voltaje positivo igual a Vdc/2, si se cierra S2 la carga tiene un voltaje negativo igual a -Vdc/2, si ambos interruptores están abiertos el voltaje es de 0, cabe aclarar que es importante no cerrar ambos interruptores al mismo tiempo para evitar cortos circuitos.

Figura 6. Configuración de inversor medio puente. Fuente Propia

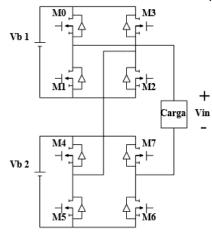

#### 2.3.1.2 Inversor de puente completo

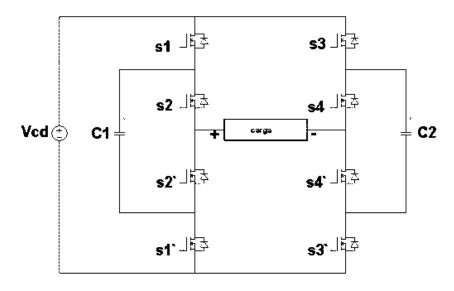

Esta topología que consiste en cuatro interruptores electrónicos como se muestra en la figura 7, que permiten el flujo de corriente de una fuente de corriente directa a una carga resistiva inductiva (RL). Se le conoce como ramas del puente H al par de interruptores del mismo lado del puente H. siendo la primera rama los interruptores M0 y M1 y la siguiente rama es M2 y M3.

Figura 7. Inversor monofásico en configuración puente H o puente completo [2]

La operación de dicha topología se puede explicar de manera simple como sigue: En un primer instante de tiempo cuando, el par de interruptores M0-M2 está cerrado y el par M1-M3 abierto, circula una corriente eléctrica a través de M0 a M2 pasando por la carga, lo que a su vez provoca una diferencia de potencial en RL de magnitud igual a Vb. En un segundo instante de tiempo, con el par M0-M2

abierto y el par M1-M3 cerrado, la corriente circula a través de M1 y M3 pasando por la carga, lo que también provoca una diferencia de potencial de magnitud igual a Vb en RL, pero de signo contrario a la primera. La alternancia de esta configuración de estados de interruptores origina que en la carga se presente una tensión de naturaleza alterna de magnitud pico igual a Vb, tal como se muestra en la Figura 2. Si además M0 y M3 o M1 y M2 funcionan abren o cierran simultáneamente el valor de tensión en la carga será de cero.

A este tipo de inversores se le conoce como inversores de tres niveles ya que la señal que generan puede adoptar cualquiera de los tres niveles de tensión siguientes: Igual a Vb cuando M0 y M2 cierran, Igual a –Vb cuando M1 y M3 cierran, Igual a cero bajo alguna de las tres siguientes combinaciones: cuando todos los interruptores están desactivados, cuando M0 y M3 cierran o cuando M1 y M2 cierran.

Cabe aclarar que las combinaciones anteriores no son las únicas posibles que se pueden implementar en un puente H, pero sí las únicas permitidas ya que cualquier otra ocasionaría (debido a la topología) un corto circuito. Además, se puede determinar que con solo una señal de encendido y su negada es posible generar los niveles Vb y –Vb en el puente H [13].

Combinaciones M1 М3 Vo M0 M2 1 Vb ON **OFF** ON OFF 2 -Vb OFF ON **OFF** ON 3 0 OFF OFF OFF OFF 4 0 ON **OFF OFF** ON 5 0 **OFF** ON ON **OFF** NA ON ON NA ON ON

Tabla 1. Combinaciones posibles

### 2.4 Filtros

La solución más utilizada en aplicaciones industriales para filtrar armónicos de corriente y compensar la potencia reactiva a frecuencia fundamental, es la instalación de filtros pasivos paralelo en las terminales de cargas no lineales. Un filtro pasivo está constituido básicamente por uno o más conjuntos de bloques LC de baja resistencia serie con el objetivo de reducir perdidas. Esta característica de bajo amortiguamiento pueda dar lugar a resonancias entre el

filtro y la impedancia de la red, y así amplificar las distorsiones en lugar de atenuarlas. Una manera diferente es usar filtros activos de corriente puesto que soluciona el problema de las resonancias paralelo. Generalmente, estos consisten en un inversor trifásico operando como fuente de corriente. Su impedancia equivalente a la salida es alta y las resonancias entre el filtro y la línea son mínimas, sin embargo, un filtro activo paralelo tiene problemas derivados de su diseño y construcción práctica. Además, para algunas aplicaciones de baja potencia, el costo del filtro activo puede convertirlo en una solución no viable en términos económicos [3]. De esta manera surgen los inversores multinivel como una nueva solución para reducir e incluso evitar el uso de filtros a la salida de la señal del inversor. Esto debido a que entre mayor sea el número de niveles menor será el contenido armónico presente en la salida de voltaie del inversor.

### 2.5 Inversores multinivel

Los inversores multinivel alimentados en tensión han surgido como una nueva opción de convertidor para aplicaciones de alta potencia. El inversor multinivel básicamente sintetiza una onda de tensión en varias tensiones de corriente directa escalonadas figuras 8 [7].

Figura 8. Salida de un inversor multinivel.

Fuente Propia

Los inversores multinivel son una tecnología clave en la generación, transmisión, distribución y utilización de la potencia eléctrica. Son utilizados en muchas aplicaciones industriales como el control de motores, compensadores estáticos, aire acondicionado, fuentes de potencia ininterrumpibles, filtros activos, sistemas de transmisión flexibles.

El primer inversor multinivel apareció en 1975 y fue el inversor multinivel en cascada patentado por Baker y Bannister, este utilizaba fuentes de corriente CD separadas para sintetizar una onda de salida escalonada. Posteriormente apareció el inversor multinivel con diodos de enclavamiento en 1980 (también

introducido por Baker y Bannister), el cual permitió usar sólo una fuente de voltaje para el inversor. El siguiente inversor multinivel apareció entre los años 1997 y 1998 y fue conocido corno inversor multinivel con capacitares flotantes, introducido por Meynard, Foch y Lavielk. Estas 3 configuraciones de inversores multinivel son conocidas como las topologías clásicas de los inversores multinivel. Desde entonces han aparecido una gran cantidad de patentes de inversores multinivel para distintas aplicaciones [4].

La función principal de los convertidores multinivel es mejorar la onda de voltaje alterno generada, usando diferentes niveles de voltaje directo. Su funcionamiento es tal que, al aumentar el número de niveles, el voltaje de salida, que está formado por escalones de voltaje, tiene mayor resolución porque entre mayor sea el número de escalones se asemeja más a una onda senoidal y con menos distorsión armónica. [5]

Los convertidores multinivel, pueden trabajar con las técnicas de modulación convencionales de PWM, pero además pueden ser modulados en amplitud, lo que produce salidas mucho más limpias. Los inversores multinivel incluyen un arreglo de semiconductores y fuentes de voltaje para formar un voltaje de salida escalonado. Las conmutaciones de los semiconductores permiten la suma o resta de las distintas fuentes de voltaje directo, generando una onda de onda de voltaje de amplitud variable.

La figura 9 muestra un diagrama esquemático de un convertidor multinivel con diferentes números de niveles, donde los semiconductores de potencia se representan por interruptores ideales con varias posiciones.

Figura 9. Convertidor de dos, tres y n niveles [2]

La salida de voltaje que presenta el inversor multinivel es de forma alterna, no senoidal, esto representa un alto índice de contenido armónico en el sistema y representa un problema que afecta directamente a la señal de salida. Para la reducción del contenido armónico se utilizan filtros pasivos a la salida de la señal del inversor y técnicas de modulación de las señales para el encendido y apagado de los interruptores electrónicos. Uno de los problemas más grandes que se presenta en los filtros pasivos suelen ser sumamente grandes y costosos,

como alternativa se evalúan distintas técnicas de modulación para el control del encendido y apagado de los interruptores electrónicos.

Los principales objetivos que se tiene en los inversores es aumentar el nivel de potencia que tienen y alcanzar el mejor desempeño reflejado con un bajo contenido armónico y reducción de pérdidas. Una de las topologías mayormente usada es la de convertidores multinivel o inversores multinivel, la función de este tipo de inversores es juntar varios niveles de voltaje de corriente directa en una sola señal en forma de escalón lo que es más parecido a una onda senoidal, es decir entre más niveles se tenga en el inversor mayor se asemeja a una onda senoidal y con un menor contenido armónico.

Por lo general los inversores multinivel se clasifican en tres topologías clásicas.

### 2.5.1 Topologías de los inversores multinivel

A continuación, se presenta un resumen, así como el funcionamiento de cada topología de los inversores multinivel como son: diodos de enclavamiento capacitores flotantes y cascada.

### 2.5.1.1 Inversor multinivel con diodos enclavados (DCMLI)

Su función principal es sintetizar una onda senoidal a partir de varios niveles de tensión normalmente obtenida de condensadores que funcionan como fuentes de CD. Los condensadores utilizados se conectan en serie para dividir la tensión y de esta manera, los dispositivos de potencia operan con una tensión menor entre terminales. En la estructura presentada por Nabae en 1980 [3] figura 10, muestra la topología de diodos de enclavamiento, es un inversor de 3 niveles monofásico y es la primera topología multinivel práctica que se utilizó y que aún es estudiada.

El voltaje de salida se obtiene conectando la carga entre los puntos A y B formando un puente completo. Utilizando esta estructura se puede extender a n número de niveles, desafortunadamente presenta como desventaja desbalances de tensión en el bus de corriente directa (CD).

Figura 10. Inversor multinivel de tres niveles monofásico. Fuente Propia

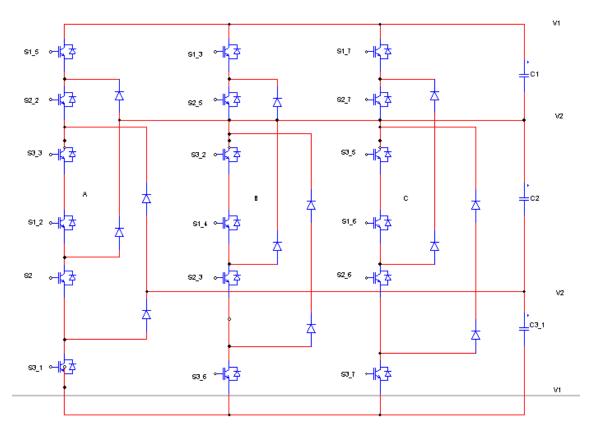

La figura 11 muestra estructura trifásica para un inversor multinivel con diodos enclavados de 4 niveles. Donde el número de niveles se define como el número de escalones de tensión que se obtiene en la salida A, B o C y el nivel de tierra.

Figura 11. Inversor multinivel de cuatro niveles trifásico. Fuente Propia

Esta topología se caracteriza por dividir la tensión continua de alimentación en una cierta cantidad de niveles por medio de condensadores conectados en serie. La cantidad de capacitores necesarios para ello está dada por (m-1), donde m representa el número de niveles del inversor. En la figura 12 se presenta un inversor multinivel de diodos enclavados cinco niveles.

Se necesita (m-1) (m-2)/2 diodos de enclavamiento, los cuales deben ser capaces de bloquear la tensión proveniente del capacitor. El número de interruptores electrónicos está dado por 2(m-1) por cada fase deseada. En la tabla 2 se presentan la secuencia de disparo y los niveles de tensión para el inversor de cinco niveles.

Figura 12. Inversor multinivel de diodos enclavados 7 niveles. Fuente Propia

Tabla 2. Combinaciones posibles de inversor de diodos enclavados

| Van    | M1 | M2 | М3 | M4 | M5 | M6 | M7 | M8 |

|--------|----|----|----|----|----|----|----|----|

| Vdc/2  | ON | ON | ON | ON |    |    |    |    |

| Vdc/4  |    | ON | ON | ON | ON | ON |    |    |

| 0      |    |    | ON | ON | ON | ON | ON |    |

| -Vdc/4 |    |    |    | ON | ON | ON | ON |    |

| -Vdc/2 |    |    |    |    | ON | ON | ON | ON |

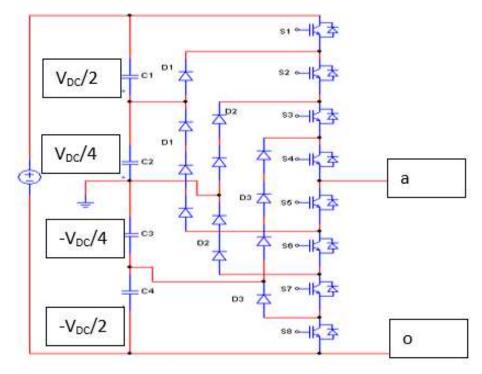

La figura 13 muestra el diagrama del inversor y el resultado de la salida de voltaje CA en el inversor multinivel de cinco niveles con diodos enclavados.

Figura 13. Inversor multinivel de diodos enclavados con salida de voltaje CA. Fuente Propia

## 2.5.1.1.1 Características principales del inversor multinivel con diodos enclavados

Las características más importantes para esta topología es que el esfuerzo en voltaje de los dispositivos se balancea con el número de niveles, ya que el voltaje que debe manejar cada dispositivo es menor, esta topología utiliza, en su versión trifásica, un mismo banco de capacitores para alimentar a las tres fases, lo cual hace que los capacitores deban ser de gran capacidad. Los diodos de enclavamiento permiten fijar los niveles de voltaje en la salida. Minimiza las pérdidas por conmutación y de esta manera aumenta la eficiencia del convertidor y permite operar desde condiciones iniciales de cero voltajes y cero corrientes.

### 2.5.1.1.2 Desventajas del inversor multinivel con diodos enclavados

Se requiere un número excesivo de diodos de enclavamiento cuando el número de niveles es alto. Debido a que los diodos de enclavamiento manejan tensiones iguales o mayores a un nivel, y cuando son mayores a un nivel se tienen que conectar en serie para dividir la caída de voltaje de manera equitativa. Cuando el número de niveles es suficientemente alto, el número de diodos requeridos hará al sistema costoso, e tedioso para implementar además es difícil obtener el control del flujo de potencia real para inversores individuales. Debido a que al manejar energía activa sólo se obtiene energía de los capacitores, estos tienden a descargarse, provocando un desbalance de voltaje en el bus de corriente directa (CD).

### 2.6 Inversor con capacitores flotantes

Para este tipo de inversores multinivel utiliza una estructura escalonada de capacitores, donde la salida se expresa como las posibles combinaciones de conexión de los capacitores de los que se compone, cada capacitor que se utiliza es para establecer los niveles de tensión.

# 2.6.1 Características de los inversores con capacitores flotantes

Cuanto mayor sea el número de niveles se utilizan más capacitores y el esfuerzo de voltaje en los dispositivos conectados disminuye conforme aumenta el número de dispositivos. Proporciona redundancia de estados para la generación de ciertos niveles, esto permite flexibilidad para mantener la carga en los capacitores y el arranque es más complejo que en el inversor multinivel con diodos enclavados.

### 2.6.1.1 Control para un inversor multinivel de capacitores flotantes

Se utiliza un algoritmo de control para para la modulación de estos inversores multinivel, la ventaja de utilizar este algoritmo es que se modela al inversor como un conjunto de estados con la finalidad de generar una máquina de estados.

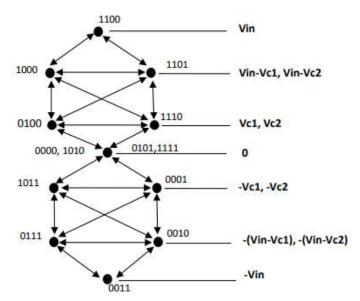

Figura 14. Inversor multinivel de capacitores flotantes de tres niveles [6]

En la tabla 3 se muestran los estados de conmutación para obtener los niveles del inversor multinivel de capacitores flotantes. En esta topología existe redundancia de combinaciones para generar un nivel.

Tabla 3. Estados de conmutación para inversor multinivel de capacitores flotantes en 3 niveles

|                          | S1 | S2 | S3 | S4 |

|--------------------------|----|----|----|----|

| Interruptor              |    |    |    |    |

| Nivel Generado           |    |    |    |    |

| 0 V                      | 1  | 1  | 1  | 1  |

|                          | 1  | 0  | 1  | 0  |

|                          | 0  | 1  | 0  | 1  |

|                          | 0  | 0  | 0  | 0  |

| +(V_capacitor)           | 0  | 1  | 0  | 0  |

|                          | 1  | 1  | 1  | 0  |

| +(V_entrada-V_capacitor) | 1  | 0  | 0  | 0  |

|                          | 1  | 1  | 0  | 1  |

| +(V_entrada)             | 1  | 1  | 0  | 0  |

| -(V_capacitor)           | 0  | 0  | 0  | 1  |

|                          | 1  | 0  | 1  | 1  |

| -(V_entrada-V_capacitor) | 0  | 0  | 1  | 0  |

|                          | 0  | 1  | 1  | 1  |

| -(V_entrada)             | 0  | 0  | 1  | 1  |

Después de conocer los modos de conmutación se realiza una síntesis de operación del inversor multinivel de capacitores flotantes, así como para sus opciones para el salto entre niveles como se muestra en la figura 15.

Figura 15. Síntesis de los modos de operación del inversor multinivel de capacitores flotantes [2]

#### 2.6.1.2 Desventajas en inversor multinivel de capacitores flotantes

Se requiere una cantidad excesiva de capacitores de almacenamiento cuando la cantidad de niveles es grande, los inversores en altos niveles son más difíciles de encapsular por los voluminosos capacitores de potencia que también son más costosos. El control del inversor puede ser muy complicado. La frecuencia de conmutación es alta provocando pérdidas por conmutación para la transmisión de potencia real.

### 2.7 Inversor multinivel conectado en cascada

Esta topología se constituye como la conexión de varios inversores de tres niveles en cascada, cada uno de ellos alimentado por una tensión directa independiente [5]. La salida es la suma de los voltajes de cada uno de los inversores de tres niveles. Con esta topología es posible obtener niveles de tensión de acuerdo a la siguiente expresión.

Ecuacion 1. Número de niveles

$$2n + 1$$

.....(1)

Donde n representa al número de inversores de tres niveles.

Los inversores multinivel conectados en cascada pueden ser a su vez clasificados como inversores simétricos y asimétricos.

La diferencia entre ellos radica en la magnitud de la fuente de alimentación de cada inversor de tres niveles. Los inversores simétricos requieren que las fuentes de alimentación tengan la misma magnitud, en cambio los asimétricos poseen fuentes de tensión de valores diferentes. Lo anterior se refleja en la cantidad de niveles que pueden generar con base en la misma secuencia de encendido. Los inversores asimétricos pueden generar más niveles de tensión que los simétricos.

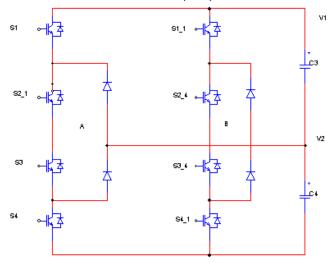

En la figura 16 se muestra el diagrama de conexión para un inversor en cascada simétrico de dos etapas y cinco niveles. Este inversor puede generar voltajes de salida que van desde -2VDC a 2VDC y al igual que con el inversor de capacitores enclavados no son únicas las combinaciones para generar los niveles de voltaje. En la Tabla 4 se presentan todas las combinaciones posibles de encendido.

Figura 16. Inversor multinivel conectado en cascada [2]

Tabla 4. Combinaciones posibles para inversor multinivel conectado en cascada

| Combinaciones | Vin1 | Vinv2 | Vinv |

|---------------|------|-------|------|

| 1             | Vb1  | Vb2   | 2Vb  |

| 2             | Vb1  | 0(4)  | Vb   |

| 3             | Vb1  | 0(5)  | Vb   |

| 4             | 0(4) | Vb2   | Vb   |

| 5             | 0(5) | Vb2   | Vb   |

| 6             | Vb1  | -Vb2  | 0    |

| 7             | -Vb1 | Vb2   | 0    |

| 8             | 0(4) | 0(4)  | 0    |

| 9             | 0(4) | 0(5)  | 0    |

| 10            | 0(5) | 0(4)  | 0    |

| 11            | 0(5) | 0(5)  | 0    |

| 12            | -Vb1 | 0(4)  | -Vb  |

| 13            | -Vb1 | 0(5)  | -Vb  |

| 14            | 0(4) | -Vb2  | -Vb  |

| 15            | 0(5) | -Vb2  | -Vb  |

| 16            | -Vb1 | -Vb2  | -2Vb |

Figura 17. Inversor multinivel de cinco niveles y grafica de VCA [7]

#### 2.8 Definición de armónicos

Los armónicos son voltajes o corrientes senoidales que poseen frecuencias que son múltiplos enteros de la frecuencia a la cual el sistema de alimentación está diseñado para operar. La distorsión armónica se origina debido a las características no lineales de los equipos y cargas de un sistema de potencia.

# 2.8.1 Indicadores esenciales de la distorsión armónica

Los principales indicadores a considerar en la distorsión armónica es el factor de potencia, factor de cresta, potencia de distorsión, espectro de frecuencia, tasa de distorsión armónica y a su vez la definición de Distorsión armónica total.

## 2.8.2 Factor de potencia

El factor de potencia está muy ligado a la distorsión armónica, entre mayor es la distorsión armónica menor será el factor de potencia y de define como la relación entre la potencia activa P y la potencia aparente S. se define con la siguiente ecuación.

Ecuacion 2. Factor de potencia

$$FP = \frac{P}{F}.$$

(2)

En el área eléctrica, el factor de potencia es frecuentemente confundido con el Coseno phi( $\cos \phi$ ), cuya definición es

Ecuacion 3. Coseno phi

$$Cos\phi = \frac{P1}{S1}....(3)$$

P1= Potencia activa del fundamental, S1= Potencia aparente del fundamental. Cabe aclarar que el cos  $\phi$  se refiere únicamente a la frecuencia fundamental, y en presencia de armónicos, es diferente del factor de potencia.

#### 2.8.3 Factor de cresta

Se define como la relación entre el valor de cresta de corriente o de voltaje (Im o Vm) y el valor eficaz.

Ecuacion 4. Factor de cresta

$$K = \frac{Im}{I_{RMS}} \quad o \quad K = \frac{Vm}{V_{RMS}}.$$

(4)

Para una señal senoidal el factor de cresta es igual a  $\sqrt{2}$ , para una señal no senoidal el factor de cresta puede tener un valor superior o inferior a  $\sqrt{2}$ . Este factor es particularmente útil para detectar la presencia de valores de cresta excepcionales con respecto al valor eficaz.

Un factor de cresta muy elevado implica sobreintensidades puntuales importantes. Estas sobreintensidades, detectadas por los dispositivos de protección, pueden ser el origen de desconexiones indeseadas.

#### 2.8.4 Potencia activa

La potencia activa P de una señal distorsionada por armónicos es la suma de las potencias activas correspondientes a los voltajes e intensidades del mismo orden.

La descomposición del voltaje y la intensidad en sus componentes armónicas puede ser escrita como:

Ecuacion 5. Potencia activa

$$P = \sum_{n=1}^{\infty} V_n I_n \cos \phi_n \dots (5)$$

Siendo  $\phi_h$  el desfase entre el voltaje y la intensidad del armónico de orden h. Se supone que la señal no contiene componente directa. En ausencia de armónicos, la ecuación  $P = V_1 * I_1 * Cos \phi_1$  indica la potencia de una señal senoidal, donde cos  $\phi_1$  es igual a  $Cos \phi$ .

#### 2.8.6 Potencia reactiva

Consideramos la potencia aparente S.

Ecuacion 6. Potencia reactiva

$$S = V_{rms} * I_{rms} \dots (6)$$

En presencia de armónicos, se puede reescribir la ecuación como:

Ecuacion 7. Potencia reactiva con armónicos

$$S^2 = \sum_{h=1}^{\infty} V_h I_h \cos \phi_h \dots (7)$$

Como consecuencia en presencia de armónicos, la relación  $S^2 = P^2 + Q^2$  no es válida. Se define la potencia de distorsión D de tal forma que  $S^2 = P^2 + Q^2 + D^2$ . Asi pues

Ecuacion 8. Potencia aparente

$$S = \sqrt{P^2 + Q^2 + D^2}....(8)$$

#### 2.8.6 Tasas de distorsión armónica

Antes de analizar la manera en la que se evalúa la distorsión armónica en redes eléctricas vamos a indicar la representación matemática de una señal eléctrica en el dominio del tiempo.

Como ejemplo se toma la frecuencia fundamental de 60HZ con sus respectivos múltiplos.

Si el voltaje y la corriente en una red eléctrica están definidos por:

Ecuacion 9. Voltaje y Corriente armónico

$$v(t) = V * Cos\omega_0 t, i(t) = I * Cos\omega_0 t....(9)$$

Respectivamente, pero como en los sistemas eléctricos en estas señales podría darse la presencia del voltajes y corrientes armónicas, entonces el voltaje y la corriente se pueden representar por:

Ecuacion 10. Voltaje armónico

$$v(t) = V_1 * Cos(\omega_0 t + \theta_1) + V_2 * Cos(2 * \omega_0 t + \theta_2) + V_3 * Cos(3 * \omega_0 t + \theta_3) + \cdots (10)$$

Ecuacion 11. Corriente armónica

$$i(t) = I_1 * Cos(\omega_0 t + \theta_1) + I_2 * Cos(2 * \omega_0 t + \theta_2) + I_3 * Cos(3 * \omega_0 t + \theta_3) + \cdots (11)$$

Que en forma compacta de podrían reescribir como:

Ecuacion 12. Resultado del voltaje

$$v(t) = \sum_{n=1}^{k} V_n * Cos(n\omega_0 t + \theta_n).....(12)$$

Ecuacion 13. Resultado de la corriente

$$i(t) = \sum_{n=1}^{k} I_n * Cos(n\omega_0 t + \theta_n)......13)$$

Donde:

$V_n$  se le define como la armónica de voltaje de orden n, a

$\mathit{I}_n$  se le define como la armónica de corriente de orden n y a

$\theta_n$  como el ángulo de la armónica n [13]

# 2.8.7 Distorsión armónica total (THD)

La tasa de distorsión armónica es frecuentemente utilizada para definir la importancia del contenido armónico de una señal alterna. Para medir la cantidad de componentes armónicas presentes en la salida de un inversor se utiliza un parámetro llamado THD, se encarga de evaluar la coincidencia de una señal con respecto a la componente fundamental de esta misma señal.

El inversor ideal es aquel que genera señales de salida con un THD de valor cero.

Se define matemáticamente la THD por la ecuación 14.

Ecuacion 14. Distorsión armónica total

$$THD = \frac{(\sqrt{\sum_{2,3,\dots}^{\infty} Vn^2})}{\text{Vo}}.$$

(14)

Donde:

Vo = Magnitud de la componente fundamental

Vn = Magnitud de la componente armónica individual

Con el fin de reducir el contenido armónico se utilizan las técnicas de modulación previamente comentadas ya que una característica de éstas es que desplazan las componentes armónicas a un rango de frecuencia alta, aproximadamente a la frecuencia de conmutación frecuencia de la portadora.

# 2.9 Esquemas de modulación

El objetivo del esquema de modulación de los inversores multinivel es sintetizar el voltaje de salida de tal manera que se asemeje a una onda senoidal. Con el paso del tiempo se han desarrollado técnicas de modulación para la reducción del contenido armónico y reducir las pérdidas de conmutación.

El método más utilizado para la modulación es el que modifica ancho de pulso de las señales de disparo de los interruptores electrónicos del inversor y se le conoce como modulación de ancho de pulso (PWM).

Existen varias formas para modificar el ancho de pulso de las señales de control de los interruptores electrónicos del inversor se clasifican en modulación por ancho de pulso único, modulación por ancho de pulsos múltiples y modulación por ancho de pulsos senoidales.

La importancia de estos métodos es generar un patrón de pulsos de disparo de los interruptores electrónicos. Estos métodos utilizan dos señales una llamada portadora (en forma triangular), donde la frecuencia establece el número de veces que los interruptores funcionan en cada medio ciclo, y una llamada moduladora (en forma senoidal) la cual establece la forma y frecuencia de la señal de salida del inversor. La comparación de estas señales establece la secuencia de las señales de disparo, así como la duración de las mismas. Es muy importante que la frecuencia de la señal portadora sea mucho mayor a la señal moduladora.

### 2.9.1 Modulación por ancho de pulso único

Tiene un solo pulso de disparo (para cada par de interruptores) por cada medio ciclo de la señal de salida del puente H. Las señales de disparo se generan comparando la señal de referencia periódica (portadora) con la señal de control (moduladora) de forma cuadrada.

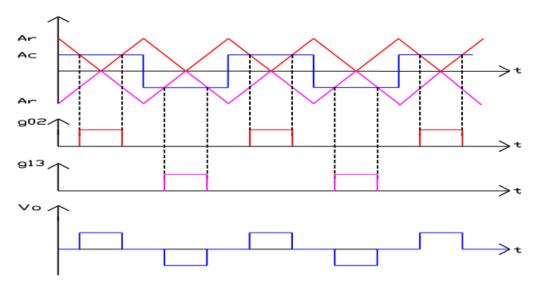

En la Figura 18 Se muestra la generación de las señales de disparo (g02 y g13) bajo este método y la salida en la carga del puente H (Vo). La señal portadora es de magnitud Ar y la señal de control de forma cuadrada es de magnitud Ac.

Figura 18. Modulación por ancho de pulso único [2]

## 2.9.2 Modulación por ancho de pulso múltiple

Consiste en generar más de un pulso en cada medio periodo en la figura 19 se muestran las señales de disparo y la salida del inversor. La ventaja de usar este método de modulación es que en la salida del inversor hay menor contenido armónico.

Figura 19. Modulación por ancho de pulso múltiple [2]

# 2.9.3 Modulación por ancho de pulso senoidal

Ésta forma de modulación consiste en utilizar una señal moduladora de forma senoidal de frecuencia igual a la que se desea obtener a la salida del inversor. Con lo anterior se logra que el ciclo de trabajo de los pulsos de disparo varíe de acuerdo con la amplitud de la onda senoidal. En la figura 20 se muestra la generación de las señales de disparo (g02 y g13) y la salida del inversor (Vo).

Figura 20. Modulación por ancho de pulso senoidal [2]

### 2.9.4 Modulación para inversores multinivel

Se utilizan las técnicas de modulación para modificar el tiempo de encendido y apagado de los interruptores electrónicos del inversor, para ello existen técnicas de modulación para los inversores multinivel. Estas se basan principalmente en el uso de múltiples señales portadoras. El número de señales portadoras necesarias está dado por n-1 donde n representa el número de niveles.

#### 2.9.4.1 Modulación por corrimiento de fase

Para obtener el patrón de encendido de los interruptores electrónicos por este método se requiere de la comparación entre n-1 portadoras con la señal de referencia (moduladora). Las n-1 portadoras deben estar desfasadas entre sí un ángulo  $\theta$ , donde.

Ecuacion 15. Angulo de disparo

$$\theta = \frac{360^{\circ}}{n-1}....(15)$$

En la figura 21 se presenta este esquema de modulación y los disparos generados.

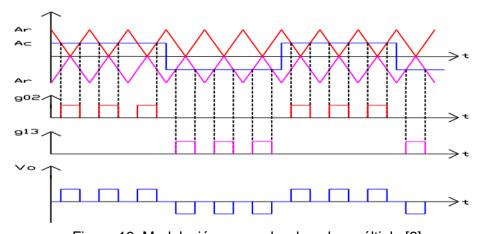

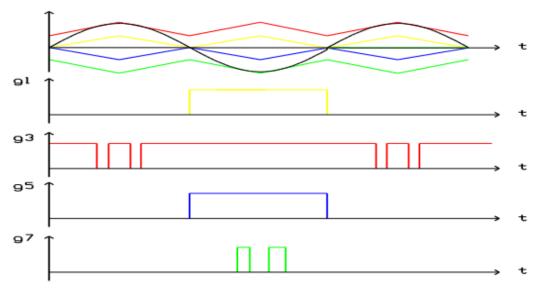

#### 2.9.4.2 Modulación por oposición y disposición de fase

Este método consiste en que la mitad de las señales portadoras se ubiquen por arriba del nivel cero de la señal moduladora (senoidal) y la otra mitad por debajo del cero de tal forma que el valor pico de la primera corresponda al valor mínimo de segunda. Existe, además, entre el grupo de arriba y abajo un desfasamiento de 180° mientras que entre las portadoras de cada grupo no hay desfasamiento. En la figura 22 se muestra el esquema correspondiente.

Figura 22. Modulación por oposición y disposición de fase [2]

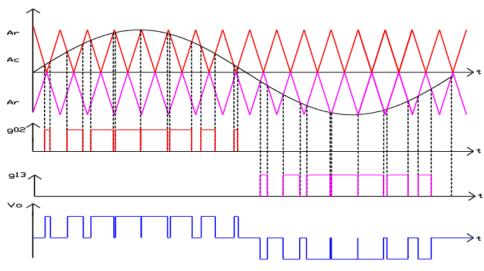

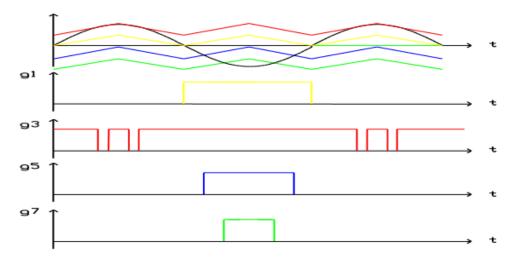

#### 2.9.4.3 Modulación por disposición de fase

En este método el conjunto de portadoras cuenta con el mismo ángulo de fase entre ellas. Las portadoras están colocadas de forma paralela de tal manera que en conjunto abarcan toda la señal moduladora. En la figura 23 se muestra tal esquema de conmutación.

Figura 23. Modulación por disposición de fase [2]

#### 2.9.5 Desempeño de los inversores

El rendimiento y optimización que tiene un inversor multinivel se mide en la calidad de señal alterna que generan, es por eso que se mide el contenido armónico y las pérdidas que presenta el sistema durante su funcionamiento.

#### 2.9.6 Pérdidas

El concepto de pérdidas, no sólo en los inversores sino en los convertidores electrónicos de potencia, es importante ya que permite cuantificar la eficiencia del sistema.