#### UNIVERSIDAD NACIONAL AUTÓNOMA DE MÉXICO

PROGRAMA DE MAESTRÍA Y DOCTORADO EN INGENIERÍA INGENIERÍA ELÉCTRICA – SISTEMAS ELECTRÓNICOS

# SUPERFICIES SELECTIVAS DE FRECUENCIA RECONFIGURABLES PARA SISTEMAS DE ANTENAS

#### TESIS QUE PARA OPTAR POR EL GRADO DE: MAESTRO EN INGENIERÍA

PRESENTA: ROLANDO SIBAJA PALAFOX

DR. JOSÉ ISMAEL LÓPEZ MARTÍNEZ, FACULTAD DE INGENIERÍA

MÉXICO, D.F. ENERO 2016

UNAM – Dirección General de Bibliotecas Tesis Digitales Restricciones de uso

#### DERECHOS RESERVADOS © PROHIBIDA SU REPRODUCCIÓN TOTAL O PARCIAL

Todo el material contenido en esta tesis esta protegido por la Ley Federal del Derecho de Autor (LFDA) de los Estados Unidos Mexicanos (México).

El uso de imágenes, fragmentos de videos, y demás material que sea objeto de protección de los derechos de autor, será exclusivamente para fines educativos e informativos y deberá citar la fuente donde la obtuvo mencionando el autor o autores. Cualquier uso distinto como el lucro, reproducción, edición o modificación, será perseguido y sancionado por el respectivo titular de los Derechos de Autor.

#### **JURADO ASIGNADO:**

Presidente: Dr. Jorge Rodríguez Cuevas

Secretario: Dra. Fátima Moumtadi

1er. Vocal Dr. José Ismael . Martínez López

2do. Vocal Dra. Margarita Navarrete Montesinos

3er. Vocal Dra. Laura Oropeza Ramos

Ciudad Universitaria, México D.F.

#### **TUTOR DE TESIS:**

Dr. José Ismael Martínez López

-----

**FIRMA**

#### **AGRADECIMIENTOS**

#### Agradezco:

A mi familia por animarme a continuar en los momentos de incertidumbre.

A todo el equipo de trabajo, profesores y alumnos de Electrónica para RF y Microoondas, por compartirme una nueva visión en el diseño electrónico, y de despejarme ciertos paradigmas que no pueden aplicarse a esta fascinante área de retos desafiantes.

A mi alma máter la UNAM, la Facultad de Ingeniería y la División de Estudios de Posgrado, por darme nuevamente la oportunidad de formar parte de su comunidad y de actualizar mis conocimientos.

Al Consejo Nacional para la Ciencia y la tecnología (CONACYT) por otorgarme una beca para la realización de mi maestría.

A la Dirección General de Asuntos del Personal Académico ( DGAPA ) por los recursos otorgados al proyecto PAPIIT IN114213

"No conozco tus órganos interiores, solo tu armadura más sencilla de 300 femtofarads. Dios me pide que al insertarte en una celda el conjunto resuene muy cerca de 20GHz. Las ondas ni siquiera acarician el otro lado, solo se tuercen en la superficie de la celda. No puedo conseguirlo, me queda una celda tan minúscula que me es imposible soldarte a ella... Al menos que seas tan pequeño como la misma celda, pero entonces ya no se trata de soldarte. Si tu armadura fuera más frágil tan solo de 15 femtofarads, otro ingeniero tendría que fabricarte al mismo tiempo que la celda, y necesariamente la celda tendría que aumentar en dimensiones. Dios ha leído mis pensamientos, se asoma entre las ondas de colores no visibles y ríe, juega conmigo. Él ya sabía la respuesta desde el principio de los tiempos, cuando deslizó un bosón a través de una abertura ".

Rolando Sibaja Palafox.

### ÍNDICE

| Resumen                                                                                       | 7           |

|-----------------------------------------------------------------------------------------------|-------------|

| Capítulo 1. Superficies Selectivas de Frecuencia Reconfigurables (SSFR) dispositivos activos. | con         |

| 1.1 Antecedentes y revisión del estado del arte                                               | 8           |

| 1.2 Justificaciones                                                                           | 21          |

| 1.3 Objetivos                                                                                 | 24          |

| 1.4 Infraestructura                                                                           | 24          |

| Capítulo 2. Elementos de análisis y diseño de la configuración básica o para la SSFR.         | de la celda |

| 2.1 Consideraciones preliminares de análisis de la SSFR                                       | 25          |

| 2.2 Selección de la geometría de la celda                                                     | 26          |

| 2.3 Dimensiones externas de la celda y sus materiales                                         | 26          |

| 2.4 Software disponible para el proyecto                                                      | 26          |

| 2.5 Modelo eléctrico básico equivalente de la celda                                           | 27          |

| 2.6 Alta del proyecto para las simulaciones, identificación de los paráme                     | tros        |

| de dispersión y utilización de elementos concentrados en las simulacion                       | es32        |

| 2.7 Estrategias de análisis y diseño para obtener el corrimiento máx                          | kimo en la  |

| frecuencia de resonancia adentro de la banda X, utilizando el in-                             | tervalo de  |

| capacitancia comercial del varactor                                                           |             |

| 34                                                                                            |             |

| 2.8 Problemática en el criterio de convergencia en las simulaciones                           | 41          |

| 2.9 Alternativas para remediar la problemática                                                | 42          |

| 2.10 Conclusiones del capítulo 2                                                              |             |

| Capítulo  | 3.   | Ejemplo    | de    | análisis | y | diseño | de | una | celda | reconfigurable | con |

|-----------|------|------------|-------|----------|---|--------|----|-----|-------|----------------|-----|

| capacitor | es i | nterdigita | ales. | 1        |   |        |    |     |       |                |     |

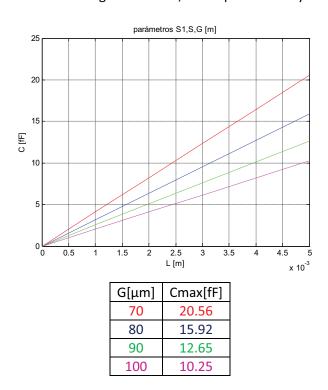

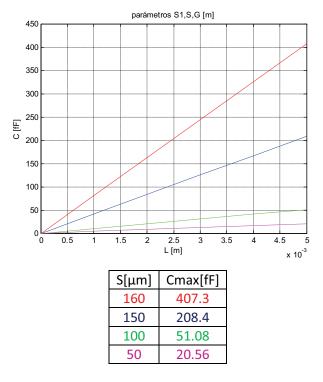

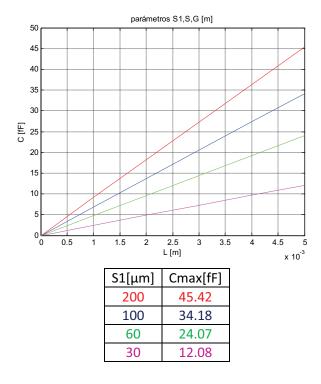

| 3.1 Comportamiento de los capacitores interdigitales de tres placas            | 44      |

|--------------------------------------------------------------------------------|---------|

| 3.2 Método para definir la geometría de los capacitores interdigitales de tres | placas, |

| conocidas la distancia de separación entre las placas, y la longitud de la     | -       |

| central                                                                        | -       |

| 3.3 Par de celdas cargadas con capacitores interdigitales en la guía de onda   |         |

|                                                                                |         |

| 3.4 Modelo eléctrico equivalente preliminar de la SSFR pasiva                  |         |

| 3.5 Conclusiones del capítulo 3                                                | /3      |

|                                                                                | 1 -     |

| Capítulo 4. Análisis y diseño de la celda con diodo varactor para obte         | ener ia |

| reconfigurabilidad en la frecuencia de resonancia y su optimización.           |         |

| 4.1 Celda con muescas y cortocircuitos radiales en forma de arco               | 74      |

| 4.2 Celda agregando una apertura anular interna                                | 90      |

| 4.3 Celda ajustando los cortocircuitos radiales rectos                         |         |

| 4.4 Identificación de la fuente de pérdidas y estrategia de análisis y diseño  |         |

| para reducirlas                                                                | 108     |

| 4.5 Nuevo diodo varactor abre las posibilidades a la reducción de las          |         |

| pérdidas                                                                       | 111     |

| 4.6 Adaptación de la celda a la guía de onda WR-90                             |         |

| 4.6.1 Celda con muescas para el diodo MA46120, si se utilizara al mismo        |         |

| MA46120                                                                        | 117     |

| 4.6.2 Celda con muescas para el diodo SMV2019, si se utilizara al              |         |

| MA46120                                                                        | 120     |

| 4.7 Selección del par celda - diodo varactor y preparación de la SSFR          |         |

| activa final                                                                   | 122     |

| 4.8 Intervalo del voltaje aplicado a los diodos varactores de la SSFR activa   | 132     |

| 4.9 Circuito de control para la SSFR activa                                    |         |

| 4.10 Conclusiones del capítulo 4                                               | 134     |

| I .                                                                            |         |

### Capítulo 5. Mediciones y conclusiones.

| 5.1 Análisis de resultados y conclusiones para la SSFR pasiva | 135  |

|---------------------------------------------------------------|------|

| 5.2 Análisis de resultados y conclusiones para la SSFR activa | 146  |

| 5.3 Conclusiones generales                                    | 148  |

| Bibliografía                                                  | -151 |

| Apéndice A.                                                   |      |

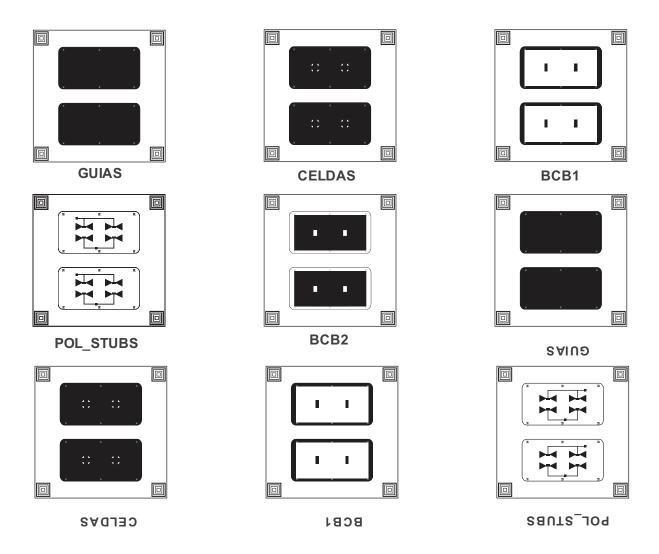

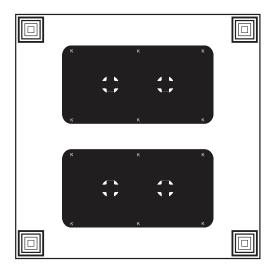

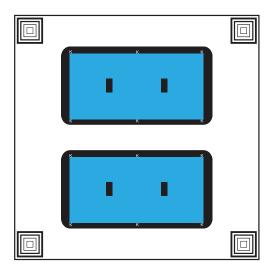

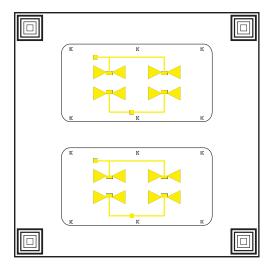

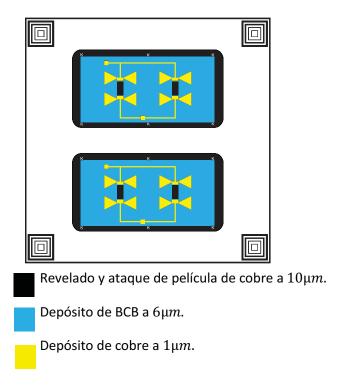

| Máscaras para fabricar las SSFR                               | 153  |

#### Resumen

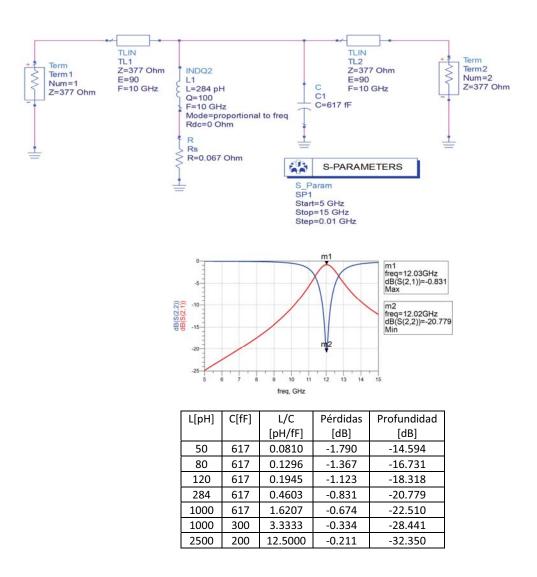

En el ámbito de las telecomunicaciones existen diversas razones por las que hay necesidad de controlar remotamente el comportamiento de una superficie selectiva de frecuencia como la saturación del espectro radioeléctrico y la prolongación de la vida útil de la batería. En este trabajo se utiliza al diodo varactor como elemento de control simple, pues requiere para operar de solo un voltaje de polarización. Es de mucho interés conocer su comportamiento en alta frecuencia incorporado en una superficie, porque los fabricantes solo reportan sus modelos a baja frecuencia. En general los diodos varactores tienen asociadas pérdidas altas, pero no se sabe qué tan altas pueden llegar a ser en alta frecuencia, ni tampoco si es posible reconfigurar sobre la frecuencia de resonancia. Este trabajo responde a estas preguntas y puede utilizarse como una referencia para futuros trabajos de investigación.

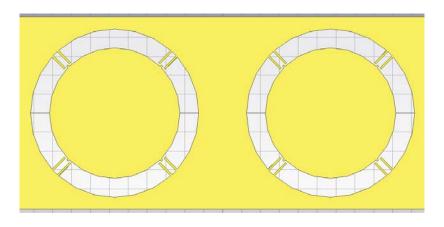

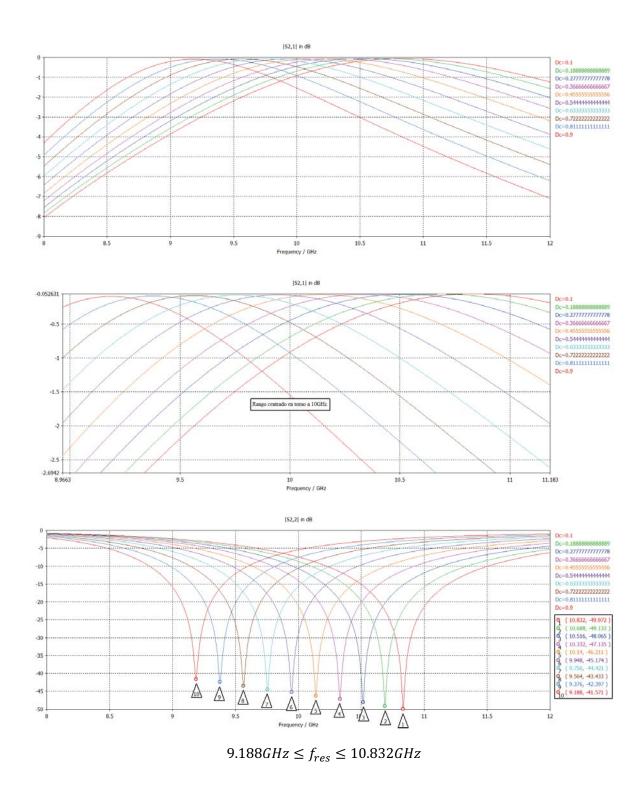

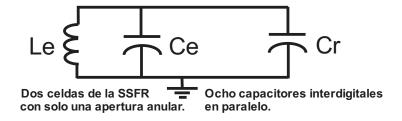

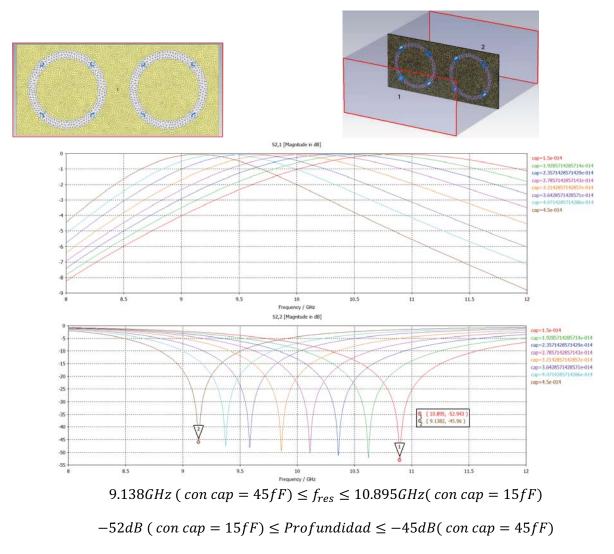

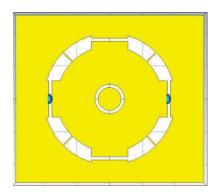

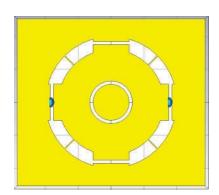

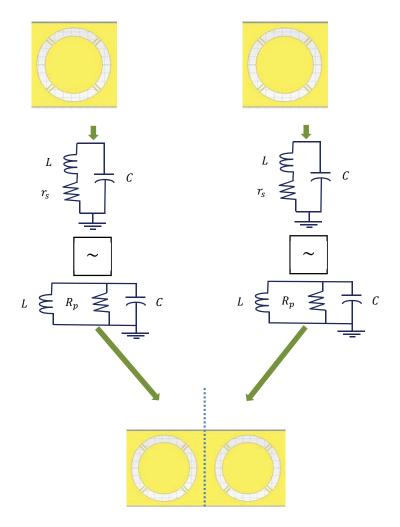

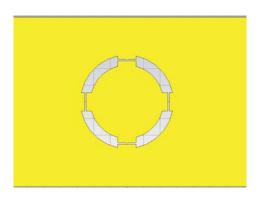

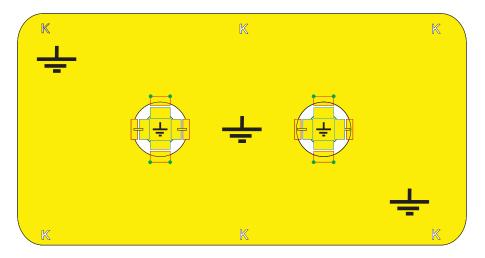

El presente trabajo trata del diseño, simulación, fabricación y medición de una superficie selectiva reconfigurable del tipo pasobanda transmitiva operando en la banda X, que emplea elementos reconfiguradores pasivos y activos, los cuales introducen cambios de capacitancia para desplazar a la frecuencia resonante. Para la superficie pasiva se emplean capacitores interdigitales, y para la superficie activa se emplean diodos varactores. Aunque la superficie pasiva no admite un control remoto, sirve para identificar ciertos problemas de diseño relacionados con la gran diferencia en el valor de la capacitancia entre un capacitor interdigital pasivo, y la que puede ofrecer un diodo varactor típico, y así poder abordar con éxito el diseño de la superficie activa. Si bien existen desarrollos con diodos varactores en la banda X como en [10], la reconfigurabilidad se logra empleando varios componentes que dificultan la adición de más celdas sobre la superficie ( su miniaturización ) y además la vuelven más costosa. Otros desarrollos se limitan a más bajas frecuencias como en [11] y [12], y hasta el momento no existe un desarrollo en banda X con diodo varactor que utilice celdas con geometría circular, la cual es utilizada en el presente trabajo por las bondades bien reconocidas [4-7], como su estabilidad en el ángulo de la onda incidente en un intervalo amplio.

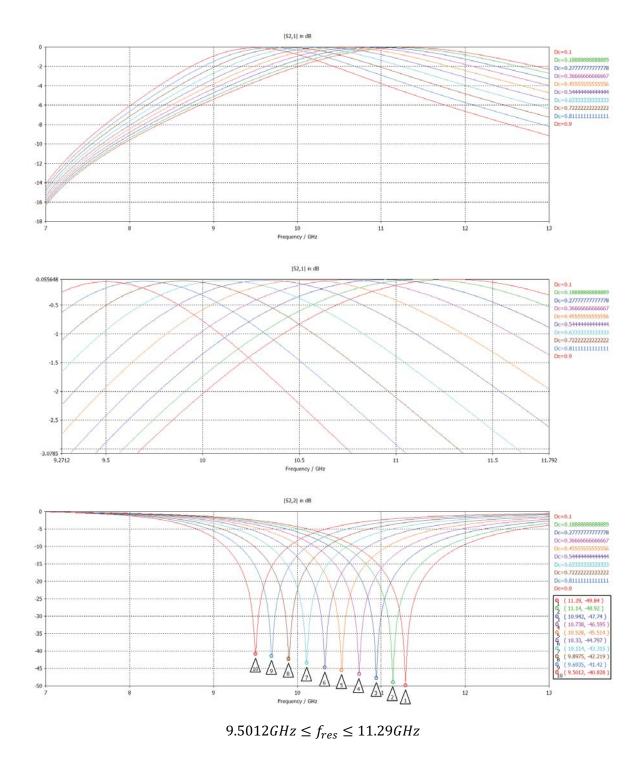

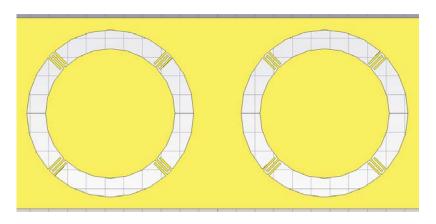

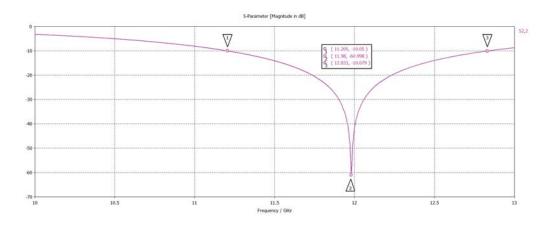

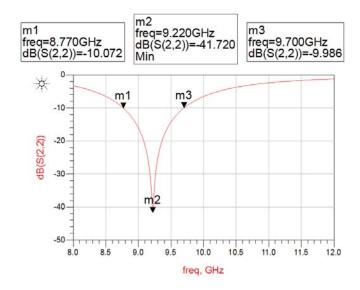

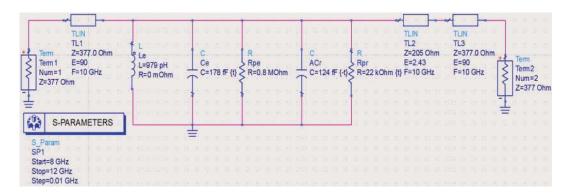

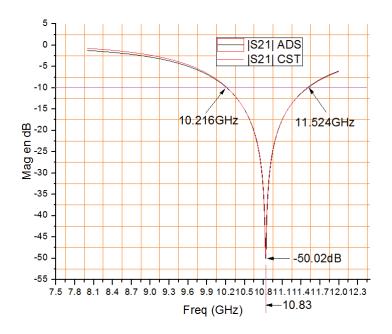

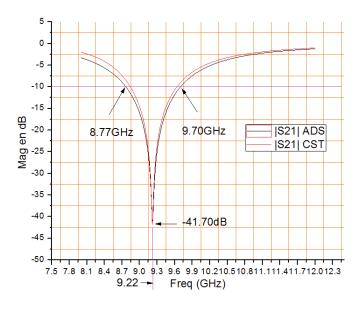

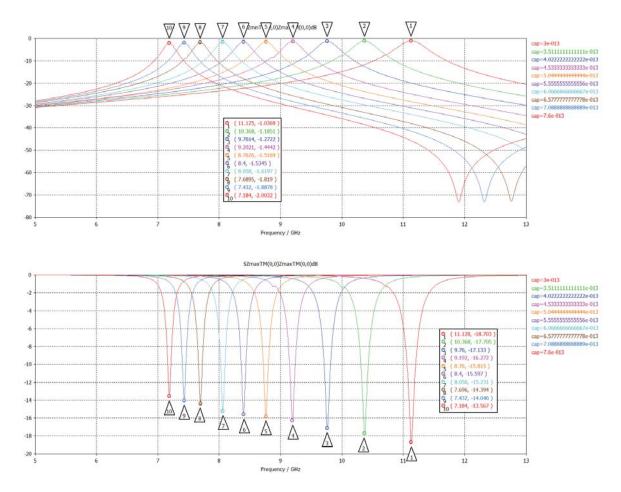

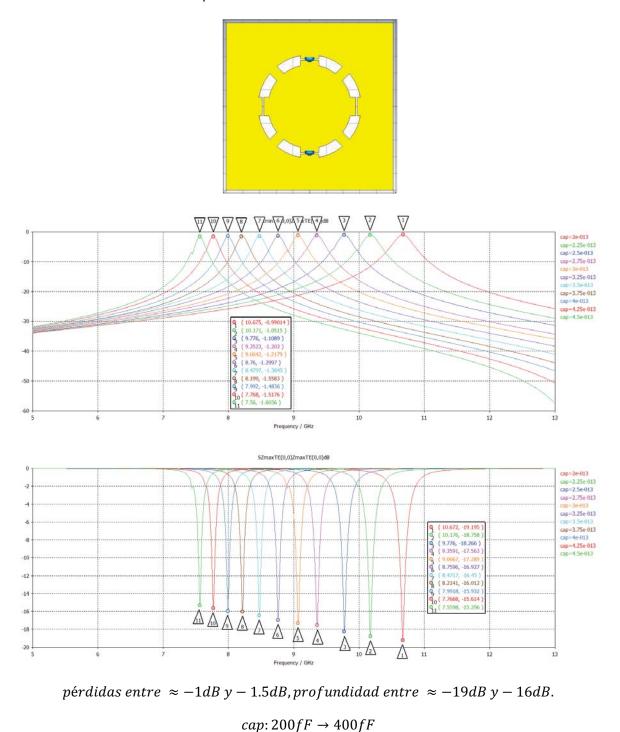

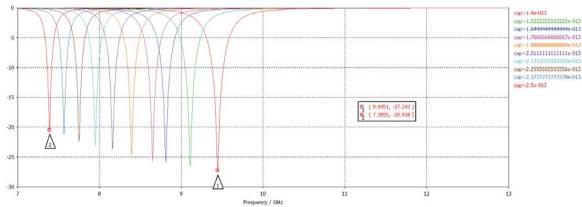

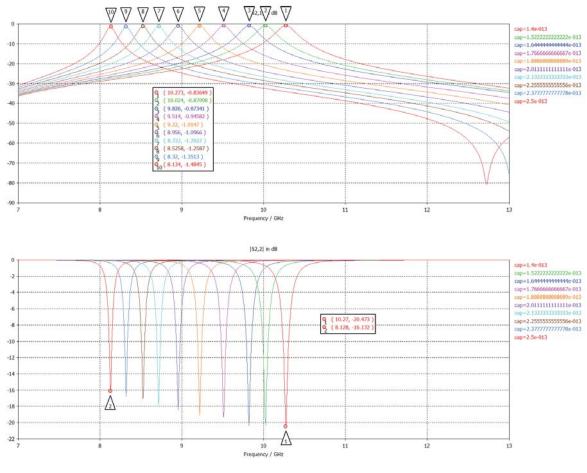

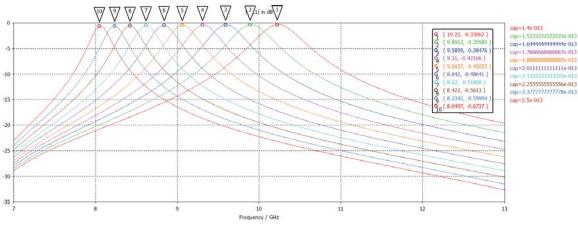

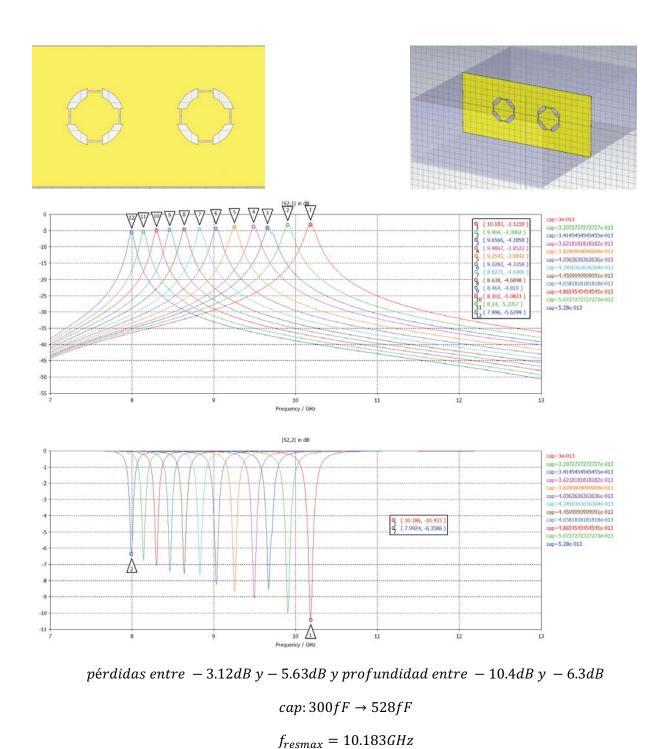

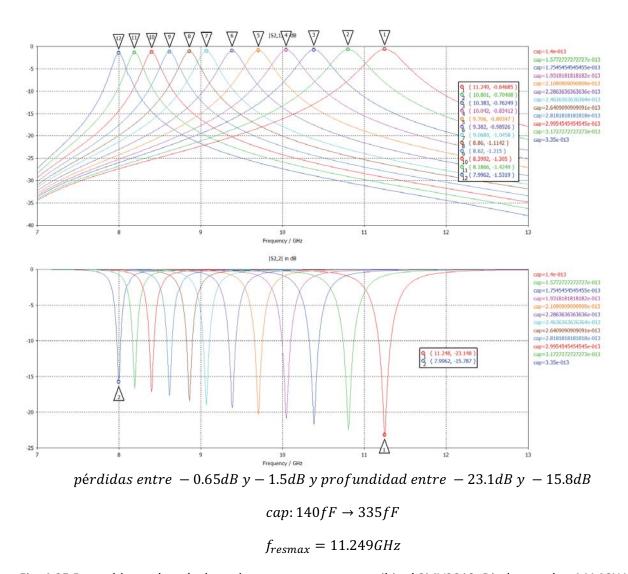

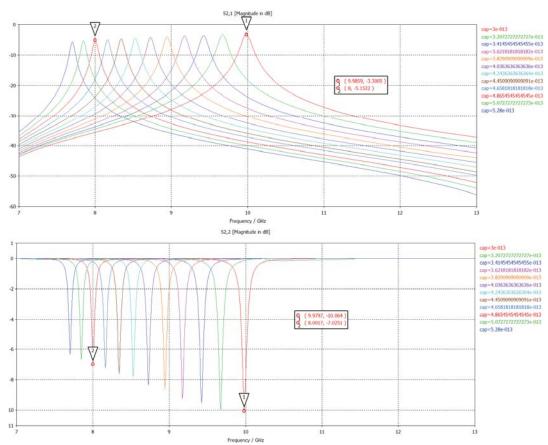

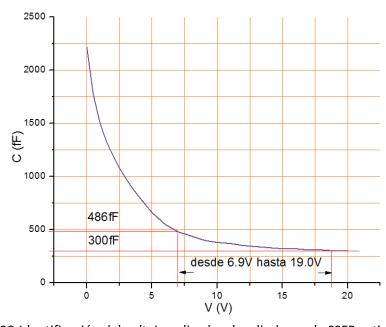

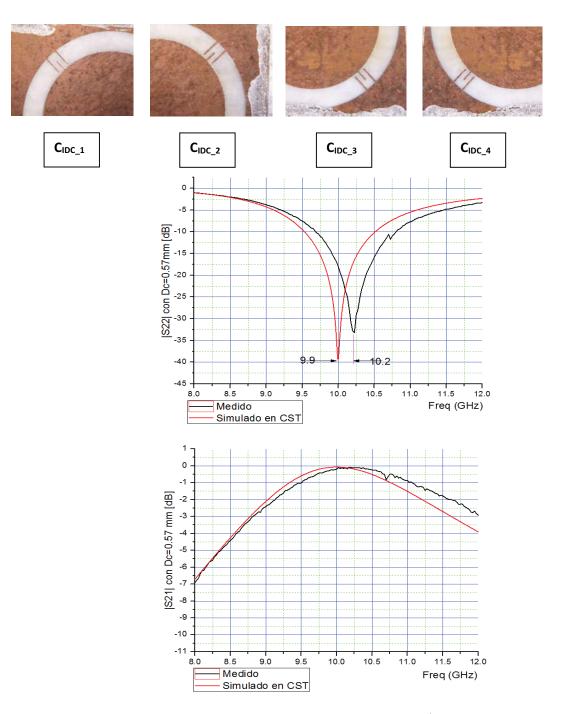

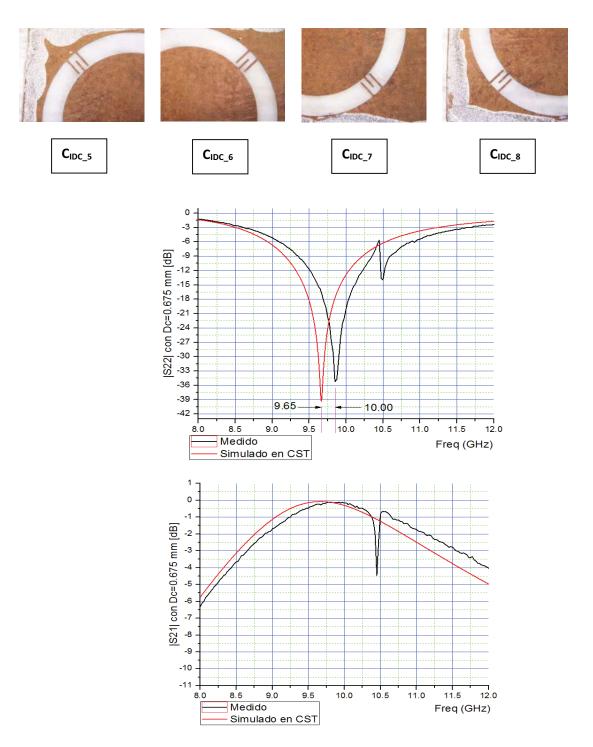

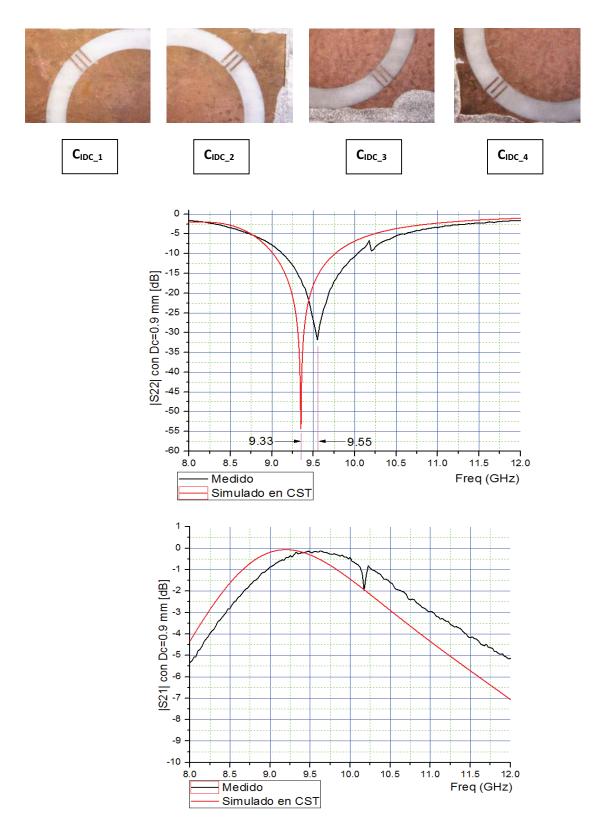

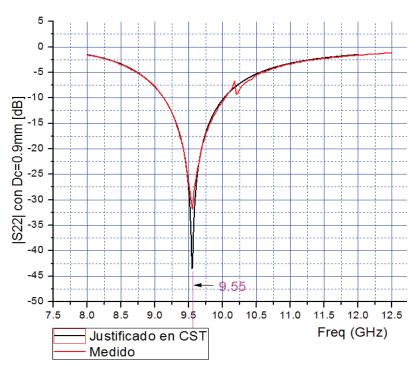

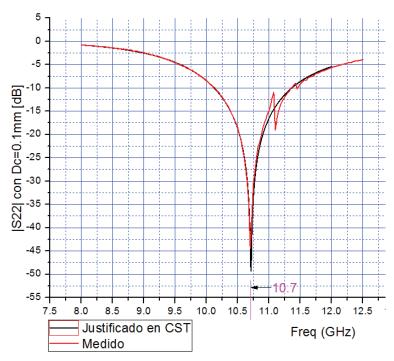

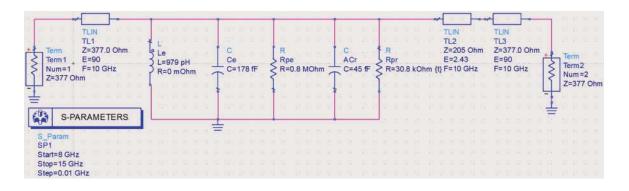

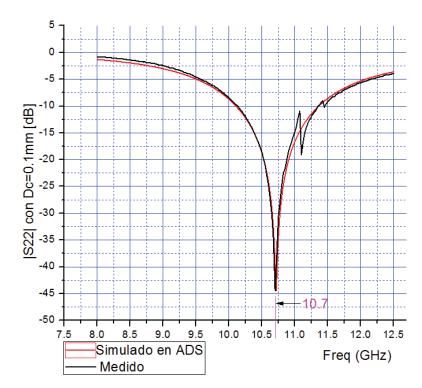

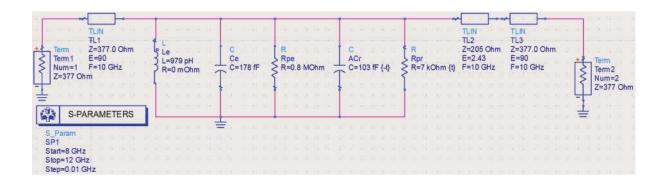

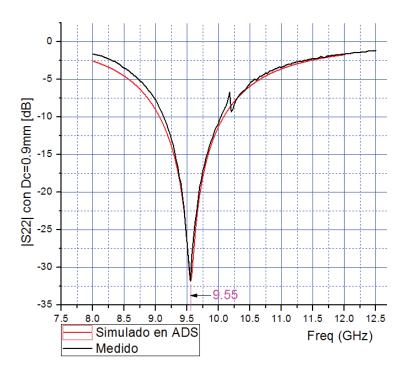

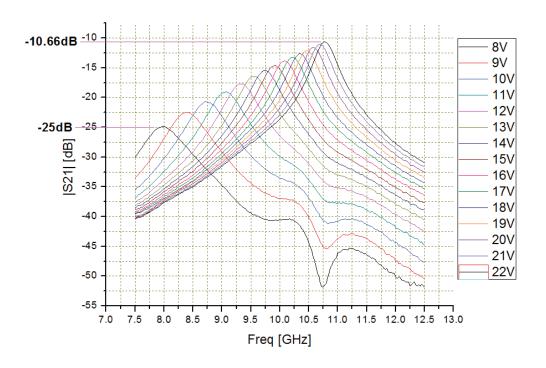

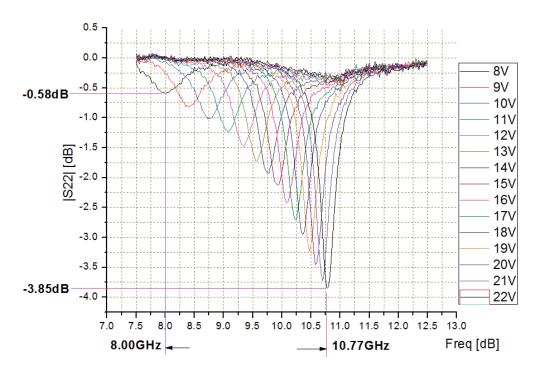

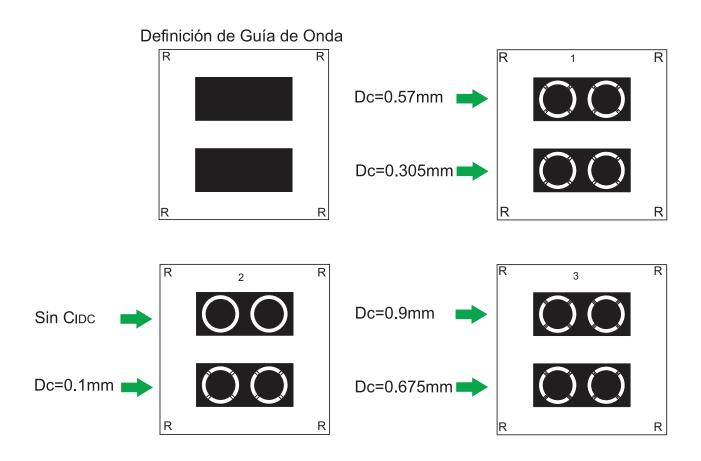

La reconfigurabilidad sobre  $f_{res}$  queda demostrada con un grupo de cinco superficies pasivas, con dos celdas cada una, variando solo la longitud de la placa central de los capacitores interdigitales de 0.1 mm a 0.9 mm, obteniéndose en las mediciones un cambio en frecuencia desde 10.7 GHz con una profundidad o valor mínimo en la magnitud del coeficiente de reflexión de 45 dB, hasta 9.55 GHz con una profundidad de 31.25 dB, respectivamente, con pérdidas en la banda prácticamente despreciables. En cuanto a la SSFR activa con diodos varactores se comprueba con las mediciones que hay una reconfigurabilidad en  $f_{res}$  en la banda X más amplia de 8GHz a 10.77GHz, cambiando al voltaje de polarización de 8V a 22V. Aportando los diodos varactores en la banda un intervalo de pérdidas comprendido entre  $\cong 7dB$   $y \cong 20$ .

Este trabajo es una referencia sobre cómo capacitancias grandes en los dispositivos de control influyen intensamente en las pérdidas al reducir el cociente L/C de la SSFR completa. Futuros trabajos con diodos varactores pueden orientarse hacia más bajas frecuencias, donde en general las pérdidas son más bajas.

# Capítulo 1

# Superficies Selectivas de Frecuencia Reconfigurables (SSFR) con dispositivos activos.

#### 1.1 Antecedentes y revisión del estado del arte.

El número creciente de servicios para las telecomunicaciones ha provocado un incremento en la transmisión de datos, saturando al espectro radioeléctrico, lo cual conduce a que en los sistemas de comunicaciones se implementen técnicas de compatibilidad electromagnética para garantizar su adecuada operación. La compatibilidad electromagnética es la habilidad de un sistema para no causar interferencia a otros equipos e incluso ser insensible a las emisiones que produce el propio sistema.

Un ambiente congestionado de señales electromagnéticas provoca interferencias indeseables y degradación en las características de propagación, por lo que es imperativo que en el lado del receptor los sistemas de antenas cuenten con la habilidad de filtrar espacialmente las señales recibidas. En altas frecuencias dicha habilidad debe de compensar a la dificultad de obtener elementos pasivos de bajas pérdidas, y también permitir el desarrollo de circuitos selectivos con altos factores de calidad.

En el ámbito de las comunicaciones móviles es fundamental prolongar la vida útil de la batería, por lo que el diseño de las antenas está orientado a minimizar las pérdidas por inserción en el modo transmitivo para volver más eficiente la conversión DC – RF, incrementando la eficiencia del sistema [1,2].

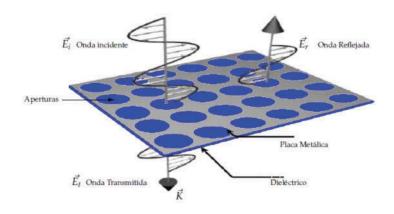

Una superficie selectiva de frecuencia (SSF) es un arreglo bidimensional y periódico. Generalmente formado por elementos tipo parche ( zonas de metal ) sobre un sustrato dieléctrico, o de aperturas ( zonas de dieléctrico ) sobre una pantalla metálica [3]. La topología, periodicidad y características de los materiales determinan su comportamiento resonante, lo cual permite la función de selectividad y de discriminación de frecuencias de la señal electromagnética.

La fig. 1.1 muestra un ejemplo de SSF junto con las ondas electromagnéticas ( OEM ) que puede procesar, dependiendo del diseño puede acentuarse la presencia de una OEM sobre las otras, y modificar sus características como sus ángulos de reflexión o de incidencia y su desplazamiento de fase.

Fig. 1.1 Una SSF tipo parche.

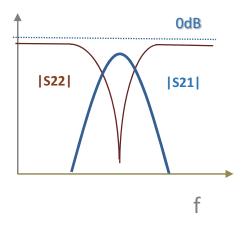

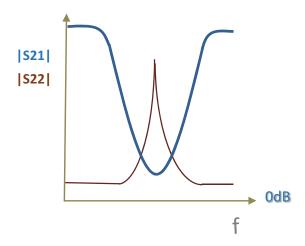

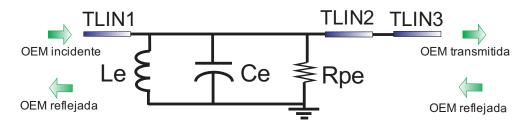

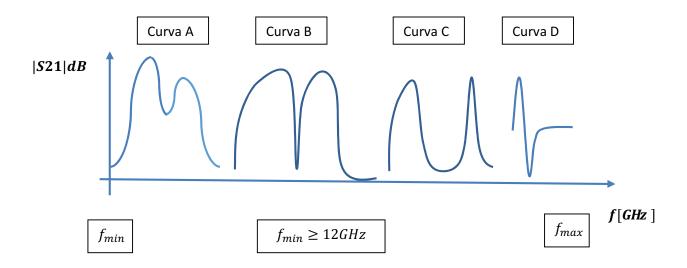

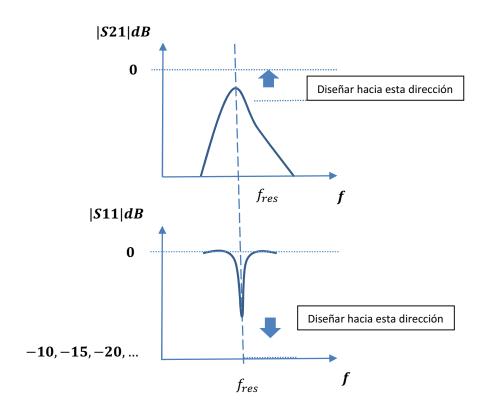

En el caso de una SSF transmitiva, es de interés su coeficiente de transmisión. La estructura es transparente para ondas incidentes con frecuencias en su banda de paso, esto es la SSF responde con valores altos, próximos a uno, en la magnitud de su coeficiente de transmisión |S21|, y valores muy bajos en la magnitud de su coeficiente de reflexión |S22|, mientras que si las ondas incidentes se encuentran en la banda de rechazo, éstas son reflejadas, es decir la SSF responde con valores próximos a uno en el coeficiente de reflexión, y valores muy bajos en el coeficiente transmisión. Un razonamiento inverso se aplica a una SSF del tipo reflectivo. Las figs. 1.3 y 1.4 aclaran esta clasificación para las SSF.

Fig. 1.3 Comportamiento de una SSF transmitiva paso banda o reflectiva rechaza banda.

Fig. 1.4 Comportamiento de una SSF transmitiva rechaza banda o reflectiva paso banda.

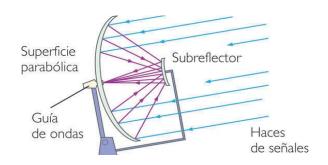

Algunas aplicaciones de las SSF comprenden la interfaz con la antena en radomos [3], estructuras en forma de cúpula que envuelven a radares y antenas para protegerlas de los factores ambientales, y que idealmente son transparentes a las radiaciones que emiten o reciben los elementos que encierran. Se encuentran en aviones, helicópteros, buques, submarinos y en instalaciones terrestres, como en la fig. 1.5. En subreflectores dicroicos [3] que son estructuras empleadas en las antenas para filtrar señales, de acuerdo a su plano de polarización, con frecuencias adentro de la banda de paso de la antena, para después desviarlas hacia una zona de interés. En la fig. 1.6 la SSF ubicada en el subreflector filtra a las señales incidentes para después orientarlas hacia una guía de ondas. Las SSF también se aplican en cuestiones ópticas como en lentes de arreglos transmitivos y reflectivos [3].

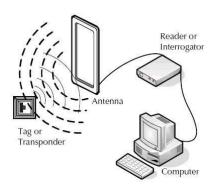

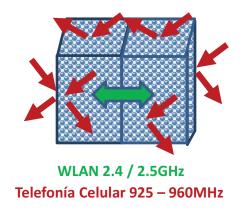

Otros desarrollos comprenden circuitos de etiquetas para la identificación por radiofrecuencia (RFID) ver la fig. 1.7, de uso intensivo en la salvaguarda e identificación de productos en tiendas departamentales, la SSF se encuentra en la etiqueta ( tag ) colocada en el producto. Las SSF también las encontramos en arquitecturas electromagnéticas para aumentar la seguridad en los edificios [18], donde las instalaciones se encuentran forradas con varias SSF. Un ejemplo de esto se ilustra en la fig. 1.8, donde se permite un flujo bidireccional de las señales de la red de área local, entre habitaciones adyacentes, pero se bloquean en ambos sentidos las señales de telefonía celular. Quizá su aplicación común, pero menos conocida, sea en los hornos de microondas [16], ver la fig. 1.9. En esta aplicación las microondas producidas por el magnetrón son reflejadas en todas direcciones por las paredes del horno y absorbidas por los alimentos. Por seguridad del usuario no se permite que atraviesen el vidrio de la puerta, el vidrio contiene empotrada una SSF con una abertura mucho menor que 12 cm, que es la longitud de onda de las microondas a 2.5 GHz, para que de esa manera la SSF bloquee dichas señales y proporcione un blindaje seguro.

Fig. 1.5 Radomo de una instalación terrestre.

Fig. 1.6 Una función de un subreflector.

Fig. 1.7 Sistema de Identificación RFID.

Fig. 1.8 Ejemplo de edificio seguro.

Ancho de malla << 12cm

Fig. 1.9 Blindaje frontal en horno de microondas.

Recientemente [9], las ondas polarizadas circularmente por sus siglas en inglés *CPW*, tienen un vasto campo de aplicación en las comunicaciones satelitales y móviles, en sistemas de navegación global satelitales *GNSS*, sistemas de identificación por radio frecuencia *RFID*, redes inalámbricas de área local y personal *WLAN* y *WPAN*, acceso por microondas a Internet *WiMAX*, servicios directos de radio difusión *DBS*, y en sistemas de recepción de televisión. Es por eso que se han propuesto varios métodos para poder convertir ondas polarizadas linealmente *LPW* a *CPW* en sistemas de antenas de múltiples haces o de apertura compartida. En dichos sistemas de alta ganancia, se requieren polarizadores de banda amplia, y por otra parte las guías de onda circulares son de banda angosta, por lo que se requieren varias estructuras planas para extender el ancho de banda de dichas guías de onda. Estas estructuras pueden construirse a partir de una SSF, que pueda convertir una *LPW* incidente, en una *CPW* transmitida [4]. Por lo tanto, es muy importante la necesidad de obtener SSF activas de alta versatilidad.

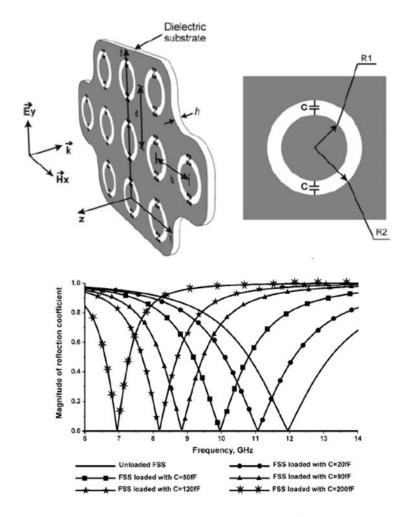

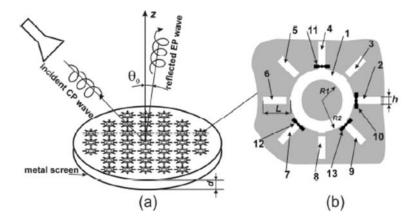

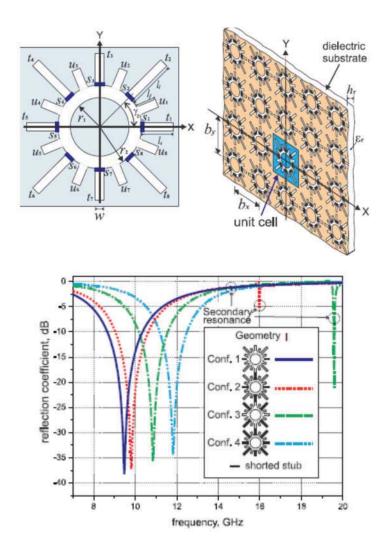

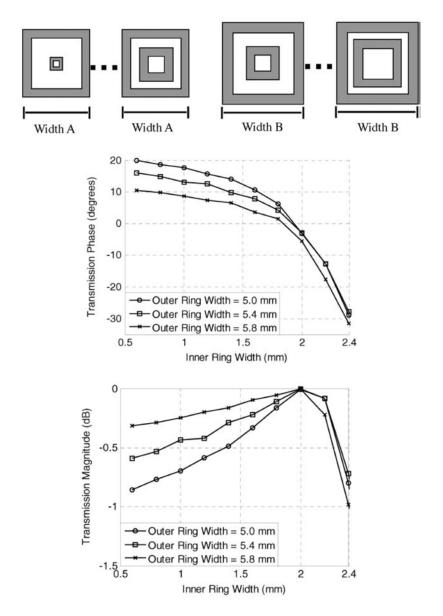

A continuación se comentan algunos desarrollos de las SSF. En la fig. 1.10 se muestra una SSF multicapa capaz de convertir una onda incidente con polarización lineal a un ángulo de inclinación de  $45^{\circ}$ , en una onda transmitiva polarizada circularmente [4]. En vista de que comercialmente no se dispone de capacitores con valores suficientemente bajos de capacitancia, en el orden de varias decenas de femtofarads para realizar corrimientos en la frecuencia resonante, problema que se agudiza en alta frecuencia, en [5] se construyen con la técnica de microfotolitografía capacitores de ese orden para integrarlos a la SSF, y estudiar su comportamiento reflectivo, ver la fig. 1.11. En [6] se utilizan combinaciones de stubs tipo ranura con diodos PIN en una SSF, para lograr cambios en la fase de una onda incidente con polarización circular, ver la fig. 1.12. En [7] se experimenta con stubs del tipo ranurado cargados con diodos PIN, para lograr un mayor número de cambios en la fase en ondas polarizadas circularmente, en este caso ocho combinaciones posibles en el cambio de la fase, dependiendo de cuál diodo PIN se encuentre cerrado, ver la fig. 1.13. Otra propuesta [8] de corrimiento en la frecuencia resonante durante la reflexión, que emplea stubs de longitud variable etiquetados con las letras "u" y "t" y RF MEMS etiquetados con las letras "s" se muestra en la fig. 1.14. El control en la fase obtenido con las geometrías de la SSF en anillo se logra gracias al Principio de Fox, aunque son posibles otras geometrías como las cuadradas en [13], donde se alcanza un comportamiento transmitivo en las celdas, ver la fig. 1.15. Si bien el comportamiento reflectivo de los desarrollos de la fig. 11 y 14 son muy parecidos, los elementos que provocan dicho comportamiento ( elementos reconfiguradores ), y el principio de reconfiguración son diferentes.

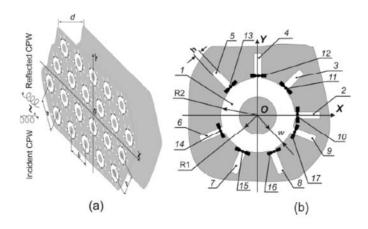

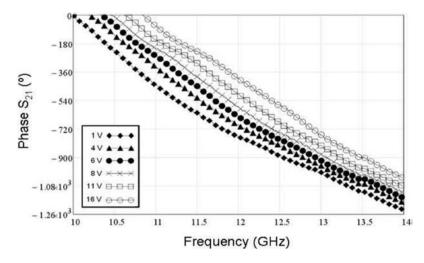

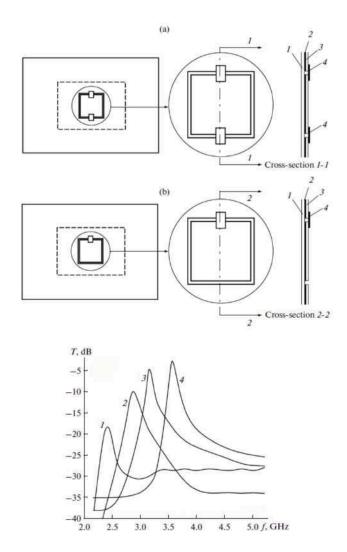

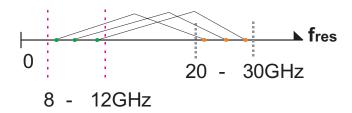

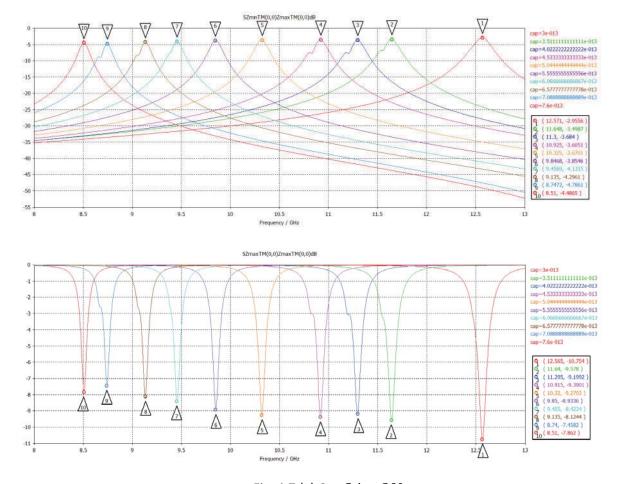

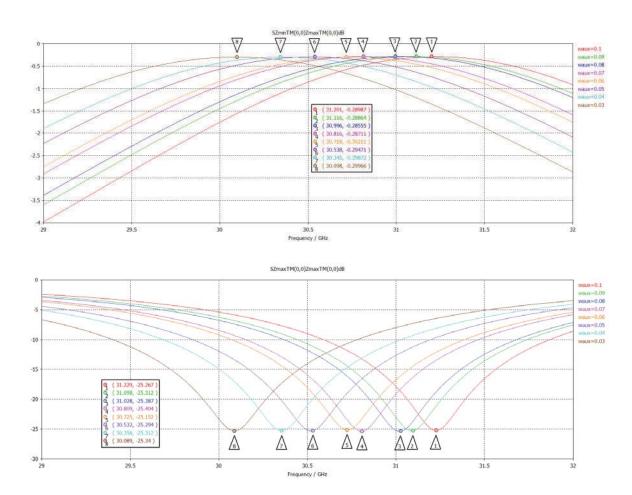

Desarrollos con diodos varactores también son posibles. Por ejemplo en [10] se utiliza un solo diodo varactor operando en conjunto con una estructura electromagnética para cambiar las características de una celda de SSF transmitiva, aunque el número de elementos que componen a la SSF no es adecuado para abaratar el costo en su construcción, ver la fig. 1.16. Los cuadrados verticales rellenos en color naranja son las estructuras tipo parche empleadas para la transmisión y recepción de las señales, la estructura ubicada en posición horizontal, contiene al desplazador de fase para corregir el error en la fase introducida por el cambio de 90° del plano de referencia, y al diodo varactor responsable del desplazamiento en la frecuencia. Los valores más altos en el voltaje de polarización del diodo reducen a la magnitud del coeficiente de transmisión, y reducen el desplazamiento en su fase. En [11] se aborda las posibilidades de obtener una celda reconfigurable de SSF tipo pasobanda, se considera uno o dos diodos varactores, y como

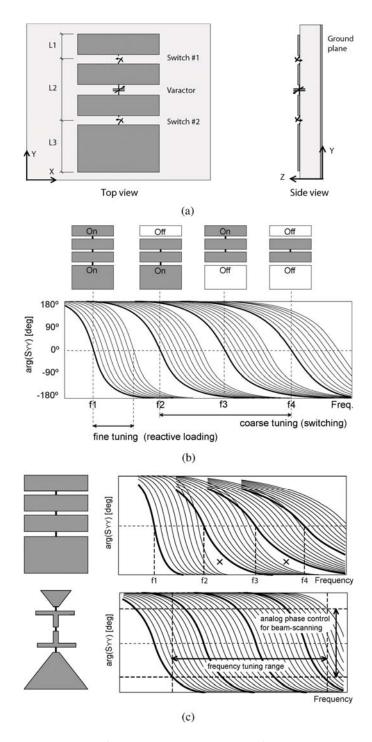

se observa en la fig. 1.17 un valor más alto en el voltaje de polarización, reduce la capacitancia de los dispositivos, y esto disminuye la capacitancia resultante en la celda, por lo que la frecuencia resonante aumenta. El coeficiente de transmisión excursiona a través de valores negativos, debido a las pérdidas asociadas a la resistencia en serie en el modelo de los dispositivos, dichas pérdidas se acentúan al utilizar bajos voltajes de polarización en inversa. En [12] se estudia una SSF reconfigurable para escanear el haz, cada celda emplea dos dispositivos digitales diodos PIN y uno analógico un diodo varactor, ver la fig. 1.18. Las cuatro combinaciones posibles de acuerdo a sus estados abierto o cerrado, que brindan los diodos PIN, conectan o desconectan secciones de la celda, permitiendo mover a la frecuencia resonante en cuatro bandas distintas. El efecto de variar el voltaje de polarización en inversa del diodo varactor permite un ajuste más fino en el ángulo del coeficiente de reflexión del haz, en cada banda de frecuencias. Las secciones de la celda se optimizan para mejorar el factor de calidad.

Fig. 1.10 Polarizador circular multicapa de una SSF de anillo partido bisectado [4].

Fig. 1.11 Una SSF de anillo ranurado cargado con capacitores monolíticamente integrados [5].

Fig. 1.12 Una SSF de anillo ranurado cargado con stubs y diodos PIN que se comporta como arreglo reflectivo del tipo espirafase [6].

Fig. 1.13 Una SSF reflectiva con desplazadores de fase de 3 bits basada en stubs radiales y diodos PIN [7].

Fig. 1.14 Una celda activa de SSF reconfigurable basada en stubs radiales y RF MEMS [8].

Fig. 1.15 Una celda pasiva de SSF transmitiva basada en doble anillo cuadrado [13].

Magnitud del coeficiente de transmisión de acuerdo al valor del voltaje de polarización del diodo varactor.

Ángulo del coeficiente de transmisión de acuerdo al valor del voltaje de polarización del diodo varactor.

Fig. 1.16 Una celda activa de SSF reconfigurable transmitiva basada en puerto bidireccional pasivo y en un diodo varactor [10].

Fig. 1.17 Una celda activa de SSF reconfigurable pasobanda basada en una celda cuadrada ranurada y en uno o dos diodos varactores [11]. Ejemplo de respuestas en el coeficiente de transmisión: las curvas 1, 2, 3 y 4 corresponden a voltajes de control en los varactores de 10, 15, 20 y 29 V, respectivamente.

Fig. 1.18 Una celda activa de SSF reconfigurable para la exploración del haz basada en dos diodos PIN y un diodo varactor por celda [12]. Las formas en "T" y en triángulo se optimizan para mejorar el factor de calidad de la celda completa.

La investigación de las SSF ya mencionada de manera somera ahora se muestra en una tabla, revelando con cierto detalle más sobre las características de los desarrollos tecnológicos. Esta tabla sin ser exhaustiva es una muestra de los avances que han ocurrido en el estado del arte.

| Artículo/año | Función<br>objetivo en el<br>desarrollo:               | Banda de<br>operación<br>[GHz] | Componentes de<br>control en la celda<br>de la SSF:                    | Número<br>de<br>Capas<br>en el<br>arreglo: | Resultados<br>medidos<br>obtenidos:                                                                                                      |

|--------------|--------------------------------------------------------|--------------------------------|------------------------------------------------------------------------|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| [4]/2014     | Conversión de<br>polarización<br>lineal a<br>circular. | 25.5-36.5                      | Exclusivamente<br>con la geometría<br>de la celda y sus<br>materiales. | 4                                          | Con un ángulo de incidencia de hasta 25° se obtienen en la transmisión razones axiales menores que 3dB.                                  |

| [5]/2012     | Pasobanda.                                             | 8.14-11.74                     | Capacitores<br>monolíticamente<br>integrados.                          | 1                                          | Ángulos de incidencia: 33.98° — 53.72° Factor de calidad: 52 — 147 Pérdidas de inserción: -0.85 a -0.15dB.                               |

| [6]/2011     | Supresión de<br>polarización<br>cruzada<br>circular.   | 30                             | 8 stubs ranurados<br>cargados con 3<br>diodos PIN.                     | 1                                          | -8dB con un ángulo de reflexión de $-31.5^{\circ}$ .                                                                                     |

| [7]/2009     | Reflexión de<br>onda<br>polarizada<br>circularmente.   | 18.3-20.5                      | 8 stubs ranurados<br>cargados con 8<br>diodos PIN.                     | 1                                          | Pérdidas de conversión menores<br>que 1.5dB con un ángulo de<br>reflexión hasta<br>38°.                                                  |

| [8]/2012     | Pasobanda.                                             | 9.84-11.80                     | 16 stubs radiales<br>cargados con 8 RF<br>MEMS.                        | 1                                          | Para un coeficiente de reflexión fijo de -10dB se obtuvieron anchos de banda entre 0.9 y 1.44GHz.                                        |

| [13]/2010    | Pasobanda.                                             | 30                             | Exclusivamente<br>con la geometría<br>de la celda y sus<br>materiales. | 4                                          | Ancho de banda de 2.25GHz y eficiencia pico de radiación del 47%.                                                                        |

| [10]/2010    | Desplazador<br>de fase<br>transmitivo.                 | 12                             | Un diodo varactor,<br>celdas y circuito<br>pasivo adicional.           | 4<br>parches.                              | Cambio en la fase hasta 392° con una capacitancia del diodo varactor de 152fF.                                                           |

| [11]/2014    | Pasobanda.                                             | 3-4.75                         | Uno o dos diodos<br>varactores.                                        | 1                                          | Intervalo de sintonización de la frecuencia resonante de 1.4 y 1.5. Magnitud del coeficiente de transmisión entre -30 y -5dB.            |

| [12]/2013    | Ángulo de<br>reflexión.                                | 1.88-3.07                      | Dos diodos PIN y<br>un diodo varactor.                                 | 1                                          | Intervalo de sintonización de la frecuencia resonante de 1 a 2. Profundidad entre -14 y -4 dB. Intervalo de fase análogo mayor que 270°. |

Tabla 1.1. Muestra del estado del arte de las SSF.

#### 1.2 Justificaciones.

Este proyecto de tesis está orientado al desarrollo de una SSF a la que pueda cambiarse su comportamiento para obtener una SSF reconfigurable o SSFR. El interés nace debido a que existe la necesidad de modificar dinámicamente la respuesta de la SSF, lo cual ha llevado a grupos de investigación a nivel mundial a investigar mecanismos de desvío de frecuencia que permitan ajustar los parámetros de la superficie para aplicaciones en tiempo real, dicha capacidad de las SSF con elementos totalmente pasivos [4-5], ha sido ampliada al integrarles dispositivos activos a las celdas del arreglo, para permitir funciones avanzadas de amplificación, multiplicación, corrimiento de fase y escaneo del haz [6-8]. Además el uso de las SSF con capacidades de reconfiguración o SSFR, permite obtener antenas de arreglos de tipo transmitivo para desarrollar funciones avanzadas de alto nivel tecnológico [10-13]. Sin embargo, la principal razón por la cual dicha tecnología no se ha utilizado ampliamente es por su elevado costo de fabricación.

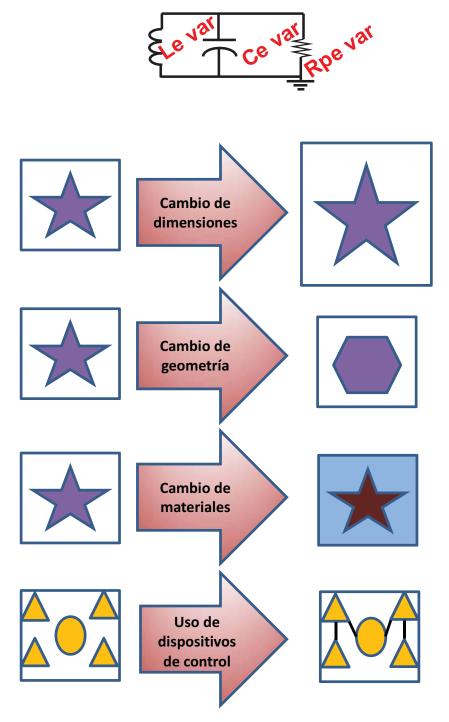

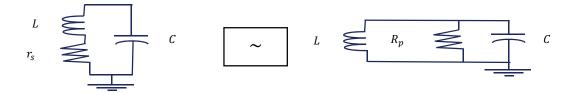

Un análisis minucioso de la tabla 1.1 revela que existen diversos métodos para convertir a una SSF en otra del tipo SSFR, la fig. 1.19 describe gráficamente a dichos métodos. Se asume que las figuras encerradas en los rectángulos son de metal, y que el área que las rodea representa al sustrato dieléctrico. En la columna izquierda se presenta a una celda de la SSF de origen o de referencia, en el centro el cambio impuesto sobre la celda, y en la columna de la derecha la celda resultante de la SSFR. Cada método cambia el valor de algún componente en el circuito resonante de la celda de la SSF, cambiando por completo su comportamiento. Una característica notable que vuelve desafiante al diseño de la SSFR, es que sin importar el método que se elija se afectan los valores de todos los componentes del circuito resonante, lo cual conduce a resultados indeseables cuya eliminación o reducción requiere de múltiples simulaciones. Las pérdidas totales de la celda se representan con el resistor en paralelo, y aunque ahora no sea evidente su valor, está fuertemente ligado a la proporción que guarda su inductancia en relación con su capacitancia. El uso de dispositivos de control como lo sugiere la fig. 1.19, imaginando que se trata de interruptores aunque no está limitado a solo ese tipo, conectan o desconectan secciones de la estructura base, distribuyendo de manera distinta los valores de capacitancia y de inductancia en la celda, incluso los mismos dispositivos contribuyen con sus respectivos valores cambiando al modelo equivalente original de la celda.

En este proyecto de tesis se provocan cambios de capacitancia para obtener una SSFR:

Se obtiene una SSFR pasiva introduciendo en una SSF de referencia un cambio de geometría, y otra SSFR activa mediante el uso de dispositivos de control sobre la superficie de una estructura base.

Fig. 1.19 Métodos de conversión de una SSF a otra SSFR.

Un cambio de geometría puede introducirse cambiando radicalmente la zona de metal, como en la fig. 1.19. Pero el cambio puede ser más sutil, practicando por ejemplo una fisura o corte a dicha zona de metal para descubrir parcialmente al sustrato. Otra forma es insertando una estructura a la ya existente, que contribuya a un mayor cambio de capacitancia sobre la inductancia, o al revés. Identificamos a esta estructura adicional como un elemento reconfigurador pasivo. Un ejemplo de este elemento de construcción simple tanto virtualmente en el simulador como en la estructura base es el capacitor interdigital.

En este proyecto de tesis la SSFR pasiva se basa en el uso de capacitores interdigitales como elementos reconfiguradores.

Los dispositivos de control del tipo interruptor son los más utilizados para obtener una SSFR. Entre estos se utilizan a los diodos PIN y los interruptores *RF MEMS*. No obstante los dispositivos analógicos, brindan una variedad más amplia de posibilidades para cambiar las características de la SSFR, comparadas con un conjunto discreto de posibilidades obtenidas con un dispositivo digital. Dentro de los dispositivos de control analógicos tenemos nuevamente a los *RF MEMS*, transistores y a los diodos varactores.

En general los *RF MEMS* presentan pérdidas muy bajas, bajo consumo de potencia de CD, y su costo de fabricación mediante técnicas fotolitográficas disminuye mucho al considerar un número de celdas alto en la SSF. Los *RF MEMS* ya sea en su versión digital o analógica, como inductor variable o capacitor variable, debido a su naturaleza mecánica son muy dependientes de factores ambientales, tales como la humedad y la temperatura, que pueden alterar su funcionamiento en campo, afectando al acoplamiento con la antena. Un componente de estado sólido tiene una mejor inmunidad a estos factores, que son difíciles de considerar en el desempeño de una SSFR basada en *RF MEMS*. En este sentido la selección de un componente de estado sólido representa una ventaja.

Ahora bien, un transistor dispone de tres capacitancias en su modelo eléctrico equivalente, por lo que es más complejo de predecir el comportamiento de la SSF con el transistor incorporado en su superficie. Un diodo varactor que cambia su capacitancia de acuerdo al valor de un voltaje aplicado, es un dispositivo de dos terminales con una sola capacitancia en su modelo, relativamente fácil de controlar, que puede servir como carga reactiva variable insertada en la estructura de la SSF. Pero un transistor ofrece una versatilidad más amplia, porque aparte de los cambios de fase y en la frecuencia resonante producidos por sus capacitancias, agrega la posibilidad de amplificación. Los diodos varactores o varicap no son tan adecuados como dispositivos de control en SSF reconfigurables, porque requieren para su operación altas corrientes de polarización que introducen altas pérdidas, debidas a la presencia de su resistencia en serie en su modelo eléctrico equivalente. El estado del arte [14] reporta pérdidas para diodos varactores de Arseniuro de Galio (GaAs) de 2.5±1 dB en la banda X, de 4.3±1.2 dB a 17 GHz y de 8.7±2.5 dB a 94 GHz. Aunque esto tampoco es inconveniente ya que dichas pérdidas pueden compensarse con una amplificación en una etapa posterior a la SSF. Así la mancuerna un solo voltaje de polarización – solo dos terminales del diodo varactor resulta en un dispositivo fácil de controlar, a pesar de sus pérdidas.

En este proyecto de tesis la SSFR activa se basa en diodos varactores comerciales ya que su relativa facilidad de control para lograr una variedad de comportamientos en la SSF reconfigurable representa una ventaja.

#### 1.3 Objetivos.

Obtener una SSFR pasiva con capacitores interdigitales y otra SSFR activa con diodos varactores. Ambas del tipo transmitivas pasobanda y sometidas a ondas incidentes normales a la superficie funcionando en la banda X (8GHz – 12GHz). Los diseños están orientados a maximizar el intervalo de reconfigurabilidad en la frecuencia de resonancia, y en minimizar las pérdidas globales de la SSFR.

#### 1.4 Infraestructura.

- Analizador vectorial de redes Agilent a 67 GHz.

- Fuente digital de voltaje de 0 − 30 Vcd y de 0 − 3A.

- Microsoldadora ultrasónica Hybond.

- Software comercial de electromagnetismo computacional.

- Sustratos de microondas, componentes activos y pasivos.

- Guías de onda rectangulares, conectores y adaptadores.

- Equipo de fotolitografía.

# Capítulo 2

# Elementos de análisis y diseño de la configuración básica de la celda para la SSFR.

#### 2.1 Consideraciones preliminares de análisis de la SSFR.

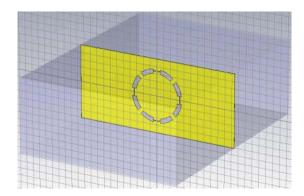

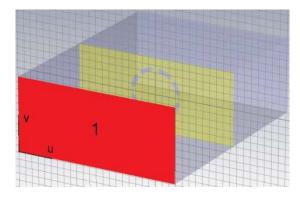

El inicio del análisis de la SSFR completa se reduce a estudiar el comportamiento de una celda unitaria, con la idea de que este comportamiento sea el mismo o muy parecido al que presentará el arreglo completo. Esto es válido debido a que se considera que la superficie selectiva de frecuencia es un arreglo de dimensiones infinitas, es decir que la influencia en el comportamiento electromagnético de una celda particular, debido al resto de las celdas, es el mismo sin importar la posición de dicha celda particular dentro del arreglo. Si la superficie fuera de dimensiones finitas, celdas ubicadas cerca de su borde, con menos celdas vecinas se comportarían de manera muy diferente que las celdas ubicadas más al centro de la superficie, donde el acoplamiento electromagnético con las celdas vecinas es más intenso.

Si bien el elemento de control es un diodo varactor, para investigar el comportamiento de la celda unitaria en cuanto al corrimiento en su frecuencia resonante  $f_{res}$ , en una primera aproximación, se considera emplear elementos capacitivos de \* parámetros concentrados ubicados en una polarización en particular de la onda incidente, la cual se asume que su ángulo de inclinación es normal al plano que contiene a la celda unitaria.

En las simulaciones se ubican capacitores de valores fijos, dentro del intervalo comercial típico de la capacitancia del diodo varactor, en posiciones estratégicas en la superficie de la celda correspondientes a una polarización en particular de la onda incidente, para investigar el comportamiento del corrimiento en el valor de  $f_{res}$  en el modo de operación transmitivo.

<sup>\*</sup>Elemento discreto que sustituye a un sistema real espacialmente distribuido para aproximarse a su comportamiento con el fin de simplificar su análisis, esto es sustituyendo un conjunto de ecuaciones diferenciales parciales de dimensión infinita por un conjunto de ecuaciones ordinarias de dimensión finita.

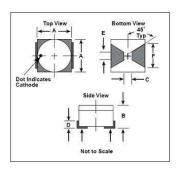

Un diodo varactor de unión hiperabrupta para aplicaciones de microondas es el SMV2019 del fabricante Skyworks, que tiene un intervalo de operación de 2.22pF a  $0V \rightarrow 0.3pF$  a 20V. Otros diodos varactores tienen un intervalo muy semejante, por lo que los capacitores empleados en la investigación del corrimiento en  $f_{res}$ , bien pueden ser de un valor entre 0.3pF y 2.22pF.

#### 2.2 Selección de la geometría de la celda.

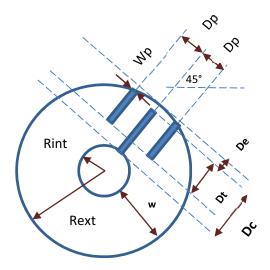

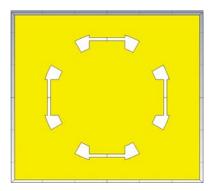

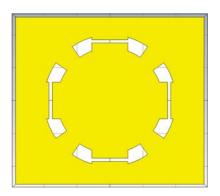

Varios trabajos de investigación como [4-7] han demostrado las bondades de emplear una geometría basada en anillos circulares para las celdas que componen una SSFR, porque debido a su forma circular se acoplan muy bien a ondas polarizadas circularmente. Además dicha geometría ha demostrado su buen funcionamiento al tolerar un intervalo amplio en el ángulo de inclinación de la onda incidente, y tiene un bajo nivel de polarización cruzada. Así que para el diseño de la celda se selecciona una geometría basada en la geometría circular.

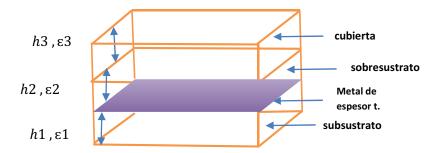

#### 2.3 Dimensiones externas de la celda y sus materiales.

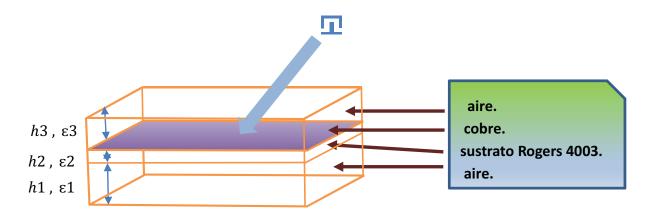

En la banda X, la longitud de onda va de 37.5 mm en 8GHz a 25 mm en 12 GHz. Las dimensiones externas de la celda deben ser tales que sea lo más sensible a las variaciones temporales de la onda electromagnética incidente y también a la posición, lo cual se logra reduciendo el área rectangular que contendrá a la celda, con dimensiones que sean una fracción de la longitud mínima de la onda incidente esperada. Si el ancho de la celda  $w_{cel}$  y su longitud  $l_{cel}$  se seleccionan en menos del 50% de 25 mm se logra una buena sensibilidad a la onda incidente. Es decir la celda como un circuito resonante de parámetros distribuidos, reacciona bien ante las variaciones temporales y posicionales de las ondas incidentes ya que sus dimensiones son menores que la longitud mínima de onda esperada. Este es un conocimiento práctico adquirido en el área de RF y microondas. Así que en las primeras simulaciones bajo este criterio se elige  $w_{cel}=l_{cel}=10\ mm$  . Para el soporte de la lámina de cobre se selecciona al sustrato dieléctrico cerámico RO4003C del fabricante Rogers, por sus bajas pérdidas en un intervalo amplio de microondas, sus parámetros son permitividad relativa  $\varepsilon_r=3.55$  , tangente de pérdidas  $\delta=0.0027$  y conductividad térmica de 0.64 W/m/°K, con un espesor de  $T_{sust}=127 \mu m$ . La lámina de cobre depositada en el sustrato tiene un espesor de  $T_{cobre}=17\mu m$  . Las dimensiones  $T_{sust}$  y  $T_{cobre}$  se consideran constantes durante las simulaciones, debido a que el sustrato RO4003C es el que está disponible para este proyecto.

#### 2.4 Software disponible para el proyecto.

Las simulaciones de las estructuras electromagnéticas se realizan con el software de Tecnología de Simulación en Computadora, sección de microondas ( *CST MWS* ). Las características empleadas para este proyecto son:

- Resolvedor numérico de frecuencia basado en el método de cálculo de Diferencias Finitas en el Dominio del Tiempo ( *FDTD* ).

- Mallado basado en tetraedros recomendado para alta frecuencia.

- > Las condiciones de frontera y los puertos de la estructura son definidas por el usuario.

- ➤ Contiene el algoritmo Delta S para analizar la convergencia de las simulaciones.

- Capacidad de simular estructuras con elementos concentrados adicionales.

En las simulaciones de los modelos eléctricos equivalentes se utiliza el software Advanced Design System ( *ADS* ), y en programas de apoyo para la construcción en *CST* y comprensión del comportamiento de las estructuras se utiliza código de otras fuentes.

#### 2.5 Modelo eléctrico básico equivalente de la celda.

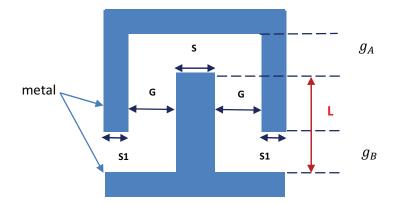

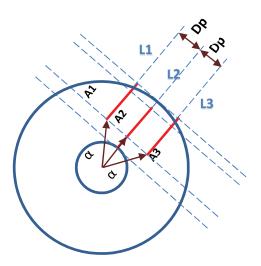

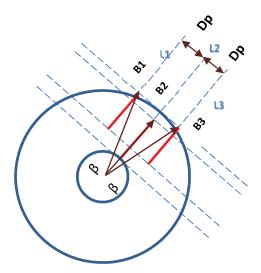

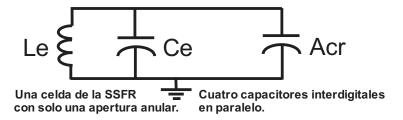

Varios trabajos de investigación [4] – [7] están basados en el modelo básico electrodinámico que permite predecir en forma aproximada el comportamiento para una celda con apertura anular, que es la configuración más simple en la geometría basada en anillos, por lo que será la primera configuración abordada en las simulaciones. Estrictamente, el análisis de la celda involucra elementos de parámetros distribuidos, que requieren métodos numéricos computacionales electromagnéticos de onda completa de elevada complejidad de cálculo. Sin embargo, un modelo eléctrico equivalente de parámetros concentrados, aunque sea aproximado, es muy útil para que el ingeniero pueda explicar en términos físicos, los cambios en los resultados entre simulaciones. Para el desarrollo del circuito eléctrico equivalente resonante se utilizan las figs. 2.1 y 2.2. Se define al plano de polarización de una onda electromagnética (OEM) como el plano que contiene a las direcciones del vector campo eléctrico, y no al vector campo magnético, porque instrumentos comerciales para medir a las OEM reaccionan a las fuerzas eléctricas que ejercen las ondas sobre los electrones de los materiales.

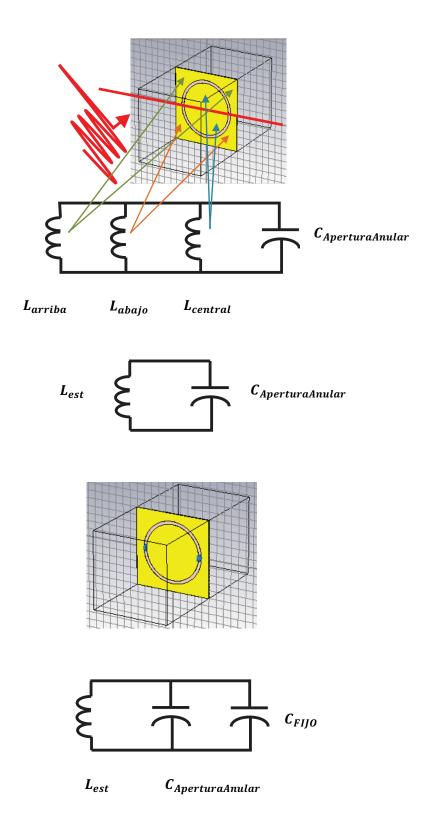

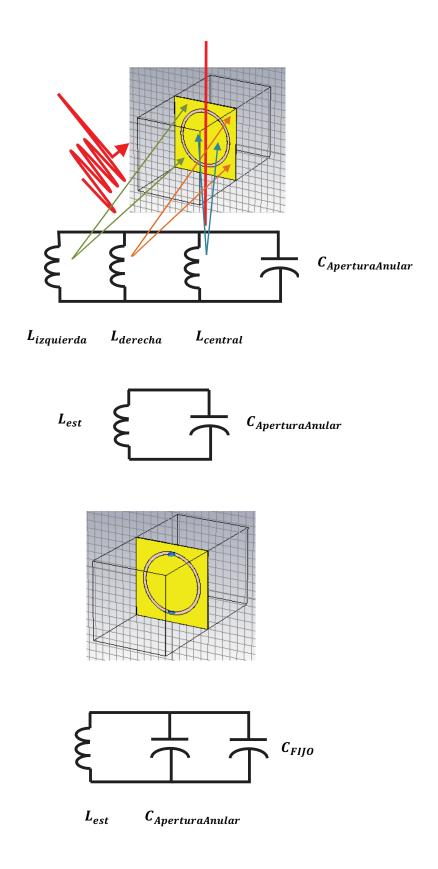

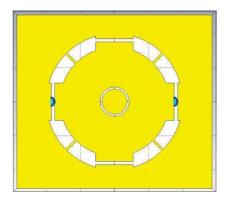

En la fig. 2.1 se muestra a una celda excitada con una OEM incidente con polarización horizontal, tanto la OEM como la línea que identifica al tipo de polarización aparecen en color rojo, dicha línea coincide con el eje de simetría horizontal de la estructura. La zona de metal se muestra en color amarillo, y la zona del dieléctrico en color gris. Nótese que el dieléctrico se encuentra distribuido en un anillo, a dicha distribución del dieléctrico se le conoce como apertura anular porque es por esa zona por donde la OEM puede atravesar con menos dificultad a la celda. Puesto que la apertura anular está rodeada por metal, eléctricamente se comporta como un capacitor de valor  $C_{AperturaAnular}$ . En la celda se identifican a tres zonas de metal: La que se encuentra arriba de la línea de la polarización, la que está debajo de la misma, y la que está en la zona central circular. Como la energía magnética almacenada se debe a la circulación de las corrientes inducidas por la OEM en la superficie del metal, cada zona está relacionada con un valor de inductancia. El metal arriba del eje de simetría horizontal de la estructura tiene una inductancia  $L_{arriba}$ . similarmente hay otra debajo de dicho eje  $L_{abajo}$ , y la zona central de metal contribuye con una  $L_{central}$ . La inductancia total de la estructura  $L_{est}$  es la combinación en paralelo de las tres inductancias anteriores. Es decir  $1/L_{est} = 1/L_{arriba} + 1/L_{abajo} + 1/L_{central}$ . Como la apertura anular consiste de un dieléctrico separada por zonas de metal el campo eléctrico se intensifica en la apertura, introduciendo una capacitancia  $C_{AperturaAnular}$  en paralelo con  $L_{est}$  en el modelo.

Fig. 2.1 Desarrollo del modelo eléctrico equivalente en parámetros concentrados aproximado de la celda unitaria en la polarización horizontal.

Fig. 2.2 Desarrollo del modelo eléctrico equivalente en parámetros concentrados aproximado de la celda unitaria en la polarización vertical.

En general, la ecuación básica de la frecuencia resonante para el circuito en paralelo L-C es:

$$f_{res} = \frac{1}{2\pi\sqrt{LC}}$$

--- (2.1)

Es posible evaluar de manera aproximada  $C_{AperturaAnular}$  y después a  $L_{est}$ , para ello se insertan pares de capacitores de valores iguales conocidos en las posiciones horizontales, identificados en la fig. 2.1 por pequeñas estructuras en color azul. La inserción de estas capacitancias externas que tiene asociado un valor combinado denotado como  $C_{FIJO}$ , es para investigar el efecto de la polarización de la onda incidente horizontal en el comportamiento resonante de la estructura completa. Ahora se encuentran los valores de la frecuencia resonante empleando el software CST. Como ejemplo numérico de este método, supongamos que para ciertas dimensiones de la celda con una sola apertura anular el software CST produce:

Para  $C_{FIJO1} = 0.015pF$  (ambos capacitores con 30fF en serie) hay una  $f_{res1} = 11.571GHz$  --- (2.2)

Para

$$C_{FIJO2}=0.22pF$$

(  $ambos\ capacitores\ con\ 440fF\ en\ serie$  ) hay una  $f_{res2}=11.397GHz$  --- (2.3)

Para comprobar los valores que se calcularán de  $L_{est}$  y de  $C_{AperturaAnular}$ , se inserta un tercer par de capacitancias, y CST en este caso produce:

Para

$$C_{FIJO3}=62.5fF$$

(  $ambos\ capacitores\ con\ 125fF\ en\ serie$  ) hay una  $f_{res3}=11.429GHz$  --- (2.4)

La ecuación (2.1) adaptada a la celda incluyendo al capacitor equivalente propuesto externo en paralelo con la apertura anular resulta en:

$$f_{res} = \frac{1}{2\pi \sqrt{L_{est}(C_{AperturaAnular} + C_{FIJO})}} --- (2.5)$$

Sustituyendo los datos de capacitancia - frecuencia de (2.2) y (2.3) en la ecuación (2.4), y resolviendo las dos ecuaciones resultantes se obtiene:

$$C_{Apertura Anular} = 6.6479 pF$$

;  $L_{est} = 28.395 pH --- (2.6)$

Se comprueban los valores obtenidos (2.6) sustituyéndolos en (2.5), así como el de  $C_{FIJO3}=62.5fF$  y debe producirse admitiendo cierto error, el valor calculado por el software que es de  $f_{res3}=11.429GHz$  según la prueba de simulación (2.4).

$f_{res3} = 11.530 GHz$  según (2.5) con un error de (11.429 - 11.530)/11.429x100 = -0.8837% inferior al 1% lo cual es aceptable.

Es común que en esta geometría con una sola apertura de dieléctrico que como el área del metal en la zona central es mayor que el área del metal circundante,  $L_{central} \ll (L_{arriba} \ en \ paralelo \ con \ L_{abajo})$  y como en la conexión en paralelo la inductancia resultante es menor que la inductancia individual más

pequeña, entonces  $L_{est} < L_{central}$  , es decir la OEM percibe de manera aproximada un valor menor que la inductancia existente en la zona de metal central.

Un análisis similar puede aplicarse para obtener el modelo eléctrico equivalente para la polarización vertical empleando la fig. 2.2  $L_{central} \ll (L_{izquierda} \ en \ paralelo \ con \ L_{derecha})$ , y en este caso la OEM percibe de manera aproximada a una inductancia  $L_{est} < L_{central}$ . Entonces si el área central de metal es más grande que el área externa circundante, la inductancia del área central influye más en el valor de  $f_{res}$ . De hecho debido a la simetría circular, las aportaciones a la inductancia y capacitancia en el circuito eléctrico equivalente son las mismas en las figs. 2.1 y 2.2, por lo tanto sin importar cuál polarización se utilice para la onda incidente en el software CST, el método anterior debe producir los mismos valores para  $C_{AperturaAnular}$  y  $L_{est}$ . Si se agrega más de una apertura anular de dieléctrico a la celda, lo cual necesariamente agrega más anillos de metal concéntricos, crece la complejidad del modelo eléctrico equivalente presentado en las figs. 2.1 y 2.2, ya que los pares adicionales  $C_{AperturaAnular} - L_{MetalCircundante}$  agregan más puntos de resonancia.

En los modelos de las figs. 2.1 y 2.2 se han despreciado las pérdidas en el metal por efecto Joule debido a la circulación de las corrientes inducidas en el metal, aunque la resistencia del metal asociada a dichas pérdidas debe considerarse en el factor de calidad Q del circuito.

En general, el factor de calidad Q de la celda está dado por:

$$Q = 2\pi f_{res} RC --- (2.7)$$

Donde C representa a la capacitancia de la apertura, una o varias que contenga la celda, y R es la resistencia en la placa y representa a sus pérdidas. El factor Q controla qué tan rápido cambia la impedancia de la celda en torno a  $f_{res}$ . También Q tiene una interpretación en términos de la energía, es  $2\pi$  veces la energía almacenada en los elementos reactivos en la resonancia dividida entre la energía disipada en un ciclo [18].

La geometría y las propiedades electromagnéticas de los materiales como son la permitividad y la conductividad influyen sobre los valores de R, L y C involucrados en las ecs. (2.1) y (2.7).

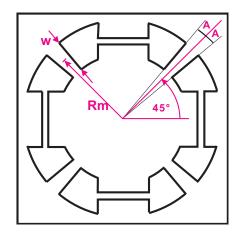

En el modelo básico electrodinámico para una celda con apertura anular, la relación aproximada que existe entre la longitud de onda resonante  $\lambda_r$  y el radio medio de la apertura anular  $r_m$  está dada por:

$$\lambda_r = 2\pi r_m - - (2.8)$$

Donde:

$$r_m = \frac{r_{ext} + r_{int}}{2}$$

--- (2.9)

Siendo  $r_{ext}$  el radio exterior de la apertura y  $r_{int}$  su radio interior,  $r_m$  es la distancia radial desde el centro de la celda hasta justo la mitad del ancho de la apertura anular. Además  $\lambda_r$  y su frecuencia respectiva  $f_{res}$  están conectadas con la velocidad de la luz  $3x10^8 \, m/_S$  como sigue:

$$\lambda_r = \frac{3x10^8}{f_{res}}$$

--- (2.10)

Sustituyendo (3.8) en (3.10) y despejando la frecuencia resonante aproximada en Hz:

$$f_{res} = \frac{3x10^8}{2\pi r_m} --- (2.11)$$

Asumiendo constantes a las dimensiones externas de la celda en todas las simulaciones, un cambio en las dimensiones de la apertura anular, producido por variar el radio interior de la apertura  $r_{int}$  y/o por variar su radio exterior  $r_{ext}$ , cambia no solo a la zona del dieléctrico en la apertura, afectando a la capacitancia, la cual a su vez cambia al factor de calidad dado por (2.7), sino también estos cambios dimensionales cambian a la zona de metal alrededor de la apertura, y en consecuencia la inductancia también cambia. Como puede concluirse, cambios en los parámetros dimensionales provocan cambios en los parámetros eléctricos, y para poder predecir la dirección del cambio durante las simulaciones, son útiles tener siempre en mente las siguientes observaciones:

Cualquier cambio dimensional en la celda que provoque un aumento en la zona de metal reduce a la inductancia. Si la zona de metal se reduce la inductancia aumenta.

Concepto físico: En una mayor área de metal la onda incidente induce un mayor número de cargas eléctricas, por lo que éstas se oponen menos a cualquier cambio en la corriente inducida, esto es la inductancia se reduce, y a la inversa.

Cualquier cambio dimensional en la celda que provoque un aumento en la zona del dieléctrico reduce a la capacitancia. Si la zona del dieléctrico se reduce la capacitancia aumenta.

Concepto físico: En una mayor separación entre las zonas de metal la onda incidente induce una menor cantidad de carga en el dieléctrico, por lo que se reduce el campo eléctrico que producen y también se reduce la capacitancia, y a la inversa.

2.6 Alta del proyecto para las simulaciones, identificación de los parámetros de dispersión y utilización de elementos concentrados en las simulaciones.

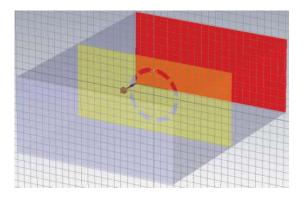

Al dar de alta el proyecto por primera vez en el software CST se debe definir como una plantilla tipo  $FSS-Unit\ Cell\ (FD)$ , para habilitar todas las características de la superficie periódica infinita, aunque las simulaciones del usuario corresponden a las de una celda unitaria. El puerto de microondas para la simulación se define desde la opción  $Solve \gg Background\ Material$  dando para  $Z_{min}\ y\ Z_{max}$  el valor de 10 mm, el cual es suficiente para contener a una celda de dimensiones externas de  $w_{cel}=l_{cel}=10\ mm$  ( tal como se definió en la sección 2.3 ). El material del medio en el que está inmersa la celda debe ser aire.

En la opción Solver >> Boundary Conditions ( condiciones de frontera ) el software podría asumir por defecto un componente tangencial del campo eléctrico igual a cero en todas las direcciones, esto es que la frontera se establece con un medio metálico, donde el campo eléctrico solo puede ser normal a la estructura. Puesto que la estructura se encuentra inmersa en un dieléctrico, en este caso aire, las condiciones de frontera deben cambiarse al estado de abierto (open). Con esta misma opción se comprueba que las condiciones de frontera no invadan a la región de celdas adyacentes en la superficie completa.

En  $Ports\gg Z_{min}\ y\ Z_{max}$  se aprecian los planos del puerto delantero y trasero de la celda, respectivamente. La propiedad para cada plano es la asignación por defecto de dos modos Floquet. El teorema de modos Floquet es una extensión del teorema de series de Fourier en el espacio, y describe matemáticamente al campo electromagnético. Al ordeñar los resultados de la simulación de una corrida con  $1D\ Results\gg S-Parameters$  aparecen ocho curvas de los parámetros de dispersión correspondientes para cada modo Floquet, etiquetadas como:

SZmin(1), Zmax(1) SZmin(2), Zmax(1) SZmax(1), Zmax(1) SZmax(2), Zmax(1) SZmin(1), Zmax(2) SZmin(2), Zmax(2) SZmax(1), Zmax(2) SZmax(2), Zmax(2)

Los números 1 y 2 repetidos entre paréntesis que se presentan en la notación de los parámetros de dispersión, se refieren a uno de los dos modos Floquet posibles asociados a un parámetro de dispersión específico, y los números 1 y 2 diferentes entre paréntesis corresponden a la interacción entre los dos modos Floquet, en un parámetro de dispersión. Las etiquetas de min y max en dichos parámetros se refieren a los coeficientes de transmisión en directa o en inversa  $S_{21}$  ó  $S_{12}$  que aparecen en la literatura de Radio Frecuencia y Microondas, las etiquetas  $\max y$  max corresponden a los coeficientes de reflexión en la entrada o en la salida, conocidos como  $S_{11}$  ó  $S_{22}$ . Excluyendo a los parámetros S que involucran el cruzamiento en los modos Floquet, los parámetros de interés en las simulaciones se reducen a:

SZmin(1), Zmax(1) SZmax(1), Zmax(1) SZmin(2), Zmax(2)SZmax(2), Zmax(2)

Dada la polarización de la onda incidente, aún falta determinar cuál de las gráficas de SZmin(1), Zmax(1) ó SZmin(2), Zmax(2) corresponden al parámetro de transmisión correcto, y cuál de las gráficas de SZmax(1), Zmax(1) ó SZmax(2), Zmax(2) corresponden al parámetro de reflexión correcto. Ambos parámetros válidos para la polarización dada. El método detallado de la identificación correcta de dichos parámetros se abordará en el ejemplo de simulación en CST de la siguiente sección 2.7.

Puesto que el dispositivo de control que se insertará en la celda de la SSF es un diodo varactor, se introduce un cambio en la capacitancia en el modelo electrodinámico de la celda, de acuerdo al valor de su voltaje de polarización en inversa. Aunque también puede introducir un cambio en la inductancia, lo cual enriquece aún más el comportamiento a estudiar de la celda, pues se tiene la opción de conectar secciones de metal por una reactancia capacitiva o inductiva . Veamos por qué es posible cargar a la celda con una u otra reactancia en las simulaciones. Al definir en el software CST al dispositivo de control como un elemento de parámetros concentrados (Lumped Elements) lo cual es válido ya que las dimensiones del diodo varactor son mucho menores que la longitud de onda de una señal en la banda X que pase por este, CST puede tratarlo en general como un elemento tipo RLCParallel, o como diodo normal con la opción Diode , entonces es posible simular al diodo varactor no solo como una capacitancia variable  $C_{var}$  , también como si en un circuito físico el diodo varactor se polarizara en directa, sustituyéndose por un cortocircuito en cierta posición sobre la apertura anular. Estrictamente, este cortocircuito tiene cierta respuesta en frecuencia como una inductancia  $L_{var}$ . Como se mencionó en la sección 2.1 al diodo varactor se simulará como una capacitancia concentrada variable, que se define en CST como del tipo RLCParallel con valores de cero en los campos R y L , y un valor distinto de cero en Farads en el campo C . Un valor de R igual a cero se interpreta en CST como un valor infinitamente grande de resistencia en paralelo.

# 2.7 Estrategias de análisis y diseño para obtener el corrimiento máximo en la frecuencia de resonancia adentro de la banda X, utilizando el intervalo de capacitancia comercial del varactor.

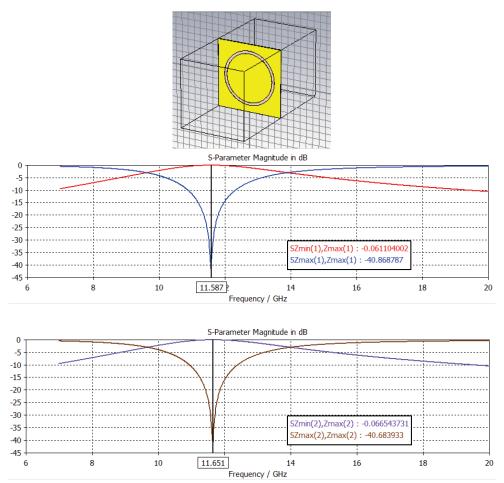

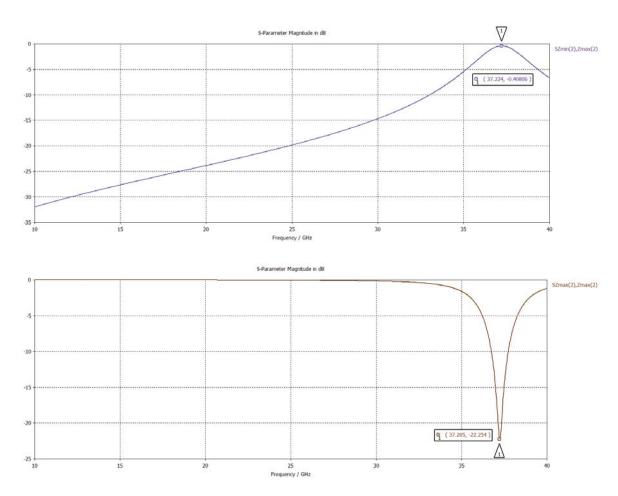

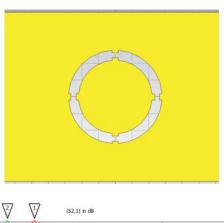

En principio se obtiene una geometría de la celda con una solo apertura circular de dieléctrico, cuyo comportamiento resonante debido solo a su naturaleza intrínseca esto es sin capacitores externos, se ubique en la banda X, como se muestra en la fig. 2.3. Como se observa la celda opera en modo transmitivo, ya que en la frecuencia resonante,  $|S_{21}|$  en dB que en la notación de CST es SZmin, Zmax es lo menos negativa posible (lo más alta posible), por debajo de la línea de 0 dB, y que en la misma frecuencia resonante,  $|S_{11}|$  en dB que en la notación de CST es SZmax, Zmax sea lo más negativa posible (lo más baja posible), por debajo de la línea de 0 dB. Es decir en  $f_{res}$  el carácter transmitivo de la celda es mucho más intenso que su carácter reflectivo. En ambos modos Floquet de los parámetros S el valor obtenido de prácticamente el mismo 11.587 vs 11.651 GHz. Es decir las SZmin(1), Zmax(1) y SZmin(2), Zmax(2) son coincidentes entre sí en todos sus puntos, no solo en el punto en que ocurre  $f_{res}$ , lo mismo que las gráficas de SZmax(1), Zmax(1) y SZmax(2), Zmax(2), esto es así porque debido a la simetría circular de la celda, la OEM que incide con polarización horizontal, sobre el eje de simetría horizontal de la celda, encuentra la misma cantidad y la misma forma de zonas de metal y dieléctrico, que la OEM que incide con polarización vertical, sobre el eje de simetría vertical de la celda, por lo tanto en ambas polarizaciones el comportamiento electromagnético es prácticamente el mismo. Si este comportamiento afuera diferente, esto es que al comparar entre sí los pares de curvas anteriores, se encuentran separadas al variar la frecuencia, no sigue la naturaleza física descrita, por lo que CST debe de calibrarse para esa geometría en particular, esto es aumentar su resolución de  $1x10^{-4}$  , valor por default en la caja de diálogo  $Frequency\ Domain\ Solver\ Parameters$  , a digamos  $1x10^{-5}$  , aunque están disponibles otros valores como  $1x10^{-9}$  ó  $1x10^{-12}$ , pero las simulaciones correrían mucho más lentas en los primeros análisis, antes de observar una tendencia de corrimiento interesante. Adicionalmente a este cambio, debe de refinarse el mallado con elementos tetrahedros, forma recomendable para alta

frecuencia, ya que permite aproximar detalles circulares en la geometría, o detalles de dimensiones muy pequeñas. El refinamiento de la malla se logra variando el número de pasos por longitud de onda,  $Steps\ per\ wavelength$ , y el número mínimo de pasos,  $Min.\ number\ steps$  ambos se encuentran en la ruta  $Global\ mesh\ properties\gg Mesh\ density\ control$ , cuidando que el valor del primero sea menor al del segundo. Valores comunes pero no exclusivos para estructuras electromagnéticas circulares son  $4,10\ y\ 7,13$ . Un refinamiento adicional consiste en cambiar las dimensiones de las aristas de los tetraedros, para que se amolden mejor en distancias cortas en los detalles de la estructura completa en  $Local\ Mesh\ Properties$ , cambiando el valor de  $Maximum\ mesh\ step\ width$ . Algunos valores comunes son  $1,0.8,0.5\ y\ 0.3$ . En la práctica se logra un mallado adecuado cuando cambios adicionales en los parámetros de los valores anteriores, no mueven sustancialmente a las curvas de dispersión, en particular en el punto en que ocurre la frecuencia resonante.

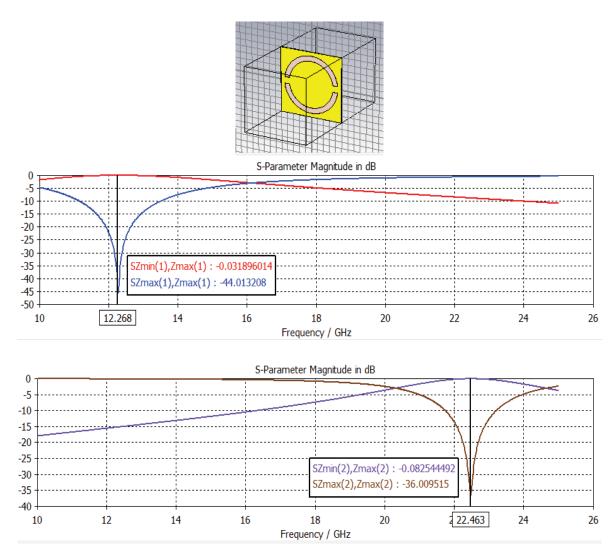

Surge la duda ¿Cuáles gráficas de la magnitud de los parámetros S en la fig. 2.3 corresponden a la polarización horizontal, y cuáles a la polarización vertical?. La respuesta es el método de identificación de parámetros prometido en la sección 2.6 anterior, y que aquí se presenta: Se rompe la simetría en el funcionamiento de la celda, agregando elementos que afecten a una polarización, pero no a la otra. Al par de curvas SZmin, Zmax y SZmax, Zmax que sí cambien corresponden a la polarización que fue afectada. Los elementos de ruptura de simetría pueden ser un par de capacitores colocados sobre la apertura anular, aunque se prefiere elementos más simples todavía como un par de corto circuitos, como en la fig. 2.4 donde se agregaron en la celda de la fig. 2.3, secciones de metal que afectan a la polarización horizontal longitud de  $r_{int}$  – 0.1mm a  $r_{ext}$  + 0.1mm en el eje x y ancho de – dimensiones 0.5mm~a~0.5mm~en~el~eje~y . Comparando las gráficas de la figs. 2.3 y 2.4, la  $f_{res}$  de Zmin(1), Zmax(1) y SZmax(1), Zmax(1) cambia un poco en cerca de 0.6 GHz, mientras que la  $f_{res}$  de Zmin(2), Zmax(2), y SZmax(2), Zmax(2) prácticamente se duplica, entonces se concluye que para la configuración de la fig. 3.3, las curvas de Zmin(2), Zmax(2) y SZmax(2), Zmax(2) corresponden a la polarización horizontal, y las curvas de Zmin(1), Zmax(1) y SZmax(1), Zmax(1) son las asociadas para la polarización vertical.

Esta conclusión es de vital importancia para identificar los gráficos resultantes en las simulaciones, y se explica como sigue:

Al no haber corto circuitos en el eje de simetría vertical, la OEM incidente con la polarización vertical experimenta muy poco cambio porque casi ve los mismos valores de inductancia y capacitancia. Los corto circuitos en el eje de simetría horizontal, parten casi por igual a la apertura anular de dieléctrico, por lo que la

OEM incidente con la polarización horizontal, cuya frecuencia es casi el doble que en la polarización horizontal sin los corto circuitos, solo es la que puede pasar por la mitad de la apertura seccionada. Entonces es de esperarse que el valor de  $f_{res}$  para la polarización horizontal actual cambie a un valor cercano al doble del que presenta la polarización horizontal sin la afectación anterior.

Mientras más angostos sean los corto circuitos agregados, habrá menos metal agregado en la polarización vertical, y por consiguiente será menor la reducción del dieléctrico, entonces el valor de  $f_{res}$  en la polarización vertical prácticamente no cambiará, y su valor en la polarización horizontal fuertemente afectada prácticamente se duplicará.

Fig. 2.3 Configuración A para lograr tener comportamiento resonante adentro de la banda X (8 – 12 GHz)  $w_{cel}=10~mm, lcel=10mm, r_{ext}=4mm, \ r_{int}=3.6~mm.$

Fig. 2.4 Modificación a la configuración A de la fig. 2.3 necesaria para la identificación de las curvas de los parámetros S de una polarización en particular de la onda incidente en dicha configuración.

Para lograr la mayor variación posible en  $f_{res}$  al agregar un par de capacitores, que afecten a una polarización en particular, digamos solo a la polarización horizontal en la celda con la configuración de la fig. 2.3, ambos con el mismo valor adentro del intervalo comercial típico de 0.3pF a 2.22pF, y colocados en el eje de simetría horizontal de la celda ( aunque puede ser el eje vertical ), se proponen las siguientes estrategias:

#### Estrategia 1:

Dimensionar la celda para que su  $f_{res}$  sin capacitores se ubique cerca del centro de la banda X, y al agregar un par de capacitores con  $0.3pF \le f_{res} \le 2.22pF$ , o en un intervalo menor, se desplacen los valores de  $f_{res}$ . dentro de la banda X.

#### Estrategia 2:

Dimensionar la celda para que su  $f_{res}$  sin capacitores se ubique arriba de la banda X, y al agregar un par de capacitores con  $0.3pF \leq f_{res} \leq 2.22pF$ , o en un intervalo menor, se desplacen los valores de  $f_{res}$ . adentro de la banda X.

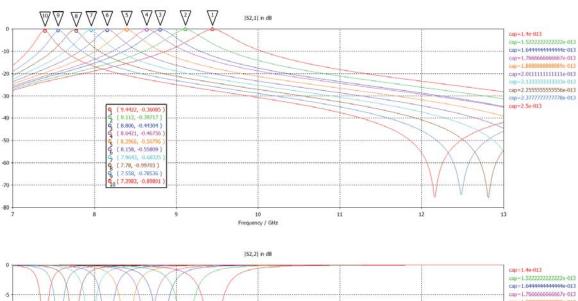

Como se menciona en estas estrategias, probablemente se logre la reconfigurabilidad en el corrimiento de la frecuencia resonante dentro de la banda X, no necesariamente en todo el intervalo comercial de capacitancia del diodo varactor, sino más bien en un sub intervalo, esto sería deseable, ya que como lo demuestran diversos trabajos de investigación con diodos varactores empleados en SSFR como en [11], bajos voltajes de polarización tienen asociados pérdidas más altas en los varactores, lo cual impacta en las pérdidas globales de la SSFR, y por el contrario altos voltajes de polarización producen menores pérdidas. Puesto que la capacitancia del varactor varía en forma inversa al voltaje de polarización ( no en forma proporcional, más bien en forma no lineal ), entonces conviene que el intervalo de capacitancia para lograr la reconfigurabilidad, se encuentre más recargado hacia el valor de 0.3pF que al de 2.22pF. Aunque en general, el diodo varactor tiene pérdidas de 2.5dB o más como se menciona en [11], [12] y [14].

Aplicando la estrategia 1 de análisis y diseño a la configuración A de la fig. 2.3. Se desea acercar más a  $f_{res}=11.651GHz$  de la misma fig. 2.3 al centro de la banda X que es 10GHz. Para lograrlo se mantiene la misma zona de metal alrededor de la apertura anular de dieléctrico, es decir se considera a  $r_{ext}=4.0mm=constante$  , y se aumenta a  $r_{int}$  partiendo del valor de la configuración A de 3.6mm , con lo cual se reduce el ancho de la apertura anular  $w_{AA}=r_{ext}-r_{int}$  , aumentando la capacitancia de la celda, lo que favorece la disminución en  $f_{res}$  . Sin embargo, dicho cambio también aumenta a la zona de metal en el centro de la celda, lo cual reduce la inductancia lo que favorece al efecto opuesto, un aumento en  $f_{res}$  . Recordando de la sección 2.5:

$$L_{est} < L_{central}$$

Esperamos que solo el cambio en la capacitancia sea el más importante para lograr reducir a  $f_{res}$ . Los resultados se condensan en la tabla 2.1 y revelan que el cambio en la capacitancia fue el importante, por lo que se confirma la disminución en  $f_{res}$ .

Tener una  $f_{res} \sin Cvar$  lo más centrada en banda X no es útil como podría pensarse, para asegurar que  $f_{res}$  a 0.3pF caiga adentro de la banda X, lo cual motivó la formulación de la estrategia 1 de análisis, en esta sección 2.7. Se ha encontrado que el valor de Cvarmin = 0.3pF es demasiado grande para conseguir la reconfigurabilidad. Es más ubicar a  $f_{res} \sin Cvar$  en el tope de la banda que es 12GHz no es suficiente, como lo sugiere la misma tabla 2.1,  $f_{res} \sin Cvar$  debe estar aún más arriba del tope. Este hecho motiva la formulación de la estrategia 2 de análisis.

| Celda: | r <sub>ext</sub><br>[m<br>m] | $r_{int}$ [mm] | <i>W<sub>AA</sub></i> [mm] | $f_{res} \sin Cvar$ [GHz] | f <sub>res</sub> a 0.3pF<br>[GHz] | Modo de<br>Operación: |

|--------|------------------------------|----------------|----------------------------|---------------------------|-----------------------------------|-----------------------|

|        | 111]                         |                |                            |                           |                                   |                       |

| A.1    | 4.0                          | 3.60           | 0.40                       | 11.6510                   | 5.9456                            | Transmitivo           |

| A.2    | 4.0                          | 3.70           | 0.30                       | 10.8830                   | 6.0907                            | Transmitivo           |

| A.3    | 4.0                          | 3.80           | 0.20                       | 10.3280                   | 6.3084                            | Transmitivo           |

| A.4    | 4.0                          | 3.85           | 0.15                       | 9.9422                    | 6.4444                            | Transmitivo           |

| A.5    | 4.0                          | 3.90           | 0.10                       | 9.6644                    | 6.6259                            | Transmitivo           |

| A.6    | 4.0                          | 3.95           | 0.05                       | 9.1995                    | 6.9887                            | Transmitivo           |

Tabla 2.1 Resumen del comportamiento de la configuración A de la fig. 2.3, buscando la variación de  $f_{res}$  adentro de la banda X aplicando la estrategia 1 de análisis.

La estrategia 1 de análisis y diseño no resultó útil porque la celda transmitiva sin capacitores resonando en la banda X es muy sensible a varias centenas de femtofarads, valor de capacitancia mínima en el que se encuentra un diodo varactor típico, pues al colocar el capacitor resuena a una frecuencia por abajo del límite inferior de la banda X .

Aplicando la estrategia 2 de análisis y diseño en la configuración A. Se desea ahora modificar las dimensiones de la celda, para obtener inicialmente sin capacitores, una frecuencia resonante por encima de la banda X, esto es  $f_{res} > 10 GHz$ . En la tabla 2.2 se muestran las iteraciones realizadas cambiando el radio interno y el radio externo de la apertura anular, pero conservando su ancho en todas las iteraciones. Valores cada vez más bajos de  $r_{int}$  y  $r_{ext}$  reducen el perímetro de la apertura anular, dichos valores se seleccionan para mantener el mismo ancho  $W_{AA} = r_{ext} - r_{int} = 0.1 mm$ , el resultado es que la capacitancia de la apertura se conserva relativamente constante. El radio medio va reduciéndose en cada iteración de arriba a abajo de la tabla 3.2, y en consecuencia según (2.11)  $f_{res} \sin Cvar$  debe de aumentar, por lo que  $f_{res} \sin Cvar$  inexorablemente abandonará la banda X. Nótese que al colocar ahora Cvarmin = 0.3pF la nueva  $f_{res}$  comienza a entrar en la banda X.

| Celda: | $r_{ext}$ | $r_{int}$ | $W_{AA}$ | f <sub>res</sub> sin Cvar | f <sub>res</sub> a 0.3pF | Modo de     |

|--------|-----------|-----------|----------|---------------------------|--------------------------|-------------|

|        | [mm]      | [mm]      | [mm]     | [GHz]                     | [GHz]                    | Operación:  |

| A.7    | 3.1       | 3.0       | 0.1      | 12.959                    | 7.8776                   | Transmitivo |

| A.8    | 3.0       | 2.9       | 0.1      | 13.367                    | 7.9365                   | Transmitivo |

| A.9    | 2.9       | 2.8       | 0.1      | 13.895                    | 8.0703                   | Transmitivo |

| A.10   | 2.8       | 2.7       | 0.1      | 14.376                    | 8.2993                   | Transmitivo |

| A.11   | 2.6       | 2.5       | 0.1      | 15.628                    | 8.5283                   | Transmitivo |

| A.12   | 2.4       | 2.3       | 0.1      | 17.000                    | 8.8730                   | Transmitivo |

| A.13   | 2.3       | 2.2       | 0.1      | 17.587                    | 9.0930                   | Transmitivo |

| A.14   | 2.0       | 1.9       | 0.1      | 20.111                    | 9.8360                   | Transmitivo |

| A.15   | 1.9       | 1.8       | 0.1      | 21.230                    | 9.8397                   | Transmitivo |

Tabla 2.2 Resumen del comportamiento de la configuración A de la fig. 2.3, buscando la variación de  $f_{res}$  adentro de la banda X aplicando la estrategia 2 de análisis.

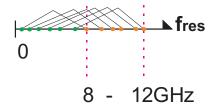

La fig. 2.5 resume las conclusiones de aplicar las anteriores estrategias de análisis y diseño, la estrategia 2 es la que finalmente se aplicará en los capítulos 3 y 4 que tratan del análisis y diseño de la SSFR pasiva y de la SSFR activa, respectivamente. Como se demostrará, para la SSFR pasiva las capacitancias agregadas son más pequeñas que las del diodo varactor en la SSFR activa, por lo que la necesidad de ubicar desde el principio a la  $f_{res}$  de la SSFR sin capacitores adicionales muy encima de la banda X es mayor en la SSFR activa que en la pasiva.

A) Estrategia 1. Se descartará.

- B) Estrategia 2. Se aplicará.

- estado de la SSF sin capacitores.

- estado de la SSF con Cmin=300fF.

Fig. 2.5 Conclusiones de las estrategias propuestas de análisis y diseño.

#### 2.8 Problemática en el criterio de convergencia en las simulaciones.

Durante las simulaciones se observa que existen ciertos conjuntos de dimensiones reducidas, en las que es imposible con un  $Cvar \ge 0.3~pF$  externo, lograr que  $f_{res}$  varíe adentro de la banda X. Dicho comportamiento se resume discutiendo los siguientes resultados de las simulaciones:

Con las dimensiones  $r_{int} = 1.825 \, r_{ext} = 1.875 \, W_{AA} = 0.050 \, r_{med} = 1.850 \, \text{todas en } mm$  .

$$f_{res}|_{\sin Cvar} = 20.461 \, GHz \, y \, f_{res}|_{Cvar=0.3pF} = 11.168 \, GHz$$

Con dichas dimensiones se logró colocar a  $f_{res}$  lo suficientemente fuera de la banda X, para que al insertar el capacitor, resulte una  $f_{res}$  próxima al límite superior de la banda X de 12~GHz. Para lograr una aproximación más cercana a 12~GHz debe reducirse ligeramente a la capacitancia de la estructura sin incorporar el capacitor, lo cual aumentará ligeramente a  $f_{res}$  en un valor por encima de 20.461~GHz. La reducción en la capacitancia se logra aumentando ligeramente al ancho de la apertura anular  $W_{AA}$ , lo cual se consigue aumentando levemente a  $r_{ext}$  en la misma cantidad en la que se reduce a  $r_{int}$ , con tal de mantener el valor de  $r_m = (r_{int} + r_{ext})/2$  para no afectar en exceso al valor de  $f_{res}$ , ya que se relacionan según (2.11) como  $f_{res} = 2\pi/r_m$ . Una vez aumentado a  $f_{res}$  se inserta el capacitor y entonces se esperaría que  $f_{res}$  se coloque en un valor mayor que 11.168~GHz más próximo a 12~GHz.

Con las dimensiones  $r_{int}=1.775~r_{ext}=1.925~W_{AA}=0.150~r_{med}=1.850~{\rm todas~en}~mm$  .

$$f_{res}|_{\sin Cvar} = 21.009 \text{ GHz y } f_{res}|_{Cvar=0.3pF} = 9.696 \text{ GHz}$$

El valor obtenido de  $9.696\,GHz$  desafía a la lógica anteriormente planteada,  $f_{res}$  tiende a abandonar la banda X, en vez de pegarse a  $12\,GHz$  .

La guía tutorial de CST en lo que se refiere al manejo de elementos concentrados, no menciona alguna explicación para este comportamiento extraño. Revisando otro software de simulación electromagnético como EMPro del fabricante Agilent Technologies, se menciona en la ruta *Managing Projects* » *Ports and Sensor Setup* » *Adding Circuit Components*, que si bien un elemento concentrado pasivo no irradia energía, puede introducir puntos de baja impedancia en la estructura, desplazando a la corriente de los elementos finitos próximos. La corriente que pasa por dichos elementos es igual a la permitividad eléctrica multiplicada por el volumen del elemento. Al exigir una resolución mayor a la malla, los volúmenes respectivos se reducen, la corriente por los elementos es menor, el elemento concentrado actúa como un sumidero de corriente, desviando la corriente de los elementos finitos vecinos, al resolver las ecuaciones de Maxwell asociadas, los resultados son matemáticamente correctos, pero sin significado físico. Así pues EMPro reconoce el problema que puede ocurrir en las simulaciones, pero no brinda alguna función que avise de dicha anomalía, la responsabilidad de admitir o no la validez del resultado, es responsabilidad del usuario.

#### 2.9 Alternativas para remediar la problemática.

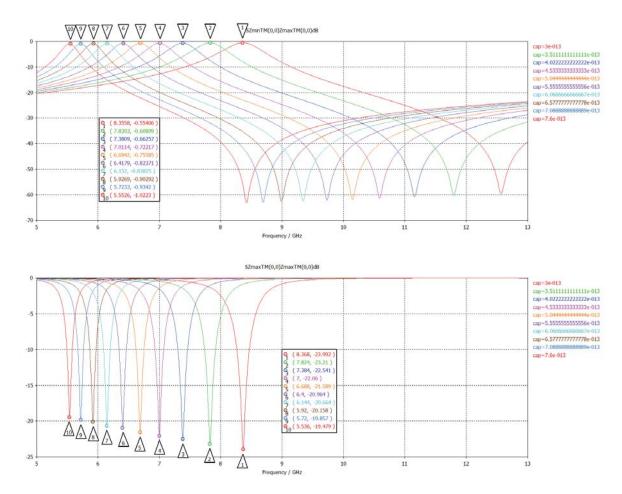

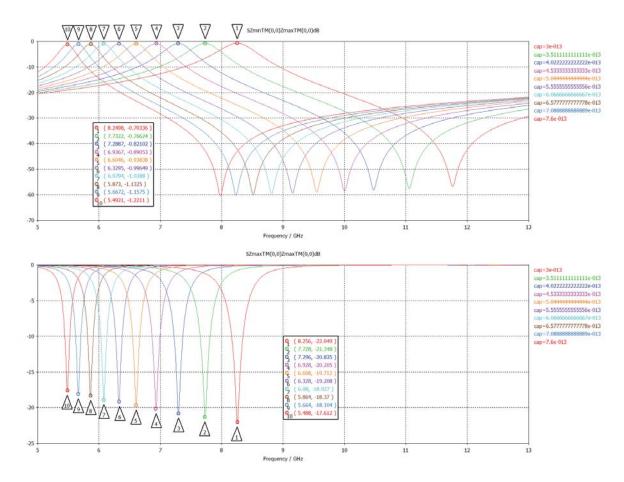

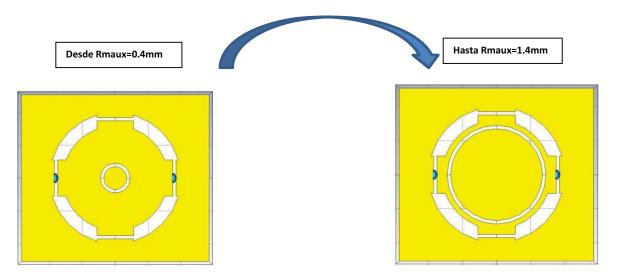

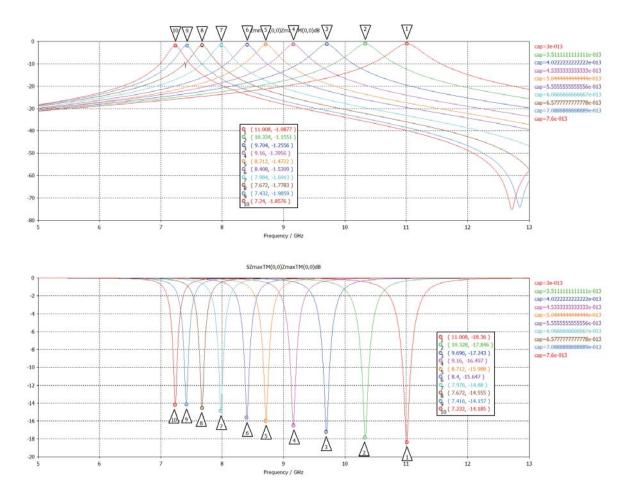

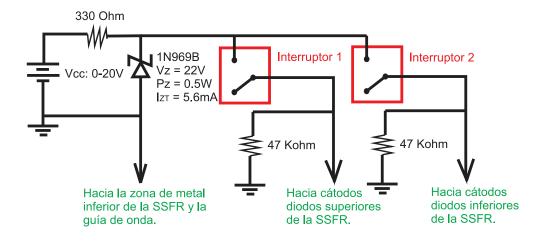

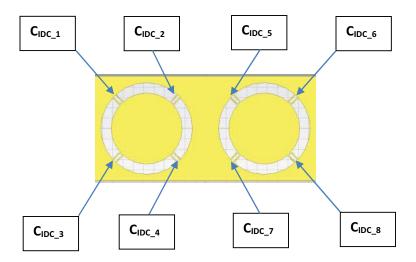

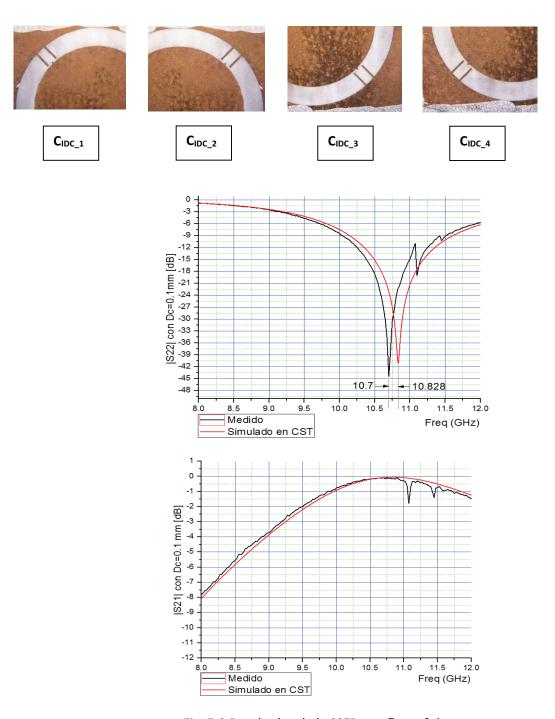

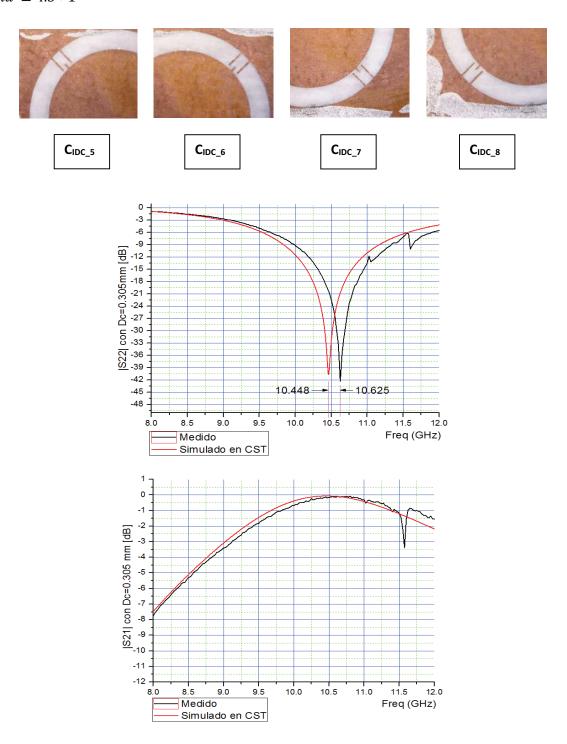

Revisar las condiciones de frontera ( boundary conditions ). Si están definidas con un componente tangencial del campo eléctrico igual a cero en todas las direcciones, significa que el software asume que la frontera se establece con un medio metálico, donde el campo eléctrico solo puede ser normal a la estructura. Puesto que la estructura se encuentra inmersa en un dieléctrico, en este caso aire, las condiciones de frontera deben cambiarse al estado de abierto (open).