# UNIVERSIDAD NACIONAL AUTONOMA DE MEXICO

# FACULTAD DE ESTUDIOS SUPERIORES CUAUTITLAN

"CAPTURA DE EVENTOS PARA UN

TURBOGENERADOR DE300 MW DEL SISTEMA

CSCCT (CONTROL SUPERVISORIO CICLO

COMBINADO TULA) CON

MICROCONTROLADORES"

T E S I S

INGENIERO MECANICO ELECTRICISTA

PRESENTA

**HECTOR**

BECERRA

HERNANDEZ

**ASESOR: ING. JORGE BUENDIA GOMEZ**

CUAUTITLAN IZCALLI, EDO. DE MEX.

1997

TESIS CON FALLA DE ORIGEN

UNAM – Dirección General de Bibliotecas Tesis Digitales Restricciones de uso

## DERECHOS RESERVADOS © PROHIBIDA SU REPRODUCCIÓN TOTAL O PARCIAL

Todo el material contenido en esta tesis esta protegido por la Ley Federal del Derecho de Autor (LFDA) de los Estados Unidos Mexicanos (México).

El uso de imágenes, fragmentos de videos, y demás material que sea objeto de protección de los derechos de autor, será exclusivamente para fines educativos e informativos y deberá citar la fuente donde la obtuvo mencionando el autor o autores. Cualquier uso distinto como el lucro, reproducción, edición o modificación, será perseguido y sancionado por el respectivo titular de los Derechos de Autor.

# FACULTAD DE ESTUDIOS SUPERIORES CUAUTITLAN UNIDAD DE LA ADMINISTRACION ESCOLAR DEPARTAMENTO DE EXAMENES PROFESSIONALES

ASUNTO: VOTOS APROBATORIOS

VNIVEMEAL NACIONAL AVÊNIMA DE MEXICO

> DR. JAIME KELLER TORRES DIRECTOR DE LA FES-CUAUTITLAN PRESENTE.

> > AT'N: Ing. Rafael Rodriguez Ceballos Jafe del Departamento de Examenes Frofesionales de la F.E.S. - C.

| permitimos comun                                                                                                     | rt. 28 del Regjamento General de Examenes. nos<br>icar a usted que revisamos la TESIS:                            |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| "Captura de Eventos para un Turbogenerador de 300Mw del<br>Sistema CSCCT (Control Supermisorio Ciclo Combinado Tula) |                                                                                                                   |  |  |  |  |  |

| con Microcontroladores".                                                                                             |                                                                                                                   |  |  |  |  |  |

| que prasenta <u>el</u>                                                                                               | pasante: Hector Becerra Hernandez                                                                                 |  |  |  |  |  |

|                                                                                                                      | enta: <u>8501085-3</u> para cotener el TITULO de:<br>ico Blectricista                                             |  |  |  |  |  |

|                                                                                                                      | dicha tosis nenne los nequisitos necesarios para<br>el EXAMEN PROFESIONAL connespondiente, otongamos<br>OBATORIO. |  |  |  |  |  |

| A T E N T A M E "POR MI RAZA HAB<br>Cuautitlan Izcal                                                                 | N T E .<br>LARA EL ESPIRITU"<br>11. Edo. de Mez., a <u>14</u> de <u>Abril</u> de 199 <u>7</u>                     |  |  |  |  |  |

| PRESIDENTE                                                                                                           | Ing. Antonio Herrera Media                                                                                        |  |  |  |  |  |

| VOCAL                                                                                                                | Ing. José Luis Rivera Lôpez                                                                                       |  |  |  |  |  |

| SECRETARIO                                                                                                           | Ing. Jorge Buendia Gomez                                                                                          |  |  |  |  |  |

| PRIMER SUPLENTE                                                                                                      | Ing. Ubaldo Ramírez Urizar 06 0597                                                                                |  |  |  |  |  |

| SECTIONS STREET                                                                                                      | Ing. Margarita López Lóbez                                                                                        |  |  |  |  |  |

Con carifio:

A mis padres.

hermanos.

y novia

#### Con Atención especial:

Al Ing. Sergio Arquelles Martinez y a todas las personas que contribuyeron a la realización de este proyecto

#### CONTENIDO

| INTROD                                 | UCCION                                                                                                                                                                                                                                                                                  | I                                |

|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| I. PRO                                 | BLEMA EN LA PRODUCCION DE ENERGIA ELECTRICA EN UNA<br>TRAL TERMOELECTRICA.                                                                                                                                                                                                              |                                  |

| 1.2 P                                  | eneralidades<br>anel de alarmas<br>egistrador de eventos                                                                                                                                                                                                                                | 1<br>1<br>2                      |

| II. ES                                 | CALAMIENTO DE SERALES                                                                                                                                                                                                                                                                   |                                  |

|                                        | eneralidades<br>tapa escaladora de señal 1200A/110AC                                                                                                                                                                                                                                    | 3<br>6                           |

| III. A                                 | CONDICIONAMIENTO DE SERALES                                                                                                                                                                                                                                                             |                                  |

| 3.2 Fi<br>3.3 De<br>3.4 Ni<br>3.5 Ut   | eneralidades  Itto de currientes transitorias  stector de nivel con histeresis  tveles lógicos de voltaja  tilidad del receptor en el HCPL-2730 y de la compuerta  REXC, para el simulació de eventualidades como niveles  gicos de voltaje                                             | 7<br>9<br>10<br>13               |

| ıv. co                                 | DNVERTIDOR DIGITAL-ANALOGICO                                                                                                                                                                                                                                                            |                                  |

| 4.2 Ne<br>ev<br>4.3 Ne<br>pa<br>4.4 Co | eneralidades<br>cesidad de multiplexar los niveles logicos de las<br>centualidades en un turrogenerador<br>cesidad de utilizar un convertidor Digital-Analogico<br>ra transmisión de coñeles<br>nvertidor Digital-Association<br>sultados obtenidos e. la experimentación con el DAC-65 | 18<br>18<br>20<br>22<br>23       |

| V. EL                                  | MICROCONTROLADOR 68H011 Y EL PUERTO E                                                                                                                                                                                                                                                   |                                  |

| 5.2 El<br>5.3 Si:<br>5.4 Lo            | neralidades<br>microcontrolado: 68HCTT<br>stema de control del ronvertidor AVD en el puerto E<br>s registros en el microscontrolador 68HCTT<br>meneria en el micro entrolacor 68HCTT<br>ogramación de dispositivos entrada/salida                                                       | 23<br>26<br>27<br>28<br>31<br>32 |

|                                        | ENO DEL PROGRAMA PARA CAPTURA DE EVENTOS EN EL<br>ROCONTROLADOR 68HC11E9                                                                                                                                                                                                                |                                  |

| 5.2 Sii<br>5.3 Sii                     | nulación de um MTS con el microcontrolador<br>mulación del Hardware redistrador de secuencias                                                                                                                                                                                           | 35<br>38<br>41<br>43             |

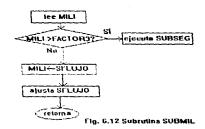

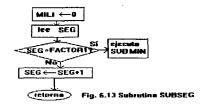

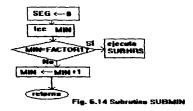

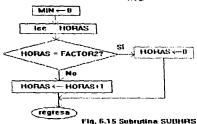

| 6.5 Programa principal y la subrutina CLARO 6.6 Resultados obtenidos 6.7 Subrutina TIMER 6.8 Subrutinas SUBSEG y SUBMIL 6.9 Subrutina SUBHRS 6.10 Conversiones de código binario a BCD en TIMER 6.11 Programa BUFFALO en el 68HC11E9 6.12 Subrutina OUTSTRG en TIMER 6.13 Inicialización del reloj |                |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| VII. PRESENTACION DE RESULTADOS                                                                                                                                                                                                                                                                    |                |

| 7.1 Generalidades<br>7.2 Presentación en el display 1720A<br>7.3 Presentación en un monitor de computadora                                                                                                                                                                                         | 56<br>57<br>58 |

| CONCLUSIONES                                                                                                                                                                                                                                                                                       | 61             |

| APENDICE A                                                                                                                                                                                                                                                                                         |                |

| Listados                                                                                                                                                                                                                                                                                           | 63             |

| APENDICE B                                                                                                                                                                                                                                                                                         |                |

| Tablas de registros e instrucciones del 68HC11E9                                                                                                                                                                                                                                                   | 73             |

| BIBLIOGRAFIA                                                                                                                                                                                                                                                                                       | 93             |

#### INTRODUCCION

La central termoeléctrica "Fco. Pérez Ríos" ubicada en el Estado de Hidalgo. Es una de las plantas generadoras de energía eléctrica más importante en nuestro país.

La generación de energía eléctrica en una central de este tipo se basa en el aprovechamiento de la capacidad calorífica de un combustible fósil llamado combustóleo para llevar a cabo un trabajo que finalmente se ve reflejado en potencia eléctrica.

El trabajo que se realiza es el siguiente:

- 1) Cambiar el estado del agua de líquido a vapor.

- 2) Convertir la energia calorifica del vapor à energia cinética en los alabes de una turbina.

- 3) Convertir la energía cinética rotativa en el eje de una turbina a potencia eléctrica a través de un generador.

Una turbina cuyo eje lleva acoplado un generador eléctrico recibe el nombre de Turbogenerador.

En los últimos años, con la demanda de energía eléctrica la central termoeléctrica "Fco. Pérez Ríos" decidió aprovechar la energía calorífica de los gases liberados a la atmosfera en los procesos termodinámicos gas-vapor. Este aprovechamiento energia se llevo a cabo en una sección de la planta que desde

entonces se conoce como "Sección Ciclo Combinado". Un Turbogenerador es una máquina de grandes dimensiones y sumamente costosa. Debido a ésto, están provistas de un sistema de protección. Ya que de lo contrario resultaría contraproducente llegar a una reparación ó sustitución de las misma.

El sistema de protección se encarga poner fuera de funcionamiento al Turbogenerador cada vez que se detecta una sobrecorriente en los devanados del generador electrico.

Las sobrecorrientes son producidas por eventos tales Alta vibracion del compresor. Alta temperatura en las chumaceras. Baja presión de aceite de lubricación. Muy alto movimiento axial del compresor. Sobrevelocidad del compresor. Paro de turbina, eta.

El departamento de "Control Supervisorio" de planta termoelectrica se encarga de estudiar, analizar y prevenir estos eventos.

La ingeniería electronica se ha desarrollado en este campo con la utilización de registradores de eventos. Estos sistemas electrónicos capturan en su memoria las eventualidades ocurridas durante la operación de una maquina en particular.

En la aereonautica, un registrador de eventos nos puede proporcionar la información necesaria para saber la causa de algún siniestro en una nave aérea. Aún cuando no haya habido sobrevivientes.

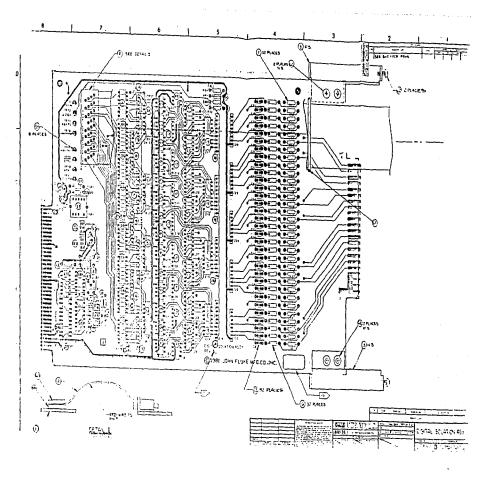

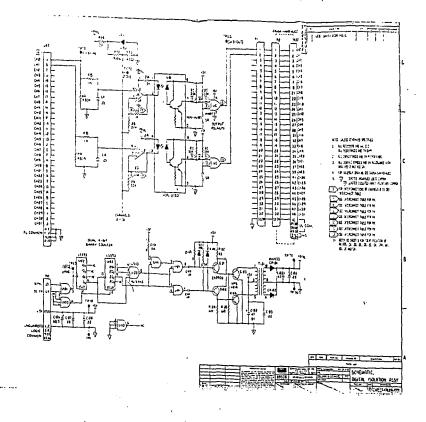

Rios" adquirio un registrador de eventos patentado por la compañía Jhon Fluke. MFG. CO. INC. Este sistema electrónico se instalo en la sección Ciclo Combinado. Desafortunadamente. e 1 controlador 2400A-104/AA y la unidad logica de procesamiento (Mainframe 2400A) del sistema dejaron de funcionar.

Mi labor de investigación en el departamento de control

entre otras actividades fue la de encontrar una solución a este

problema. Por la responsabilidad que implica solución del mismo,

surge la necesidad de una propuesta de tesis.

El método a secuir es el siguiente:

- Multiplexar las señales que recibía el controlador 2400A-104/AA para enviarlas al microcontrolador 68HC11.

- Programar al microcontrolador 68HC11 para captura e identificación de la información enviada.

- Sustituír a la unidad lógica de procesamiento (Mainframe 2400A) por una computadora personal PC.

- Diseñar un programa en la computadora que pueda interpretar información enviada a través del puerto serie.

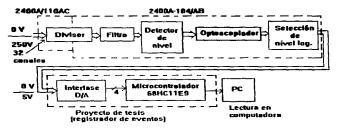

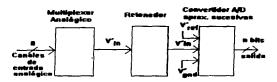

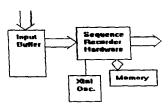

Los pasos a seguir pueden apreciarse claramente en la siguiente figura:

Registrador de eventos basado en el microcontrolador 68HC11E9 adaptado a la ctapa acondicionadora de señal de un turbocenerador de 300Mw

El capítulo 1 explica el problema que existe en una central termoeléctrica cuando ocurre una falla en el turbogenerador y no se cuenta con un registrador de eventos.

- Commence of the Commence of

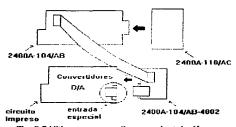

El capítulo 2 describe el escalamiento de señales que se lleva a cabo en la etapa 2400A/110AC en el registrador de eventos patentado por la compañía Jhon Fluke. MFG. CO. INC. para 32 señales de voltaje producidas por los eventos de un turbogenerador.

El capítulo 3 describe el acondicionamiento de las señales en las etapa 2400A-104/AB en el registrador de eventos patentado por la compañía Jhon Fluke MFG. CO. para las señales enviadas por el divisor 2400A/110AC.

El capítulo 4 trata sobre la transferencia de datos implementada con los convertidores DAC-08.

El capítulo 5 se refiere al microcontrolador 68HC11 y a la forma de operación del puerto E cuando funciona como convertidor analógico-digital.

El capítulo 6 trata sobre el diseño del programa en lenguaje ensamblador que utiliza el microcontrolador para la

captura y registro en tiempo real de los eventos.

El capítulo 7 muestra algunas herramientas disponibles en el lenguaje de programación QBASIC para la comunicación con dispositivos conectados a la interfaz RS-232. También, se expone el algoritmo diseñado en este lenguaje para interpretar la información registrada por el microcontrolador una vez que ha sucedido una falla en el turbogenerador.

#### PROBLEMA EN LA PRODUCCION DE ENERGIA ELECTRICA EN CAPITULO I. UNA CENTRAL TERMOELECTRICA

#### 1.1 GENERALIDADES

El problema básico en cualquier industria productiva es el de mantener un nivel de productividad mínimo necesario para satisfacer las demandas del mercado.

Cuando no se logra ser lo suficientemente productivos. Se pérdidas económicas que resultan ser sumamente cuantiosas.

La Comisión Federal de Electricidad es la única industria en México encargada de producir energía eléctrica. Su nivel de productividad excede las demandas de consumo diario en nuestro país.

Sin embargo, existen pérdidas económicas debidas a un mayor consumo de combustible en las centrales termoeléctricas. Lo que se manifiesta cuando alguna de las mismas no está produciendo la suficiente potencia.

La perdida total ó parcial de potencia en una central termoeléctrica generalmente viene precedida por la inactividad en algún turbogenerador.

Las pérdidas son mínimas cuando se logra un arrangue rápido en el turbogenerador. Pero no siempre sucede así. En muchas ocasiones los arranques pueden demorarse hasta 24 Hrs. cuando se desconoce por completo el "origen del disparo" (conjunto de eventualidades previas al paro del turbogenerador).

Para prevenir un "disparo" (paro del turbogenerador) se hace necesario tener un registro de los eventos previos.

#### 1.2 PANEL DE ALARMAS

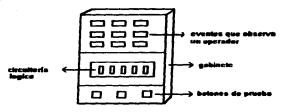

control instaladas en LAS SALAS de cada central termoeléctrica cuentan con "paneles de alarmas" (Ver fig. 1.1). a cargo de un "operador" para tener un registro de eventos.

Un operador es la persona encargada de notificar las

eventualidades observadas en un panel de alarmas.

En muchas ocasiones, el operador no está momento de suceder los eventos, por lo que el "disparo de unidad" (paro del turbogenerador) es inevitable.

Otra desventaja que se presenta un panel de alarmas es la confiabilidad de sus componentes. Ya que los focos en los anunciadores son susceptibles de fundirse. Por otra parte, el cableado y la forma de transmisión de las señales representa un problema continuo.

Se cuenta con "probadores de alarmas" que avudan a la reparación y mantenimiento de los paneles. Pero el problema no termina por solucionarse.

Fig. 1.1 Panel de alarmas a cargo de un operador

#### 1.3 REGISTRADOR DE EVENTOS

notifique las eventualidades.

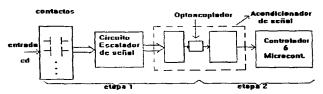

Un "registrador de eventos" (Ver fig.1.2) es un sistema electrónico que registra en una memoria una serie de datos digitales relacionados con una secuencia de eventos. Sus característicos de operación dependen de cada fabricante. El registro lo efectúan repetidamente en periodos rápidos de tiempo (milésimas se segundo). Están constituídos por un circuito escalador de señal, una interfase acondicionadora de señal y un controlador.

Un registrador de eventos aplicado a las necesidades de la industria electrica proporciona las siguientes ventajas:

- 1) No requirre de un "operador" que observe un panel de alarmas v

- Es un sistema electronico implementado con un controlador o microcontrolador que por sus características resultan ser sumamente confiables.

- En caso de suceder un "disparo" se puede conocer su origen con toda precisión.

- El arranque de un turbogenerador se puede llevar a cabo de forma inmediata.

- Las perdidas económicas en la producción de energía electrica se reducen a un minimo.

Las desventajas que se tienen con un sistema electronico de este tipo es en cuanto al número de señales que pueden procesarse con el controlador o microcontrolador. Ya que los puertos de

entrada son limitados. Sin embargo debemos señalar que un registrador de eventos es muy útil cuando es instalado en lugares estrategicos. Es decir. en las áreas de mayor interes en una central termoeléctrica.

Por otra parte, es posible tener una estadística del comportamiento de las eventualidades a largo plazo ocurridas en un turbogenerador mediante el uso de los archivos de eventos cotidianos en computadora. De tal manera que los "disparos de unidad" tengan lugar en periodos más prolongados de tiempo mediante un análisis exhaustivo de la información estadística obtenida.

Fig. 1.2 Arquitectura de un registrador de eventos

#### CAPITULO II. ESCALAMIENTO DE SERALES

#### 2.1 GENERALIDADES

Cuando hablamos de realizar un dibujo a "escala" nos referimos a hacer una representación gráfica de un objeto real con dimensiones diferentes. Las dimensiones de un dibujo a escala pueden ser mayores ó menores que las del objeto en cuestión, pero siempre en forma proporcional.

Por ejemplo una cámara fotográfica reduce las dimensiones de un objeto real a unos cuantos centímetros en un retrato, sin modificar en lo absoluto la imagen que percibimos al observar dicho objeto. En este caso, podemos decir que se ha hecho un "escalamiento de dimensiones".

En electrónica, un "escalamiento de ceñal" puede definirse como el aumento 6 disminución en forma proporcional de los valores que presenta una variable física.

Los valores de corriente y voltaje en una señal pueden disminuir o aumentar en forma proporcional a traves de los devanados de un transformador electrico.

#### 2.1.1 RELEVADORES

En la industria electrica existen muchos dispositivos electromecánicos de gran utilidad. Toda máquina electromecánica está provista de un arrollamiento electrico por el cual circula una corriente que produce una fuerza electromotiz utilizada para realizar un trabajo.

Un relevador es dispositivo electromecanico formado por una bobina electrica y dos laminillas de material conductor. Cuando la bobina es excitada. Las laminillas tienden a unirse o

separarse entre s1.

En condiciones normales (no hay excitación en la bobina), los relevadores pueden ser de dos tipos (Ver fig. 2.1)

- 1) De contactos normalmente abiertos

- 1) De contactos normalmente abiertos

2) De contactos normalmente cerrados

En ambos casos, la fuerza mecánica ejercida por un resorte se encarga de mantener separadas ó unidas a las laminillas. La fuerza electromotriz creada por la bobina tiene un efecto inverso al producido por la acción del resorte.

Un relevador de contactos normalmente cerrados requiere mayor corriente de excitación en su bobina para cambiar de estado las laminillas que un relevador de contactos normalmente abiertos. (Ver Tabla 1).

Fig. 2.1 (a) Contactos normalmente cerrados (b) Contactos normalmente abiertos

#### 2.1.2 UTILIDAD DE UN RELEVADOR EN LAS SERALES DE EVENTOS

Un sistema de protección a base de relevadores se encarga de poner fuera de funcionamiento a un turbogenerador cada vez que se detecta una sobrecorriente en los devanados del generador electrico.

Las sobrecorrientes son producidas por eventos tales como Alta vibración del compresor. Alta temperatura en las chumaceras. Baja presión de aceite de lubricación, etc.

Si la bobina en un relevador se excita con una sobrecorriente producida por algún evento, entonces el cambio de estado en las laminillas nos indicara que existe un problema en los devanados del generador electrico.

Por otra parte, es posible generar una señal de voltaje para cada evento si conectamos una batería en serie con un relevador (ver fig. 2.2).

En consecuencia, un sistema de protección a base de relevadores puede ser conectado a un registrador de eventos (Verfig. 2.3) para análisis, estudio y prevención de las eventualidades.

| Estado del contacto | Voltaje aplicade                        |  |

|---------------------|-----------------------------------------|--|

| Cerrado             | Seliales de entrada<br>auperiores a 68V |  |

| Ablerte             | Señoles de entrada<br>inferiores a 40V  |  |

Table 1. Relación entre señales de entrada y el estado de los contactos

Fig. 2.2 Conexión serie batería - relevador

contactos

# entrada | Circuito | Acondicionador | Controlador | 6 | Microcont.

Fig. 2.3 Sistema de protección a base de relevadores conectado a un registrador de eventos.

Las señales de voltaje generadas por los eventos en un turbogenerador son escaladas por un circuito divisor de tensión en la etapa 2400A/110AC en el registrador de eventos patentado por la compañía Jhon Fluke, MFG, CO, INC.

#### 2.2 ETAPA ESCALADORA DE SERAL 1200A/110AC

El registrador de eventos está provisto de una etapa escaladora de señal que reduce el valor de las señales de voltaje producidas por cada uno de los eventos (Ver tabla 2).

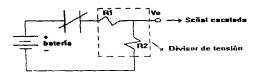

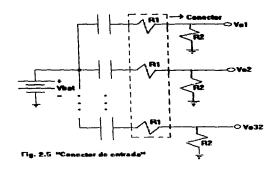

La etapa escaladora de señal está formada por un arreglo resistivo en "cascada" conocido con el nombre de "divisor de tensión". (Ver fig. 2.4).

| estada del<br>contacto | Veltajo aplicade                | Voltaje escalado |

|------------------------|---------------------------------|------------------|

| Cerrado                | Seliates superiores<br>a 66Vcd. | 2.47Vcd          |

| Ablesta                | Seliales interiores<br>a 48Vcd. | 1.67Vcd          |

Table Z. Seffales de voltale escaladas por el divisor de tensión

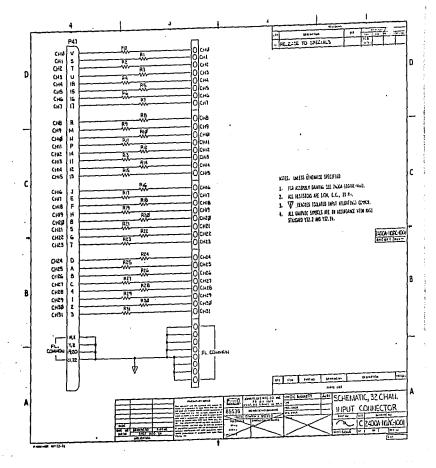

El registrador puede escalar 32 señales de voltaje utilizando un "conector de entrada" (Ver fig. 2.5). Que contiene las primeras 32 resistencias R1 del divisor.

Fig. 2.4 Arregio resistivo en "cascada" para escalar las señales de voltaje en un evento.

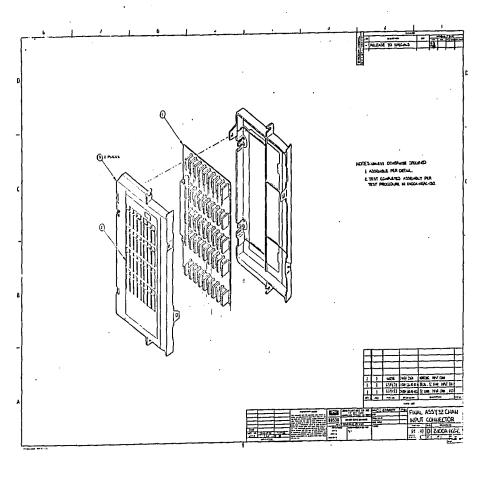

El conector de entrada acepta 32 señales de alto voltaje AC ó CD. Las resistencias se encuentran atornilladas y encapsuladas por bloques en una celda plastica cuyas dimensiones son 21x2. 9x11 centimetros (Ver diagramas). Su ueso aproximado es de 0.36 Kg. El valor de cada resistencia es de 10 Megaohms. Puéden aplicarse como maximo  $\frac{1}{2}$ .350 Vg. entre una terminal y tierra o entre ambas terminales de una resistencia.

Las siglas 1200A/110AC son utilizadas para identificar el conector como parte del registrador. El segundo elemento resistivo R2 del divisor de tensión (Ver fig. 2.5) tiene un valor de 430 Kilo ohms. Estos 32 elementos resistivos no forman parte del conector 1200A/110AC. Se encuentran alojados en la tarjeta electrónica 2400A-104/AB (etapa acondicionadora de señal) del recistrador.

#### CAPITULO III. ACONDICIONAMIENTO DE SERALES

#### 3.1 GENERALIDADES

Con el desarrollo creciente y contínuo de la tecnología e investigación en los países desarrollados. Ha sido posible lograr grandes avances científicos, en el area de la ingeniería electrónica. Como resultado de esto, la automatización y la implementación de sistemas digitales en casa todas las areas se ha convertido en un proceso sin límites.

En las comunicaciones, se puede contar con un sistema de redes por computadoras a gran escala.

En la industria de manufactura, los procesos automatizados son rapidos y eficientes.

En la medicina, pueden visualizarse y ser diagnosticadas casi todo tipo de deficiencias en el organismo humano a través de las computadoras.

En las centrales termoeléctricas es posible tener un control sumamente confiable y poderose con la tecnología de los microcontroladores.

#### 3.1.1 ACONDICIONAMIENTO DE SESALES EN UN SISTEMA DE CONTROL

Como podemos apreciar, es posible establecer una relación directa entre el mundo en que vivimos y la tecnología. Parte de esta relación es la que se ha logrado en la ingeniería de control moderna mediante la creatividad y el ingenio humano.

El proceso creativo en este ámbito puede dividirse en tres partes:

- Captura de las variables físicas que forman parte del fenómeno en estudio.

- 2) Acondicionamiento de las señales.

- 3) Diseño del control de las variables.

Todo tipo de sensores y transductores electrónicos son dispositivos que nos pueden proporcionar una señal eléctrica en función de una varable física. Por ejemplo, en la industria textil se hace necesario utilizar sensores de luz que envían una señal eléctrica en función de las rpm de un motor en una banda biladore.

Una vez que se ha logrado tener una señal electrica producida por algún fenomeno en particular. Se hace necesario llevar a cabo un "acondicionamiento" de la misma. Esto se debe a que el fenomeno en estudio tiene características muy fluctuantes e indeterminadas, las cuales se ven reflejadas en las señales electricas que producen los transductores.

En la mayoría de los casos, un "acondicionamiento de señal" cumple con los siguientes objetivos:

- Linealizar el comportamiento exponencial o logaritmico de alguna variable física.

- Eliminar fluctuaciones en la funcion lineal producidas por "ruido".

- 3) Convertir los valores determinados por la función lineal a niveles lógicos. En caso de utilizar un control digital.

#### 3.1.2 ACONDICIONAMIENTO DE SERALES EN UN REGISTRADOR

Un registrador de eventos no es un sistema de control. Debido a esto, el acondicionamiento de seña: unicamente realiza lo siguiente:

- 1) Elimina el "ruido" en las señales escaladas.

- Convierte los valores de las señales escaladas a niveles lógicos.

Para lograr los dos objetivos anteriores es necesario contar con un filtro de corrientes transitorias, un detector de nivel con histeresis y un optoacoplador. Cada una de estas partes conforman la tarjeta electronica 2400A-104/AB del registrador.

En las secciones siguientes explicaremos con detalle el funcionamiento del acondicionador de señal.

#### 3.2 FILTRO DE CORRIENTES TRANSITORIAS

Cualquier circuito electrónico que maneja oscilaciones de voltaje periódicas, presenta pequeñas corrientes transitorias posteriores a cada oscilación. Aunque la duración de estas corrientes suele ser muy pequeña, es suficiente para causar problemas en la información procesada por los sistemas digitales.

En un registrador de eventos. cada señal de voltaje producida por el cambio de estado en un relevador genera transitorias. Por corrientes ejemplo. un relevador cuvos contactos están cerrados. contactos están cerrados, presentan un voltaje escalado de  $2.47V_{cd}$ , cuando el voltaje en la batería es de  $60V_{cd}$ , (Ver Tabla 2. Section 2.2). Al momento de ocurrir una sobrecorriente es decir. la bobina del relevador es excitada por una corriente mayor a la generada por la bateria de 60V<sub>rd</sub>. El voltaje escalado de 2.47V d debe reducirse por lo menos a 1.67V para que pueda interpretarse como un cambio de estado del relevador de cerrado a

Sin embargo, el cambio de voltaje de 2.470 da 1.670 tarda en estabilizarse. Es decir. se presenta una señal de voltaje amortigüada con valores pico fluctuantes. (Ver fig. 3.1), durante un periodo de tiempo pequeño.

Estas señales amortiquadas distorsionan la información digital de entrada a un microprocesador ó microcontrolador. Por lo que deben ser eliminadas.

Fig. 3.1 Señal transitoria de voltaje

La solución del problema es posible mediante el uso de "filtros". Existen una gran variedad de ellos. Pero todos tienen una característica en comun: Son arreglos resistivos-capacitivos (Ver fig. 3.2). Este es un filtro "pasa bajas de primer orden". utilizado por el registrador de eventos, los valores de R y C son de 1Kilo ohm y 0.01 microferadios respectivamente. Un filtro de este tipo surpime señales a frecuencias pequeñas o bien, en periodos de tiempo relativamente largos. De tal manera que el registro de la información digital en un microprocesador o microcontrolador es confiable.

Fig. 3.2 Filtro pesa bajou

#### 3.3 DETECTOR DE NIVEL CON HISTERESIS

En muchas ocasiones deseamos que se lleve a cabo una serie de eventos especiales cuando realizamos una "acción determinada". Por ejemplo, cuando oprimimos un botón y suena una alarma, cuando nos acercamos a una puerta provista de sensores y ésta se abre para que entremos, cuando accionamos una palanca y todo un sistema de bombeo comienza a funcionar. etc.

La acción determinada que realizamos simplemente es activar un "mecanismo" con una "corriente eléctrica".

En electrónica, podemos activar "circuitos integrados" tales como compuertas, contadores, convertidores, memorias, microprocesadores, microcontroladores, optoacopladores, etc. con corrientes producidas por las "señales de salida" en circuitos analogicos como Detectores de Nivel. Convertidores D/A, etc.

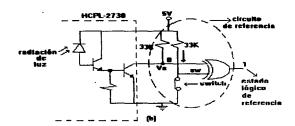

#### 3.3.1 OPTOACOPLADOR HCPL-2730

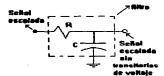

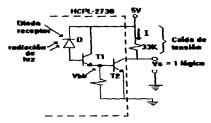

Cuando un sistema electronico utiliza etapas distintas (Componentes analogicos y digitales) es necesario transmitir la señal de una etapa a otra a traves de un circuito integrado llamado "Optoacoplador". (Ver fig. 3.3). Esto se hace con el fin e proteger los sistemas digitales de sobrecorrientes producidas en los componentes analogicos.

Fig. 3.3 Uso de un optoacoptador

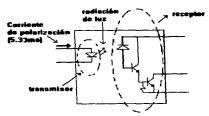

Existen una gran variedad Optoacopladores. Su principio de operación es el de radisción de luz interna entre un transmisor y un receptor. El registrador de eventos utiliza el optoacoplador HCPL-2730 (Ver fig. 3.4). En este caso, el transmisor es un "diodo". El cual debe "polarizarse en directa" con una corriente de 5.33 mili amperes.

Fig. 3.4 Optoacopledor HCPL-2739

## 3.3.2 UTILIDAD DE UN DETECTOR DE NIVEL PARA POLARIZAR EL TRANSMISOR DE UN OPTOACOPLADOR

La corriente de polarización directa que recibe un diodo transmisor en un optoacoplador puede ser la señal de salida de cualquier circuito analógico.

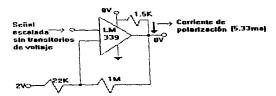

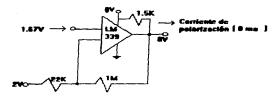

El transmisor del optoacoplador HCPL-2730 recibe la señal de salida de un arregle analogico llamado "Detector de Nivel con Histeresis". (Ver fig. 3.5). Este detector utiliza el circuito integrado LM339. las regiones de operación y su modo de funcionamiento se explicará en la siguiente sección.

Fig. 3.5 Detector de nivel con histéresis

## 3.3.3 REGIONES DE OPERACION Y MODO DE FUNCIONAMIENTO DEL DETECTOR USADO EN EL REGISTRADOR DE EVENTOS

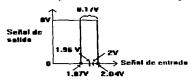

Este circuito recibe señales de  $2.47V_{cd}$  y  $1.67V_{cd}$  , dependiendo del estado cerrado ó abierto de los contactos en el relevador emisor de señal.

Supongamos que el relevador tiene sus contactos cerrados, o bien, se envía un voltaje de entrada de 2.47 $V_{\rm cl}$  al detector, éste lo compara con un voltaje "umbral superior" de 2.04 $V_{\rm cl}$  (Ver fig. 3.6). Como es mayor, envía una señal de 0 $V_{\rm cl}$  a la salida, lo que hace fluír una corriente de polarización de 5.33 mili amperes a través de la resistencia de polarización de (Ver fig. 3.5). Si por causas de "ruido", el detector cae en la región de "histéresis", es decir, en la región comprendida entre los voltajes 2.04 $V_{\rm cl}$  y 1.87 $V_{\rm cl}$  de la gráfica. La corriente de polarización mantiene su valor.

Si se presenta una eventualidad en el turbogenerador y el relevador respectivo cambia el estado de sus contactos, la señal enviada al detector cambia de 2.47 $v_{\rm cd}$  a 1.67 $v_{\rm cd}$  .. éste lo compara con el voltaje "umbral inferior" de 1.87 $v_{\rm cd}$  . Como es menor, envía una señal de 8 $v_{\rm cd}$  a la salida, lo que elimina el flujo de la corriente de polarización (Ver fig. 3.7).

Fig. 3.6 Región de aperación del detector

Si por razones de "ruido", el detector cae en la región de histéresis, la corriente de polarización sigue siendo nula.

Debemos señalar. que un circuito detector puede ser calibrado para trabajar en diversas regiones de operación con el mismo rango de histéresis unicamente ajustando el valor del voltaje de referencia. Como podemos apreciar, este valor ha sido ajustado a 2%, en el registrador de eventos.

El Detector descrito anteriormente es la última fase en la etapa de circuitería analógica que integra la etapa acondicionadora de señal del registrador. La segunda etapa está formada por el receptor del HCPL-2730 y de componentes digitales (C.I. 74LS86 que son compuertas logicas cuya función es asegurar un nivel logico de voltaje para las señales enviadas por el receptor. En la siguiente sección veremos la lógica programada para esta compuerta, así como el funcionamiento del receptor y la relación que existe entre ambos.

Fig. 3.7 Corriente de palarización nula en el detector

#### 3.4 NIVELES LOGICOS DE VOLTAJE

Un nivel de lógico de voltaje es un valor comprendido entre  $0 v_{cd}$  y  $5 v_{cd}$ . En electrónica digital, estos valores extremos son interpretados como "estados lógicos", es decir, "apagado ó encendido". Matemáticamente, corresponden a los números 0 y 1 del sistema de numeración binario.

Como sabemos, en un sistema de numeración, podemos efectuar operaciones aritméticas muy diversas. Los "circuitos integrados digitales" se han encargado de cubrir este campo. Por ejemplo, "compuerta logica" es un circuito integrado que puede realizar operaciones de suma, resta, y multiplicación. Una "memoria" resultados para almacena su posterior uso procesamiento. Un "microprocesador" efectúa operaciones lógicas y aritméticas a gran velocidad. Un "microcontrolador" reúne las características de una memoria y un microprocesador juntos, etc. Gracias a estos avances tecnológicos se puede contar hoy en día con computadoras muy sofisticadas (inteligencia artificial) gue ayudan al hombre en la solución de los problemas más compleios.

El problema decapturar eventos en un turbogenerador no es un problema de gran complejidad, pero si requiere del uso de circuitos integrados digitales. Por esta razón se hace necesario simular las eventualidades como niveles lógicos.

Parte de este trabajo se llevó a cabo en la primera etapa de circuiteria analógica del registrador. Los pasos que integran esta etapa son:

- 1) Escalar los voltajes  $40V_{cd} 60V_{cd}$  a  $1.67V_{cd} 2.47V_{cd}$  respectivamente.

- 2) Eliminar transitorios de voltaje en las señales  $1.67 \rm V_{cd}$   $2.47 \rm V_{rd}$ .

- Detectar los cambios de voltaje de 1.67V<sub>cd</sub> a 2.47V<sub>cd</sub> y viceversa.

La segunda etapa del registrador de eventos comienza a partir del receptor del HCPL-2730. En las secciones siguientes hablaremos sobre el funcionamiento del mismo, así como de una compuerta lógica llamada "Or-Exclusiva" y la relación que existe entre ambos.

#### 3.5 UTILIDAD DEL RECEPTOR EN EL HCPL-2730 Y DE LA COMPUERTA OR-EXCLUSIVA PARA SIMULACRO DE EVENTUALIDADES COMO NIVELES LOGICOS DE VOLTAJE

Como hemos estado mencionando, la utilidad de los circuitos integrados digitales es de sumo interés en la solución de problemas complejos. La magnitud de estos es muy diversa, dependiendo de la situación en la que nos encontremos. Sin embargo, debemos señalar que la aplicación más frecuente de estos sistemas radica en la solución de problemas técnicos industriales.

El problema de capturar eventos en un turbogenerador se vuelve complejo y fuera del alcance humano por las siguientes razones:

- Los cambios diferenciales de temperatura, presión y nivel no pueden ser percibidos por una persona.

- 2) Las señales de cada evento que son enviadas por los

- relevadores tienen una duración de milisegundos.

- 3) Los eventos son impredecibles.

Luego, para poder abordar el problema y tratar de plantear una solución en base a sistemas digitales se hace necesario, como primer paso, simular los eventos como señales lógicas de voltaje.

#### 3.5.1 FUNCIONAMIENTO DEL RECEPTOR EN EL HCPL-2730

El receptor es un circuito formado por un diodo D y dos transistores Tl v T2 denominado "Darlington" (Ver fig. 3.5). El diodo receptor D tiene la función de interruptor, es decir, abre 6 ciorra el circuito. Cuando se presenta un evento, el diodo transmisor del HCPL-2730 manda una señal radiante de luz al diodo receptor D. En este momento el circuito se cierra y comienza a fluír una corriente I a través de la resistencia de 33K, originando una cada de tensión en la misma, esto hace que el voltaje de salida V, en el colector del transistor TC sea la diferencia entre los SV de la fuente y la caída de tensión resistiva. Esta diferencia corresponde a un nivel lógico de voltaje alto. O bien, a un estado de "encendido" que puede interpretarse como un 1 logico en los sistemas digitales.

Cuando termina la duración del evento, el diodo transmisor deja de enviar radiación de luz al diodo receptor D. En consecuencia. el circuito se abre y la corriente I deja de fluir a través de la resistencia. Por lo que la señal de salida V, cambia de un nivel lógico de voltaje alto a bajo. En otras palabras, se presenta un cambio de estado a "apagado" que corresponde a un O lógico en los sistemas digitales.

Fig. 3.8 Receptor del HCPL-2738

El siquiente paso a seguir en la simulación de eventos como niveles lógicos de voltaje es la implementación de un circuito lógico de "referencia". Ya que de lo contrario, sería imposible saber cúal fue el "estado inicial" del que partimos. Por ejemplo, si tenemos un estado lógico de 1 en  $\rm V_3$  y éste cambia a O. sería lógico pensar que acaba de ocurrir un evento. Sin embargo, esta afirmación es válida siempre y cuando sepamos que el 1 lógico es el estado inicial.

El circuito de referencia utilizado por el registrador de eventos está formado por una compuerta lógica llamada "Or-Exclusiva" que se explicará en la siguiente sección.

#### 3.5.2 LA COMPUERTA OR-EXCLUSIVA COMO CIRCUITO DE REFERENCIA

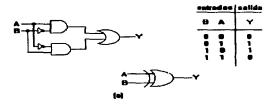

Una compuerta logica o compuerta binaria es el elemento básico en los sistemas digitales. Opera con el sistema de numeración binario (1 y 0 logicos). Todos los sistemas digitales se construyen urando solo tres compuertas lógicas. A estas compuertas se les conoce con el nombre de AND. OR y NOT. (Ver fig. 3.9). Muchos problemas de logica digital utilizan "combinaciones de compuertas". Uno de ellos, es el que se presenta cuando necesitamos detectar ó sensar un cambio de estado logico. Es decir, de la 0 ó viceversa.

Este problema es típico en un registrador de eventos, ya que necesitamos detectar el cambio de estado en los contactos de un relevador. La solución se ha logrado con la implementación de un "circuito de referencia" usando una combinación especial de compuertas llamada "compuerta Or-Exclusiva" (Ver fig. 5.10). Como podemos observar, este circuito es una simple conexión entre el receptor del HCPL-2730 y la compuerta. El estado logico de referencia viene determinado por la posición del switch.

Fig. 3.9 (a)compuerta AND, (b)compuerta OR, (c)compuerta NOT

Si la posición del switch es "cerrada", tendremos un estado lógico de referencia igual a 1 a la salida de la compuerta cuando el nivel lógico de V, sea de 0. Obviamente, si ocurre un evento, la señal de 0 lógico en V, cambiará a 1 lógico, haciendo qué exista un cambio de estado a la salida de la compuerta de 1 a 0 lógico. En este momento, podemos saber que ha ocurrido un evento. Análogamente, si la posición del switch es "abierta", tendremos un estado lógico de referencia igual a 0 a la salida de la compuerta cuando el nivel lógico de V, sea de 0. Luego, al suceder una eventualidad, la señal de 0 lógico en V, cambiará a 1 lógico, de tal manera que el estado innicial a la salida de la compuerta cambiará de 0 a 1 lógico, indicando la presencia de una eventualidad.

En el registrador de eventos, la posición del switch normalmente se encuentra cerrada (Ver diagramas).

El circuito de referencia es la ultima parte que integra la etapa acondicionadora de señal 2400A-104/AB en el registrador. Los diagramas respectivos se muestran el final del capítulo.

La parte experimental de esta tesis comienza a partir del siguiente capítulo, donde hablaremos sobre un circuito multiplexor analógico diseñado especialmente para servir como interfase entre los 32 niveles logicos de voltaje del registrador vun puerto de entrada al microcontrolador 68HC11E9.

Fig. 3.10 (a)Compuerta Or-Exc. (b)Circulto de referencia sw=1

#### CAPITULO IV . CONVERTIDOR DIGITAL-ANALOGICO

#### 4.1 GENERALIDADES

Los aparatos telefónicos, son utilizados a diario por millones de personas en todo el mundo. Como sabemos, el modo de operación de un teléfono es muy simple, unicamente oprimimos una serie de teclas y establecemos la comunicación deseada. Si por alguna razón, tenemos la necesidad de cambiar la comunicación, simplemente colgamos y oprimimos nuevamente una serie de teclas diferente a la primera.

El proceso de seleccionar una línea de comunicación telefónica a través de una combinación determinada de teclas puede definirse en electronica como "Multiplexar una señal". Todos los telefónos modernos llevan en su construcción interna circuitos integrados llamados "multiplexores".

Existen muchas otras aplicaciones de los circuitos multiplexores, entre ellos destacan la construcción de interfases para "comunicación digital". Cuando hablamos de comunicación digital, podemos pensar en el intercambio de información entre una computadora y sus periféricos. Por ejemplo, sería imposible enviar información de un teclado a la memoria du na computadora si esta no tuviese un "puerto de comunicación" para recibir los datos. En un puerto se enlazan líneas de comunicación (Ver fig. 4.1), a través de las cuales se genera un flujo de datos.

En muchas ocasiones las líneas de comunicación difieren de la configuración del puerto, es decir, podemos tener 8 líneas de comunicación y nuestro puerto sólo puede admitir 4 de ellas. Para resolver este tipo de problemas se utilizan interfases multiplexoras.

Fig. 4.1 líneas de comunicación entre un teclado y una computadors

## 4.2 NECESIDAD DE MULTIPLEXAR LOS NÍVELES LOGICOS DE LAS ENENTUALIDADES EN UN TURBOGENERADOR.

Hace algunos años, el registrador de eventos instalado en la sección de ciclo combinado de la central termoeléctrica "Fco. Pérez Ríos", contaba con un controlador identificado con las siglas 2400A-104/AA (Ver fig. 4.2) en comunicación con la etapa acondicionadora de señal 2400A-104/AB descrita en el capítulo anterior. De la figura, podemos apreciar que el número de líneas de comunicación es de 32 (una por cada evento).

Fig. 4.2 Registrador de eventes en la central termoeléctrice hace algunos alios.

Recientemente, el departamento de Control Supervisorio de la central decidió abordar el problema. Esta decisión, basada en un presupuesto económico y experiencia técnica enfocó, la solución a los siguientes puntos:

- Conservar las tarjetas acondicionadoras de señal 2400A-104AB.

- 2)Utilizar un controlador versátil y económico que pudiese suplir las características del 2400A-104/AA ó mejorarlas.

- Utilizar una computadora personal con un programa nuevo para sustituír el programa de prueba"A104AB" en la unidad de procesamiento Mainframe 2400A.

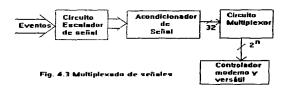

En el punto número 2, aparece el primer problema. Si nosotros cambiamos de controlador, las características tecnicas de éste pueden ser iguales ó mejores al primero, pero las líneas de comunicación no son las mismas. Entonces, para poder llevar a cabo este punto se hace necesario diseñar un circuito multiplexor (Ver fig. 4.3), que pueda resolver el problema de comunicación entre las 32 lineas a la salida del acondicionador y las 2º líneas de entrada al nuevo controlador.

#### 4.3 NECESIDAD DE UTILIZAR UN CONVERTIDOR DIGITAL-ANALOGICO PARA TRANSMISION DE SERALES

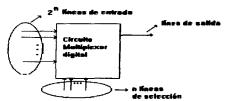

En electrónica, existen multiplexores digitales y analógicos. Como su nombre lo indica, los primeros manejan datos digitales y los segundos datos analógicos. Los multiplexores constan principalmente de tres partes (Ver fig. 4.4), un circuito de líneas de entrada, una línea de salida y líneas de selección.

Fig. 4.4 Circuito multiplexor digital

Los multiplexores no pueden transferir un dato en la línea de salida si no se indica en las líneas de selección cual de todos 108 que conforman las líneas de entrada es el que va a ser transferido. Esto implica, diseñar un "circuito digital de selección" que se ajuste a nuestras necesidades. Más aún. si la transferencia de datos debe hacerse en milesimas de segundo al puerto de entrada en un controlador, el circuito digital de selección debe ser lo suficientemente rápido para evitar perdidas información. En este caso, podría utilizarse como circuito selector, las lineas en un puerto de salida del mismo controlador previamente programado, es decir, mediante el uso de software (logica programada) llevar a cabo la selección (Ver fig.4.5). Sin embardo, esto implicaria utilizar "memoria extra" controlador, que por lo general es reducida. Existen circuitos integrados de memoria que pueden ser adaptados a controladores para ampliar las capacidades de software de los mismos. Fero esta lalternativa debe ser considerada len casos muy necesarios.

Sin embargo, el punto numero 2de la solución blanteada por el departamento de control supervisorio, nos permite utilizar un controlador versatil y economico. En la actualidad, los controladores que cumplen con estas caracteristicas son los "microcontroladores". Estos circuitos integrados, se han perfeccionado mucho, en tal magnitud, que podemos afirmar que son computadoras del tameño de un "chip".

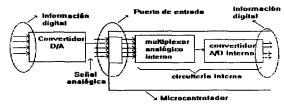

Gracias a las capacidades que ofrecen los microcontroladores

en día. se hace posible utilizar un convertidor digitalhacer la transmisión de datos (Ver analógico para fig.4.6). la analógica que llega al puerto de entrada en **61** microcontrolador, tiene una representación única como información digital en las líneas de salida del convertidor A/D (Analógico-Digital) interno. Esta relación entre ambos tipos de datos recibe el nombre de "resolución" y su valor depende del fabricante.

Luego. la implementación de una transmisión de datos con ayuda de un convertidor D/A se reduce simplemente a buscar la resolución apropiada.

Todo convertidor, necesita ser alimentado por una fuente de poder. Esto representa una desventaja cuando deseamos implementa la transmisión de datos, ya que se presenta "ruido" en la señal analogica de salida generado por la fuente. En la práctica, esta distorsión nos indicaría la aparición de eventos irreales, pero serían facilmente reconocidos como tales por su naturaleza.

Fig. 4.6 Transmisión de datos a través de un convertidor D/A

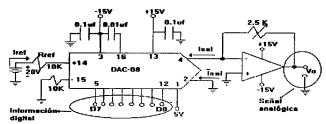

En el mercado, existe una gran variedad de convertidores D/A que pueden servir para implementar una transmisión de datos. El componente utilizado en esta tesis, fue el circuito integrado

"DAC-08", que es un convertidor D/A (Digital-Analógico) de 8 bits En la siguiente sección hablaremos sobre el funcionamiento de este componente.

#### 4.4 CONVERTIDOR DIGITAL-ANALOGICO

En la sección anterior, se mencionó la forma de implementar transmisión de datos con el uso de convertidores D/A. El convertidor utilizado en la experimentación de este proyecto, es un circuito integrado laamado "DAC-08" encapsulado en un empaque doble de 16 terminales (Ver fig. 4.7). Debemos señalar que cualquier convertidor D/A puede servir para éste propósito, siempre y cuando pueda ser ajustado a las características de operación del convertidor A/D interno. Todos los convertidores pueden ser ajustados para operar con un factor de conversión llamado "resolución". Esta cantidad, es la razón matemática que existe entre el valor de la señal analógica de salida y el valor decimal equivalente de la información digital de entrada a un convertidor. Por ejemplo, si los datos digitales de entrada en el circuito de la figura 4.7 son 11010110, o bien 21410 y la señal analògica de voltaje es de 5 $V_{cd}$ , entonces el factor de resolución sería de 23.4 $\times 10^{-3}$ . Este número esta determinado por el fabricante en los convertidores D/A internos, pero en los convertidores A/D existentes en el mercado, pueden ser ajustados a una resolución determinada según las necesidades personales.

Fig. 4.7 Convertidor Digital-Analógico

En esta tesig, el convertidor DAC-08 se ajustó a una resolución de 20x10<sup>3</sup>. Por las razones antes mencionadas. Para lograr este factor de conversión fue necesario lo siguiente:

1)Construir una fuente regulada de voltaje para obtener los valores de  $+15V_{cd}$   $-15V_{cd}$  ,  $+20V_{cd}$  y  $+5V_{cd}$  en la alimentación del DAC-08

2) Armar 3 circuitos similares más, para la simulación de 32 eventos como niveles lógicos de voltaje.

# 4.5 RESULTADOS OBTENIDOS EN LA EXPERIMENTACION CON EL DAC-OS

En la sección 4.3, se habló sobre los efectos de "ruido" emitidos por la fuente de alimentación al convertidor D/A. Durante la experimentación en este proyecto, las fluctuaciones se presentaron en los bits de menos peso. Por ejemplo, si la información digital a la entrada del DAC-08 a ser transmitida era de 11010101, la salida del convertidor A/D registraba 1101011; como información recibida. Si la señal de entrada se cambiaba a 11010110, entonces obteniamos 11010111; en el convertidor. Este tipo de resultados, siguen siendo de utilidad, siempre y cuando el número binario de entrada forme parte del número binario a la salida, como en los casos previamente citados. En caso contrario, si los números binarios a la salida del convertidor se hubiesen registrado como 11010110, esta información sería de utilidad en un 90% para nuestros propositos, puesto que la eventualidad no registrada en el bit 20 tendria que ser averiguada personalmente en campo.

La parte experimental con Hardware se concluye con este capítulo. En los siguientes capítulos hablaremos acerca de la experimentación con software, donde manejamos programación de bajo y alto nivel, comenzaremos con lenguaje ensamblador, por lo que se hace necesario hablar previamente de las características técnicas del dispositivo a programarse.

# CAPITULO V. EL MICROCONTROLADOR 68HC11 Y EL PUERTO E

# 5.1 GENERALIDADES

En la sección 4.3 del capitulo anterior, se habló de las capacidades que ofrece un microcontrolador moderno para poder implementar una transferencia de información con convertidores.

Hablar sobre microcontroladores seria muy extenso, ya que en la actualidad, existen varios fabricantes y múltiples modelos diferentes de chips. Mas aun, no es posible en un solo libro de texto cubrir todo lo referente a un microcontrolador en particular. En esta tesis, mencionaremos las características mas generales y destacaremos las caracidades mas atractivas que se utilizaron en este proyecto con el microcontrolador 68HC11E9 de MOTOROLA.

# 5.1.1 ¿QUE ES UN MICROCONTROLADOR?

Cuando se vió la necesidad de realizar un gran número de operaciones aritméticas y lógicas a gran velocidad, surgió la primera computadora en el mundo, utilizando la tecnología de la época. Lo que dió lugar a la primera generación de computadoras.

Gracias a los avances tecnologicos, las computadoras fueron perfeccionandose cada dia mas, su tamaño se reducia gradualmente

y se incrementaba su capacidad. La libre competencia en el mercado no se hizo esperar, surgieron muchos modelos de computadoras y diversos fabricantes. Entonces, a través de la historia se fueron clasificando las computadoras de acuerdo a sus características técnicas en generaciones distintas. En la actualidad, nos encontramos en una generación muy avanzada de computadoras y la evolución en este campo sigue teniendo lugar en diversas partes del mundo a gran escala. Parte de este desarrollo técnico, ha dado lugar a la aparición de los "microcontroladores" en el mercado.

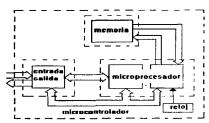

que una computadora, Al iqual un microcontrolador realizar operaciones aritméticas y lógicas a gran velocidad. tiene los elementos básicos que integran una computadora (Ver que son. microprocesador, memoria y unidades de entrada/salida. La diferencia entre ambos, radica en su tamaño y capacidad. La mayoría de nosotros conocemos las dimensiones de una computadora personal. Un microcontrolador es tan pequeño, que puede ser alojado en una tarjeta electrónica de 17x8 centímetros con todo el hardware necesario para su uso. Sin embargo, un microcontrolador no puede sustituir a una computadora en capacidad. Un microcontrolador se invento con la finalidad de ser programado e instalado en algun sistema de control. En actualidad. podemos encontrar microcontroladores "ordenadores de lazo" (loop command), utilizados en el diseño de de control en las centrales termoeléctricas. también en invección electrónica de combustible" propios de automoviles sofisticados, así como "registradores de secuencia" en diversos sistemas electronicos, etc.

Fig. 5.1 Argultectura de un microcontrolador

#### 5.1.2 ¿COMO FUNCIONA UN MICROCONTROLADOR?

En la sección anterior, se mencionaron las partes principales de un microcontrolador, sus características físicas y se hizo una analogia con el funcionamiento de una computadora.

Debemos señalar, que un microcontrolador *no es una*

computadora y tampoco puede realizar las funciones de esta. Pero las operaciones que realizan ambos son muy parecidas, así como el funcionamiento de sus mecanismos internos. En la siguiente tabla podemos apreciar algunas de éstas similitudes.

| FUNCION                                       | COMPUTADORA                       | MICROCONTROLADOR                                                                    |  |  |  |

|-----------------------------------------------|-----------------------------------|-------------------------------------------------------------------------------------|--|--|--|

| Operaciones<br>aritméticas y<br>lógicas       | Unidad aritmética y<br>lógica CPU | Unidad aritmética y<br>lógica CPU                                                   |  |  |  |

| Almacenamiento de la información              | Memoria RAM. ROM                  | Memoria RAM, ROM y<br>EEPROM                                                        |  |  |  |

| Entrada de<br>información                     | Teclado, lápiz<br>óptico          | Teclado (Con el uso<br>de un ensamblador)                                           |  |  |  |

| Presentación de la<br>información interna     | Impresora, monitor                | Impresora, monitor<br>(Con interfase a un<br>programa en lenguaje<br>de alto nivel) |  |  |  |

| Comunicación entre<br>usuario y la CPU        | Intérprete de<br>comandos         | Intérprete de comandos                                                              |  |  |  |

| Comunicación con<br>dispositivos<br>digitales | Puertos serie y<br>paralelos      | Puertos<br>bidireccionales de 8<br>a 16 bits                                        |  |  |  |

La mayoría de nosotros hemos utilizado una computadora, o por lo menos hemos visto lo que otras personas realizan con ella. Las tareas que se pueden realizar hoy en día con una PC son muy diversas, pero la forma de trabajar de esta siempre es la misma. Es decir, realiza lo siguiente:

- 1) Recibe información externa.

- 2) Procesa la información.

- 3) Devuelve resultados.

Los microcontroladores trabajan exactamente igual, y su area de trabajo ha sido enfocada a la solución de problemas electronicos. Es decir, ya no se hace necesario "tener conectada" una computadora y estar utilizando su hardware interno para implementación de "procesos digitales".

información que recibe un microcontrolador, es un "conjunto de instrucciones" que le indican una tarea específica a realizar. Cada instruccion, es almacenada en un lugar único en la memoria interna del microcontrolador. Posteriormente, cada una de ellas pasa a ser procesada por una "unidad logica y aritmetica" dentro del CPU. Una vez concluido el procesamiento de una instrucción, el microcontrolador realiza lo indicado por esta. El procedimiento . se repite una y otra vez hasta que todas instrucciones hayan sido procesadas y ejecutadas.

Los resultados devueltos, pueden observarse en un monitor de computadora.

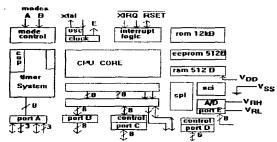

# 5.2 EL MICROCONTROLADOR 68HC11

Este microcontrolador. es un "circuito integrado" que contiene muchos dispositivos de "entrada/salida"y varios tipos de memoria que podemos programar. Si requerimos más dispositivos, podemos hacer una expansión de hardware fácilmente.

Se cuenta con una capacidad de 12 Kilo Bytes en ROM y 512

Bytes en RAM (Ver fig. 5.2), todos los dispositivos de entrada/salida que observamos, pueden ser utilizados en el modo de operación A. Este modo, se conoce también como "simple". En el modo B o "expandido", algunos dispositivos no pueden utilizarse. algunas direcciones internas ocupan las líneas de entrada/salida. E:1 CPU puede ejecutar un máximo de instrucciones para control de datos, direcciones y líneas entrada/salida. Los dispositivos de "comunicación serial" SPI nos permiten establecer comunicación con una computadora presentación de resultados, así como de poder utilizar el "intérprete de comandos" del microcontrolador. Los 512 Bytes en presentación de resultados, así permiten almecenar las instrucciones del programa nos diseñado, en algunas ocasiones este espacio de memoria no es suficiente para nuestra aplicación. y se hace necesario utilizar comandos del intérprete para mover instrucciones a Podemos establecer v controlar de memoria. comunicaciones con dispositivos externos a través de la interfase SPI. Estas conexiones externas, se llevan a cabo en los puertos paralelos de entrada/salida A. B. C. D y E. El "Timer System". permite medir intervalos de tiempo, controlar el tiempo de señales de salida, medir fácilmente las RPM de un motor, generar pulsos de salida con mucha exactitud, etc. Podemos conectar sensores, muchos tipos de interfases y circuitos analógicos al puerto E. ya que una de las capacidades del microcontrolador nos permite utilizar este puerto como sensor de voltaie.

Fig. 5.2 Microcontrolador 68HC11

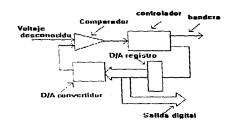

# 5.3 SISTEMA DE CONTROL DEL CONVERTIDOR A/D EN EL PUERTO E

Cuando programamos cualquier dispositivo entrada/salida en el 68HC11E9, activamos internamente un "sistema de control" propio del dispositivo.

El "sensor de voltaje", en el puerto E del 68HC11E9, es un dispositivo controlado por un sistema de "lazo cerrado" (Ver fig. 5.3). Inicialmente, el registro D/A tiene un voltaje de referencia  $V_{\rm rel}$ igual a la mitad del voltaje maximo de conversion  $V_{\rm ax}$ . El comparador. resta un voltaje desconocido  $V_{\rm c}$  (voltaje de entrada al puerto) del voltaje de referencia, si el resultado de la operación es negativo, significa que  $V_{\rm c}$  es mayor que  $V_{\rm rel}$  luego, el controlador comienza a incrementar el valor de  $V_{\rm rel}$  con un factor geometrico de  $(V_{\rm ax}-V_{\rm rel})$  (1/ $Z^{\rm rl}$ ) hasta que el resultado de la resta en el comparador sea positivo, en este momento el valor de voltaje en el registro D/A se convierte en la salida digital.

Si el resultado de la resta entre el voltaje de referencia inicial y el voltaje desconocido es positivo, significa que V, es menor que V, el luego, el controlador comienza a decrementar el valor de V, el con un factor geometrico de V, el luego, el controlador comienza a decrementar el valor de V, el con un factor geometrico de V, el luego, en este momento, el valor de voltaje en el registro D/A se toma como referencia V, el valor de voltaje en el registro D/A se toma como incrementos geometricos (V, el v, el luego, el v, el v,

Fig. 5.3 "sensor de voltaje" en el puerto E

Como podemos darnos cuenta, se requiere un tiempo minimo necesario para convertir el nivel de voltaje en la entrada. Por esta razon, el 65HC11E9 cuenta con un retenedor interno (Ver fig.

5.4) para asegurar una conversión correcta. Este tiempo de conversión, se ha calculado con un valor aproximado de  $64_{18}$ .

Fig. 5.4 "retenedor" de señales analógicas en el puerto E

#### 5.4 LOS REGISTROS EN EL MICROCONTROLADOR 68HC11

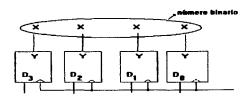

la ejecución de cualquier algoritmo microprocesador o microcontrolador, se llevan a cabo operaciones de almacenamiento y lectura de números binarios. Los cuales, son almacenados por un conjunto de "flip-flops". Un flip-flop es la "unidad minima" de memoria en los sistemas digitales, esto significa, que tienen la capacidad de almacenar un bit información. El flip-flop más común en los sistemas digitales el "tipo D" (Ver fig.5.5), el cual cambia su estado de salida "Y" por una señal de entrada "D" cada vez que recibe un "pulso de reloj". Si diseñamos un "circuito sincrono" con dos o mas flip-flops, podemos almacenar un conjunto de bits que nos representaran un número binario (Ver fig. 5.6). Un circuito de este tipo, se conoce como "registro". En un microcontrolador, los registros pueden transferir su información en forma paralela. serial o retenerla si el "control" en una parte de hardware del microcontrolador depende de la misma.

Fig. 5.5 Table de funcionamiento del "filo-flop D"

Fig. 5.6 Flegistre de cuatre bits, X=8 é 1 légices

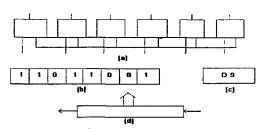

Los registros, pueden representarse con simbologías muy diversas, dependiendo de los detalles a ilustrar. Por ejemplo, si deseamos mostrar en un diagrama electrónico la presencia de un registro, lo podemos hacer mediante la interconexión de pequeñas fig. 5.7(a)) simulando los flip-flops. Si caias (Ver información binaria tiene a su cargo el control de circuitería interna, es aconsejable mostrar el estado de los flip-flops (Ver 5.7 (b))con unos y ceros. Cuando deseamos ilustrar las operaciones transferencia o almacenamiento de una instrucción mnemonica, se utiliza la notación más común. donde el contenido del registro, se indica con un número hexadecimal (Ver. fig.5.7 (c)), finalmente, si deseamos explicar una operación de corrimiento ó transferencia paralela en un registro, hacemos uso de flechas para indicar el flujo de información (Ver fig. 5.7 (d)).

Fig. 5.7 Simbología utilizada para representar un registro

# 5.4.1 REGISTROS DEL MICROPROCESADOR EN EL 68HC11E9

Las operaciones de almacenamiento.transferencia, aritméticas, salto y decisión son ejecutadas por el CPU (microprocesador) del 68HC11E9. Como sabamos, la arquitectura básica de cualquier microprocesador consta de tres partes principales:

- 1) Sistema de control en direcciones, datos y señales.

- Unidad lógica y aritmética.

- 3) Registros.

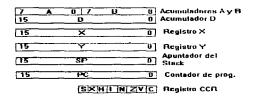

En esta estructura, existe un conjunto de lineas donde se intercambian datos entre la unidad lógica y los registros. De lo contrario, no sería posible llevar a cabo la ejecución de las instrucciones. El CPU en el microcontrolador 68HC11 tiene seis registros en su arquitectura (Ver fig. 5.8), cinco de ellos pueden almacenar datos de 16 bits y uno se encarga de controlar el estado de las "banderas". El registro D puede utilizarse por separado. Es decir, como dos registros de 8 bits independientes A y B para manipulación de datos. Los registros X y Y se utilizan generalmente para almacenamiento de direcciones. Cuando un programación requiere el uso del "Stack", algoritmo de e ì registro SP es utilizado para llevar a cabo direccionamientos indexados. El registro PC almacena el valor de las direcciones enla memoria EEPROM. El contenido de este registro varía de acuerdo a la ejecución del algoritmo. El registro CCR (Condition Code Register) recibe señales que dependen de la ejecución de cada una de las instrucciones, la logica de interrupción y muchas instrucciones de salto dependen de las condiciones presentadas en este registro.

Fig. 5.8 Registros del CPU en el 68HC11E9

# 5.5 LA MEMORIA EN EL MICROCONTROLADOR 68HC11

Una memoria, es un dispositivo que puede almacenar números binarios por medio de señales digitales provenientes de un circuito electrónico. a través de un alambrado físico externo, o por la acción de instrumentos que sean capaces de generar campos eléctricos y magnéticos. Podemos definir a una memoria como un "conjunto de registros" hechos con filp-flops. El acceso a los registros, se hace de manera secuencial, por lo que cada uno tiene un número llamado "direccion" que lo identifica dentro del hardware de la memoria. Toda memoria en un microcontrolador interactúa con otros dispositivos. Esta interacción, puede lograrse con cuatro señales digitales que controlan el flujo de información al chip (Ver fig. 5.9), éstas señales son:

- 1) Bus de direcciones.

- 2) Bus de datos.

- 3) Linea de lectura/escritura.

- 4) Señal de reloj.

El Bus de direcciones, es un grupo de lineas de entrada a la memoria, en donde se lleva a cabo una "selección" de registros. El Bus de datos, es un grupo de líneas entrada/salida en donde los números binarios son leidos é accesados a la memoria de acuerdo con el registro previamente seleccionado. Si algún dispositivo, en comunicación con la memoria va a realizar una operación, la línea de lectura/escritura indicara la naturaleza de ésta. El pulso de reloj. Se encarga de activar al chip de memoria cada vez que se va realizar una transferencia.

Los registros que integran una memoria, pueden representarse como un conjunto de "bloques" unidos entre sí, formando una "pila"(memoria), como se muestra en la figura 5.10, cada bloque contiene un "numero hexaderimal" de 8 bits. Este número, nos representa el dato contenido en un registro de la memoria. El número que identifica cada registro dirección) es un numero hexadecimal de lá bits que se encuentra a la izquierda de cada bloque.

Fig. 5.9 Interacción de una memoria con dispositivos

Fig. 5.18 Representación simbólica de una memoria

# 5.6 PROGRAMACION DE DISPOSITIVOS ENTRADA/SALIDA

Cuando deseamos utilizar algún dispositivo de entrada/salida en el microcontrolador, necesitamos conocer los registros que "controlan su hardware". Estos registros de control, nos permiten habilitar y configurar cada dispositivo para que funcione de una manera específica. En condiciones normales (condiciones de reset), los registros de control se encuentran ubicados en las directiones 1000 a 103F en el espaçio de memoria del microcontrolador (Ver fig. 5.11). Si deseamos cambiar su posición en la pila, podemos hacer uso del registro INIT, el cual intercambia las direcciones de la memoria RAM con las direcciones de los registros.

En el apéndice B, pueden consultarse direcciones, bits y nombres de los 64 registros en el 68HC11E9.

Fig. 5.11 Espacio de memoria en el 68HC11

En ésta tesis utilizamos los siguientes:

- 1) El registro TMSK2 del dispositivo "Contador de 16 bits"

- 2) El registro TFLG2 del dispositivo "Interrupción de reloj"

- 3) El registro ADCTL del dispositivo "Sensor de voltaje"

- 4) El registro OPTION del dispositivo "Sensor de voltaje"

- 5) Los registros ADRX del dispositivo "Sensor de voltaje"

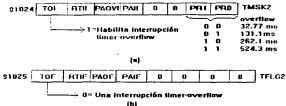

El TMSK2 controla la velocidad de conteo del dispositivo. Es decir, el contador de 16 bits puede incrementar el valor de sus registros de 0000 a FFFF a razones de 32.77,131.1.262.1, y 524.3 milésimas de segundo, según lo indique el registro TMSK2.

Por ejemplo, si deseamos que el 68HC11E9 "realice una tarea determinada" cada 32.77 milésimas de segundo, hacemos que los bits de control TOI. PRI y PRO sean igual a 1.0 y 0 lógicos en el registro de control (Ver fig. 5.12(a)) respectivamente, mediante las instrucciones:

# LDAA 4880 STAA TMSK2

El contador alcanzará su valor máximo en 32.77 ms . es decir el valor de FFFF, entonces enviará una señal al registro TFLG2. la cual, podra ser detectada como un cambio de estado de l a 0 lógico en el bit TOF del registro (Ver fig. 5.12(b)). Para probar el estado de este bit, se utiliza una instruccion de 4 bytes con el siguiente formato:

# etiqueta BRCLR O.X.mascara.saito

en donde etiqueta, es la primera linea (Interrupt Vector) de un segmento de programa en ROM llamado "rutina de interrupcion". O bien, la tarea que deseamos realizar a los 32.77 ms. Esta rutina, se ejecuta solamente cuando se ha presentado la señal en el registro, es decir, cuando su valor cambia de IXXXXXXX a OXXXXXXX, este cambio de estado es posible conocerlo mediante el segmento de instruccion BRCLR O,X, mascara, en donde O,X nos representa la direccion del registro TFLG2 y mascara tiene el valor hexadecimal de 80. En caso de no existir ningun cambio de estado. La rutina de interrupcion en ROM sera ignorada y la ejecucion passara al espacio de memoria en EEPROM indicado por la etiqueta salto.

Fig. 5.12 Bits de control en los registros TMSK2 y 1FLG2

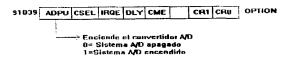

Si utilizamos el sensor de voltaje en el 68HC11E9, para capturar señales analógicas de dispositivos externos conectados al puerto E. Debemos, encender el sistema A/D colocando un l lógico en el bit de control ADPU (Ver fig. 5.13 (a)) del registro OPTION como sique:

#### LDAA #\$80 STAA OPTION

Además, podemos indicarle a nuestro dispositivo, que trabaje de manera contínua sensando cuatro señales analógicas en los bits más bajos del puerto, colocando un 1 lógico en los bits SCAN. MULT y un 0 lógico en los bits CC y CB en el registro de control ADCTL (Ver fig. 5.13 (b)) con las siguientes instrucciones:

#### LDAA #830 STAA ADCTL

Para asegurar un valor correcto de conversión, es aconsejable generar un "retardo" de  $64_{\rm ms}$ , mediante el software:

# LDAB #\$1A RETA DECB BNE RETA

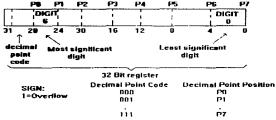

Cada lectura de voltaje, en los bits 0-3 (bits mas bajos) del puerto, tendran un equivalente binario de 8 bits de acuerdo con una resolución de 20mV/bit. Estos numeros binarios, se almacenaran de manera contínua en los registros ADR1, ADR2.ADR3 y ADR4 respectivamente.

fel

CCF SCAN MULTI CO. \$1000 CA Selections - Selecciona el el modo de nibble superior 101 operación ó inferior en el 0=mode simple puerto E 1=modo múltiple 00-bits 0-3 Controla el No. de 01=bits 4-/ conversiones 0=4 conversiones y se detiene 1.-Convicte continuamente

Fig. 5.13 Bits de control en los registros OPTION y ADCTL

# CAPITULO VI. DISERO DEL PROGRAMA PARA CAPTURA DE EVENTOS EN EL MICROCONTROLADOR 68HC11E9

# 6.1 GENERALIDADES

El problema de "capturar eventos", como la mayoría de los problemas electronicos, tiene un grado de dificultad relativa, es decir, depende de nuestra imaginacion, y del hardware, o software que tengamos a nuestra disposición.

Para introducirnos al concepto del mismo, comenzaremos por describir la solución que inicialmente se había logrado con el controlador 2400A-104/AA del registrador patentado por Jhon Fluke MFG. CO. INC. y el alcance de su metodología.

Una vez que tengamos en mente el concepto básico, hablaremos sobre el método de solución obtenido en este proyecto con el 68HC:1E9 y las ventajas que presenta utilizar un microcontrolador de estas características.

# 6.1.1 LOUE SIGNIFICA CAPTURAR UN EVENTO EN TERMINOS DIGITALES?

En términos digitales, capturar un evento se define como la acción de "registrar la aparición de un estado lógico" en un "momento determinado". Para ilustrar esto, supengamos que tenemos un número binario igual a 11011011, grabado como dato en una localidad de un chip de memoria. Si pór alguna razon desconocida, este dato sufre un cambio en alguno de sus bits, es decir a 11010011, entonces podemos decir que el "cuarto bit" en nuestro dato "cambió de la 0" lógico. Posteriormente, si por otra causa desconocida se produce un nuevo cambio de estado como 11110011, podemos afirmar que el "sexto bit" "cambió de 0 a 1" lógico. Si las causas desconocidas continúan presentandose, y nuestro dato sigue cambiando, entonces se produciran más números binarios y mas afirmaciones.

Ahora, supengamos que despues de N causas desconocidas nuestro dato deja de presentar cambios. Entonces, tendriamos un registro de N numeros binarios y N afirmaciones. Por lo tanto, podriamos decir que hicimos una "captura de N eventos".

# 6.1.2 NECESIDAD DE UTILIZAR UN CHIP DE MEMORIA PARA LA CAPTURA DE UN EVENTO

Come hemos visto. La accion de "tedistrar un evento" es equivalente a "escribir un numero finario", donde cada evento es representado por un bit de dicho numero. En sistemas digitales, el unico dispositivo que nos sirve pora alhacenar numeros binarios es un "chip de memoria". Luedo esta debe interactuar con dispositivos externos "registradores de extencia" para que la información que vava a ser accesada a la misma, pueda ser considerada como una secuencia o contine de eventos.

#### 6.1.3 FUNCIONAMIENTO DEL CONTROLADOR 2400A-104/AA

El controlador 2400A-104/AA, fue diseñado especialmente para captura, 32 eventos, es parte de una patente adquirida por la Comisión Federal de Electricidad en el año de 1981. Actualmente, no se encuentra en funcionamiento. En esta tesis, únicamente será expuesto el concepto básico sobre el cual se basó la construcción de esta patente, con la finalidad de mostrar al lector lo que significa "capturar un evento" con sistemas digitales.

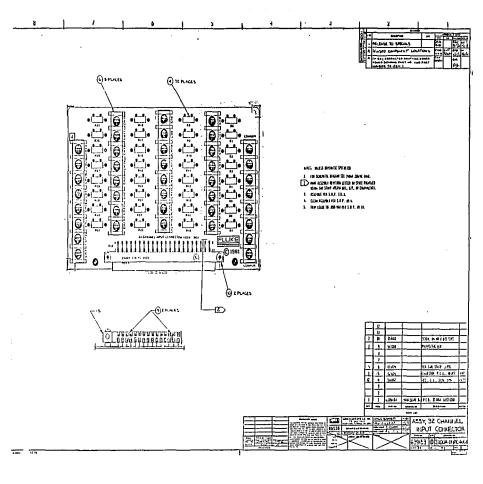

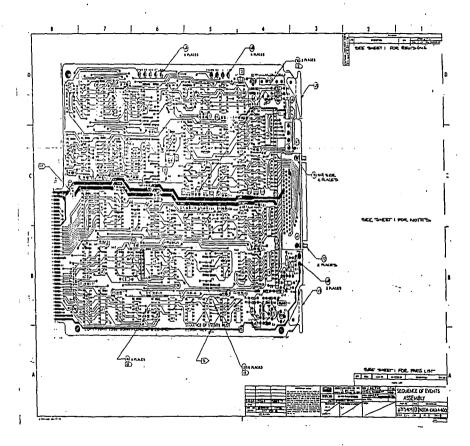

Este controlador, es una tarjeta electrónica con dimensiones físicas de 19.5x 35 centímetros. (Ver diagramas) en donde se encuentran alojados chips lógicos como son compuertas, flip-flops, buffers de tercer estado y una "memoria" entre otros.

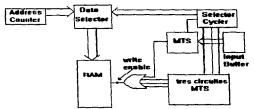

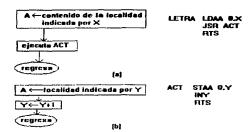

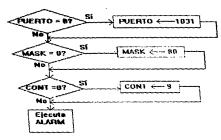

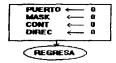

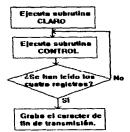

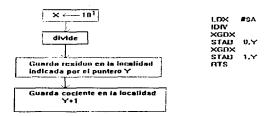

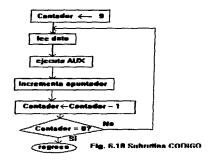

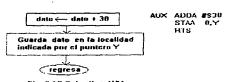

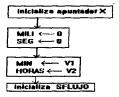

Esta circuitería, se agrupa en cuatro bloques principales (Ver fig. 6.1) que son: