# UNIVERSIDAD NACIONAL AUTONOMA / DE MEXICO

FACULTAD DE INGENIERIA

DISEÑO DE UNA RED DE COMUNICACIONES DISTRIBUIDAS Y CONTROL DE ENERGIA ELECTRICA

T E S I S

QUE PARA OBTENER EL TITULO DE:

INGENIERO MECANICO ELECTRICISTA

P R E 8 E N T A N I

VELAZQUEZ MONTERO JAVIER

VELAZQUEZ MONTERO RICARDO

DIRECTOR DE TESIS:

ING. EDUARDO RAMIREZ SANCHEZ

MEXICO, D. F.

1996

TESIS CON FALLA DE ORIGEN

UNAM – Dirección General de Bibliotecas Tesis Digitales Restricciones de uso

# DERECHOS RESERVADOS © PROHIBIDA SU REPRODUCCIÓN TOTAL O PARCIAL

Todo el material contenido en esta tesis esta protegido por la Ley Federal del Derecho de Autor (LFDA) de los Estados Unidos Mexicanos (México).

El uso de imágenes, fragmentos de videos, y demás material que sea objeto de protección de los derechos de autor, será exclusivamente para fines educativos e informativos y deberá citar la fuente donde la obtuvo mencionando el autor o autores. Cualquier uso distinto como el lucro, reproducción, edición o modificación, será perseguido y sancionado por el respectivo titular de los Derechos de Autor.

QUEREMOS AGRADECER A TODAS AQUELLAS PERSONAS QUE NOS BRINDARON SU COMPRENSIÓN Y APOYO EN EL TRANSCURSO DE NUESTROS ESTUDIOS.

A NUESTROS PADRES, POR LA ORIENTACIÓN BRINDADA DESDE EL INICIO DE NUESTRAS VIDAS, Y POR SUS ENSEÑANZAS, QUE SIRVIERON DE BASE PARA NUESTRA FORMACIÓN.

A NUESTROS HERMANOS, POR SU CONFIANZA Y APOYO.

A NUESTROS MAESTROS, POR COMPARTIRNOS UNA PARTE DE SUS CONOCIMIENTOS.

A NUESTRA ALMA MATER LA UNAM, QUE FUE EL ESCENARIO DE NUESTROS MEJORES TIEMPOS.

# ÍNDICE

| INTRO | DUCC   | ION      |                |                |             |             |        |     | 1  |

|-------|--------|----------|----------------|----------------|-------------|-------------|--------|-----|----|

| CAPÍT | шог    |          | TECNOLOG       | A LONWOR       | ĸ           |             |        |     |    |

|       |        | DUCCIÓ   |                | IN LONGO       |             |             |        |     | 4  |

|       |        |          | OS DE LONV     | IOBK           |             |             |        |     | 6  |

| 1.2   |        |          | uitos Integrad |                |             |             |        |     | 6  |

|       |        |          | sores/Recepto  |                |             |             |        |     | 7  |

|       |        |          | colo LONTALI   |                | IVIX        |             |        |     | 7  |

|       |        |          | Besarrollo L   |                |             |             |        |     | 7  |

| 4.2   |        |          | DNBUILDER      | ONBUILDER      |             |             |        |     | 8  |

| 1.3.* |        |          | de Desarrollo  | LONDIN D       | *n          |             |        |     | 9  |

|       |        |          | Procesador L   |                |             |             |        |     | 11 |

|       | 1.3.2  |          | Emulador Ni    |                |             |             |        |     | 13 |

|       |        |          | Computador     |                |             | ONDUU DE    | ь      |     | 13 |

|       |        |          | Ruteador LC    |                | era (SDC) L | ONDUILUE    | .rv    |     | 14 |

|       | 122    |          | le Expansión l |                | D do Trones | minián/Dooc | naidn  |     | 14 |

|       |        |          | e Expansión i  |                |             |             | pcion  |     | 15 |

| 1.4   |        |          | NBUILDER       | LONDUILDE      | n ue ciluac | ia/Jailua   |        |     | 15 |

| 1.4.5 |        |          | mbiente de De  | searrollo Into | rado I ONE  | ann neo     |        |     | 16 |

|       |        |          | e Desarrollo I |                | Jiado COM   | JUILULIN    |        |     | 17 |

|       | 1.4.2  |          | Compliador     |                |             |             |        |     | 18 |

|       |        |          | Depurador N    |                |             |             |        |     | 16 |

|       | 142    |          | ntas para el l |                | Dad         |             |        |     | 18 |

|       | 1.4.3  |          | Manejador d    |                | Neu         |             |        |     | 18 |

|       |        |          | Analizador d   |                |             |             |        |     | 19 |

|       |        | 1.4.0.2  | Vilamenaci d   | a protocoro    |             |             |        |     |    |

| CAPÍT | ULO II |          | CIRCUITOS      | INTEGRADO      | S NEURO     | N           |        |     |    |

|       |        | ÓIDQUAC  |                |                |             |             |        |     | 20 |

|       |        |          | HARDWAR        | DELOS CI       | RCUITOS I   | NTEGRADO    | OS NEU | RON | 23 |

|       |        |          | s del Procesa  |                |             |             |        |     | 23 |

|       |        | Memoria  |                |                |             |             |        |     | 26 |

|       |        |          | EEPROM         |                |             |             |        |     | 26 |

|       |        | 2222     | RAM estátic    | а              |             |             |        |     | 27 |

|       |        |          | ROM progra     |                |             |             |        | 1 2 | 27 |

|       | 2.2.3  |          | de Memoria     |                |             |             |        |     | 27 |

|       |        | Entrada/ |                |                |             |             |        |     | 31 |

|       |        | 2.2.4.1  | Once termin    | ales bidirecc  | lonales E/S |             |        |     | 31 |

|       |        | 2.2.4.2  | Dos tempori    | zadores/conf   | adores de   | t6 bits     |        |     | 31 |

|       | 2.2.5  | Comunic  | ación de la Re | ed             |             |             | 100    |     | 32 |

|       | 2.2.6  | Sistema  | de Reloj       |                |             |             |        |     | 32 |

|       |        |          | Circuiteria d  | ivisora de rel | oi ·        |             |        |     | 34 |

|       | 2.2.7  |          | es Adicionales |                | •           |             |        |     | 36 |

|       |        | 2.2.7.1  | Modo dormi     | do /despierto  |             |             |        |     | 36 |

|       |        |          | Temporizad     |                |             |             |        |     | 36 |

|       | 2.2.8  |          | l de Servicio  |                |             |             |        |     | 37 |

| *************************************** |                                                                                |    |

|-----------------------------------------|--------------------------------------------------------------------------------|----|

|                                         |                                                                                |    |

| 2.3                                     | ORGANIZACIÓN DEL PROCESADOR                                                    | 38 |

|                                         | 2.3.1 Los Procesadores                                                         | 38 |

|                                         | 2.3.2 Organización de las Memorias                                             | 39 |

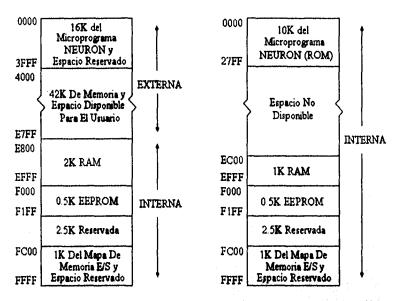

|                                         | 2.3.2.1 Organización de la memoria MC143150                                    | 39 |

|                                         | 2.3.2.2 Organización de la memoria MC143120                                    | 40 |

| 24-                                     | INTERFACE DE ENTRADA/SALIDA                                                    | 41 |

|                                         | 2.4.1 Consideraciones de Hardware                                              | 42 |

|                                         | 2.4.2 Interface Digital                                                        | 43 |

|                                         | 2.4.2.1 Bit E/S                                                                | 43 |

|                                         | 2.4.2.2 Byte E/S                                                               | 43 |

|                                         | 2.4.2.3 Detección de nivel                                                     |    |

|                                         |                                                                                | 44 |

|                                         | 2.4.2.4 Nibble E/S                                                             | 45 |

|                                         | 2.4.3 Funciones de Interface en Paralelo E/S                                   | 46 |

|                                         | 2.4.4 Interface Serial                                                         | 47 |

|                                         | 2.4.4.1 Bit de corrimiento de E/S                                              | 47 |

|                                         | 2.4.4.2 Función NeuroAlambrada de E/S                                          | 47 |

|                                         | 2.4.4.3 Serial de E/S                                                          | 47 |

|                                         | 2.4.5 Función de Interface Temporizador/Contador                               | 47 |

|                                         | 2.4.5.1 Funciones de entrada del temporizador/contador                         | 48 |

|                                         | 2.4.5.2 Funciones de salida del temporizador/contador                          | 52 |

|                                         |                                                                                |    |

|                                         |                                                                                |    |

| CAPÍT                                   | ULO III PROTOCOLO LONTALK                                                      |    |

|                                         | INTRODUCCIÓN                                                                   | 57 |

| <b>U</b>                                | 3.1.1 El Canal Físico                                                          | 59 |

|                                         | 3.1.2 Nombrando, Direccionando y haciendo Rutas                                | 61 |

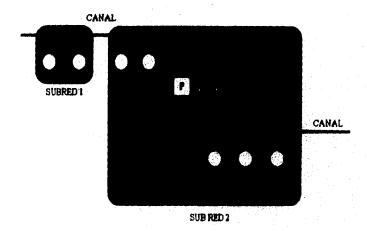

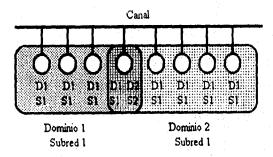

|                                         | 3.1.2.1 Dominio                                                                | 62 |

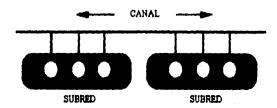

|                                         | 3.1.2.2 Subred                                                                 | 63 |

|                                         | 3.1.2.3 Nodo                                                                   |    |

|                                         |                                                                                | 66 |

|                                         | 3.1.2.4 Grupos                                                                 | 66 |

|                                         | 3.1.2.5 El ID único                                                            | 67 |

|                                         | 3.1.2.6 Los formatos de dirección                                              | 67 |

|                                         | 3.1.2.7 Manejo de redes y generación de direcciones                            | 67 |

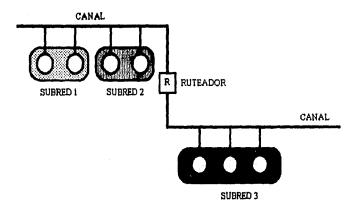

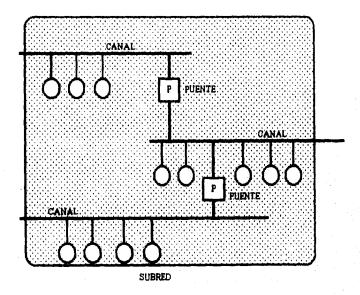

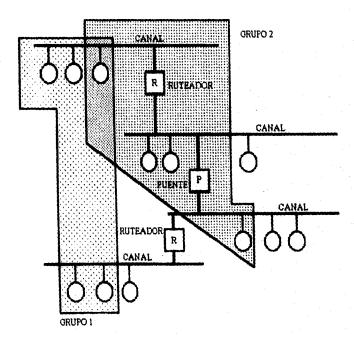

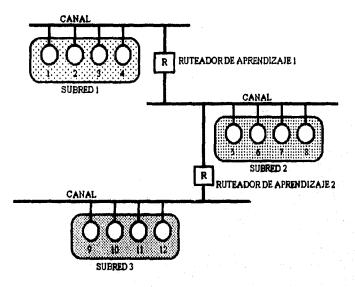

|                                         | 3.1.2.8 Ruteadores y puentes                                                   | 68 |

|                                         | 3.1.3 Servicio de Comunicación                                                 | 71 |

|                                         | 3.1.3.1 Eficiencia, tiempo de respuesta, seguridad y confiabilidad             | 71 |

|                                         | 3.1.3.2 Seleccionando servicios de mensaje para la compatibilidad y eficiencia | 71 |

|                                         | 3.1.3.3 Detección de colisión                                                  | 72 |

|                                         | 3.1.3.4 Prioridad                                                              | 72 |

|                                         | 3.1.3.5 Autenticidad                                                           | 73 |

|                                         | 3.1.4 Temporizadores del Protocolo LONTALK                                     | 74 |

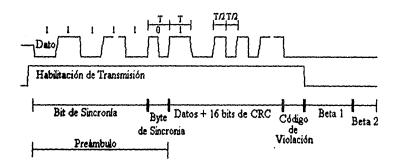

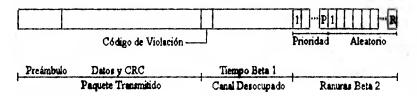

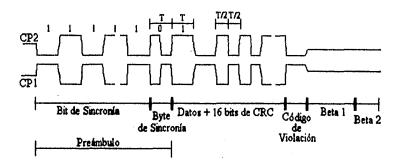

|                                         | 3.1.5 Paquetes Fluyendo al Circuito NEURON                                     | 74 |

|                                         | 3.1.6 Interpretación de los Datos                                              | 76 |

|                                         | 3.1.6.1 Variables de la red                                                    | 76 |

|                                         | 3.1.7 Compatibilidad de la Aplicación                                          | 77 |

|                                         | 3.1.8 Servicio de Protocolo y Parámetros                                       | 77 |

|                                         |                                                                                | 79 |

|                                         | 3.1.9 Limites y Regiones                                                       |    |

|                                         | 3.1.10 La Tabla de Dirección                                                   | 80 |

| 3.2.                                    | MEDICIÓN DEL TIEMPO DE RESPUESTA DEL LONTALK                                   | 80 |

| CAPÍT   |       |            | TRANSMISORES                            | S/RECEPTOR       | ES LONWOI    | RK          |           |            |

|---------|-------|------------|-----------------------------------------|------------------|--------------|-------------|-----------|------------|

|         |       | DUCCIÓ     |                                         |                  |              |             |           | 82         |

| 4.2     |       |            | ON DE LA RED                            |                  |              |             |           | 84         |

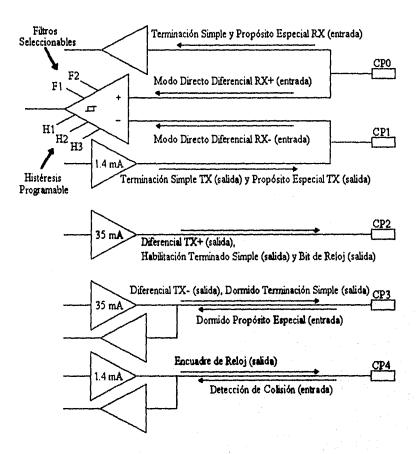

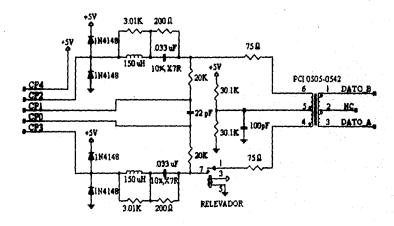

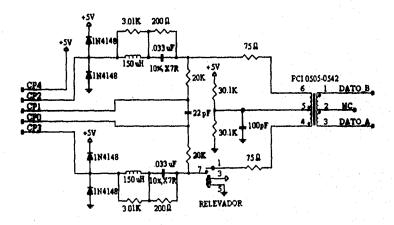

|         | 4.2.1 | Modo Di    |                                         |                  |              |             |           | 85         |

|         |       |            | Modo directo de                         |                  |              |             |           | 86         |

|         |       |            | Modo directo dife                       |                  |              |             |           | 90         |

|         |       |            | Modo directo dife                       |                  | ormador aco  | plado)      |           | 95         |

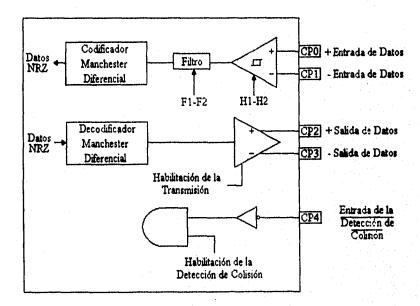

|         |       |            | Transmisor/rece                         |                  |              |             |           | 97         |

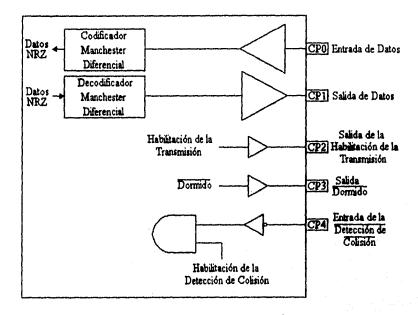

|         | 4.2.2 |            | Propósito Especi                        |                  |              |             |           | 98         |

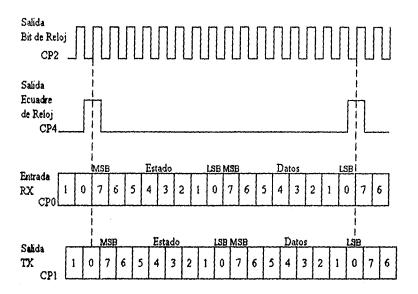

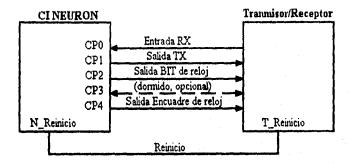

|         |       | 4.2.2.1    | E/S física del mo                       | do de propósil   | o especial   |             |           | 100        |

|         |       | 4.2.2.2    | Estado de los bits                      | 3                |              |             |           | 101        |

| 4.3,-   |       |            | es/receptores                           |                  |              |             |           | 103        |

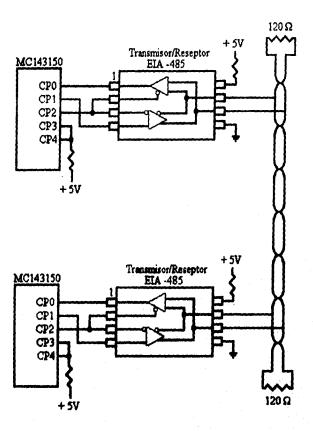

|         | 4.3.1 | Transmi    | sor/Receptor LON                        | BUILDER de F     | ar Trenzado  | )           |           | 103        |

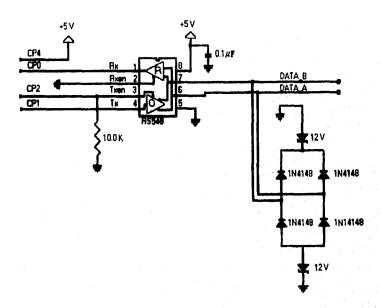

|         | 4.3.2 | Transmi    | sor/Receptor LON                        | BUILDER TP-      | RS485        |             |           | 103        |

|         | 4.3.3 | Transmi    | sor/Receptor LON                        | BUILDER RF       |              |             |           | 104        |

| CAPÍTI  |       |            | DIOPRIO DE LA C                         | TED LIGANIDO     | LONDUUR      | ED          |           |            |

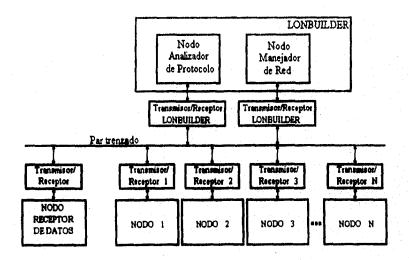

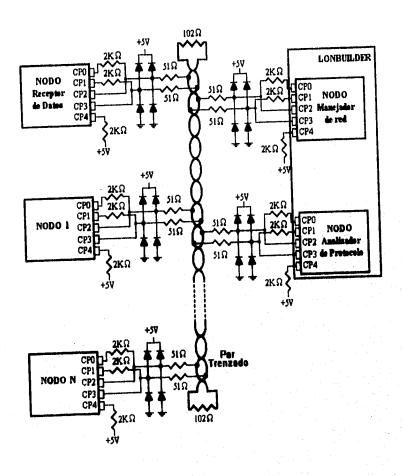

|         |       | DUCCIÓ     | DISEÑO DE LA F                          | KEN NOWNDO       | FOMBUILD     | EK          |           | 405        |

| 0.1.    |       |            |                                         |                  |              |             |           | 105        |

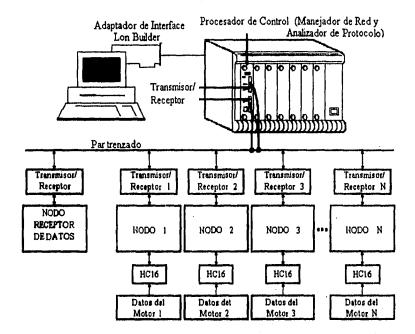

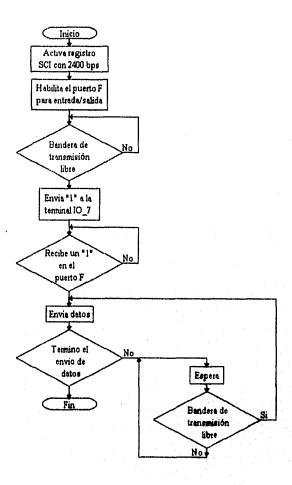

|         | 5.1.1 | Definition | del Proyecto<br>Transmisión de I        |                  | 010 -1       | LONIMORY    |           | 105        |

|         |       |            | Red LONWORK                             |                  | C to at nodo | LONWORK     |           | 106<br>106 |

|         |       |            | Visualización de                        |                  |              |             |           | 107        |

|         | E 4 2 |            |                                         | ios datos        |              |             |           | 107        |

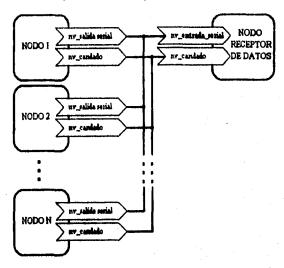

|         | 5.1.2 |            | llo del Proyecto                        | landaa           |              | a., 6.,aldm |           | 107        |

|         |       |            | Identificación de<br>Definición de la i |                  |              |             |           | 107        |

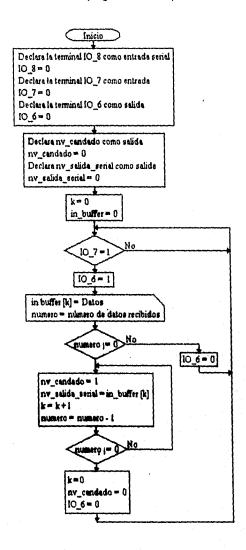

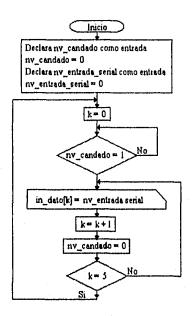

|         |       |            | Los programas d                         |                  |              |             | 1         | 108        |

|         |       | 5.1.2.3    | Depuración y pru                        | ie ia aplicación | de cada nos  | 10          |           | 114        |

|         |       |            | Instalación de los                      |                  |              | 10          |           | 114        |

|         | E 4 2 |            | sor/Receptor utiliza                    |                  | ia ieu       |             |           | 115        |

|         | 5.1.5 | Hansin     | sol/Neceptor utiliza                    | auo              |              |             |           | 110        |

| CAPÍTI  | ULO V | 1          | INTERFACE ENT                           | FRE EL CIRCL     | JITO INTEGI  | RADO NEURO  | N Y MCU'S | i · .      |

| 6.1     | INTRO | DUCCIÓ     | N                                       |                  |              |             |           | 117        |

|         | 6 1.1 | Interface  | en Paraielo                             |                  |              |             |           | . 117      |

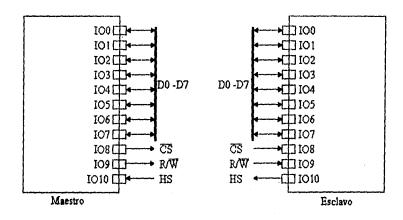

|         |       | 6.1.1.1    | Modo maestro/er                         | sclavo A         |              |             |           | 117        |

|         |       | 6.1.1.2    | Modo maestro/es                         | sclavo B         |              |             |           | 118        |

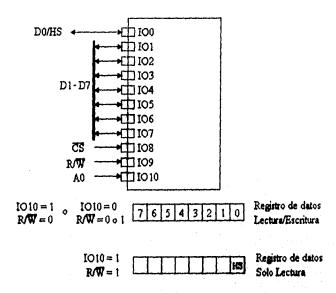

|         |       | 6, 1, 1, 3 | Paso de testigo                         |                  |              |             |           | 119        |

|         |       | 6.1,1.4    | Protocolo de salu                       | udo -            |              |             |           | 120        |

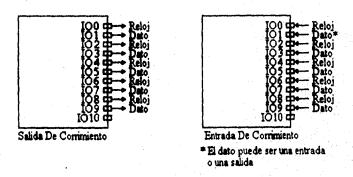

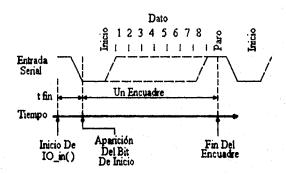

|         |       |            | orrimiento de Entre                     |                  |              |             |           | 120        |

|         | 6.1.3 | Función    | Neuro Alambrada                         | de Entrada/Sa    | lida         |             |           | 121        |

|         |       | 6,1.3.1    | Modo maestro N                          | euroAlambrad     | 0            |             |           | 121        |

|         |       | 6.1.3.2    | Modo esclavo No                         | euroAlambrado    |              |             | 100       | 121        |

|         |       | Interface  |                                         |                  |              |             |           | 121        |

| 6.2     | ELEC  | CIÓN DE    | LA INTERFACE D                          | E LA RED LO      | NWORK        |             |           | 122        |

|         |       |            |                                         |                  |              |             | State St. |            |

| CONC    | USIO  | NES        |                                         |                  |              |             |           | 127        |

|         |       |            |                                         |                  |              |             |           |            |

|         |       |            |                                         |                  |              |             |           |            |

| APÉNI   | DICE  |            |                                         |                  |              |             |           | A-1        |

|         |       |            |                                         |                  |              |             |           | 1.5        |

|         |       |            |                                         |                  |              |             |           |            |

| QIBI 16 | VODAL | ia ·       |                                         |                  |              |             |           |            |

### INTRODUCCIÓN

La tecnología ha jugado un papel más que relevante y estratégico, indispensable para dar continuidad a nuestro entorno. La ingeniería, como creadora de la infraestructura tecnológica, ha tenido que avanzar a pasos agigantados, tratando de resolver los problemas que las necesidades de la sociedad han ido planteando.

Dentro del marco de la apertura económica, con el Tratado de Libre Comercio de Norteamérica, se observa claramente que las empresas mexicanas deben ser lo suficientemente competitivas para no perecer ante compañías extranjeras y nacionales. El alto nivel de tecnologia de empresas extranjeras, es la base fundamental para lograr niveles de calidad elevados en sus productos, reducción de gastos de operación, administración, así como un mayor aprovechamiento de las materias primas.

Es necesario, por lo tanto, que en México se apliquen tecnologías de punta para poder competir con los mercados internacionales. El papel de los ingenieros en este momento es crucial para el ámbito mexicano, ya que debemos ser capaces de aprovechar la infraestructura actual, y optimizar la utilización de los recursos disponibles, apoyados de la nueva tecnología que nos llega de los diferentes países, primordialmente de Estados Unidos.

Los microprocesadores han hecho posible muchos avances científicos, industriales y comerciales que no se hubiesen podido lograr por otros medios. A lo largo de los años hemos presenciado cómo se ha ido asumiendo, dirigiendo y absorbiendo el fenómeno microprocesador, y el hecho es que hoy es imposible prescindir de él en la realización de un diseño digital no trivial.

Por otro lado, en los últimos años la industria de las redes de gran cobertura ha madurado y es hoy por hoy un sector estable. Las redes locales, por el contrario, constituyen un campo relativamente nuevo. La tecnología en la que se basan, empezó a adquirir interés a mediados de los setenta, y es en la actualidad uno de los sectores de más rápido crecimiento dentro de la industria de comunicaciones.

La automatización de edificios, fábricas, máquinas, vehículos, etc. han sido de gran importancia en la vida moderna. La tecnología LON (redes de operación local) ofrece poderosos medio para implementar una variedad de sistemas distribuidos, los cuales sensan, monitorean y controlan, además de otras aplicaciones. LONWORK es una colección de herramientas y componentes, los cuales pueden ser utilizados para aplicaciones de construcción específica LON.

En México solo existen un par de estaciones de desarrollo para la construcción de LON (redes de operación local), contando la Unidad de Diseño Electrónico de la UNAM con una de estas estaciones de desarrollo. Por lo que, en México, no se cuenta con mucha información sobre esta nueva tecnología. Por tal motivo y para poder familiarizarnos con esta tecnología, es necesario dar a conocer los componentes que integran la tecnología LON, su funcionamiento, así como sus principales características. Además, de que posteriores trabajos que deseen utilizar esta tecnología, cuenten con información suficiente para poder realizarlos.

Para poder alcanzar los objetivos anteriormente expuestos el trabajo se divide en siete capítulos, de los cuales cuatro de ellos se enfocan exclusivamente a dar una explicación de la tecnología LON (componentes que lo integran, funcionamiento, principales características, etc.).

En el capítulo 1 "Tecnologia LONWORK", Se describen las herramientas y componentes necesarios para la fabricación de redes LON, así como la comparación entre las redes LON y LAN.

El capítulo 2 "Circuitos Integrados Neuron", describe los Circuitos Integrados Neuron, que son la base de la tecnologia LON. Como están organizados, como funcionan, cuales son sus componentes principales, y como interactuan entre ellos son algunas de los puntos que se exponen.

Capitulo 3 "Protocolo LONTALK", en este capitulo se explica el funcionamiento del protocolo que utiliza la tecnologia LON, así como algunos aspectos referentes al direccionamiento y ruteo de los canales de comunicación. Se explican también algunos servicios que proporciona este protocolo.

Capítulo 4 "Transmisores/Receptores LONWORK", se enfoca principalmente en dar algunas alternativas para el uso de transmisores/receptores, así como alternativas para el uso de diferentes medios de comunicación. Y los modos en los que puede trabajar el puerto de comunicaciones del Circuito Integrado Neuron.

En los dos capítulos restantes se tiene por objetivo el diseño y la construcción de una red de comunicaciones distribuidas y control de energia eléctrica utilizando la tecnología LONWORK

En el capítulo 5 "Diseño de la red usando LONBUILDER" se tiene por objetivo dar a conocer el diseño del sistema, tomando como referencia lo descrito en los capítulos anteriores.

Capítulo 6 "Interface entre Circuitos Integrado Neuron y MCU's", tiene por objetivo explicar las diferentes interfaces que pueden realizarse entre un Circuito Integrado Neuron y los MCU's (microcontroladores). También, se explica la inteface realizada entre los microprocesadores HC16 y el Circuito Integrado Neuron, necesaria para el desarrollo del proyecto.

Finalmente, se concluye con una serie de reflexiones, resultado del desarrollo de este trabajo, y se incluye un apéndice con las principales diferencias que existen entre el lenguaje de programación C y el lenguaje de programación NEURON C utilizado en este trabajo.

# CAPÍTULO I TECNOLOGÍA LONWORK

#### 1.1 INTRODICCIÓN

La tecnología LON (Local Operating Network - redes de operación local) ofrece medios poderosos para implementar una variedad de sistemas distribuidos, los cuales sensan, monitorean y controlan, además de otras aplicaciones. LONWORK es una colección de herramientas y componentes, los cuales pueden ser utilizados para aplicaciones de construcción especifica de LONs. LONWORK puede ser usado dentro de una gran variedad de caminos para la automatización de fábricas, vehículos, casas y maquinaria a un bajo costo.

Las LONs constituye una clase de tecnología en la cual se incluyen dispositivos inteligentes, en donde la comunicación entre ellos es posible gracias a una variedad de medios de comunicación que utilizan un protocolo estándar. En este sentido, una LON es similar a una red de área local (LAN - Local Area Network) que permite la comunicación entre computadoras. La tecnología LON soporta un sistema distribuido, esto permite que no sea necesario un sistema de control central.

Lo que distingue a LONs de LANs es su propósito. LANs son diseñados para mover datos (tales como documentos, imágenes y base de datos) entre computadoras. Una ejecución de LAN es vista en términos de su rendimiento efectivo, por lo general medido en Megabits transmitidos por segundo. Una LON está diseñada para sensar y controlar mensajes los cuales son generalmente muy cortos, conteniendo comandos e información de estados que habilitan la acción. La ejecución de LON es vista en términos del tiempo de respuesta y las operaciones completadas por segundo.

La compañía Echelon, generadora de la tecnología LON, tiene una amplia experiencia en tecnología de comunicaciones, tecnología de control y tecnología en semiconductores, dando como resultado una gran colección de componentes y herramientas ilamadas LONWORK, los cuales, son fáciles de instalar y flexibles. Además diferentes componentes (compatibles con LONWORK) podrían elegirse para el diseño de productos basados en LONWORK.

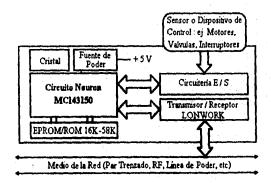

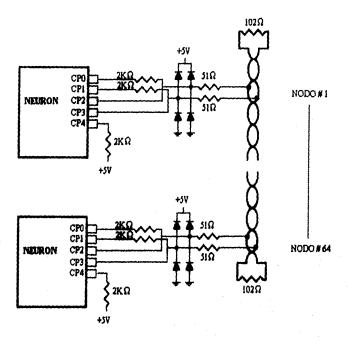

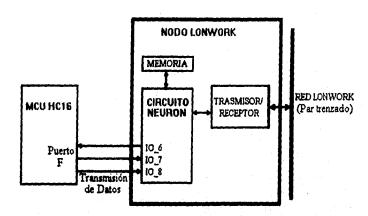

La combinación lógica de los dispositivos de las LONs, que cuentan con inteligencia artificial y dispositivos de comunicación, son llamados nodos. Un nodo puede ser un dispositivo alambrado semejante a un interruptor, un sensor analógico/digital o a un actuador. Los nodos LONWORK generalmente consisten de los siguiente:

- Uno o más sensores o actuadores y el hardware asociado a la aplicación.

- Un circuito integrado llamado NEURON.

- Un transmisor/receptor que proporciona el enlace para la comunicación.

Ver figura 1.1.

Figura 1.1 Diagrama de Bioques de un Nodo Típico

#### 1.2 LOS ELEMENTOS DE LONWORK

La tecnología LONWORK es una plataforma completa para implementar sistemas de redes con un control distribuído. Estos sistemas consisten de dispositivos inteligentes o nodos que interactuan con su medio ambiente, y se comunican entre ellos a través de una gran variedad de medios de comunicación, usando mensajes basados en un protocolo de control. LONWORK incluye todos los elementos requeridos para diseñar, construir y mantener LONs: los Circuitos Integrados NEURON y el transmisor/receptor LONWORK que forman la parte física del nodo; el protocolo LONTALK que proporciona una comunicación formal y los fundamentos de las operaciones internas entre los productos; y un banco de desarrollo LONBUILDER que habilita un desarrollo rápido de productos y redes.

#### 1.2.1 Los Circuitos Integrados NEURON

El corazón de cada nodo es un miembro de la familia de Circuitos Integrados NEURON, ya sea el NEURON 3120 o el NEURON 3150. Ambos proporcionan una solución para las comunicaciones, la entrada/salida y el control para muchas aplicaciones; El NEURON 3150 también soporta memoria externa para aplicaciones más complejas. Ambos dispositivos contienen tres CPUs idénticos de 8 bits; de los cuales dos son dedicados a la comunicación, y el tercero está dedicado al código de la aplicación.

El NEURON 3120 contiene memorias ROM, RAM y EEPROM. El NEURON 3150 contiene memorias RAM y EEPROM y provee una interface de memoria externa. Ambos contienen 11 terminales bidireccionales de entrada/salida para la interface de aplicaciones de hardware, una interface de 5 terminales para un transmisor/receptor LONWORK, un temporizador/contador, y muchas otras características, incluyendo un número serial de 48 bit permanentemente programado dentro de cada dispositivo.

Otras caracteristicas únicas de los Circuitos NEURON es que están microprogramados (firmware). El NEURON 3120 contiene dentro de 10k de memoria ROM (o en los primero 10 K de memoria externa direccionada para el NEURON 3150) el microprograma NEURON. El microprograma implementa el llenado del protocolo de comunicaciones LONTALK y maneja todos los detalles de la lista de tareas, manejo de entrada y salida, manejo de la red, comunicación, y control interno.

#### 1.2.2 Transmisores/Receptores LONWORK

Una característica de las redes LONWORK es su habilidad para comunicarse a través de diferentes medios en una red específica.

Los primeros productos desarrollados por Echelon, son un grupo de módulos que permiten la comunicación de los circuitos NEURON sobre lineas de potencia, radio frecuencia, e instalación de alambres eléctricos de par trenzado. Además, la flexibilidad de comunicación de los puertos de los circuitos NEURON habilitan al desarrollador para la implementación de un transmisor/receptor para otros medios de comunicación (ej. coaxial, fibra óptica, etc.) para necesidades especiales que se tengan.

#### 1.2.3 El Protocolo LONTALK

Echelon utiliza LONTALK como el esqueleto para toda la comunicación que ocurra sobre LON. El protocolo LONTALK es versátil y soporta un rango amplio de aplicaciones. LONTALK es definido por el internacional Standard Organization (ISO) y el Open Systems Interconection (OSI) que se utiliza como modelo de referencia.

El protocolo LONTALK está diseñado para proveer la antrega de mensajes cortos de control a través de una variedad de medios de comunicación. Con el apropiado transmisor/receptor, los nodos pueden comunicarse entre si a través de algún medio, como par trenzado, linea de potencia y radio frecuencia.

Las LONs que siguen el protocolo LONTALK son llamados redes LONWORK, y los nodos que utilizan el protocolo LONTALK son llamados nodos LONWORK, o simplemente nodos.

#### 1.2.4 Banco de Desarrollo LONBUILDER

El banco de desarrollo LONBUILDER es un medio que provea las herramientas necesarias para crear aplicaciones LONWORK. Una aplicación LONWORK consiste de dispositivos inteligentes, o nodos, que son conectados con uno o más medios de comunicación y que se comunican entre ellos usando el protocolo LONTALK. El sistema LONBUILDER es usado para programar nodos, para enviar

mensajes, para cambiar diferentes condiciones, y para tomar decisiones en respuesta a mensajes que ellos reciben. Como ya se había mencionado cada nodo contiene: un circuito NEURON, el cual es un dispositivo programable que implementa el protocolo LONTALK y ejecuta la función de aplicación deseada del nodo; un transmisor/receptor, para proveer la interface mecánica y electrónica entre los circuitos NEURON de los nodos y el medio de comunicación; y circuitos para conectar el circuito NEURON a dispositivos de entrada/salida como desplegadores, etc.

#### 1.3 EI SISTEMA LONBUILDER

El sistema LONBUILDER facilita el desarrollo independiente de cada uno de los nodos cuya función puede ser simple o compleja, y la integración de estos nodos dentro de aplicaciones LONWORK, los cuales pueden ejecutar tareas más complejas y sofisticadas.

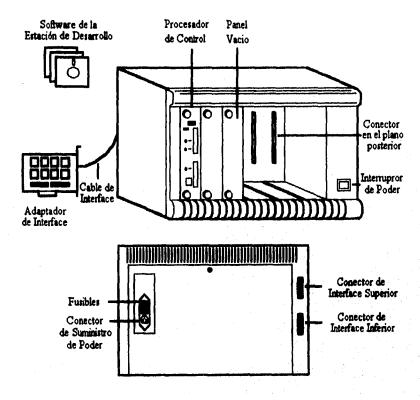

El banco de desarrollo LONBUILDER (ver figura 1.2) consiste de una integración entre hardware y software, el cual opera en conjunto con una computadora personal. Durante el desarrollo, una aplicación LONWORK típica crece desde una red de dos nodos hasta una red de varios nodos. El sistema LONBUILDER ayuda a la expansión de nodos, y se compone de:

- La estación de desarrollo LONBUILDER

- Las terjetas procesador LONBUILDER

- Las tarjetas de expansión LONBUILDER

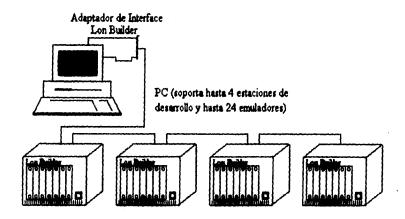

Sobre una simple PC, el sistema LONBUILDER provee un medio ambiente de desarrollo que puede crecer desde un par de aplicaciones emuladas de nodos, residentes en la estación de desarrollo, hasta un sistema distribuido de 24 nodos emulados y 256 nodos remotos.

Figura 1.2 Banco de Desarrollo LONBUILDER

#### 1.3.1 Estación de Desarrollo LONBUILDER

La estación de desarrollo LONBUILDER incluye:

- Un recinto con suministro de poder y conectores de hardware que soporta hasta seis tarjetas procesador opcionales.

- Un Procesador de Control LONBUILDER, el cual proporciona el control para una estación de desarrollo, manejando la comunicación de comandos y datos entre un adaptador de interface LONBUILDER (instalada en una PC) y las tarjetas procesador (instaladas en la estación de deserrollo). Un cable de interface enlaza el Procesador de Control LONBUILDER al Adaptador de Interface LONBUILDER. El Procesador de Control incluye los nodos manejador de red y analizador de protocolo, los cuales son nodos dedicados, usados para el software Manejador de Red LONBUILDER y software Analizador de Protocolo LONBUILDER.

#### En la figura 1.3 se muestra la Estación de Desarrollo LONBULDER

Figura 1.3 Estación de Desarrollo LONBUILDER

Un adaptador de interface LONBUILDER instalado en la PC provee una alta velocidad de comunicación entre el software de la PC y las tarjetas procesador en la estación de desarrollo. Hasta cuatro estaciones de desarrollo pueden ser conectadas en una PC, soportando un total de 24 tarjetas procesador, estas conexiones se muestran en la figura 1.4.

Figura 1.4 Conexión de Estaciones de Desarrollo

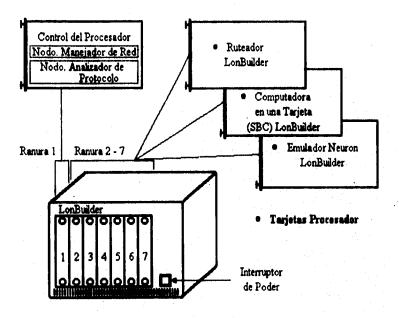

En el banco de desarrollo LONBUILDER existen sels ranuras que pueden alojar algunas mezclas de las tarjetas procesador LONBUILDER.

#### 1.3.2 Tarjetas Processdor LONBUILDER

Existen tres tipos de tarjetas procesador LONBUILDER: Emulador NEURON LONBUILDER, Computadora en una tarjeta (SBC) LONBUILDER, y Ruteador LONBUILDER.

- Emulador NEURON para la depuración del software y hardware de los prototipos.

- LONBUILDER SBC (computadora en una tarjeta) para el uso en el desarrollo con una PC o remotamente con un transmisor/receptor y utilizando una fuente de alimentación externa.

- Ruteador LONBUILDER para proporcionar comunicación entre dos diferentes cansles o medios de comunicación (ej. instalación de par trenzado y radio frecuencias).

Las tarjetas procesador pueden aceptar dos tipos opcionales de tarjetas de expansión. Las tarjetas de expansión pueden ser transmisores/receptores LONBUILDER, tarjetas de entrada/salida LONBUILDER, transmisores/receptores, o interface entrada/salida.

En la figura 1.5 se muestran las tarjetas procesador y en la tabla 1-1 algunas características de éstas.

Figura 1.5 Tarjetas Procesador LONBUILDER

| Tabla 1-1 | Componentes | de la tarieta procesador l | ONBUILDER |

|-----------|-------------|----------------------------|-----------|

|           |             |                            |           |

| Terjeta<br>Procesador | Procesadores                 | Cantidad de<br>Memoria                                    | Aceptación opcional de tarjetas de expansión transmisor/receptor | Aceptación<br>opcional de<br>tarjetas de<br>expansión<br>de E/8 | Soporta la<br>depuración<br>NEURON C |

|-----------------------|------------------------------|-----------------------------------------------------------|------------------------------------------------------------------|-----------------------------------------------------------------|--------------------------------------|

| Emulador              | Un circuito<br>NEURON 3150   | 64 KB de<br>aplicación<br>64 KB de<br>control             | Si<br>una tarjeta                                                | Si<br>una tarjeta                                               | Si                                   |

| SBC                   | Un circuito<br>NEURON 3150   | 64 KB de<br>aplicación                                    | Si<br>una tarjeta                                                | Si<br>una tarjeta                                               | No                                   |

| Ruteador              | Dos circuitos<br>NEURON 3150 | 32 KB de<br>sistema para<br>el circuito<br>NEURON<br>3150 | Si<br>dos tarjetas                                               | Na                                                              | No                                   |

#### 1.3.2.1 Emulador NEURON LONBUILDER

Los nodos son inicialmente desarrollados en el Emulador NEURON LONBUILDER, una tarjeta procesador que permite la depuración del software usando el depurador NEURON C. El emulador incorpora un circuito integrado NEURON 3150 con 64 KB de RAM. También incluye una memoria adicional de 64 K para usaria con el depurador en el control del programa de la aplicación.

El emulador siempre reside en la estación de desarrollo, du...de proporciona el soporte de hardware para cargar la aplicación, hacer un punto de interrupción en el correr del programa de la aplicación, realizar pasos simples en el programa, hacer reinicio/comenzó/paro, y utilizar una memoria de protección de lectura/escritura. El emulador también proporciona un controlador de porcentaje de reloj de software el cual puede ser de 10 MHz, 5 MHz, 2.5 MHz, 1.25 MHz, y 625 KHz. El software LONBUILDER puede emular el mapa de memoria del circuito NEURON 3120 sobre los emuladores NEURON 3150.

#### 1.3.2.2 Computadora en una tarjeta (SBC) LONBUILDER

El SBC LONBUILDER es una computadora en una tarjeta incorporando un circuito NEURON 3150 con 64 KB de memoria no volátil RAM. Después de depurar la aplicación de software sobre el emulador, éste puede ser bajado hacia un SBC. El SBC puede ser instalado en la estación de desarrollo o usado remotamente con una fuente de poder externa. El SBC acepta igual número de tarjetas de expansión que el emulador, permitiendo probar el prototipo.

#### 1.3.2.3 Ruteador LONBUILDER

El Ruteador LONBUILDER es una tarjeta procesador que contiene dos circuitos NEURON 3150. Cada ruteador soporta dos tarjetas de expansión transmisor/receptor opcionales para proporcionar rutas entre dos comunicaciones o canales. Los ruteadores pueden ser instalados de la siguiente forma:

- Ruteador de aprendizaje, el cual monitorea el tráfico de redes para aprender la topología de la red. El ruteador utiliza la información de la topología de la red para seleccionar paquetes de rutas entre canales.

- Ruteador configurado, el cual utiliza tablas de rutas basadas en la configuración de la red para la ruta de los paquetes entre canales. El manejador de red LONBUILDER configura automáticamente las tablas de rutas.

- Puente, el cual transmite todo el paquete entre los dos canaies conectados sobre el dominio en el cual el puente es instalado.

- Repetidor, el cual transmite todo el paquete entre los dos canales conectados sin estimar el dominio en el cual el repetidor es instalado.

Un ruteador LONBUILDER puede ser instalado en la estación de desarrollo o usado remotamente con una fuente de poder externa.

#### 1.3.3 Tarjeta de Expansión LONBUILDER de Transmisión/Recepción

Las tarjetas procesador requieren un tarjeta de expansión transmisor/receptor para proporcionar la interface física de una comunicación entre canales. Los transmisores/receptores LONBUILDER son útiles para redes con par trenzado y radio frecuencia. Se puede desarrollar transmisores/receptores con un diseño propio.

Las tarjetas transmisor/receptor LONBUILDER provee la interface física entre un Emulador, SBC, Ruteador, o procesador de control y un canal de la red.

#### 1.3.4 Tarjeta de Expansión LONBUILDER de Entrada/Salida

Las tarjetas procesador LONBUILDER acepta una segunda tarjeta de expansión además de una tarjeta de expansión transmisor/receptor. Hay diferentes opciones para desarrollar los prototipos de interface entrada/salida:

- Desarrollar una tarjeta de expansión entrada/salida.

- Usar la tarjeta de entrada/salida LONBUILDER para desarrollar el prototipo de interfaces entrada/salida. La tarjeta de entrada/salida LONBUILDER incluye memoria intermedia (buffers) para las señales entrada/salida del circuito NEURON y prototipos de hardware.

- Utilizar la tarjeta de interface de aplicación LONBUILDER para realizar la interface con dispositivos de entrada/salida y nodos externos para la estación de desarrollo.

#### 1.4 SOFTWARE LONBUILDER

El Software LONBUILDER proporciona herramientas para la programación de la aplicación, también proporciona herramientas manejadoras de red que conocen las necesidades del desarrollo de la aplicación LONWORK.

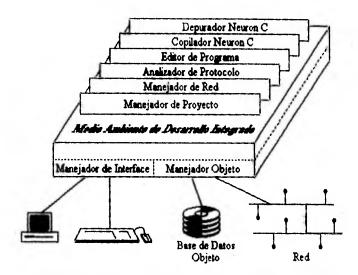

Las herramientas para la programación de la aplicación LONBUILDER incluyen el manejador del proyecto, editor, compilador, y depurador del programa. Todas estas herramientas están enlazadas a través de un Medio Ambiente de Desarrollo Integrado (IDE), ilustrado en la figura 1.6.

Figura 1.6 Herramientas para la Programación de la Aplicación

El banco de desarrollo LONBUILDER provee este poderoso juego de herramientas integradas de software:

- El Medio Ambiente de Desarrollo Integrado LONBUILDER incluye una base de datos, un manejador de proyecto, y un editor integrado.

- El equipo de desarrollo NEURON C contiene el compilador NEURON C y el depurador de programa NEURON C.

- El Manejador de Red LONBUILDER permite programar para cargar, configurar, y controlar redes LONWORK.

- El Analizador de Protocolo LONBUILDER permite la programación para el monitoreo y diagnóstico del tráfico de red.

#### 1.4.1 Medio Ambiente de Desarrollo Integrado LONBUILDER

El medio ambiente de desarrollo integrado LONBUILDER (IDE) soporta programas de la aplicación para automatizar el ciclo de desarrollo, proporcionando un armazón común para las herramientas de software. El IDE básico incluye lo siguiente.

- Base de datos enfocada a objetos, el cual almacena el valor de los parámetros de uso definible de la aplicación, ruteador, y nodos manejadores de redes.

Estos valores son repartidos por todas las herramientas de software LONBUILDER.

- Navegador, el cual simplifica viendo y camblando la base de datos. Un gran proyecto puede consistir de cientos de objetos. La definición de estos objetos son fácilmente manejados usando el navegador.

- Manejador de proyecto, el cual maneja la configuración de los nodos definidos dentro de la base de datos y habilita para la construcción de una aplicación basada en los valores de la base de datos. Los manejadores de objetos invocan opcionalmente al compilador NEURON C, para compilar los programas de la aplicación, y las herramientas de manejo de la red para construir la información de la configuración de la red, cargar la aplicación y empesarla.

- Editor Integrado para crear programas de aplicaciones y para llamar a el manejador de proyectos. El editor está integrado al compilador NEURON C, los errores encontrados con el compilador son fáciles de hallar y corregir.

- Herramientas adicionales, las cuales pueden ser sumadas por el IDE básico, Incluyendo los componentes del equipo de desarrollo NEURON C.

#### 1.4.2 Equipo de Desarrollo NEURON C

El equipo de desarrollo NEURON C incluye el compilador NEURON C y el depurador NEURON C.

Et NEURON C (un lenguaje de alto nivel de programación basado en el lenguaje ANSI C) permite al desarrollador una producción de aplicaciones rápida que involucra el listado, la comunicación nodo a nodo, y la interface de hardware. La aplicación del NEURON C por otra parte, cuenta con el microprograma (firmware) para manejar e implementar los detalles en el listado, la comunicación, y la interface de hardware. De este modo, el microprograma proporciona un sistema operador de red para ejecutar el programa de la aplicación y liberar al desarrollador de tratos con bajo nivel, detalles de comunicación y el proceso de entrada/salida. Combinando el NEURON C y el microprograma NEURON se facilita la elaboración de programas compactos que son fáciles de desarrollar y de fácil mantenimiento.

Las redes LONWORK proveen la capacidad de conectar una variedad de nodos que realizan un control distribuido, sensan, realizan identificaciones, además de otras aplicaciones. El nodo usa uno o más medios de comunicación y se comunica con algún otro dispositivo usando un protocolo común, LONTALK. Los dispositivos sobre la red LONWORK son programados en NEURON C.

#### 1.4.2.1 Compilador NEURON C

El compilador NEURON C, toma de la entrada NEURON C, el código fuente almacenado sobre la PC, y genera el código que se almacena en la base de datos para después ser cargada a uno o más nodos. El compilador NEURON C genera códigos para el circuito NEURON 3120 y el circuito NEURON 3150.

#### 1.4.2.2 Depurador NEURON C

El depurador NEURON C corre sobre una PC mientras depura la corrida de aplicación NEURON C sobre uno o hasta 24 emuladores NEURON. El depurador NEURON C proporciona una vista en la pantalla de la PC de los programas de aplicación ejecutados sobre los emuladores NEURON. Utilizando esta vista en la pantalla, se puede colocar un punto de ruptura en el programa, empezar y parar la ejecución del programa y realizar simples pasos a través del programa. También se puede evaluar y modificar variables del programa usando nombres símbólicos NEURON C. El depurador NEURON C proporciona visibilidad dentro de la ilamada a la pila del programa, proporcionando comandos para visualizar el llamado a la pila y cambiar el contexto corriente para alguna función dentro de la pila.

#### 1.4.3 Herramientas para el Manejo de la Red

Las herramientas para el manejo de la red LONBUILDER incluyen el manejador de red LONBUILDER y el analizador de protocolo LONBUILDER. Estas herramientas son usadas para definir, configurar, cargar, monitorear, y controlar múltiples nodos en una red de desarrollo.

#### 1.4.3.1 Manejador de red.

El manejador de red LONBUILDER proporciona las herramientas para definir, configurar, cargar, y controlar nodos LONWORK y redes. El manejador de red usa la interface de red incluida en el Procesador de Control de la estación de desarrollo para enviar comandos de manejo de red hacia otros nodos dentro de la misma red.

El manejador de red es usado para realizar lo siguiente:

- Definir la configuración física de los nodos para asociar el hardware con un programa de la aplicación. Este define la image, de la aplicación.

- Definir las conexiones de la red, generando información acerca de la dirección de los nodos (llamado la lmagen de la red), y cargando aplicación e imagen de la red sobre el hardware.

- Poner nodos sobre la linea de la red, sacar nodos de la linea, reiniciar nodos, ieer memoria de nodos, escribir memoria de nodos, y probar nodos.

- Monitorear el estado de todos los nodos sobre la red.

- Examinar y cambiar variables de la red sobre algunos nodos en la red.

- Recuperar los datos de su propia identificación y su propia documentación describiendo las variables de la red en algún otro nodo.

#### 1.4.3.2 Analizador de protocolo

El analizador de protocolo LONBUILDER monitorea, colecta, y despliega las estadísticas del tráfico de la red y la ejecución de la red selectivamente.

El analizador de protocolo es usado para realizar lo siguiente:

- Vigilar el tráfico de la red.

- Salvar todo el tráfico de la red en un archivo para desplegarlo después.

- Salvar un tráfico específico de la red en un archivo para la específicación de los filtros de paquetes basado en la fuente del nodo, la destinación de nodo, tipo de paquete, variable de la red y eliqueta de mensaje.

- Resumir la ejecución de la red, los contadores de paquetes por tipos de paquetes, y el contador de errores.

# CAPÍTULO II CIRCUITO INTEGRADO NEURON

#### 2.1 INTRODUCCIÓN

Los Circuitos Integrados NEURON MC143150 y MC143120 de motorola, son dispositivos que hacen posible implementar a bajo costo aplicaciones de redes de operación local. Por medio de una combinación única de hardware y un microprograma (firmware), estos dispositivos proveen todas las funciones necesarias para procesar entradas da sensores y dispositivos de control, además da poder controlar la propagación de la información qua viaja sobre una variedad de medios da comunicación. El MC143150 y MC143120 junto con el Banco de Desarrollo LONBUILDER ofrecen:

- Un fácil control de redes.

- Capacidad de volvar a configurar después de la instalación de la red.

- Manejo de mensajes del protocolo LONTALK sobre la red.

- Un medio ambiente orientado a objetos para desarrollo de sistemas.

El MC143150 esta disariado para monitorear y controlar sistemas que necesitan de un programa de la aplicación grande. Una interface hacia una memoria externa permite al sistema el uso de 42 K, de los 64 K de espacio total disponibles, para el almacenamiento del programa de la aplicación. El MC143160 no tiena memoria ROM interna. El equipo iniclador LONBUILDER (MC143160EVK) proporciona al código objeto del protocolo de comunicación, al sistema operativo y las 24 funciones de antrada/salida. El código del protocolo y el código de la aplicación puede ser localizados an memoria externa ROM, EPROM, NVRAM o RAM estática con batarias de respaldo.

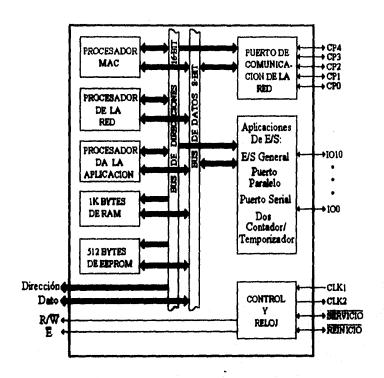

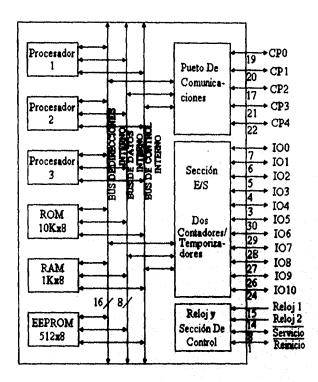

La figura 2.1 muestra en diagrama de bloques el Circuito Integrado NEURON MC143150

Figura 2.1 Diagrama de Bioques Simplificado del Circuito Integrado NEURON MC143160

El MC143120 no tiene interface para memoria externa y esta diseñado para aplicaciones que requieran programas de la aplicación pequeños. Este contiene 10 K de ROM de mascara que implementa el protocolo de comunicación, el sistema operativo y las 24 funciones de entrada/salida que pueden ser accesadas por el programa de la aplicación. El programa de la aplicación reside dentro de la memoria EEPROM interna de 512 bytes y utiliza el microprograma (firmware) sobre la ROM de mascara para la aplicación específica.

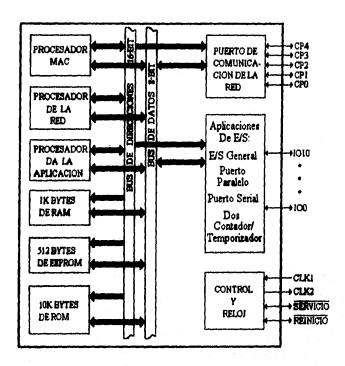

En la figura 2.2 se muestra en diagrama de bioques el Circuito Integrado NEURON MC143120.

Figura 2.2 Diagrama de Bloques Simplificado del Circuito Integrado NEURON MC143120

Ambos dispositivos tienen 11 terminales (pines) de entrada/sailda con hardware y software integrados para la conexión de motores, válvulas, manejadores de desplegadores, convertidores A/D, sensores, termistores, interruptores, retardadores, triacs, tacómetros, otros microprocesadores, modems, etc. Cada uno de ellos tienen tres procesadores, de los cuales dos interactuan con un subsistema de comunicación, realizando la transferencia de información de un nodo hacia otro nodo en un proceso automático dentro de un sistema de control distribuído.

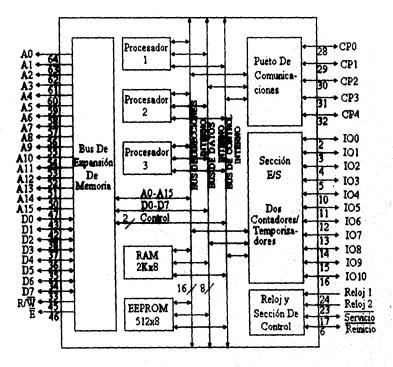

#### 2.2 RECURSOS DE HARDWARE DE LOS CIRCUITOS INTEGRADOS NEURON

Los primeros miembros de la familia de procesadores Circuilo Integrado NEURON son el MC143150 y el MC143120. El MC143150 (figura 2.3) soporta memoria externa para aplicaciones más complejas, mientras que el MC143120 (figura 2.4) es un sistema completo que soporta diversas aplicaciones. La mayoría de los bloques de hardware de ambos procesadores son iguales, excepto los que son especificados en la tabla 2.1.

Tabla 2.1 Comparación de los procesadores MC143150 y MC143120

| Características                  | MC143160 | MC143120 |

|----------------------------------|----------|----------|

| CPUs                             | 3        | 3        |

| Bytes de RAM                     | 2,048    | 1,024    |

| Bytes de ROM                     |          | 10,240   |

| Bytes de EEPROM                  | 512      | 512      |

| Temporizador/contador de 16-Bits | 2        | 2        |

| Interface de memoria externa     | Si       | No       |

| Terminales                       | 64/68    | 32       |

#### 2.2.1 Unidades del Procesador

Los tres estados de máquina idénticos (un estado de máquina por procesador) de 8 bits forman un multiprocesador simétrico, cada uno ejecutando un microciclo diferente dentro de un ciclo de tres fases (una fase por cada microciclo) en cualquier tiempo. Cada uno de éstos tiene su propio juego de registros (tabla 2.2), pero los tres toman parte en los 8 bits de datos y direcciones de las ALUs y el circuito para acceso a la memoria. Esto reduce el tamaño del dispositivo sin afectar la ejecución.

Tabla 2.2 Juego de Registros

| Mnemónicos | Bits | Contenido                                                 |

|------------|------|-----------------------------------------------------------|

| BANDERAS   | 8    | Número del CPU, selección rápida de E/S, y bit de acarreo |

| IP         | 16   | Apuntador de la instrucción siguienta                     |

| BP         | 16   | Dirección de los 256 bytes de la página base              |

| DSP        | 8    | Apuntador de datos de la pila dentro de la pagina baso    |

| RSP        | 8    | Retorno al apuntador de pila dentro de la página base     |

| TOS        | 8    | Cime de los datos de la pila, entrada de la ALU           |

| SAR        | 8    | Registro del enálisis de la asignatura                    |

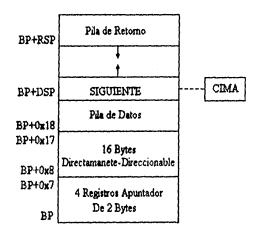

La arquitectura está orientada a la pila; una primera pila de un ancho de 8 bits es usada para la referencia de los datos, y la ALU opera sobre el registro TOS (cima de la pila) y la entrada siguiente en la pila de datos, la cual se encuentra en RAM. Una segunda pila almacena las direcciones de retorno para la instrucción CALL, y puede también ser usada para almacenar datos temporales (ver figura 2.5). Esta arquitectura maneja códigos muy compactos. Las Tabla 2.5, 2.6, y 2.7 delinean el juego de instrucciones.

Figura 2.3 MC143150

Figura 2.4 MC143120

La figura 2.5 muestra la organización de una página base, la cual puede ser de hasta 256 bytes de largo. Cada uno de los tres procesadores usa una página base diferente, cuya dirección está dada por el contenido del registro BP (página base) de este procesador. La cima de la pila de datos está dentro de los 6 bits del registro TOS, y el elemento siguiente en la pila de datos está localizado dentro de la página base en el desplazamiento dado por el contenido del registro DSP. La pila de datos crece desde la memoria baja hacia la memoria alta, y la pila para las direcciones de retorno crece desde la memoria alta hacia la baja.

Figura 2.5 Organización de la página base de la memoria

#### 2.2.2 Memorias

#### 2.2.2.1 EEPROM

El MC143150 y el MC143120 tienen internamente 512 bytes de memoria EEPROM que se puede programar. Toda la memoria EEPROM puede ser escrita, con excepción de 8 bytes. Los 8 bytes faltantes son escritos durante la fabricación, y contiene un identificador único de 48 bits para cada parte, más 16 bits para el código de fabricación del dispositivo. El tiempo de borrado y el tiempo de escritura son cada uno de 10 ms por byte. La memoria EEPROM puede ser escrita hasta 10,000 veces. Para el MC143120 y el MC143150 la memoria EEPROM almacena la información de la instalación específica, tal como las direcciones de la red y parámetros de comunicación. Para el MC143120, la memoria EEPROM también almacena el programa de la aplicación generado por el Banco de Desarrollo LONBUILDER. El código de la aplicación para el MC143150 puede ser almacenado dentro del dispositivo o fuera de él, en una memoria externa.

#### 2.2.2.2 RAM estática

El MC143150 tiene 2048 bytes de RAM estática y el MC143120 tiene 1024 bytes de RAM estática. El estado de la RAM es retenido por largo tiempo mientras se esté aplicando energia al dispositivo, igualmente en el modo "dormido".

#### 2.2.2.3 ROM programada

El MC143120 contiene 10,240 bytes de ROM preprogramada. Esta memoria contiene el microprograma LONWORK, incluyendo el código del protocolo LONTALK, el tiempo real de la lista de tareas y las librerlas de la función de la aplicación. Para todo esto el MC143150 accesa memoria externa. El código objeto es suplementado con el sistema de desarrollo LONBUILDER.

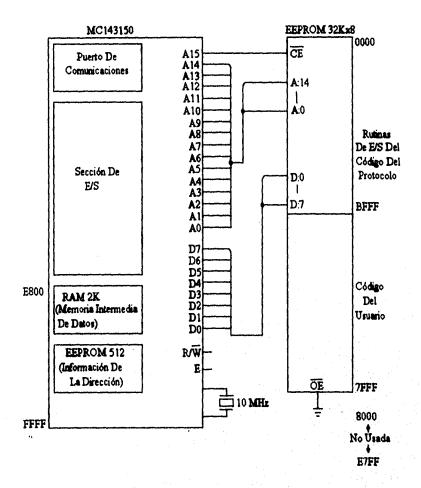

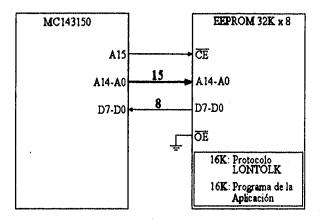

#### 2.2.3 Interface de Memoria Externa (solo para el MC143150)

Esta interface soporta hasta 42 Kbytes de espacio de memoria externa para programa y datos adicionales. El espacio total de la dirección es de 64 Kbyles. Sin embargo, 6 Kbytes del espacio de dirección está reservado por el dispositivo, los restantes 58 Kbytes son el espacio para la dirección externa, de los cuales, 16 K son usados por el microprograma del Circuito Integrado NEURON, el depurador de desarrollo LONBUILDER, y espacio reservado. El espacio de la memoria externs pude ser poblada con RAM, PROM, EPROM ó EEPROM en 256 bytes adicionales. El mapa de memoria se muestra en la figura 2.12. El bus tiene 6 lineas de datos bidireccionales, y 16 lineas de dirección manejadas por el procesador. Dos lineas de interfece (RW y E) son usadas para el acceso a la memoria externa. A la velocidad máxima de reloj (10 MHz de reloj de entrada), se requiere de 70 ns o un tiempo de acceso menor para la memoria externa. Si la entrada del reloj es menor, una memoris más lenta puede ser usada. Los valores permitidos para la entrada del reloj son de 10 MHz, 5 MHz, 2.5 MHz, 1.25 MHz, y 625 KHz. La habilitación del reloj (É) es 1/2 de la velocidad de entrada del reloj. La habilitación del reloj está en bajo siempre que el dato esté empezando ha ser transferido entre el Circuito Integrado NEURON y la memoria externa. Toda la memoria (interna y externa) puede ser accesada por algunos de los tres procesadores en la fase apropiada del ciclo de instrucción. Dado que el ciclo de instrucción de los tres procesadores se realiza en un tercio de ciclo con respecto uno del otro, el bus de la memoria es usada por un procesador a la vez.

La figura 2.6 muestra el diagrama de interfaces del MC143150 para diferentes tipos de memoria. Una configuración de hardware minima usaría una memoria EEPROM externa para almacenar el código del protocolo y el código de la aplicación del usuario (figura 2.7). Esta configuración puede no permitir al operador del sistema cambiar el código de la aplicación después de la instalación. Sin embargo, la información de la paginación y dirección podría ser alterada, ya que esta información reside en los 512 bytes de la EEPROM interna. Cuando se están desarrollando nodos que deben ser escritos nuevamente sobre la red con el código de la aplicación, y este sobrepasara los 512 bytes de la EEPOM interna, se requiere de una memoria externa EEPROM, NVRAM o SRAM con baterlas de respaldo. También se requiere, cuando se diseña un nodo usando un reloj de cristal lento, donde posiblemente, reducirla significativamente la velocidad de la memoria. Las terminales usadas para la interface de memoria externa son listados en la table 2,3. La señal de reloi É no es frecuentemente usada para leer memoria externa, pero puede estar conmutando con lineas decodificadas de dirección y la señal RW para generar la señal WRITE para memoria externa. Puede ser usada A15 (linea de dirección 15) o un decodificador de señal PAL conmutado con R/W para generar señales de lectura para la memoria externa. El MC143150 necesita ver el dato (tiempo de setup) 65 ns antes del flanco de subida del reloj E.

Figura 2.6 Interface de Memoria Externa

Figura 2.7 Minima Interface de Memoria para el MC143150

Tabla 2.3 Terminales de la interface de memoria externa

| Terminales | Dirección      | Función                 |

|------------|----------------|-------------------------|

| A0 - A15   | Salida         | Terminales de dirección |

| D0 - D7    | Entrade/Selide | Terminales de datos     |

| E          | Salida         | Habilitación de reloj   |

| RW         | Salida         | Selección Leer/Escribir |

Ya que uno de los procesadores internos siempre está usando el bus de direcciones, la realización de una interface entre el Circuito Integrado NEURON y un MCU (microcontrolador) sólo es posible con el uso de manejadores externos tres estados sobre las 16 líneas del bus de direcciones, compartiendo así, el bus de direcciones y el bus de datos (y memoria) del Circuito Integrado NEURON con el bus de direcciones y el bus de datos del MCU. Este método no es recomendado o emulado por el Banco de Desarrollo LONBUILDER. El mejor método de interface del Circuito Integrado NEURON y el MCU es a través de los 11 terminales de entrada/salida. Existe modo serial y paralelo para este propósito el cual es implementado fácilmente usando el lenguaje de programación NEURON.

#### 2.2.4 Entrada/Salida

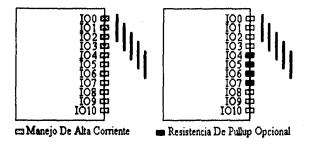

#### 2.2.4.1 Once terminales bidireccionales E/S

Estas terminales son usadas en diferentes configuraciones para proveer una interface flexible hacia un hardware externo y para proveer el acceso a los temporizadores/contadores interno.

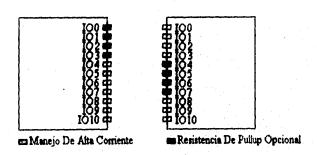

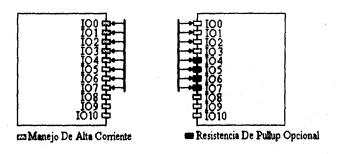

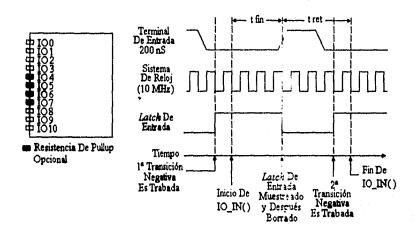

Las terminales IO4 - IO7 tienen transistores de pull-ups que son habilitados o deshabilitados con una directiva del compilador. Las terminales IO0 - IO3 tienen la capacidad de entregar una corriente alta (20 mA a 0.8 V). Las demás terminales tienen la capacidad estándar de entrega de corriente (1.4 mA a 0.4V). Todas las terminales (IO0 hasta IO10) tienen niveles de entrada TTL con histéresis. Las terminales IO0 hasta IO7 también tienen latches detector de nivel baio.

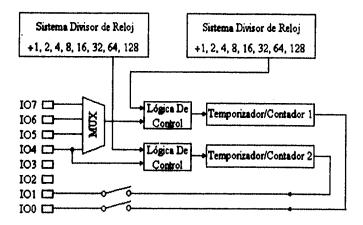

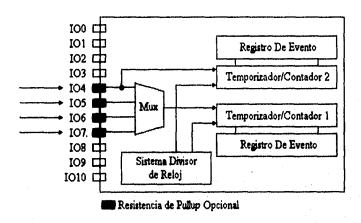

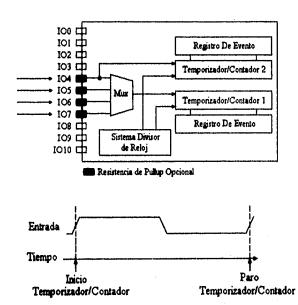

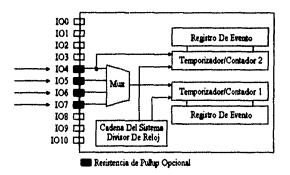

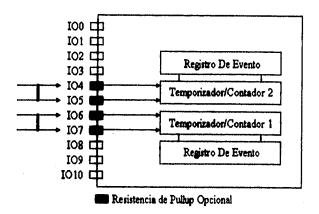

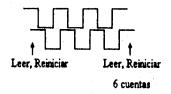

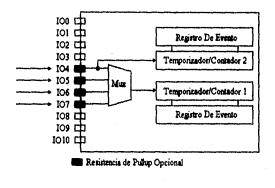

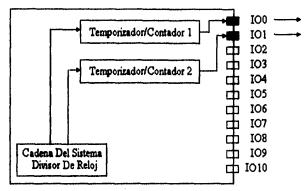

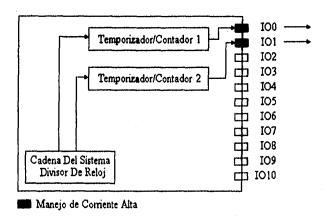

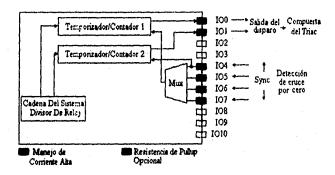

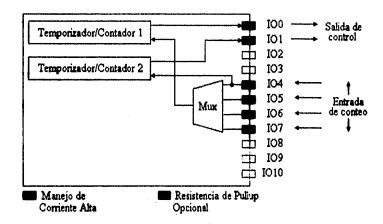

# 2.2.4.2 Dos temporizadores/contadores de 16 bits

Los temporizadores/contadores están implementados con un registro que puede ser escrito por el procesador, un contador de 16 bits, y un latch que puede ser leido por el procesador. Los 16 bits del registro se accesan byte por byte. El MC143150 y el MC143120 tienen un temporizador/contador cuya entrada se puede seleccionar de entre las terminales 104 hasta 107, y cuya salida es la terminal IO0, y un segundo temporizador/contador con entrada en la terminal IO4 y salida por la terminal IO1 (figura 2.8). Note que las entradas/salidas no están dedicadas para la función del temporizador/contador. Si por ejemplo, el temporizador/contador 1 es usado para señal de entrada solamente, entonces IOO es disponible para otra función de entrada o salida. El reloj para los temporizadores/contadores y las habilitaciones de las entradas pueden ser hechas desde terminales externas, o desde relojes escalados derivados del sistema de reloj; la velocidad de reloj de los dos temporizadores/contadores son independientes uno del otro. El funcionamiento del reloj externo ocurre opcionalmente sobre el fianco de subida, el fianco de bajada, o ambos fiancos de baiada v subida de la entrada.

Figure 2.8 Circuiteria del Temporizador/Contador

#### 2.2.5 Comunicación de la Red

Las cinco terminales del puerto de comunicación son la conexión a la red, que hace Interface con una amplia variedad de medios (se requiere de un transmisor/receptor). El puerto de comunicación puede ser configurado para operar en uno de dos modos: Modo directo (terminación simple o diferencial) o modo de propósito especial.

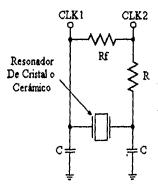

### 2.2.6 Siatema de Reloj

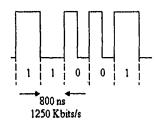

El Circuito Integrado NEURON incluye un oscilador que puede ser usado para generar una entrada de reioj usando un cristal externo. La transconductancia de este oscilador es menos de 2.1 milisiemens. El Circuito Integrado NEURON puede operar sobre un rango de velocidad de reioj de entrada desde 10 MHz hasta 625 KHz para aplicaciones de baja potencia. Las frecuencias de entradas válidas de reioj son: 10 MHz, 5 MHz, 2.5 MHz, 1.25 MHz, y 625 KHz. Alternativamente un generador de reioj externo puede manejar la terminal de entrada CMOS CLK1 de el Circuito Integrado NEURON, en tal caso CLK2 debe ser dejado desconectado. La precisión de la frecuencia de reioj debe ser de +/- 1.5% o de mayor precisión

para asegurar que los nodos puedan sincronizar correctamente sus bits de reloj cuando usan el transmisor/receptor en Modo Directo. Los valores para el cristal son listados en la tabla 2.4, hasta para una entrada de 625 KHz. Ver figura 2.9. Ya que la entrada de reloj es dividida entre dos, se permite un amplio rango de entrada del ciclo de trabajo.

Figura 2.9 Circuito Generador de Reioj del Circuito NEURON

Tabla 2.4 Valores de los componentes del generador de reloj

|                                 | Cristal |       | Resonador<br>cerámico |        |

|---------------------------------|---------|-------|-----------------------|--------|

| Frecuencia del reloj de entrada | R       | C     | R                     | C      |

| 10.0 MHz                        | 270 Ω   | 30 pF | 270 Ω                 | 30 pF  |

| 5.0 MHZ                         | 470 Ω   | 30 pF | 270 Ω                 | 30 pF  |

| 2.5 MHZ                         | 1 KO    | 36 pF | 1 KΩ                  | 36 pF  |

| 1.25 MHZ                        | 1.2 KΩ  | 47 pF | 1.2 ΚΩ                | 47 pF  |

| 625 KHz                         | 2.7 KΩ  | 47 pF | 1.2 ΚΩ                | 100 pF |

Rf = 100 k $\Omega$  para todas las condiciones. La frecuencia de resonancia del reloj cerámico o del cristal es igual a la entrada de la frecuencia del reloj. El cristal podría estar en resonancia paralela o serie. La tolerancia de resistencias y capacitores es de +/- 5%.

# 2.2.6.1 Circuiteria divisora de reloi

El Circuito Integrado NEURON divide la entrada del reloj por un factor de 2 para proveer un sistema de reloj simétrico sobre el dispositivo. La entrada del reloj puede ser generada por una fuente de oscilación externa TTL, o por un dispositivo oscilador usando un cristal externo o un resonador cerámico.

Un ciclo de instrucción del procesador es tres veces el ciclo de reloj del sistema, o seis ciclos del reloj de entrada. La mayoría de las instrucciones toman entre uno y siete ciclos de instrucción del procesador. A una velocidad de entrada de reloj máxima (10 MHz), el tiempo de instrucción son entre 0.6 µs y 4.2 µs. La fórmula para obtener el tiempo de instrucción es:

Las tablas 2.5, 2.6 y 2.7 listan las instrucciones del procesador y sus tiempos. Se provee este para poder calcular el tiempos de respuesta para eventos realizados sobre las terminales de entrada/salida. Toda la programación del Circuito Integrado NEURON está hecha con NEURON C usando un Sistema de Desarrollo LONBUILDER.

Tabla 2.5 Tiempos de las instrucciones del programa de control

| Mnemónicos  | Cicios | Descripción                                   |

|-------------|--------|-----------------------------------------------|

| NOP         | 1      | No operación                                  |

| SBR         | 1      | Salto corto                                   |

| GR/BRC/BRNC | 2      | Salto, salto sobre (no) acarreo               |

| SBRZ/SBRNZ  | 3      | Salto corto sobre (no) cero                   |

| BRF         | 4      | Salto largo                                   |

| BRZ/BRNZ    | 4      | Salto sobre (no) cero                         |

| RET         | 4      | Regreso desde la subrutina                    |

| BRNEO       | 4/6    | Salto si no es igual (realizado/no realizado) |

| DBRNZ       | 5      | Decrements y brincs si no es cero             |

| CALLR       | 5      | Llameda a subrutina relativa                  |

| CALL        | 6      | Llama a subrutina                             |

| CALLF       | 7      | Llemeda e subrutina tejana                    |

Tabla 2.6 Tiempos de las instrucciones dei programa de controi

| Mnemónicos           | Ciclos | Modo de dirección                                            |

|----------------------|--------|--------------------------------------------------------------|

| PUSH TOP             | 3      | Registro TOS                                                 |

| PUSH/POP cpureg      | 4      | Algún registro del CPU                                       |

| PUSH/POR ID          | 4      | Página base más desplazamiento (8-23)                        |

| PUSH/POP !TOS        | 4      | Página base más contenido de TOS                             |

| PUSH (RSP)           | 4      | Datos sobre la cima del regreso a la pila                    |

| PUSHS/PUSH # literal | . 4    | Valor literal de 3 ô 6 bits                                  |

| PUSHPOP              | 5      | Pop desde el regreso de la pila, push para regresar a los    |

|                      |        | datos de la pila                                             |

| POPPUSH              | 5      | Pop desde los datos de la pila, push para regresar a la pila |

| LDBP dirección       | 5      | Carga el apuntador de la página base                         |

| PUSH/POP (DSP)(D)    | 5      | Contenido del minimo desplazamiento del DSP (1-8)            |

| PUSD # literal       | 6      | Valor literal de 16 bits                                     |

| POPD/PUSHD (PTR)     | 6      | 16 bits indirectos a través del apuntador de la página base  |

| PUSH/POP [PTR](TOS)  | 6      | Indirecto a través del apuntador de la página base más       |

|                      |        | TOS.                                                         |

| PUSH/POP (PTR)[D]    | 7      | Indirecto a través del apuntador de la página base más       |

|                      |        | desplazamiento                                               |

| PUSH/POP absoluto    | 7      | push en los datos de la memoria para los datos de la pila    |

Labla 2.7 Tiempos de Instrucción de la Al U

| Mnemónicos          | Ciclos        | <b>Operación</b>                                          |  |

|---------------------|---------------|-----------------------------------------------------------|--|

| INC/DEC/NOT         | 2             | Incremento/decremento/negación                            |  |

| TOSROLC/RORC        | 2             | Rotación iz/der del TOS a través del acarreo              |  |

| SHLISHR             | 2             | Corrimiento lógico iz/der del TOS                         |  |

| SHAL/SHRA           | 2             | Corrimiento aritmético iz/der del TOS                     |  |

| DROP NEXT           | 2             | Descenso al siguiente elemento desde los datos de la pile |  |

| DROP (RSP)          | 2             | Descenso a la cima del retorno de la pila                 |  |

| ADD/AND/OR/XOR      | 3             | Operando con la literal sobre TOS                         |  |

| DROP TOS            | 3             | Descenso a la cima de los datos de la pila                |  |

| ALLOC # literal     | 3             | Mover et apuntador de datos de la pila                    |  |

| ADD/AND/OR/XOR      | 4             | Operando con el siguiente elemento sobre TOS              |  |

| ADC/SBC/SUB/XCH     | 4             | Operando con el siguiente elemento sobre TOS              |  |

| INC [PTR]           | 6             | Incrementando el apuntador de la página base (0-3)        |  |

| DEALLOC_R # literal | 6             | Moviendo el apuntador de datos de la pila y regresándolo  |  |

| IN/OUT              | 7+4<br>#bytes | Bloque entrada/salida                                     |  |

### 2.2.7 Funciones Adicionales.

### 2.2.7.1 Modo dormido/deaplerto

El Circuito Integrado NEURON puede estar dentro de un modo de consumo de baja energía controlado por software. En este modo, el reloj del sistema y todos los temporizadores/contadores están apagados, y se encuentra guardado todo el estado de información (incluyendo el contenido de la RAM interna). La operación normal se reanuda cuando una transición de entrada ocurre en alguna de las siguiente terminales:

Terminales de entrada/saiida (de mascara):

Una de las terminales IO4 hasta IO7, es seleccionada por el multiplexor del temporizador/contador.

- Terminal de servicio (sin mascara)

- Puertos de comunicación (de mascara):

Modo Directo Diferencial CP0 o CP1

Modo Directo de Terminación Simple CP0

Modo de Propósito Especial CP3

El software de la aplicación puede especificar que los transistores de pull-up (programables sobre la terminal de servicio y la terminal de entrada/salida IO4 - IO7) están deshabilitados para reducir el consumo de energia futura.

# 2.2.7.2 Temporizador perro de guardia

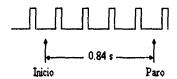

Los procesadores Circuito Integrado NEURON son protegidos contra un mai funcionamiento de software o memorias defectuosas por tres temporizadores perro de guardia, uno para cada procesador. Si la aplicación o el sistema de software falla, son reiniciados estos temporizadores y el Circuito Integrado NEURON es reiniciado automáticamente. El periodo del perro de guardía es aproximadamente de 0.84 segundos para la velocidad de entrada de reloj máxima (10 MHz) y es escalado inversamente con la velocidad de entrada del reloj. Cuando el Circuito Integrado NEURON está en el modo dormido, todos los temporizadores perro de guardia son deshabilitados.

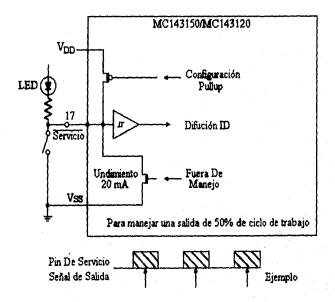

### 2.2.8 Terminal de Servicio

Esta terminal actúa como entrada y como salida, alternando la entrada y la salida a una velocidad de 76 Hz con un ciclo de trabajo de 50%. Cuando esta terminal actúa como salida, éste puede suministrar 20 mA para manejar un LED. Cuando se usa exclusivamente como una entrada, éste tiene una opción de seleccionar un transistor de pull-up interno. Bajo el control del microprograma del Circuito Integrado NEURON, esta terminal es usada durante la configuración e instalación del nodo conteniendo el Circuito Integrado NEURON. El microprograma enciende el LED cuando el Circuito Integrado NEURON no ha sido configurado con la información de la dirección de la red. Poniendo la terminal de servicio a tierra causa que el Circuito Integrado NEURON transmita un mensaje manejador de red (conteniendo sus 48 bits únicos ID) sobre la red. Un circuito típico para la terminal de servicio de LED y push-button es mostrado en la figura 2.10. Durante el reinicio, el estado de la terminal de servicio esta indeterminada.

Figura 2.10 Circulteria de la Terminai de Servicio

### 2.3 ORGANIZACIÓN DEL PROCESADOR

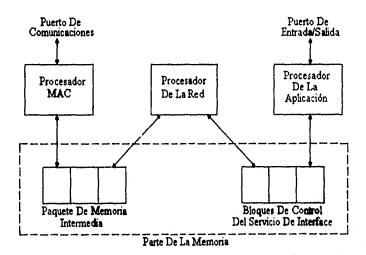

#### 2.3.1 Los Procesadores

Los tres procesadores están dedicados a las funciones siguientes para el software del sistema (ver figura 2.11).

Procesador 1, es el procesador del Control de Acceso al Medio (MAC) que manipula la primera de los siete niveles del protocolo de la red. Este incluye el manejo de hardware del subsistemas de comunicación, así como la ejecución del algoritmo que evita la collsión. El procesador 1 se comunica con el procesador 2 usando paquetes de memoria intermedia (buffers), localizados en alguna parte de la memoria.

Procesador 2, es el Procesador de la Red que implementa del segundo hasta el sexto nivel del protocolo de la red. Este manipula el procesado de las variables de la red, el direccionamiento, el procesado de las operaciones, la autenticidad, el diagnóstico, los tiempos de software, el manejo de redes y el encaminado de funciones. El procesador 2 usa paquetes de memoria intermedia (buffers), localizados en alguna parte de la memoria para comunicarse con el procesador 1, y el Servicio de interface de Control de Bioques (SICBs) para comunicarse con el procesador 3.