# UNIVERSIDAD NACIONAL AUTONOMA DE MEXICO

ESCUELA NACIONAL DE ESTUDIOS PROFESIONALES

" A R A G O N

DESARROLLO DE UN TRANSDUCTOR ELECTRONICO

APLICADO EN LA RED DE DISTRIBUCION DE

ENERGIA ELECTRICA

TESIS

QUE PARA OBTENER EL TITULO DE:

INGENIERO MECANICO ELECTRICISTA

P R E S E N T A :

CESAR JAVIER RUIZ ARMENTA

TESIS CON FALLA DE ORIGEN

### UNAM – Dirección General de Bibliotecas Tesis Digitales Restricciones de uso

### DERECHOS RESERVADOS © PROHIBIDA SU REPRODUCCIÓN TOTAL O PARCIAL

Todo el material contenido en esta tesis está protegido por la Ley Federal del Derecho de Autor (LFDA) de los Estados Unidos Mexicanos (México).

El uso de imágenes, fragmentos de videos, y demás material que sea objeto de protección de los derechos de autor, será exclusivamente para fines educativos e informativos y deberá citar la fuente donde la obtuvo mencionando el autor o autores. Cualquier uso distinto como el lucro, reproducción, edición o modificación, será perseguido y sancionado por el respectivo titular de los Derechos de Autor.

## INDICE

| INT | RODUCO | ION                                                      |                                                                                                                                                                                                                                  |

|-----|--------|----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | DESCI  | RIPCION GENERAL DE LA RED DE DISTRIBUCION DE ENERGIA ELE | ECTRICA 5                                                                                                                                                                                                                        |

|     | 1.1    | Panorama general del sistema eléctrico de potencia       |                                                                                                                                                                                                                                  |

|     | 1.2    | La red de distribución de energía eléctrica              | 6                                                                                                                                                                                                                                |

|     |        | 1.2.1 Problemática en la operación actual de la red .    |                                                                                                                                                                                                                                  |

|     | 1.3    | La automatización en la red de distribución              | salak (jan jawa sikin                                                                                                                                                                                                            |

|     |        | 1.3.1 Un sistema piloto de automatización para la red    |                                                                                                                                                                                                                                  |

| 2   | ESPEC  | IFICACION FUNCIONAL DEL TRANSDUCTOR ELECTRONICO          | 17                                                                                                                                                                                                                               |

|     | 2.1    | Elementos asociados al Transductor                       | 17                                                                                                                                                                                                                               |

|     | 2.2    | La especificación funcional del Transductor Electrónico  | para Medición (TEM) 21                                                                                                                                                                                                           |

|     |        |                                                          | e e de la companión de la comp<br>La companión de la companión d |

| 3   | DISEÑ  | D Y CONSTRUCCION DEL CIRCUITO TRANSDUCTOR ELECTRONIC     | CO PROTOTIPO 27                                                                                                                                                                                                                  |

|     | 3.1    | Principio de operación del Transductor Electrónico para  | Medición prototipo 27                                                                                                                                                                                                            |

|     | 3.2    | Diseño del Transductor Electrónico para Medición proto   | tipo 30                                                                                                                                                                                                                          |

|     |        | 0 0 1 115 dula da antrada                                |                                                                                                                                                                                                                                  |

Desarrollo de un Transductor Electrônico para Wedición aplicado en la red de distribución de energía eléctrica.

| . ; • |         | 3.2,1.1      | Circuito detecto   | r de cruce por                          | cero     |          |      |       | 34 |

|-------|---------|--------------|--------------------|-----------------------------------------|----------|----------|------|-------|----|

|       | 3.2.2   | Módulo de    | conversión         |                                         |          |          | ,    |       | 37 |

|       |         | 3.2.2.1      | Circuito acondic   | lonador de señ                          | ia1      | ,        |      |       | 40 |

|       | 3.2.3   | Módulo de    | control y proces   | amiento                                 |          | ••••     | lev- |       | 41 |

|       |         | 3.2.3.1      | Juego de instruc   | clones                                  |          | •        |      |       | 48 |

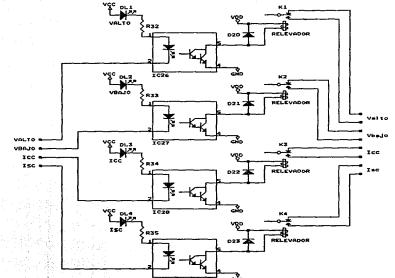

|       | 3.2.4   | Módulo de    | salidas            | ••••••                                  |          |          |      |       | 48 |

|       |         | 3.2.4.1      | Salidas de alarma  |                                         |          | 1046 716 | 100  | 8.0   |    |

|       |         | 3.2.4.2      | Valores limites p  | ara voltaje y c                         | orriente | ••••     |      | (A)   | 50 |

|       |         | 3.2.4.3      | Salidas para med   | ición                                   |          | • • • •  |      |       | 52 |

| 3.3   | Diagra  | nas eléctric | cos del Transduct  | or prototipo                            |          |          |      |       | 57 |

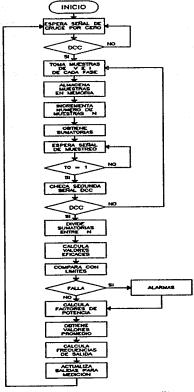

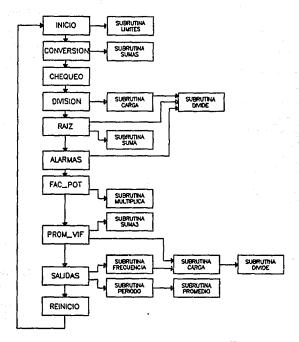

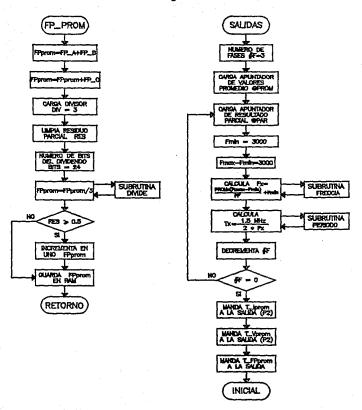

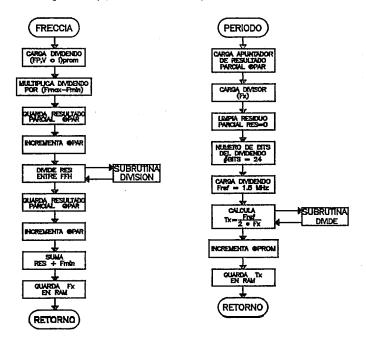

| 3.4   | Progra  | ma del micro | ocontrolador       |                                         |          |          |      | ••••  | 63 |

|       |         |              |                    |                                         |          |          |      |       |    |

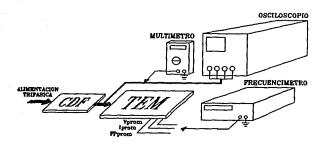

| PRUEE | AS DE O | PERACION AI  | L PROTOTIPO        |                                         |          |          |      |       | 71 |

| 4.1   | Constr  | ucción del   | circuito de prueba | a                                       |          | ••••     |      | ••••• | 71 |

|       | 4.1.1   | Circuito d   | esvlador de fase   |                                         |          |          |      |       | 72 |

| 4.2   | Resulta | ido de las p | oruebas            | • • • • • • • • • • • • • • • • • • • • |          |          |      |       | 75 |

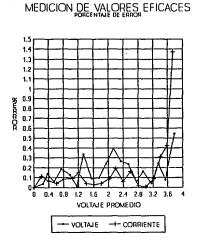

|       | 4.2.1   | Medición d   | e valores eficace  | s                                       |          | ••••     |      |       | 75 |

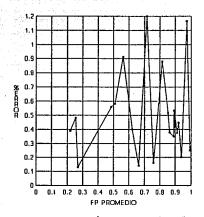

|       | 4.2.2   | Medición d   | el factor de pote  | ncia                                    |          |          |      |       | 75 |

## Desarrollo de un Transductor Electrónico para Medición aplicado en la red de distribución de energía eléctrica.

| CONCLUSIONES Y RECOMENDACIONES                      |           | ••••    |      | 80  |

|-----------------------------------------------------|-----------|---------|------|-----|

| ANEXO 1. Error en el proceso de medición del TEM    |           |         | •••• | 82  |

| ANEXO 2. Juego de instrucciones 8751                |           |         | •••• | 91  |

| ANEXO 3. Programa del 8751 para el cálculo de la ra | Iz cuadra | da .    |      | 94  |

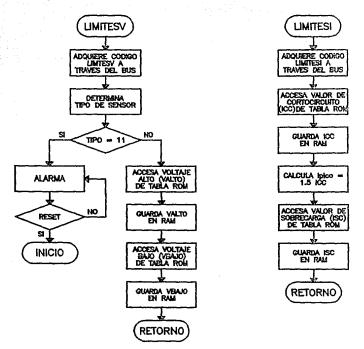

| ANEXO 4. Diagramas de flujo del programa del TEM .  |           |         |      | 100 |

| BIBLIOGRAFIA                                        |           | ••••    |      | 115 |

| BIBLIOGRAFIA                                        |           | • • • • | •••• | 11  |

#### INTRODUCCION

Las características del suministro eléctrico imponen requerimientos especiales de operación de las redes de distribución en cuanto a su confiabilidad y continuidad. El tiempo de interrupción por usuario, que representa un indicador básico de la calidad del servicio, es afectado por el tiempo de localización y atención de fallas y por la dimensión geográfica del alcance del disturbio, particularmente en 20nas con alta densidad de población.

Para apoyar a la operación de la red de distribución, las compañías suministradoras están desarrollando proyectos de automatización basados en los equipos de procesamiento de información y los medios de comunicación disponibles actualmente.

El objetivo principal de la automatización de la red de distribución es reducir el número de usuarios afectados por interrupciones y la duración de éstas.

En México, en varias divisiones de distribución, se han dado pasos hacia la automatización de la red a través de varias acciones: instalación de sistemas de telecontrol para desconectadores motorizados en la División Bajlo, lo cual ayudó a reducir los tiempos de interrupción por maniobras, realizadas anteriormente por cuadrillas de trabajadores. La impiantación de un sistema de control supervisorio en subestaciones y la aplicación de un sistema de adquisición de datos y control supervisorio al control de desconectadores en la División Sureste mejoró notablemente el desempeño de las redes de distribución con los consiguientes beneficios para los usuarios y la propia compañía suministradora.

En el Instituto de Investigaciones Eléctricas (IE) se planteó un proyecto para la automatización de la red de distribución. Tal proyecto contempla la instalación de equipo para monitoreo y control en la red, así como el desarrollo de programas de cómputo y adaptación de programas ya existentes para auxiliar en el manejo de información.

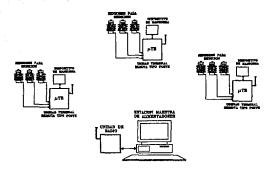

Se ideó la implantación de un sistema piloto, integrado por un Centro de Control simulado por una computadora personal, terminales remotas tipo poste (µTRs), aparatos de radio como medio de comunicación y sensores para medición. Las funciones que realizará este sistema piloto pueden describirse en los siguientes términos:

La comunicación vía radio entre las µTRs y el Centro de Control permite al operador del Centro recibir la información de campo referente a valores de parámetros eléctricos, estado de los elementos de protección y seccionamiento, así como indicación de condiciones anormales en el funcionamiento de la red por medio de señales de alarma.

Durante el funcionamiento normal de la red, el Centro de Control procesa la información recibida y la almacena en una base de datos que se actualiza periódicamente; de esta forma el Centro de Control puede determinar en forma rápida la localización y magnitud de una falla cuando ésta se presenta, y en base a la información sobre cargas y energía disponiblo, determina la mejor alternativa para reconfigurar la red y lograr con ello reducir al mínimo la cantidad de usuarlos afectados. Tal reacomodo de cargas se logra por medio de órdenes de apertura-cierre enviadas a las uTRs para que éstas a su vez accionen sobre sus elementos de seccionamiento asociados. En todo momento, el operador del Centro de Control está informado de los eventos ocurridos y por ocurrir, por medio de diagramas unifiliares de la red presentados en pantalia.

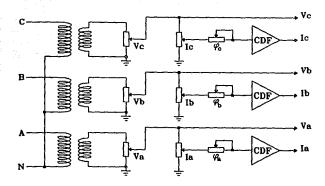

En cuanto a los sensores para medición, que se utiliza uno por fase, son elementos que proporcionan salidas de voltaje alterno proporcionales a las corrientes y voltajes de fase en la red.

Para la implantación del sistema piloto se dispone de µTRs concebidas para aplicación general y cuya operación consiste, como ya se mencionó, en informar al Centro de Control sobre cambios detectados en sus entradas digitales (abierto-cerrado) y el valor de sus entradas analógicas las cuales, para el caso de las µTRs existentes, deben ser señales de frecuencia. También, cuando el Centro de Control así lo indica, las µTRs envían órdenes de apertura-cierre a los elementos de protección o seccionamiento a ellas asociados.

De acuerdo con lo anterior, las µTRs disponibles no están habilitadas para recibir directamente las señales proporcionadas por los sensores y tampoco cuentan con la capacidad de realizar la medición de parámetros eléctricos tales como voltaje, corriente y factor de potencia.

Para resolver este inconveniente, se descartó la posibilidad de sustituir a las µTRs por otras con la capacidad de manejar las señales analógicas provenientes de los sensores y realizar la medición, puesto que el cambio implicaría una inversión elevada. El costo de una µTR está en función del tipo y número de entradas a procesar.

Como una mejor alternativa se optó por desarrollar un circulto electrónico que efectuara la medición de las señales provenientes del sensor y proporcionara a la µTR señales en frecuencia

representativas de los valores medidos. También, el circuito deberá ser capaz de detectar condiciones de falla en la red y notificario, por medio de señales de alarma, a la μTR para que ésta a su vez así lo indique al Centro de Control.

De lo anteriormente expuesto, puede resumirse que el diseño del circuito electrónico mencionado salva la necesidad de adquirir una µTR para la aplicación específica permitiendo el aprovechamiento del equipo existente y en consecuencia el ahorro de recursos. Por otra parte, y lo que se considera más importante, se propicia el desarrollo de tecnología propia que puede ser explotada posteriormente en diferentes aplicaciones.

El objetivo de este trabajo es el presentar el desarrollo del circuito electrónico mencionado, que en lo sucesivo se denomina Transductor Electrónico para Medición (TEM), el cual representa un pequeño aporte en lo que a diseño de equipo aplicado en las redes de distribución de energía eléctrica se reflere.

#### Contenido de la Tesis.

En el capítulo uno se describe en forma general el sistema eléctrico de potencia con el fin de mostrar al lector la parte que de dicho sistema será el campo de aplicación del circulto desarrollado. La parte de interés del sistema será la red de distribución.

Se hace mención de los beneficios que brinda la automatización en la red de distribución de energía eléctrica y que representa una posible solución a la problemática de operación que actualmente afecta en forma considerable su funcionamiento. Se describe un sistema plloto de automatización, propuesto por el instituto de investigaciones Eléctricas y para el cual se planteó el desarrollo del circuito Transductor Electrónico para Medición.

El capítulo dos presenta la especificación funcional del TEM establecida por el IIE y en la cual se indican en detalle las funciones y características que deberá cubrir el circuito. También en este capítulo so describen los elementos asociados al TEM: los sensores para medición y la unidad terminal remota.

El capítulo tres comprende el diseño del TEM en base a las especificaciones proporcionadas. Se describe la teoría de funcionamiento del TEM y se presenta el diseño de los módulos que lo integrarán, así como los criterios aplicados para la selección de los componentes empleados en su construcción.

El diseño del circulto está basado en un microcontrolador, lo cual permitirá, con cierta facilidad, realizar cambios y mejoras en las funciones del TEM modificando el programa del microcontrolador. El diseño modular permitirá que puedan efectuarse cambios en el tipo y cantidad de salidas pensando en otra posible aplicación del TEM.

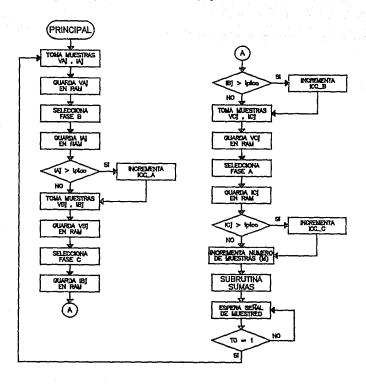

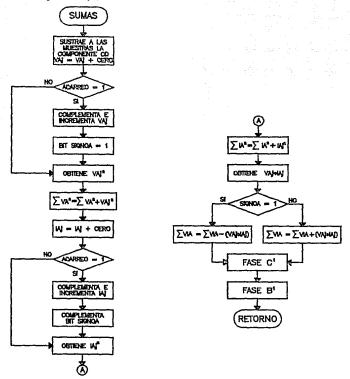

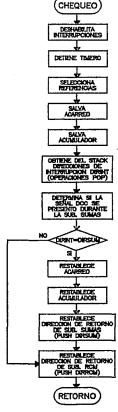

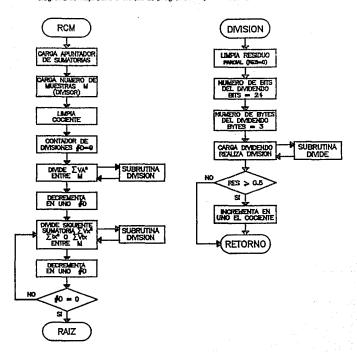

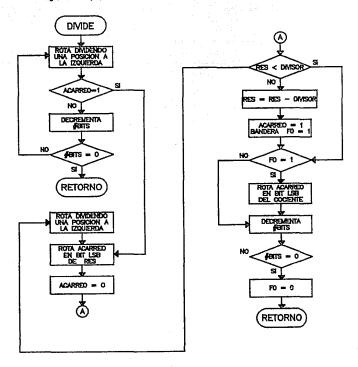

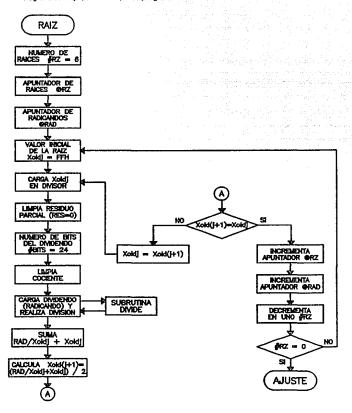

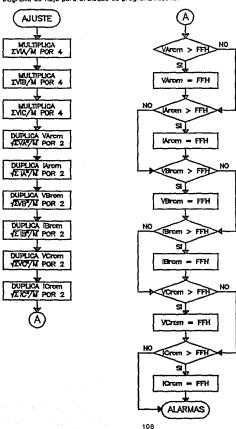

Se incluye en el capítulo tres un diagrama a bioques que describe en forma general el funcionamiento del TEM y la descripción, más en detalle, de las subrutinas que forman el programa del microcontrolador. Se incluyen también los diagramas eléctricos de cada uno de los módulos del TEM.

En el capítulo cuatro se presenta la implementación del circuito de prueba y los resultados obtenidos de las pruebas realizadas al TEM prototipo para verificar su correcta operación.

Por último, se concluye sobre el trabajo desarrollado y se sugieren algunas adiciones que podrían realizarse en el circuito para aumentar su utilidad.

#### CAPITULO 1

## DESCRIPCION GENERAL DE LA RED DE DISTRIBUCION DE ENERGIA ELECTRICA

#### 1.1 Panorama general del sistema eléctrico de potencia.

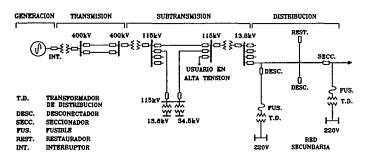

Fundamentalmente un sistema eléctrico de potencia está integrado por instalaciones de Generación, Transmisión, Subtransmisión y Distribución, como se muestra en la Figura 1.1.

Las instalaciones de Generación están constituidas por las plantas que pueden ser Termoeléctricas convencionales, Hidroeléctricas, Turbogas, Ciclo combinado, Carboeléctricas, Nucleoeléctricas, Geotermoeléctricas.

Las instalaciones de Transmisión comprenden las grandes subestaciones elevadoras y reductoras, así como sus respectivas ilneas de transmisión, generalmente de 230 y 400 kV. Las instalaciones de Subtransmisión se refieren a las líneas de subtransmisión de 115 y 138 kV, y sus respectivas subestaciones reductoras a 13.8, 23 y 34.5 kV.

Figura 1.1 Diagrama esquemático de un sistema eléctrico de potencia.(Adaptada de José L.A., "Funciones del área de distribución relacionadas con la confiabilidad",RVP-88,agosto 1988,p.41).

Los sistemas de Distribución comprenden las líneas y redes de 13.8, 23 y 34.5 kV, así como también los transformadores de distribución y sus correspondientes redes secundarias.

Una parte del sistema eléctrico de potencia con alta problemática en su funcionamiento es la red de distribución. En ella se presenta el mayor porcentaje de fallas ocurridas en el sistema; por tal motivo, las compañías suministradoras de energía eléctrica ponen especial interés en majorar el desempeño de sus redes. Uno de los aspectos considerados para esta mejoría es la optimación de la metodología de atención a fallas, agilizando los procesos de detección, localización y reparación.

Teniendo como objetivo lo anterior, existen proyectos dentro de los cuales se han desarrollado oquipos e implantado sistemas para el apoyo en la supervisión y control de las redes de distribución.

Este trabajo representa un pequeño aporte al desarrollo de equipo aplicado en la red de distribución de energía eléctrica y puesto que ésta será el campo de interés, se presentará una descripción del funcionamiento y problemática de la red de distribución, antes de iniciar el desarrollo del tema principal.

#### 1.2 La red de distribución de energía eléctrica.

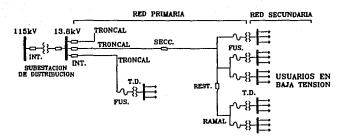

La red de distribución se divide en dos partes: red primaria y red secundaria (Figura 1.2). La red primaria opera con los niveles de distribución proplamente dichos (13.8, 23 y 34.5 kV) y su función es el suministrar energía a la red secundaria y a los usuarios industriales relativamente grandes. La red secundaria o de baja tensión (220 V) alimenta a usuarios residenciales, comerciales y a pequeñas industrias.

La red secundaria es aquélla que empleza en el secundario de un transformador reductor de distribución (T.D.) y termina en la entrada de servicio de los usuarios en donde se miden los consumos.

La red primaria tiene su origen en la Subestación de Distribución (SE), después del interruptor.

A partir de este punto surgen caminos para la circulación de la energía siguiendo una configuración radial, en otras palabras, el extremo final de la línea (remate) no regresa a la SE. Estos circuitos son conocidos como alimentadores. En una SE típica salen de cinco a ocho alimentadores, los cuales se

Figura 1.2 Diagrama típico de una red en conexión radial.

enlazan entre sí y con alimentadores de otras subestaciones, utilizando equipos de maniobra y protección con el fin de poder cambiar la configuración de la SE y de la red en caso que así se requiera.

La sección del alimentador que no cuenta con equipos que interrumpan automáticamente una sobrecorriente se le denomina troncal, y constituye la primera sección del alimentador. Las fallas ocurridas en la troncal sólo pueden ser liberadas por el interruptor de la SE. Con objeto de dar flexibilidad a la operación, la troncal del alimentador se divide en secciones de longitud variable usando para este fin seccionadores o cuchillas de operación bajo carga, cuya función es desenergizar una sección determinada, ya sea por cuestiones de mantenimiento o para el apoyo al interruptor de la SE en la localización de fallas.

Las secciones que salen del troncal se conocen como ramales. En los ramales se instalan equipos de protección automática tales como restauradores y cortacircuitos fusibles, cuya función principal es la de interrumpir el paso de la corriente en caso de presentarse una elevación de ésta fuera de los ifinites permitidos, protegiendo así al resto del alimentador.

De lo anterior, puede resumirse que los sistemas de distribución son aquéllos que llevan la energía eléctrica hasta el consumidor haciendo la transferencia desde los sistemas de transmisión o subtransmisión. Los objetivos de las redes de distribución se basan en los requerimientos de los usuarios:

- Disponer de la energía eléctrica en el momento que se requiera.

- Que las características del suministro cumplan con normas de calidad en cuanto a variaciones de tensión y frecuencia.

- Que la energía eléctrica se suministre con el mínimo de interrupciones y que la duración de las mismas también sea mínima.

- 4. Que el costo de la energía sea mínimo.

Para cubrir estos requerimientos, los proyectos encargados han establecido entre otros, los siguientes objetivos:

- Mantener una constante mejora en los parámetros de calidad del servicio destacando la tensión de suministro, el Índice de salidas y el Tiempo de Interrupción por Usuario (TIU)<sup>1</sup>.

- Operación eficiente reduciendo pérdidas de energía. Las estadísticas muostran que la mayor cantidad de las pérdidas en un sistema eléctrico son localizadas en la red de distribución<sup>2</sup>.

- Contar con estadísticas de operación de la red que retroalimenten con información al diseño de las mismas y a las especificaciones de selección y adquisición de los componentes.

#### 1.2.1 Problemática en la operación actual de la red.

La calidad del servicio eléctrico es definida como la capacidad del sistema para proporcionar, dentro de los límites establecidos, un suministro aceptable; las variables que se deben tomar en cuenta para su evaluación son:

<sup>&</sup>lt;sup>1</sup>El TIU es el tienpo promedio en que cada usuario no dispuso del servicio, durante un período específico.

ROBERTIO ESPINOSA Y FELPE PEREZ, "Principios básicos de confiabilidad en sistemas de distribución", en: RYP-88 Vol. Sistemas de Distribución 2a, parte (1; Acapulco, Máx.: IEEE, 1988) pp. 45-49.

- Tensión

- Frecuencia

- Forma de onda

- Relación entre fases

- Confiabilidad

- Interrupciones

De éstas, los disturbios más comunes que afectan a los usuarios son la tensión y las interrupciones, siendo éstas últimas las que afectan considerablemente la continuidad del servicio, debido al tiempo que se requiere para restablecerlo a la normalidad después de la ocurrencia de una falla (en 1990 el TIU nacional fue del orden de 400 minutos al año). Por otra parte, el número de usuarios afectados depende de la configuración de la red, por lo que la disminución de tal número se logra modificando la red de tal forma que para una misma interrupción, se tenga una cantidad menor de usuarios afectados.

La duración de una interrupción está constituida por:

- El tiempo de detección

- El tiempo de atención

- El tiempo de reparación, seccionamiento o transferencia"

- El tiempo de restablecimiento

Por lo tanto, disminuyendo cualesquiera de ellos, se obtiene una reducción del Tiu.

Para llevar a cabo la función operativa de las redes aéreas, se cuenta con sectores de operación cuyo personal se auxilla de cuadrillas para atender maniobras. La filosofía de operación está basada en la utilización de los elementos de protección y seccionamiento, instalados tanto en la subestación como en los circuitos, usando los medios de comunicación de teléfono a las subestaciones y de radio a las cuadrillas de campo.

Cuando una falla ocurre en ramales, el equipo de protección opera para liberarla. En el caso de los restauradores, el servicio se restablece automáticamente si la falla es transitoria. Por el contrario, si la falla es permanente, el operador se entera de la ubicación aproximada del disturbio por medio de las liamadas telefónicas que hacen los usuarios afectados. Entonces, se comunica por radio con las cuadrillas de mantenimiento del área, para que revisen y corrijan el daño, restableciendo el servicio posteriormente.

En el caso de la troncal, por la cantidad y tipo de usuarios, se puede contar con procedimientos de atención a fallas conocidos como planes de contingencia. La función principal de estos planes es restablecer el servicio en las secciones de troncal no falladas, en el menor tiempo posible, para poder dedicar mayores esfuerzos a la reparación del daño.

Considerando la secuencia lógica a seguir en caso de falla en la troncal, suponiendo que no se tienen restauradores ni fusibles, lo cual representa el caso general, se sucede al ocurrir una falla que el interruptor de la subestación se dispara, abre el circuito y todo el alimentador queda sin energía. El operador se entera del disturbio pero no de su ubicación. Como primer paso se comunica con la cuadrilla para que se traslado al sitio donde está localizado el seccionador que divide en dos partes la troncal y lo abran. La cuadrilla le comunica la ejecución de esta acción, con lo que cierra nuevamente el interruptor de la subestación. Si la falla está ubicada en la primera sección del alimentador, el interruptor abre nuevamente bajo la acción del cortocircuito. La secuencia se repite tantas veces como sea necesario, dependiendo del número de seccionadores instalados en la troncal y de la ubicación de la falla.

Una vez ubicada y aislada la sección falitada, se revisan los entaces disponibles con otros alimentadores que permitan energizar las secciones no faliadas. Es importante que el operador conozca en ese momento la capacidad de energía disponible en los otros alimentadores y la que se dejó de alimentar por la falla, para que reconfigure la red en forma adecuada.

Por lo anterior, en la atención de un disturbio se pueden clasificar tres actividades blen definidas:

- a) Localización y aislamiento de la falla

- b) Reparación del daño

- c) Puesta en servicio del alimentador

El tiempo de atención de un disturbio depende de la cantidad de maniobras, facilidad para ejecutarias y sobre todo el tiempo de traslado del personal a los lugares de maniobra. Todos estos factores están relacionados con la longitud del circuito, condiciones ambientales y de tráfico.

De acuerdo a estadísticas sobre disturbios se encontró que el tiempo promedio empleado en la localización y alslamiento de la falla, incluyendo el tiempo de traslado para la primera maniobra, representa el 70% del tiempo total de atención. La reducción de este tiempo a valores mínimos es factible de consequir mediante la automatización de la red de distribución<sup>3</sup>.

#### 1.3 La automatización en la red de distribución.

Históricamente, los sistemas de distribución han operado con un mínimo de monitoreo: principalmente con un control manual y local de capacitores, desconectadores y reguladores de volta le. Dero careciendo de un apoyo computacional extenso para los operadores del sistema.

El tema de la automatización de la red de distribución se ha venido tratando en México desde hace más de diez años<sup>4</sup>. Desde entonces se han realizado algunos trabajos sobre este campo en diferentes zonas del país, actividades tales como instalación de sistemas de telecontrol para desconectadores motorizados<sup>5</sup>, control supervisorio en subestaciones<sup>6</sup> y aplicación de un sistema de adquisición de datos y control supervisorio al control de desconectadores<sup>7</sup>. Sin embargo, a pesar de los trabajos que se han realizado sobre el tema de la automatización de la red, hasta la fecha la información publicada al respecto en nuestro país es escasa.

En años anteriores han evolucionado tecnologías automatizadas para monitoreo de subestaciones y alimentadores, para reconfiguración de alimentadores y para control de reactivos. Esta innovación en las tecnologías de las comunicaciones y los controles por microprocesadores, prometen apoyar en forma importante la habilidad de los sistemas de distribución para satisfacer las demandas futuras y redundar en beneficios importantes para la confiabilidad y eficiencia en la operación de los circuitos de distribución.

<sup>3-</sup>MABERTO SOLORZANO A. Y FCO. JAVIER ROBLEDO V., "El difermiento de inversiones: un beneficio potencial de la autoaatización de rodes de distribución aéreas", en RVP-90, Vol. Conductores aislados y Distribución. (3; Acapulco, Máx.: IEEE, 1990) pp. 198-205.

<sup>\*\*</sup>PUIÓN DE LA ROSA A., JAME CARRILLO C. [ot.al.], "Arquitectura funcional de un sistema piloto de automatización de la rod de la ingeniería y Control de Calidad, LATRICON-90 Todo II (Monterrey, Méx.: IEEF, 1990).

<sup>&</sup>lt;sup>5</sup>CFE, Div. de Distribución Bajlo, "Telecontrol de la red de distribución de la Cd. de Guanajuato", en: <u>Reunión de Verano</u> de Potencia 1939 (2; Acapulco, Máx.: IEEE, 1939).

<sup>&</sup>lt;sup>B</sup>CFE, Div. de Distribución Sureste. <u>Control supervisorio en subestaciones de distribución</u>. Gerencia de Distribución (México: 1989).

<sup>&</sup>lt;sup>7</sup>CFE, Div. de Distribución Sureste. <u>Enlaces de circuitos de distribución por telecontrol</u>. Gerencia de Distribución (México: 1989).

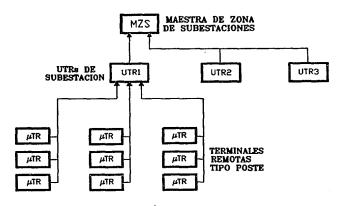

En el trabajo de Peralta Barros<sup>8</sup> se plantea un método de localización de fallas en los alimentadores de distribución empleando un sistema de control supervisorio. La Figura 1.3 liustra el esquema de la configuración para un sistema de automatización de la red de distribución con una estructura jerárquica de tres niveles. En dicha figura las flechas indican jerarquía de control y de comunicaciones hacia arriba. El sistema de comunicaciones es un medio que permite transferencia de datos en ambos sentidos.

Figura 1.3 Niveles jerárquicos en un sistema automatizado.

El funcionamiento del sistema de automatización puede resumirse en los siguientes términos: El nivel más alto de capacidad computacional es el de la Maestra de Zona de Subestaciones (MZS). Este computador actualiza continuamente una base de datos la cual comprende todas las subestaciones y sus alimentadores; para adquirir esta información la MZS se comunica con las Unidades Terminales

<sup>&</sup>lt;sup>8</sup>ALBERTO J. PERALTA B., "Localización de fallas en las redes de distribución de energía eléctrica". (Tesis de Maestría en Electrónica: 1982).

Remotas de Subestación (UTRs). La MZS puede generar una acción de control como resultado de un procedimiento de exploración.

La UTR monitorea los puntos de importancia dentro de la subestación y se comunica con las microterminales remotas (µTRs) para actualizar su base de datos, la cual comprende la configuración de dicha subestación con sus alimentadores. La UTR realiza sus cálculos, basados en los parámetros disponibles dentro de su rango de control y recomienda las acciones a tomar a la MZS cuando sea explorada por ésta.

Las µTRs son el nivel de inteligencia más bajo en el sistema y se localizan en los aparatos de protección contra sobrecorriente (APS) y en los puntos claves de monitoreo de los alimentadores. La µTR calcula en todo momento la magnitud de las corrientes de ilnea y las compara con valores prestablecidos para poder determinar si el APS asociado debiera disparar debido a la ocurrencia de fallas. Las µTRs envían la siguiente información a la UTR para formar la base de datos de distribución: el estado de los APS, una señal que indique la detección de sobrecorriente, una señal que indique la detección de no corriente, y opcionalmente, enviarán la magnitud de la corriente de falla.

#### 1.3.1 Un sistema piloto de automatización para la red.

Para apoyar a la operación de la red, las compañías suministradoras están desarrollando proyectos piloto de automatización basados en los equipos de procesamiento de información y los medios de comunicación disponibles actualmente.

Sin embargo, además de los problemas puramente técnicos, la implantación de un sistema para automatizar las redes de distribución se ha enfrentado al problema de determinar la factibilidad económica de su aplicación. La capacidad del sistema automatizado, las funciones a realizar y el crecimiento del mismo son la base de su evaluación económica, mediante la comparación de la operación de la red antes y después de la automatización.

Por otra parte, en los últimos diez años el sector eléctrico nacional ha visto mermados sus recursos económicos para la atención de sus programas de inversión y mantenimiento, por lo que a últimas fechas ha sido necesario reconsiderar la filosofía y alcance del programa de automatización, a fin de aumentar la posibilidad de su realización con un costo mínimo e incremento de su confiabilidad.

En el IIE se ha trabajado en un proyecto sobre el tema, que tiene como objetivo medir los beneficios de la automatización de la red de distribución mediante la evaluación del incremento de la conflabilidad del servicio eléctrico suministrado en una zona piloto automatizada.

El proyecto ha sido dividido en tres etapas, a saber:

ETAPA 1. Creación del sistema de detección de fallas y monitoreo de cargas.

ETAPA 2. Sistema de control remoto.

ETAPA 3. Automatización de alimentadores.

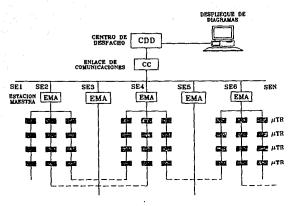

La arquitectura funcional propuesta para el sistema de distribución automatizado se ilustra en la Figura 1.4.

El primer nivel de control Jerárquico está integrado por un Centro de Despacho de Distribución (CDD) cuyas funciones son, principalmente, de carácter administrativo o de gestión de la red.

El segundo nivel lo constituye un conjunto de Estaciones Maestras de Alimentadores (EMA), cuyo número dependo de la cantidad de puntos de control y monitoreo de la red a controlar. La función principal de las EMA es la atención a disturbios en la red, mediante la localización y atsiamiento de secciones faliadas del alimentador, así como la reconfiguración automática de la red para alimentar las secciones sanas y disminuir al mínimo la cantidad de usuarios afectados.

Para realizar estas funciones, la EMA contará con su propia base de datos en la que estará atmacenada la información del estado de los equipos de manlobra y valores medidos de parámetros elèctricos, tanto del alimentador dañado como de los enlaces sanos. De acuerdo con la información recabada, la EMA decidirá las acciones correctivas que será necesario ejecutar para la mejor alternativa de reconfiguración de la red. Esto será realizado a través de ordenar tales acciones a las µTRs involucradas, las cuales a su vez actuarán sobre los equipos de seccionamiento. En caso necesario, la EMA informará al CDO la ocurrencia del evento, las acciones ejecutadas y la configuración final de la red.

Figura 1.4 Arquitectura funcional del sistema de distribución automatizado. (Adaptada de R. De la Rosa, [et.al.], "Arquitectura funcional de un sistema de automatización de la rod de distribución", LATINCON-90, sept. 1990).

La configuración básica de la EMA y el equipo de campo se muestra en la Figura 1.5; está compuesta por la Estación Maestra propiamente dicha y por unidades de monitoreo, detección y control instaladas en los puntos de seccionamiento de la red.

La configuración modular permite iniciar la implantación del sistema en forma plioto a nivel EMA, incluyendo las funciones de control de alimentadores. El sistema pilioto debe incluir los equipos de campo suficientes para evaluar la factibilidad del proyecto completo.

Para contar con la capacidad de medir parámetros de las líneas tales como voltaje, corriente y factor de potencia e indicar condiciones anormales de los mismos, y por los motivos expuestos al inicio de la tesis (*introducción*, p.2) se planeó el desarrollo del circuito Transductor Electrónico para Medición (TEM). La información generada por el TEM será presentada a una terminal remota tipo poste que contará con un radio como medio de comunicación hacia el nivel jerárquico superior.

Figura 1.5 Sistema básico para automatización de alimentadores. (Adaptada de Ramón De la Rosa, [et.al.], op.cit.).

En el siguiente capítulo se presenta la especificación funcional del circuito Transductor Electrónico para Medición, también se describen brevemente los elementos que estarán asociados al TEM: sensores para medición y microterminales remotas.

#### CAPITURO 2

#### ESPECIFICACION FUNCIONAL DEL TRANSDUCTOR ELECTRONICO

#### 2.1 Elementos asociados ai Transductor.

Los sensores para medición constituyen el enlace directo entre el Transductor Electrónico para Medición (TEM) y las líneas de distribución, las cuales puedon ser de 13.8, 23 o 34.5 kV. Por su parte, la microterminal remota (uTR) se mencionó como el nivel de inteligencia más bajo en la arquitectura de un sistema automatizado; sin embargo, cabe mencionar que la uTR considerada en esta aplicación no es un elemento proplamente "inteligente", es decir no posee la capacidad de tomar decisiones por cuenta propia, sino que sus acciones sobre los elementos de campo están controladas por el nivel inmediato superior, la UTR de subestación.

#### Sensores para medición.

Existen diferentes tipos de sensores para la medición de variables en una red de distribución de energía eléctrica.

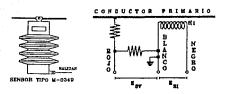

El sensor considerado para el desarrollo de este trabajo es uno tipo M-0349, fabricado por Beckwith Electric Co. Inc., de EUA (esto es sólo como referencia ya que podrá utilizarso cualquier dispositivo que cumpla con las especificaciones de entrada del TEM). Este sensor, cuyo aspecto físico y conexión de sus elementos internos se muestran en la Figura 2.1, puede ser utilizado como aislador convencional con la ventaja de que permite sensar tanto la corriente como el voltaje en las líneas de una red de distribución.

El sensor proporciona en una de sus dos salidas una señal de voltaje  $(E_{\rm S})^2$  linealmente proporcional a la corriente del conductor primario; en la otra salida, entrega una señal de voltaje  $(E_{\rm S})^2$  linealmente proporcional al voltaje de línea a tierra del conductor primario.

Figura 2.1 Aspecto físico y elementos internos del sensor para modición.

#### a) Salida de voltaje proporcional a la corriente (Es).

Una salida de voltaje de 60 Hz  $(E_{\rm SI})$  entre las terminales blanco y negro (Figura 2.1) es producida por la circulación de corriente a través del conductor primario. El valor de  $E_{\rm SI}$  está afectado directamente por el diámetro del conductor primario de la siguiente manera:

#### b) Salida de voltaje proporcional al voltaje de Iĥea $(E_{SV})$ .

Una señal de voltaje de 60 Hz ( $E_{\rm QV}$ ) linealmente proporcional al voltaje de línea a tierra del conductor primario es obtenida en la correspondiente salida del sensor (terminales bianco y rojo) y cuyo valor puede determinarse por medio de la siguiente relación:

Ep =

$$10^3$$

\*  $E_{SV}$

Ep voltaje de línea a tierra del conductor primario  $E_{SV}$  salida de voltaje

Algunas de las específicaciones proporcionadas por el fabricante para los sensores considerados se indican en la Tabla 1.

| TIPO DE SENSOR                  | 15 kV           | 25 kV                                     | 34.5 KV  |  |  |  |

|---------------------------------|-----------------|-------------------------------------------|----------|--|--|--|

| TENSION NOMINAL L-L,KV          | 15.0            | 25.0                                      | 34.5     |  |  |  |

| TENSION NAX. L-TIERRA, KV       | 8.95            | 16.0                                      | 22.0     |  |  |  |

| TENSION SOSTENIDA DE PRUEBA,KV  |                 |                                           |          |  |  |  |

| a. 60 Hz en seco                | 34.0            | 50.0                                      | 70.0     |  |  |  |

| b. 60 Hz en húmedo              | 45.0            | 70.0                                      | 95.0     |  |  |  |

| c. Impulso 1.5x50 Bil.,kV       | 110.0           | 150.0                                     | 200.0    |  |  |  |

| TENSION DE FLAMED, KV           |                 |                                           |          |  |  |  |

| a. 60 Hz en seco                |                 | 110.0                                     |          |  |  |  |

| b. 60 Hz en hûmedo              | 55.0            | 75,0                                      | 100.0    |  |  |  |

| c. Impulso 1.5x50               |                 |                                           |          |  |  |  |

| 1. Positivo                     | 125.0           | 170.0                                     | 225.0    |  |  |  |

| DISTANCIA DE FUGA,pulgadas      | 15.5            | 24,0                                      | 37.0     |  |  |  |

| TEMPERATURA DE OPERACION        | -40             | *C a +8                                   | 0.C      |  |  |  |

| CARACTERISTICAS DE SALIDA       |                 |                                           |          |  |  |  |

| a. Sensor de corriente          |                 |                                           |          |  |  |  |

| 1. Salida 60 Hz,E <sub>si</sub> | Ver exp         | Ver explicación en tex<br>±3% de lectura  |          |  |  |  |

| 2. Exactitud                    | ±3              | ±3% de lectura                            |          |  |  |  |

| 3, Impedancia de salid          | la 60 Hz        | 577 cha                                   | 3        |  |  |  |

| b. Sensor de voltaje            |                 |                                           |          |  |  |  |

| 1. Salkda 60 Hz,E <sub>ev</sub> | Ver exc         | licación i                                | en texto |  |  |  |

| 2. Volta je máximo de s         | satida, V 0.895 | Ver explicación en texto<br>0.895 1.6 2.2 |          |  |  |  |

| 3. Exactitud                    |                 | da lect                                   | ura      |  |  |  |

| SALIDA DE CORTOCIRCUITO 60 HZ   |                 | _                                         |          |  |  |  |

| a. Corriente                    | 517             | ×10 <sup>3</sup> Ann                      | peres    |  |  |  |

| b. Volta je                     | 2               | 98.2 Vol                                  | s        |  |  |  |

Tabla 1. Especificaciones del sensor de corriente y voltaje M-0349.

#### Microterminal remota.

La µTR que recibirá la información del TEM es una tipo DTE-532DL, fabricada por la compañía Desarrollo Tecnológico en Electrónica, de Chihuahua, México. Esta µTR es un equipo de adquisición de datos y telecontrol orientado al monitoreo de un número reducido de puntos que cuenta con un modem integrado para manejo de comunicaciones y una interfase directa para línea telefónica o bien para enlace directo con radio.

A través de su interfase de comunicaciones, el equipo puede enviar la información adquirida a una estación maestra localizada remotamente (en una subestación de distribución), así como recibir comandos de control para la actuación sobre puntos específicos del sistema.

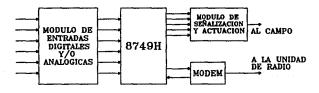

La operación de la  $\mu$ TR se centra en el microcontrolador intel 8749. La figura 2.2 muestra un diagrama a bloques de los componentes de la  $\mu$ TR.

Figura 2.2 Bioques componentes de la µTR DTE532-DL.

La  $\mu TR$  posee 8 puntos de entrada, los cuales pueden ser configurados como entradas analógicas o digitales, según se requiera.

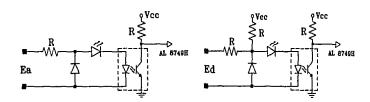

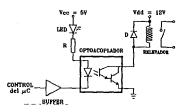

Para las entradas analógicas, el microcontrolador recibe el estado del esquema de aislación óptica asociado a la entrada (Figura 2.3a). Las entradas analógicas reciben del campo una señal de frecuencia, la cual es procesada y puesta a disposición del programa y/o del usuario, según sea el caso.

La adquisición de las señales digitales es efectuada directamente por el microcontrolador, el cual recibe el estado de aislación óptica asociado a las entradas (Figura 2.3b). La interfase de entradas digitales es igual para cualquier tipo, sean éstas de detección de cambio momentáneo, estándar o para acumuladores de pulsos, ya que la diferenciación se hace por medio de la programación del microcontrolador, de acuerdo a las funciones del protocolo de comunicaciones. Las entradas digitales reciben del campo un contacto seco (sin voltaje) y están provistas de polarización interna para detectar su movimiento.

Figura 2.3a Configuración para una entrada analógica de la u.TR.

Figura 2.3b Configuración para una entrada digital de la µTR.

Las especificaciones técnicas de la  $\mu$ TR DTE532-DL proporcionadas por el fabricante se listan en la Tabla 2.

#### 2.2 La especificación funcional del Transductor Electrónico para Medición (TEM).

De acuerdo con la información presentada en el punto anterior, puede determinarse que el circulto Transductor Electrónico para Medición deberá ser capaz de manejar las señales alternas

```

CONFIGURACION MAXIMA DEL FOLIPO.

Entradas digitales:

8 puntos (*)

4 puntos (2 mandos dobles)

Satidas digitales:

Entradas analogicas:

8 nuntos (*)

PROCESAMIENTO.

Procesador:

8 bits

Memoria EPROM:

2 kilobytes

Menoria RAM:

128 bytes

Puertos paralelos E/S:

2 de 8 bits

1 de 8 bits

Temporizador:

ENTRADAS DIGITALES.

Máx. de puntos:

Hasta 1 (de los 8)

Acumuladores:

Conexión:

Contacto seco

Duración del pulso:

10 ms (mínimo)

Alstaniento ôntico

Protecciones:

Relevador (cocional)

Interposición:

ENTRADAS AVALOGICAS.

Núm. Máx. de canales:

Hasta 8 (de los 8 puntos digitales)

Aistación:

Doto-transistor

Señales de entrada:

Frecuencia de 1-6 kHz

Frecuencia de 0-100 Hz

(Otras escalas según se solicite)

SALIDAS DE CONTROL.

Hasta 4 (2 dobles)

Núis, de salidas:

Contacto NA o NC

Tipo de salida:

10 A @ 250 Vac

Capacidad:

Programable (0.5s tfp.)

Tiempo de operación:

Hasta 250 Vac

Alim, contactos de salida:

DIAGNOSTICOS.

Local:

Lámoaras indicadoras

COM INICACIONES.

Moden integrado

Modulación:

FSK

Velocidad:

300 bands

600 ohres

Impedancia de salida:

Protecciones:

Transitorios (SMC)

Radio-

15 watts

PROTOCOLO DE COMUNICACIONES.

7 bits

Dirección:

1 a 8 bits

Function:

Código de seguridad:

Regundante/Cogniegento

Longitud del Telegrama:

Variable

FUENTE DE ALBENTACION.

Alimentación primaria:

127 Vac ± 10%

Voltaie de salida:

14 Vdc @ 4.5 Amperes

Bateria de respaldo:

12 Vdc @ 4 Amperes-hora

GARINETE.

Operación:

Exteriores

NEMA 4X

Norma:

20x16x8 pulgadas

Dimensiones:

*Mutuamente excluyentes

```

Tabla 2. Especificaciones para la uTR DTE-5320L.

proporcionadas por los sensores, procesarias y entregar en su salida señales compatibles con las entradas de la uTR.

La información recibida por la "TR puede ser utilizada en un sistema de control supervisorlo con fines de protección, monitoreo, medición, automatización, corrección de factor de potencia, etc.

#### Características funcionales.

Las funciones y características generales que deberá cubrir el Transductor Electrónico para Medición (TEX) son las siguientes:

- a) Construido a base de dispositivos de estado sólido y emplear como elemento principal un microcontrolador.

- b) Tarjeta del circuito impreso lo más pequeña posible de tal forma que pueda ser integrada dentro de una UTR tipo poste (µTR). En su defecto, la tarjeta será protegida en una caja metálica tipo intemperie.

- c) Contar con dispositivos locales indicadores de falla (LEDs) que muestren su estado de operación (correcto-incorrecto).

- d) Asimismo, existirán en la tarjeta puntos especiales para medición en campo de los parámetros manejados por el TEM.

- e) La alimentación para el TEM será proporcionada por una fuente propia que recibirá una señai alterna en baja tensión (127 Vac, 60 Hz) y contendrá una batería como respaldo.

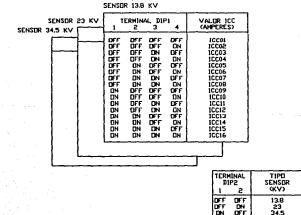

- f) El TEM deberá ser capaz de procesar las seis entradas alternas provenientes de los sensores para medición, calcular el valor eficaz de cada una de ellas y luego determinar:

- el valor promedio de los tres voltales de fase

- el valor promedio de las tres corrientes de fase

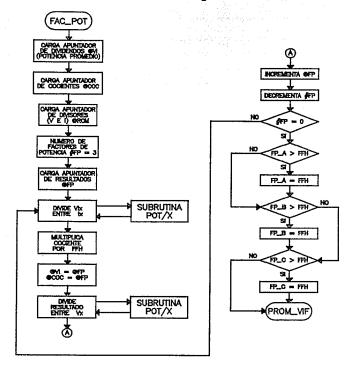

- g) También, el TEM deberá calcular el factor de potencia de cada fase y después el valor promedio de los mismos.

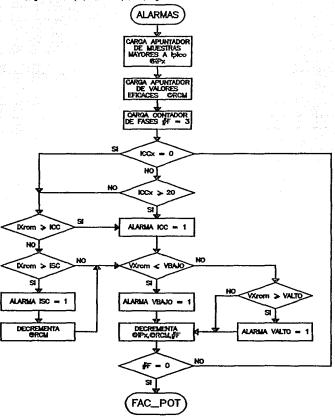

- h) Indicar, por medio de alarmas, la detección de las siguientes condiciones:

- voltaje alto (Valto)

- voltaje bajo (Vbajo)

- corriente de cortocircuito (icc)

- corriente de sobrecarga (isc)

Las señales de entrada serán continuamente comparadas con sus respectivos valores límites, previamente establecidos, para que al momento en que cualesquiera de ellas calga fuera de su rango se genere la correspondiente señal de alarma.

Toda esta información, analógica y digital, será presentada en las entradas de la uTR.

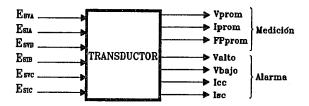

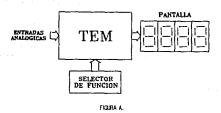

El siguiente bioque (Figura 2.4) muestra la denominación de las entradas y salidas del TEM.

Figura 2.4 Entradas y salidas del Transductor Electrónico para Medición.

#### Entradas.

${\sf E_{SV}}$  y  ${\sf E_{SI}}$  son ambas señales alternas de voltaje en el rango de  ${\sf a5}$  Vpico, representativas del voltaje y la corriente de fase respectivamente.

#### Salidas para medición.

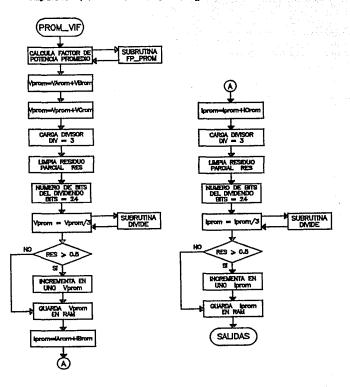

Estas tienen fines de medición y estadística, por lo que se hace necesario obtener un valor promedio y no el valor instantáneo. La definición de estas salidas es como sigue:

Iprom es una salida que representará el promedio de los valores eficaces (rcm) de las tres corrientes de fase.

Vprom es una salida que representará el promedio de los valores eficaces (rcm) de los tros voltales de fase.

FPprom es una salida que representará el valor promedio de los ángulos entre voltaje y corriente de cada fase.

El intervalo de actualización de estas salidas de medición deberá ser el mínimo posiblo y serán presentadas en un rango de frecuencia compatible con las entradas de la µTR. El valor mínimo de frecuencia corresponderá a una entrada mínima y el valor máximo de frecuencia al correspondiente límite superior en la entrada.

#### Salidas de alarma.

Las señales de alarma están orientadas para ser utilizadas en sistemas automáticos de control y protección. El TEM proporcionará las siguientes salidas:

Vmáx señal que indica que el voltaje de una o más fases está por encima del valor máximo permitido.

Vmín señal que indica que el voltaje de una o más fases ha caído por debajo del valor permitido.

/cc cuando en cualesquiera de las fases se detecta una corriente superior a un valor de cortocircuito establecido, la señal icc se activa.

isc cuando se detecta en cualesquiera de las fases una corriente de operación superior a un valor de sobrecarga dado, la señal isc se activa.

Estas salidas de alarma son señales digitales del tipo activa-inactiva con niveles de voltaje de cinco (activa) o cero volts (inactiva).

#### Valores limites.

Los valores límites para las señales de alarma podrán ser establecidos externamente para las tres fases.

En base a las específicaciones proporcionadas en este capítulo se diseñará el circulto Transductor Electrónico para Medición (TEM). El siguiente capítulo presenta el procedimiento seguido para el desarrollo del diseño.

#### CAPITULO 3

#### DISERO Y CONSTRUCCION DEL TRANSDUCTOR ELECTRONICO PROTOTIPO

#### 3.1 Principio de operación del Transductor Electrónico para Medición prototipo.

De acuerdo con las especificaciones establecidas en el capítulo 2, el Transductor Electrónico para Medición (TEM) deberá calcular los valores eficaces o rcm (raíz cuadrática media) de sels señales alternas (representativas de voltajes y corrientes de fase) y también el factor de potencia de cada fase para luego determinar los valores promedio de estos tres parámetros. Cada uno de los resultados promedio obtenidos serán presentados como una señal de frecuencia variable en las respectivas salidas y se activarán las señales de alarma correspondientes en caso de condiciones anormales en los valores eficaces medidos.

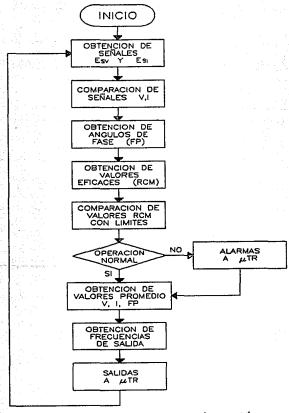

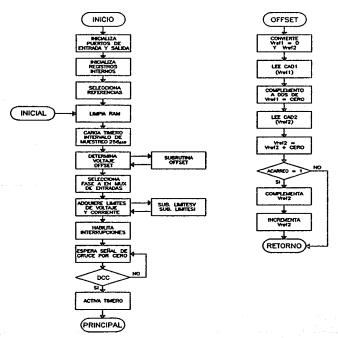

La Figura 3.1 muestra un diagrama a bloques que describe en forma general la secuencia de acciones que deberá realizar el TEM, desde la adquisición de las señales alternas de entrada hasta la generación de las señales digitales de salida.

En las especificaciones para el TEM se indicó que éste debería ser diseñado en base a un microcontrolador. Por otra parte, como se expuso en el punto 1 del capítulo 2, las señales que entrega en su salida un sensor para medición, proporcionales al voltaje y a la corriente de fase, son ambas señales de voltaje ( $\mathbb{E}_{SY}$  y  $\mathbb{E}_{SI}$ ), por lo que será necesario convertir estas señales a una forma digital para que así puedan ser procesadas por el TEM.

Figura 3,1 Funcionaziento general del Transductor Electrónico para Medición.

Una expresión matemática general para el cálculo del factor de potencia en un circulto de corriente alterna, para cualquier forma de onda de voltaje y corriente, se establece como sigue:

$$FP = \frac{\text{Potencia media}}{\text{Vrcm - Irem}}$$

(3.1)

donde FP es el factor de potencia y Vrcm e Ircm son los valores eficaces de las ondas de Voltaje y corriente. Expresada en forma equivalente:

$$FP = \frac{\frac{1}{T} \int_{0}^{T} v(t) \cdot i(t) dt}{\sqrt{\frac{1}{T} \int_{0}^{T} v(t)^{2} dt} \cdot \sqrt{\frac{1}{T} \int_{0}^{T} i(t)^{2} dt}}.$$

(3.2)

La evaluación de esta ecuación puede realizarse por medio de la técnica digital de muestreo<sup>9,10</sup>. Esta consiste en tomar muestras simultáneas de las señales de voltaje y corriente a intervalos iguales de tiempo sobre un número entero de ciclos; por lo tanto, un ciclo es dividido en N secciones, cada una de las cuales tiene su correspondiente valor instantáneo de voltaje y corriente.

En la ecuación 3.2 las integrales pueden ser reemplazadas por una sumatoria y el intervalo de tiempo T por el número de muestras tomadas H:

$$FP = \frac{\frac{1}{N} \sum_{j=1}^{N} v(t)_{j} \cdot i(t)_{j}}{\sqrt{\frac{1}{N} \sum_{j=1}^{N} v(t)_{j}^{2}} \cdot \sqrt{\frac{1}{N} \sum_{j=1}^{N} i(t)_{j}^{2}}}.$$

(3.3)

<sup>&</sup>lt;sup>9</sup>TURGEL, RAYMONO S. 'Digital Mattereter Using a Sampling Method\*. En: <u>IEEE Transactions on Instrumentation and Measurement</u>, v.M-63, n.4 (Dic. 1974), pp.337-341.

<sup>&</sup>lt;sup>10</sup>DURWI, S.S. (et.al.). "Microcomputer-controlled sampling digital power, ras and PF meter". En: Int. Journal of Electronics, v.63, n.3 (1997), pp. 455-461.

Los valores instantáneos de voltaje y corriente pueden ser digitalizados utilizando un convertidor analógico-digital (CAD) y las salidas resultantes,  $\mathbf{v_j}$  e  $\mathbf{I_j}$ , pueden ser entonces empleadas por el microcontrolador para el cálculo de los valores eficaces, la potencia promedio y con éstos el factor de potencia.

#### 3.2 Diseño del Transductor Electrónico para Medición prototipo.

La utilización de un microcontrolador en el diseño del TEM proporcionará flexibilidad en cuanto a futuros cambios en su operación modificando su programa. Para contribuir a lo anterior, el circuito será diseñado en forma modular para facilitar también su modificación.

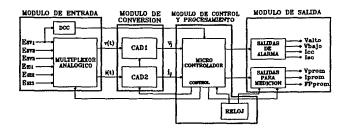

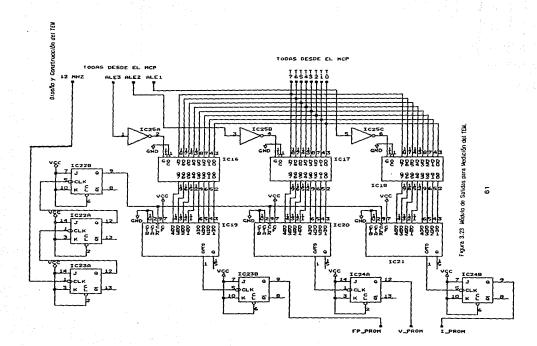

Se ha dividido el desarrollo del TEM en cuatro módulos principales, denominados:

- 1) Módulo de entrada

- 2) Módulo de conversión

- 3) Módulo de control y procesamiento

- 4) Módulo de salida

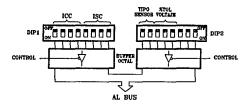

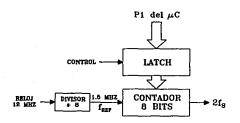

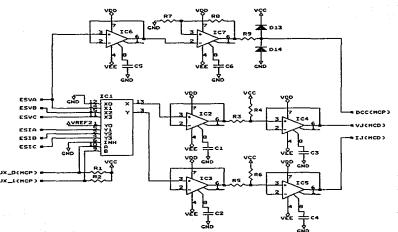

La Figura 3.2 muestra un diagrama a bioques del circulto prototipo del TEM y se indica la relación entre ellos.

En el diagrama, las ilneas de control servirán para seleccionar cada uno de los tres pares de señales de entrada e iniciar el muestreo de éstas para luego almacenarias dentro del microcontrolador. Otras líneas controlarán el envío de información hacia el módulo de salidas.

Un circuito detector de cruce por cero (DCC) será utilizado para sincronizar el ciclo de muestreo con el inicio y fin de la señal de referencia.

Los valores eficaces de voltaje y corriente de cada fase serán comparados dentro del microcontrolador con los niveles límites prestablecidos para cada uno de ellos y si caen fuera del rango permitido, se activarán las señales de alarma correspondientes.

Figura 3.2 Diagrama a bloques del Transductor Electrónico para Medición prototipo.

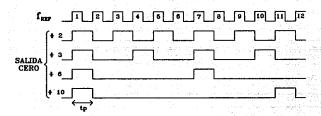

El circuito de reloj será el encargado de generar la base de tiempos para el funcionamiento del microcontrolador y la generación de las salidas en frecuencia.

Para diseñar cada uno de los módulos es necesario considerar algunos aspectos para la selección de los elementos electrónicos que los integrarán, en especial para los módulos de conversión y de control y procesamiento, puesto que en ellos se basará primordialmente el funcionamiento del TEM.

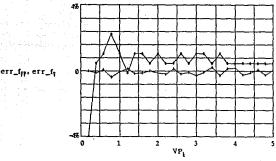

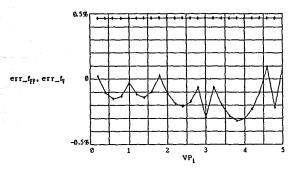

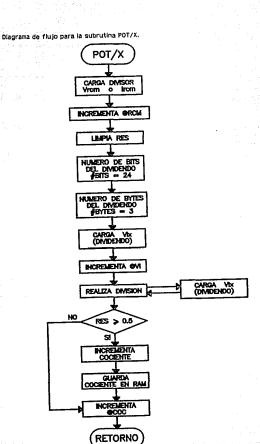

Como puede observarse en la anterior ecuación 3.3, el módulo de control y procesamiento deberá realizar operaciones de suma, multiplicación, división y obtención de raíz cuadrada. Por otra parte, ¿qué cantidad de muestras por ciclo será necesario tomar para obtener un resultado correcto en la evaluación de esta ecuación? En Omran et.al.,1987 se presenta un análisis del error en función del número de muestras por ciclo y una gráfica, mostrada en la Figura 3.3, en la cual puede apreciarse que el porcentaje de error entre el valor real y el calculado se mantiene constante y aproximadamente igual a 0.02% para un número de muestras por ciclo mayor a 500 (considerando un CAD de 8 bits<sup>11</sup> y una frecuencia de 30 a 70 Hz para la señal de entrada).

<sup>11</sup>bit (binary digit o dígito binario).

Floura 3.3 Error en el cálculo del FP en función del número de muestras y resolución de conversión.

Suponiendo la aplicación de una razón de muestreo de 512 muestras/ciclo para cada uno de los tres pares de señales de entrada, la frecuencia de muestreo sería (512)(3)(60) = 92.16 kHz, (para señales de 60 Hz); es decir, una muestra por fase cada 10.85 µs (1/92.16 kHz). Para almacenar las muestras tomadas durante un ciclo sería necesaria una memoria de lectura/escritura o RAM (Random Acces Memory) con una capacidad de 3 kilobytes<sup>12</sup>; las muestras adquiridas al final del ciclo de conversión serían luego empleadas para realizar los cálculos necesarios. La mayor parte de los 10.85 µs se emplearían para seleccionar las señales de entrada, direccionar la RAM y generar las órdenes de escritura, por lo que sería necesario un CAD con un ciclo de conversión <sup>13</sup> menor a 2 µs.

<sup>12</sup>kliobyte = 1000 bytes. Una palabra de 8 bits constituye un byte.

<sup>&</sup>lt;sup>13</sup>Tiempo que transcurre desde la aplicación de una orden de conversión hasta la obtención de datos válidos en la salida del CAO,

El empleo de una memoria RAM de tal capacidad implica un costo extru y sobre todo complejidad en el sistema. Por esto, se realizó un programa de computadora para determinar el número mínimo necesario de muestras por ciclo, que combinado con un CAD de bajo tiempo de conversión y un microcontrolador de alta capacidad de procesamiento, permitiera la eliminación de la memoria RAM del diseño; por otra parte, el número de muestras tomadas deberá ser tal que no afecte considerablemente la exactitud en el cálculo de la ecuación 3-3.

Con el análisis realizado, presentado en el ANEXO 1, se determinó un error de aproximadamente 1% para una frecuencia de muestreo de 4.5 kHz (25 muestras/cicio por fase), es decir se muestrearia una fase cada 222 µs. Con la selección de un CAD con un tiempo de conversión mínimo y un microcontrolador con buena capacidad de procesamiento, este tiempo podría ser más que suficiente para muestrear las seis señales de entrada y procesar las muestras obtenidas antes de tomar las siguientes, evitándose así la utilización de una RAM.

Otro aspecto del diseño lo constituye la selección del tipo de circuitos a utilizar. Para la construcción de los módulos del TEM se ha elegido circuitoría con tecnología CMOS de alta velocidad o HCMOS (High speed Complementary Metal Oxide Silicon, o Silicón con Complemento de Oxido Metálico), en primer lugar, por la razón de que se requiere el manejo de gran cantidad de información tanto analógica como digital en cortos períodos de tiempo y por otra parte, este tipo de tecnología consume baja potencia, lo cual la hace adecuada para su aplicación en sistemas atimentados con baterías, como es el caso del TEM.

Otras características de los circultos HCMOS que los hacen más adecuados para esta aplicación sobre otro tipo de tecnologías son su alta immunidad al ruido (0.9 a 1.35 volts), amplio rango de temperatura de operación (-55 a 125°C) y excelente respuesta a variaciones del voltaje de alimentación (Vcc de 2 a 6 volts)<sup>14</sup>

#### 3.2.1 Módulo de entrada.

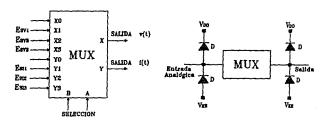

Este módulo consta básicamente de un multiplexor analógico para el manejo de las señales de entrada. Se ha incluido en este punto el diseño del circuito detector de cruce por cero (DCC), ya que a éste le es aplicada una de las señales entrada tomada como referencia.

<sup>14</sup> MOTOROLA INC. Motorola High-speed CMOS Logic Data. (EVA: Motorola inc.,c1989). pp. 4-3,4-4.

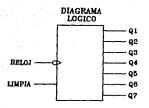

Puesto que se requiere tomar muestras simultâneas de un par de señales a la vez, se ha seleccionado un multiplexor doble de 4 a 1, el 74HC4052 cuyo diagrama se muestra en la Figura 3.4.

Con una polarización de  $V_{00}$  = +5V y  $V_{EE}$  = -5V, el multiplexor podrá manejar las señales alternas de  $\pm$ 5V pico especificadas como entradas máximas para el TEM. En la Figura 3.4 so muestra también el esquema de protección para las entradas y salidas del multiplexor, los diodos utilizados para tal efecto son de silicio de pequeña señal (1N914) y se emplean para limitar los voltajes de entrada a los niveles de polarización en el caso de que se presenten voltajes transitorios por encima de  $V_{00}$  o por debajo de  $V_{FF}$ .

Figura 3.4 Diagrama lógico del multiplexor analógico 74/04052, Protección de entradas y salidas contra voltajes transitorios excessivos.

Las ifineas de selección A y B del multiplexor serán utilizadas por el microcontrolador para hacer llegar hacia el módulo de conversión cada uno de los tres pares de señales de entrada (X1-Y1, X2-Y2, X3-Y3).

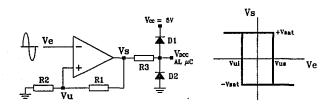

#### 3.2.1.1 Circuito detector de cruce por cero.

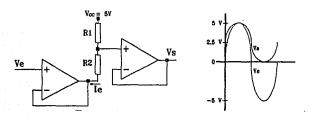

El circulto mostrado en la Figura 3.5 es un detector de cruce por cero con histéresis. El funcionamiento del circuito, compuesto por un amplificador operacional (op-amp) en configuración de

inversor, es como sigue: cuando la señal de entrada. Ve sobrepasa un valor. V<sub>US</sub> (voltaje de umbral superior) la salida. Vs. irá al voltaje de saturación negativo. --Veat, y cuando el voltaje de entrada sea menor a un valor. V<sub>UI</sub> (voltaje de umbral inferior), la salida será igual al voltaje de saturación positivo.+-Veat. tal como se ilustra en la gráfica de la misma figura.

Los niveles de saturación en la salida del op-amp generalmente son un volt menores que los voltajes de polarización, que para este caso serán de £12 V. Se ha elegido un op-amp de precisión, el LM108, debido a sus características de baja corriente de polarización de entrada y bajo consumo de corriente aún en saturación, entre otras.

Figura 3.5 Diagrama del circuito detector de cruce por cero.

Puesto que la señal generada por este circuito será aplicada al módulo de control, en la salida del op-amp se emplean dos diodos para limitar la señal Vs a los niveles de D y 5 volts, que son los niveles lógicos mínimo y máximo que maneja el microcontrolador.

El voltaje de referencia. Vu, aplicado en la entrada no inversora del op-amp, es una fracción del voltaje de salida. Vs. y es obtenido por medio de un divisor resistivo (R<sub>1</sub> y R<sub>2</sub>). Este voltaje de referencia debe ser lo sufficientemente pequeño para que los cambios en la salida se efectúen cuando la señal de entrada tiene un valor cercano a cero y también, Vu debe ser lo sufficientemente grande para prevenir que el circuito discrimine posibles señales de ruido que ocasionarían detecciones falsas de cruce por cero.

Para calcular los volta les de umbral que determinan el ciclo de histèresis se tione que 15:

$$V_{Ug} = \frac{R_2}{R_1 + R_2} (+V_{se}).$$

(3.4)

$$V_{UI} = \frac{R_2}{R_1 + R_2} (-V_{mil})$$

(3.5)

SI +Vsat = -Vsat = Vsat:

$$V_U = \frac{R_2}{R_1 + R_2} V_{\underline{m}}$$

(3.6)

Despejando Ra:

$$R_2 = \frac{V_U}{V_{\text{max}} - V_U} R_1. \tag{3.7}$$

Para un ciclo de histéresis de 5 mV, es decir  $V_{LS} = 2.5$  mV y  $V_{UI} = -2.5$  mV, un voltaje de saturación Vsat = 12 V y una resistencia  $R_1 = 10$  M $\Omega$ :

$$R_2 = \frac{5mV}{12V - 5mV} 10M\Omega$$

$$R_2 = 4.16 \text{ K}\Omega$$

Para un voltaje Vs = -Vsat se tiene en la malla de salida:

$$R_3 = \frac{V_{set} - V_{DCC}}{I}$$

(3.8)

<sup>15</sup>poert F. COUGHLIN, FREDERICK F. DRISCOLL. <u>Circuitos integrados lineales y anolificadores operacionales.</u> (México: Prentice-Hall, c1997). 394 pp.

donde I es la corriente a través del diodo D<sub>2</sub> fluyendo hacia el op-amp y V<sub>000</sub> es el voltaje en el diodo, el cual está específicado como 1 V ● 10 mA. Sustituyendo estos valores en la Ec. 3.8:

$$R_3 = \frac{12V - 1V}{10mA}$$

$$R_3 = 1.1 \text{ KO}$$

#### 3.2.2 Módulo de conversión.

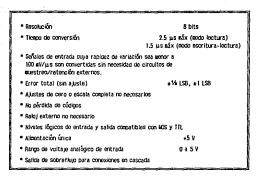

El convertidor analógico-digital (CAD) utilizado para el diseño del módulo de conversión es el ADCO820, cuyas características se listan en la Tabla 3 y la identificación de sus terminales se muestra en la Figura 3.6.

Como puede observarse en la tabla, este CAD cubre el requisito de un tiempo de conversión mínimo; sin embargo, sólo puede manejar señales analógicas en el rango de 0 a 5 volts, por lo que será necesario diseñar un circuito que acondicione las entradas al TEM (45 V) a niveles de 0 a 5 volts pico-pico. Este circuito acondicionador será descrito en el siguiente punto.

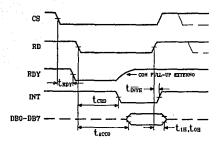

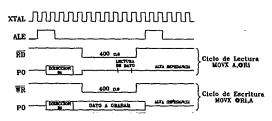

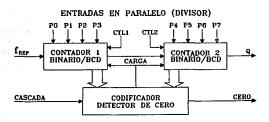

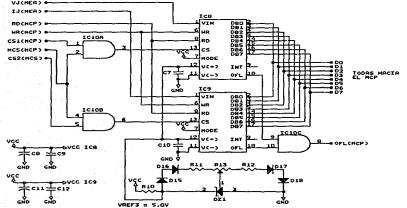

El convertidor tiene dos modos de funcionamiento seleccionables por medio de la terminal MODE. El primero de ellos es el Modo de Lectura (MODE en bajo), en este modo con CS en bajo, la conversión se iniciará en la transición negativa del pulso RD; CS y RD deben permanecer en bajo hasta el final de la conversión, lo cual será indicado por la transición alto-bajo de INT y un estado de alta impedancia en la terminal RDY para habilitar la salida de datos (DBO a DB7). La Figura 3.7a muestra el diagrama de tiempos para este modo.

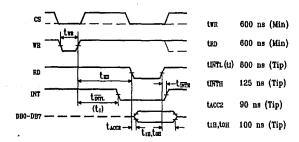

En el Modo Escritura-Lectura (MODE en alto), con CS en bajo la conversión se inicia en la transición negativa del pulso WR. Aproximadamente 800 ns después de la transición positiva del pulso WR, el resultado de la conversión estará dispuesto para ser leído y esto será indicado por la transición alto-bajo de INT. Los datos DBO a DB7 estarán presentes en la salida cuando se realice la transición negativa del pulso RD. El diagrama y especificaciones de tiempos para este modo se muestran en la Figura 3.7b.

Tabla 3. Características del convertidor analógico-digital ADC0820

Figura 3.6 Identificación de terminales del convertidor analógico-digital ADCO820.

Se requieren dos CADs para esta aplicación y serán utilizados en el modo Escritura-Lectura, esto permitirá generar una señal única WR para iniciar la conversión en ambos al mismo tiempo y después iter en secuencia las salidas utilizando un pulso RD para cada convertidor.

Figura 3.7a Diagrama de tiempos para el modo lectura (MODE en bajo).

Figura 3.7b Diagrama y especificación de tiespos para el modo escritura-lectura (MODE en alto).

Si el voltaje analógico de entrada en un instante es mayor que el voltaje de referencia V<sub>REF(+)</sub> = +5 V, la terminal OFL cambiará de alto a bajo al final del ciclo de conversión. Esta señal puede ser utilizada para conectar en cascada dos o más convertidores y aumentar así el número de bits, o como es el caso de este diseño, puede ser utilizado como una alarma para indicar un voltaje de entrada fuera del línite superior permitido.

## 3.2.2.1 Circuito acondicionador de señal.

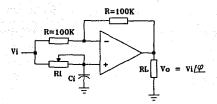

Este circuito convertirá la señal alterna de entrada (10 V pico-pico) a una señal directa variable entre 0 y 5 V con la misma forma de onda de la señal de entrada. El circuito considerado y la relación de las señales de entrada y salida se muestran en la Figura 3.8.

Figura 3.8 Circuito acondicionador de las soñales de entrada aplicadas el CAD.

El circuito está constituido por dos op-amps como seguidores de voltaje, el primero proporciona una impedancia de entrada alta y el segundo una impedancia de salida lo suficientemente baja para un adecuado acoplamiento de este circuito al CAD. El divisor resistivo monta la salida en una componente de 2.5V (Vs = 2.5V si Ve = 0) y proporciona la señal dentro de los límitos requeridos.

La ecuación para el voltaje de salida Vs es:

$$V_8 = \frac{(V_{\infty} - V_{e}) R_2}{R_1 + R_2} + V_{e}.$$

(3.9)

Si R<sub>4</sub> = R<sub>5</sub> = R se tendrá que:

$$V_8 = \frac{V_{\infty} - V_0}{2} + V_0 - \dots$$

(3.16)

Para obtener la máxima excursión de voltaje en la salida del primer seguldor de voltajo la corriente de salida del op-amp debe ser mínima; estableciendo un valor máximo de 250 µA para le se tiene que para el primer op-amp:

$$Ie = \frac{V \infty - Ve}{2R} \tag{3.11}$$

le será máxima para Ve = 0, por lo tanto:

$$R = \frac{5V}{2(250\mu A)}$$

$$R = 10 K\Omega$$

## 3.2.3 Módulo de control y procesamiento.

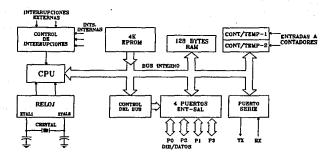

El módulo de control y procesamiento, que será el corazón del TEM, lo constituye el microcontrolador. Como se menciona al inicio de este capítulo, este circuito deberá contar con la capacidad de realizar operaciones de suma, multiplicación y división a una velocidad lo mayor posible. Después de un análisis de diferentes microcontroladores, se eligió para el diseño del TEM a la familia 8051 de inte<sup>FR</sup>. Las características del microcontrolador utilizado, el 8751H, se listan en la Tabla 4. (Las figuras que hacen referencia al microcontrolador 8751 fueron traducidas y adaptadas del manual: intel 8-bit Embedded Controller Handbook, 1990; el cual puede consultarse para mayor información sobre éste y otros dispositivos de la familia MCS-51<sup>M</sup>1).

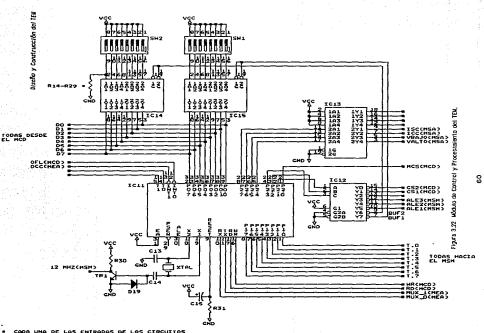

La Figura 3.9 muestra la estructura básica de la arquitectura del microcontrolador 8751H. A continuación se presenta una breve descripción de las características do este circuito, que lo hacen ideal para su aplicación en este trabajo y además pueden permitir futuras mejoras en el desempeño del TEM.

Para el funcionamiento del 8751H se ha seleccionado la frecuencia más alta de reloj, 12 MHz, lo cual representa un ciclo de instrucción de 1 µs. Esto permitirá tomar una mayor cantidad de muestras de las señales de entrada y sobre todo procesar los datos obtenidos y actualizar las salidas con mayor rapidez.

| <ul> <li>Tecnología de fabricación</li> </ul>                          | HMOS                                     |  |

|------------------------------------------------------------------------|------------------------------------------|--|

| • Voltaje de alipentación                                              | +5 V                                     |  |

| * Frecuencia de reloj                                                  | 3.5 a 12 MHz                             |  |

| * Puertos de entrada-salida                                            | 4 (8 Ifneas c/u)                         |  |

| • Puerto para comunicación serie                                       | Full duplex                              |  |

| * Fuentes de interrupción                                              | 5 (2 externas,3 internas)                |  |

| • Hiveles de prioridad de Interrupción                                 | 2                                        |  |

| Contadores/Temporizadores Internos                                     | 2 de 16 bits                             |  |

| <ul> <li>Unidad Central de Procesasiento (CPU)<sup>16</sup></li> </ul> | 8 bits                                   |  |

| • Memoria de programa (EPROM) <sup>17</sup>                            | 4K × B                                   |  |

| • Memoria RAM                                                          | 128 x 8                                  |  |

| • Juego de instrucciones                                               | 111 (64 de un sõlo ciclo <sup>18</sup> ) |  |

Tabla 4, Características del microcontrolador 8751H.

Para generar la frecuencia de trabajo del microcontrolador se utilizará un cristal de cuarzo de 12 MHz conectado en las terminales correspondientes del circuito (XTAL1 y XTAL2).

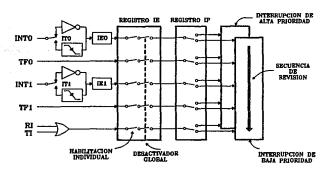

El 8751H posee cinco fuentes de interrupción: dos externas, dos internas y una proveniente del puerto para comunicación serie. Una de las primeras será generada por la señal del circuito detector de cruce por cero (DCC), para iniciar en ese instante el proceso de muestreo y cálculo.

La Figura 3.10 muestra en mayor detalle el bloque de control de Interrupciones. Cada una de éstas puede ser habilitada/deshabilitada individualmente por medio de la asignación de un valor 1 o O respectivamente, en los correspondientes bits del registro IE. Físicamente esto equivale a cerrar

<sup>16</sup>CPU (Central Process Unit)

<sup>17</sup> EPROM (Erasable Programmable Read Only Memory o Memoria de sólo Lectura Programable y Borrable)

<sup>18</sup>El tiempo de duración de un ciclo de instrucción es igual a 12/f<sub>RFI (L.)</sub>.

Figura 3.9 Diagrama a bloques de la estructura interna del microcontrolador 8751.

Figura 3.10 Sistema de control de interrupciones del microcontrolador 8751.

o abrir un interruptor electrónico que ceda o niegue el paso de las señales de interrupción hacia la CPU. También, como puede observarse en la figura, existe un control (un bit en el registro IE) para deshabilitación de todas en conjunto.

Por otro lado, cada interrupción puede tener uno de dos niveles de prioridad: alto (bit-1) o bajo (bit-0), según se programen los bits del registro IP. Los niveles de prioridad se refieren a que una interrupción de baja prioridad puede ser a su vez interrumpida por una de alta prioridad, pero no por otra de baja prioridad y que una interrupción de alta prioridad no puede ser interrumpida por ninguna otra.

Si dos peticiones de interrupción de diferente nivel se presentan simultáneamente, la petición de mayor prioridad será atendida. Cuando se presentan dos peticiones simultáneas de interrupción del mismo nivel, se realiza una secuencia de revisión (polling) para determinar cuál petición será atendida en primer lugar.

En la Figura 3.10, INTO e INT1 son las entradas para las señales que generan las interrupciones externas y RI junto con Ti (interrupciones de recepción y transmisión) generan la del puerto serie. TFO y TF1 son las señales de interrupción internas generadas por sobrefíujos en los contadores TO y T1 respectivamente.

El 8751H posee dos temporizadores, uno de ellos será utilizado para establecer el intervalo de muestreo, es decir, los instantes en que deberán tomarse muestras de las señales de entrada. El segundo temporizador servirá como un "escape" en el caso de que por algún motivo la señal DCC que indica el final del ciclo de muestreo no se presentara.

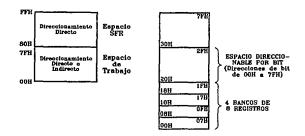

La CPU es el "cerebro" del 8751H, es aquí desde donde se accesan, se decodifican y ejecutan las instrucciones de programa contenidas en la memoria EPROM. La CPU está integrado básicamente por la Unidad Aritmética-Lógica (ALU, Arithmetic-Logic Unit) y sus registros asociados, denominados Acumulador (A), Registro B, Registro de Estado del Programa (PSW, Program Status Word), el Apuntador de la Pila (SP, Stack Pointer) y los registros de 16 bits Contador de Programa (PC, Program Counter) y Registro Apuntador de Datos (DPTR, Data Pointer Register), todos ellos contenidos en una sección de la RAM.

La CPU realiza todas las operaciones aritméticas y lógicas indicadas por las instrucciones del programa con datos contenidos en la RAM o provenientes de los puertos de entrada-salida; también controla la transferencia de información entre los diferentes registros.

#### Memoria RAM.