# UNIVERSIDAD NACIONAL AUTONOMA DE MEXICO

# **FACULTAD DE INGENIERIA**

# SISTEMA PARA MONITOREO Y CONTROL DE PROCESOS MONOVARIABLES ANALOGICOS BASADO EN LA NORMA IEEE-961

TESIS

QUE PARA OBTENER EL TITULO DE

INGENIERO MECANICO ELECTRICISTA

(AREA ELECTRONICA)

PRESENTAN:

ACOSTA CASTRO EDUARDO

PALI RODRIGUEZ EDGAR MANUEL

STONE AGUILAR JESUS EDUARDO

México, D. F.

1991

# UNAM – Dirección General de Bibliotecas Tesis Digitales Restricciones de uso

# DERECHOS RESERVADOS © PROHIBIDA SU REPRODUCCIÓN TOTAL O PARCIAL

Todo el material contenido en esta tesis está protegido por la Ley Federal del Derecho de Autor (LFDA) de los Estados Unidos Mexicanos (México).

El uso de imágenes, fragmentos de videos, y demás material que sea objeto de protección de los derechos de autor, será exclusivamente para fines educativos e informativos y deberá citar la fuente donde la obtuvo mencionando el autor o autores. Cualquier uso distinto como el lucro, reproducción, edición o modificación, será perseguido y sancionado por el respectivo titular de los Derechos de Autor.

# TEMARIO

- I Objetivo.

- II Introducción.

- III Diseño del módulo A/D.

- III.1 Descripción del módulo.

- III.2 Convertidor ADC1205.

- III.3 Etapa analógica de entrada.

- III.4 Decodificación de dispositivos.

- III.5 Proceso de conversión.

- IV Diseño del módulo D/A.

- IV.1 Descripción del módulo.

- IV.2 Convertidor DAC1230.

- IV.3 Decodificación de dispositivos.

- IV.4 Proceso de conversión.

- V Diseño del módulo generador de interrupciones.

- V.1 Descripción del módulo.

- V.2 Temporizador programable 8253.

- V.3 Decodificación de dispositivos.

- V.4 Procedimiento de interrupción.

- VI Programación de los módulos.

- VI.1 Programación del módulo A/D.

- VI.2 Programación del módulo D/A.

- VI.3 Programación del módulo de interrupciones.

- VII Planteamiento del problema: Control de un horno eléctrico de 1000 °C.

- VII.1 Acondicionamiento de la señal.

- VII.2 Diseño de el actuador.

- VII.3 Implementación del algoritmo de control.

- VII.4 Resultados de las pruebas.

- VIII Conclusiones.

- IX Bibliografía.

# A Apéndices.

- A.1 Revisión de la norma IEEE-961.

- A.2 Revisión del Controlador Universal Industrial (CUI).

- A.3 Revisión de sensores de temperatura.

- A.4 Revisión del Multibasic.

- A.5 Programas.

- A.5.1 Programa de iniciación y uso de los módulos.

- A.5.2 Programa del algoritmo de control.

- A.6 Procedimientos de ajuste.

- A.7 Listado de componentes.

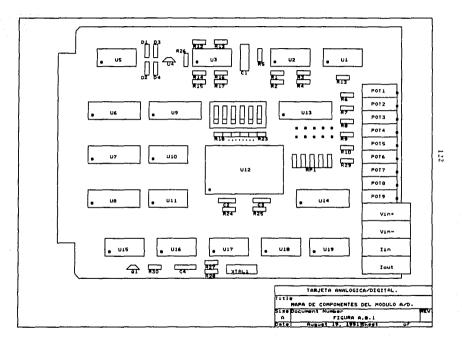

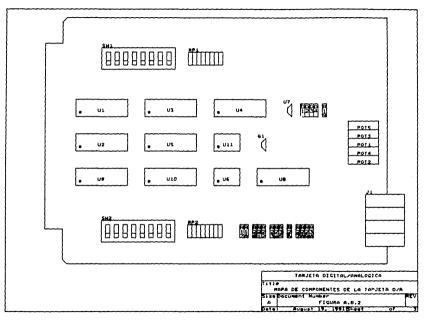

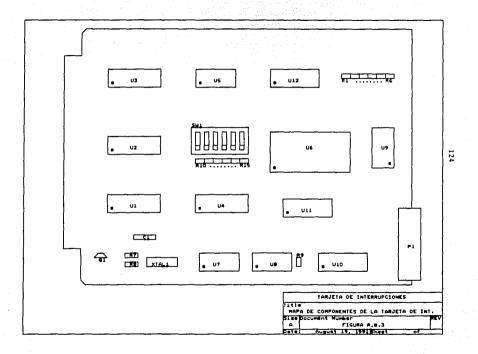

- A.8 Mapa de componentes.

- A.9 Especificaciones técnicas de los módulos.

### I. OBJETIVO

El objetivo de este trabajo es el diseño y la construcción del prototipo de un sistema electrónico capaz de monitorear y controlar procesos monovariables analógicos basado en el uso de convertidores A/D y D/A cumpliendo con la norma IEEE-961 en su bus de comunicación.

# II. INTRODUCCION

Las necesidades en la industria actual en México tienen requerimientos cada vez mayores de tecnología para poder competir en los mercados internacionales; ello se traduce en la necesidad de tener un control adecuado y autónomo en sus procesos de producción, lo que da por resultado que el industrial se vea obligado a importar dicha tecnología a un alto costo.

La idea de desarrollar en México un sistema de control de procesos que cumpla con las especificaciones de un estándar industrial internacional, que sea sencillo en cuanto a su manejo y programación, además de barato, es el motivo de este trabajo.

El sistema en conjunto se basa en el estándar industrial llamado STD-BUS.

Se cuenta con el apoyo de un sistema creado con anterioridad en el Instituto de Ingeniería de la UNAM llamado CVI (Controlador Universal Industrial) que se basa en la misma porma.

El CUI es un sistema que contiene la arquitectura básica de una computadora basada en el microprocesador 8088, contiene memorias RAM, ROM y puertos paralelo y serie.

En el CUI se encuentra instalado en memoria ROM el lenguaje de programación con el cual se trabajará. Este lenguaje llamado Multibasic es adecuado para las tareas de control, ya que es bastante rápido y tiene la posibilidad de

manejar varias rutinas de control dando la impresión de lievarias a cabo a un mismo tiempo.

El sistema tiene además la ventaja de poder ser conectado a una terminal de computadora lo cual facilita la programación y los cambios que deseen hacerse, además de la visualización directa de las condiciones de operación, elaboración de reportes, realización de gráficos y el respaldo de la información en medios de almacenamiento permanentes (cintas magnéticas, discos flexibles o duros).

Mediante la conexión de distintas tarjetas al bus, es posible entonces trabajar en forma modular para desarrollar distintas tareas.

Para cumplir con los objetivos de este trabajo se desarrollaron las tarjetas necesarias para realizar el control de alguna variable física. Se diseñó una tarjeta de adquisición de datos basada en un convertidor A/D, una tarjeta de control basada en un convertidor D/A y una tarjeta que se encarga de programar el periodo de las interrupciones. Estas tres tarjetas interactúan con el CUI de manera modular para realizar rutinas de control, monitoreo y supervisión.

Cada una de las tarjetas desarrolladas en el presente trabajo fueron diseñadas con base en la tecnología HCMOS de alta velocidad, lo cual presenta las ventajas de tener un consumo de energía muy bajo y de procesar la información con la velocidad suficiente para llevar a cabo un adecuado control del proceso.

Para poder probar el sistema en una situación real de operación, se tomó como ejemplo de aplicación el control de un horno eléctrico de 0 a 1000. C de temperatura usado en laboratorio para la calcinación de muestras orgánicas. Para poder cerrar el lazo de control, se desarrolló una etapa electrónica de acondicionamiento y compensación de unión fria para la señal de un termopar, y la etapa electrónica que sirve como actuador.

# III. DISENO DEL MODULO A/D.

#### III.1. DESCRIPCION DEL MODULO A/D.

El objetivo de este módulo es el de servir de interfaz entre el proceso a monitorear (variable sensada) y el microprocesador.

El módulo se diseñó con base en el estándar STD-BUS (Ver apéndice A.1.), su función es la de convertir una señal analógica, proveniente de un circuito sensor de alguna variable física, en un código digital que será procesado por el sistema para realizar, con base en esa información, una rutina de procesamiento o registro.

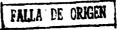

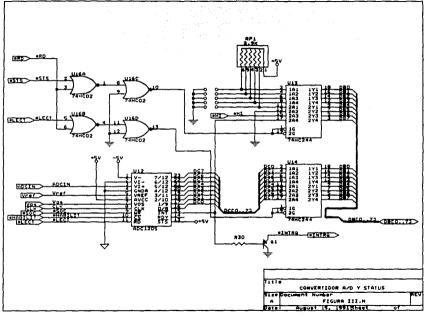

El diagrama de bloques de la figura III.A muestra la relación entre los distintos dispositivos digitales de la tarjeta.

La tarjeta está constituída por las siguientes secciones digitales:

a) Decodificación de dispositivos.

Esta etapa es la encargada de dar acceso a las señales que realizan la decodificación de los distintos dispositivos internos de la tarjeta.

b) Acceso al bus de datos.

Esta sección se encarga del control del flujo de los datos ya sean de lectura o de escritura.

c) Señales de atención al convertidor A/D.

En esta parte se tiene la circuitería que maneja las ordenes que se darán al convertidor (de habilitación, conversión o de lectura)

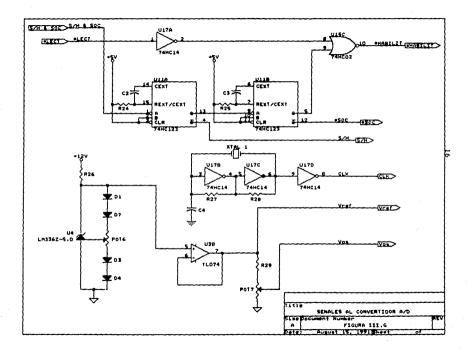

Esta etapa cuenta además con la circuitería necesaria para dar servicio al convertidor. Se diseñó un generador de señal de reloj de 1 MHz, dos monoestables para realizar el muestreo de la señal analógica de entrada e iniciar su conversión, y dos referencias de voltaje ajustables para realizar los ajustes de cero y de escala completa.

# d) Registro de status.

La tarjeta cuenta con un registro de status de 8 bites, de los cuales, los cinco menos significativos forman la palabra de identificación de tarjeta. Esta palabra se puede elegir a conveniencia del usuario, por medio de jumpers, para que cada uno de sus módulos cuente con una palabra distinta de identificación, la función de los restantes bites del registro de status se muestra a continuación:

# Registro de

D4

D5......Bit de existencia de tarjeta.

D6......Bit de habilitación de interrupción

D7.....Bit de interrupción.

# e) Programación de modo y ganancia.

Esta sección cuenta con circuitos que almacenan información binaria (flip-flop's) en los cuales es posible modificar su status para realizar un cambio en el modo de entrada de la señal analógica (simple o diferencial) o bien, realizar un cambio en el factor de amplificación de dicha señal.

# f) Programación del tipo de entrada.

Al igual que en la etapa anterior, esta sección cuenta con un flip-flop que realiza la selección del tipo de entrada con el que se trabajará (corriente o voltaje).

# g) Conversión analógica-digital.

En esta sección se cuenta con un convertidor análogo-digital de 12 bites (ADC1205) el cual es el encargado de realizar la transformación del valor de la señal analógica de entrada u un código digital reconocible por el microprocesador.

El módulo cuenta además con una etapa de electrónica analógica la cuál tiene por objeto el acondicionamiento de una señal análoga externa para su posterior conversión a código digital.

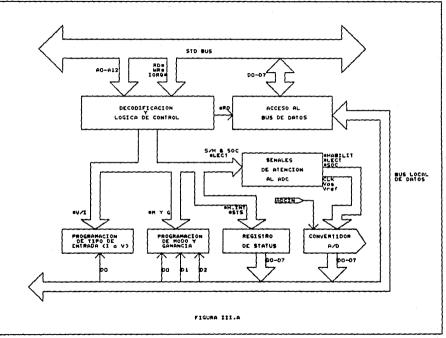

El diagrama de bloques de la figura III.B muestra la relación entre los distintos dispositivos analógicos.

La tarjeta se constituye por las siguientes secciones analógicas:

a) Convertidor de corriente a voltaje.

En esta etapa se diseñó un convertidor de corriente a voltaje el cual recibe como entrada una señal analógica en el rango de 4 a 20 mA el cual transforma en una salida de voltaje de 25V.

b) Selector de tipo y modo de entrada.

La tarjeta cuenta con la posibilidad de admitir entradas analógicas tanto de corriente como de voltaje, las cuales se escogen por programa. Si la señal analógica de entrada es de voltaje, entonces se puede elegir, también por programa, si será entrada simple o diferencial. En el caso de tener entrada de corriente, se deberá programar necesariamente en modo simple. Por entrada simple se entiende que la señal está referida a la masa del sistema, mientras que la entrada diferencial está "flotando".

c) Amplificador de instrumentación.

Se diseñó un amplificador de instrumentación con ganancia unitaria, el cual proporciona una alta impedancia de entrada y una alta razón de rechazo en modo común.

d) Amplificador de ganancia programable.

En esta etapa se encuentra un amplificador con 4 ganancias seleccionables por programa (0.5,1,10 y 100).

e) Retenedor de orden cero.

Para mantener el valor invariante de la señal durante el tiempo de conversión, se tiene un retenedor de orden cero. La señal que se tiene a la salida de dicho retenedor entra directamente al convertidor A/D.

## 111.2. CONVERTIDOR ADC1205.

El convertidor usado en la tarjeta de adquisición de datos es el circuito ADC1205, el cual, es un dispositivo de tecnología CMOS que realiza la conversión de señales analógicas de voltaje por el metodo de aproximaciones sucesivas, con una resolución de 12 bites, más un bit de signo. El bus de datos de salida del convertidor es compatible con los microprocesadores que manejan buses de datos de 8 bites ( Z-80, 68000, 8088, 8086, etc.)

Estos 13 bites de datos se entregan por medio de dos palabras de 8 bites. La primera palabra contiene en los 4 bites más significativos la información sobre el signo, mientras que los bites restantes representan los cuatro bits más significativos del valor del dato convertido. La segunda palabra de 8 bites completa el código convertido.

Los números negativos se representan en "complemento a dos". Todas las señales digitales son compatibles con tecnología TTL y MOS.

Si la entrada analógica varía ente 0 y +5V entonces el circuito se puede polarizar sólo con una fuente de +5V. Sin embargo, si la entrada varía entre  $\pm$ 5V, será necesaria una fuente adicional de -5V. Este dispositivo tiene un tiempo de conversión de 100  $\mu$ s, lo cual lo hace lento para algunas aplicaciones. Se eligió este integrado básicamente por su bajo costo y fácil adquisición en el mercado.

El circuito debe ser sincronizado con una señal de reloj de 1 MHz. Además cuenta con dos entradas analógicas para realizar los ajustes a cero y a escala completa (Vos y Vref).

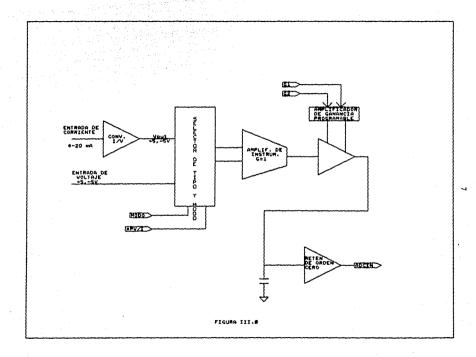

#### III.3. ETAPA ANALOGICA DE ENTRADA.

Esta etapa se diseñó para lograr un acondicionamiento de la señal analógica proveniente de algún dispositivo sensor, de tal forma que permita la entrada de señales tanto de voltaje como de corriente; los rangos de entrada de dichas señales varian de ± 5 V y de 4 a 20 mA para escala completa, respetivamente.

La tarjeta cuenta con un convertidor de corriente a voltaje (CIV), el cual transforma la señal de corriente de 4 a 20 mA en una salida de ± 5 V (en modo simple). El CIV está compuesto por un par de amplificadores operacionales (U3C y U3D, Figura III.C), el primero con una configuración inversora con ajuste de offset y el segundo una configuración sumador no inversora.

Tanto la señal de entrada de voltaje como la salida del CIV pasan por un selector analógico (UI) que realiza la selección del tipo de entrada así como el modo (simple o diferencial), el cual es un circuito híbrido que contiene tres multiplexores de 2x1, los cuales se seleccionan por medio de 3 lineas digitales.

Una vez seleccionado el tipo y el modo de entrada de la señal analógica, ésta pasa a un amplificador instrumentación con ganancia unitaria formado por los amplificadores U2A, U2B y U2C. Después la señal pasa a un amplificador de ganancia programable formado por amplificador operacional en configuración inversora con ajuste de offset (U2D) y un circuito multiplexor híbrido de 8x1 con tres lineas de selección digitales. La señal que proviene de éste amplificador pasa por uno de multiplexores de Ul para que en su momento sea seleccionada por la linea S/H y sea realizado un muestreo de la señal. El valor de la señal en éste instante es almacenado por un retén de orden cero para que se conserve invariante durante el proceso de conversión que se describirá más adelante.

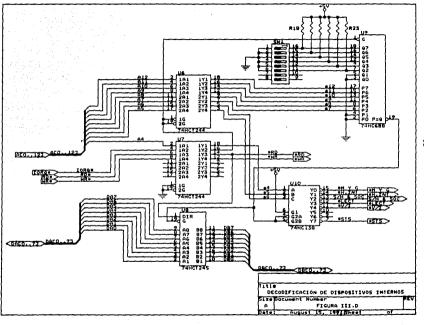

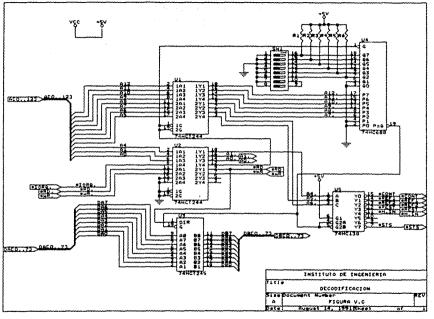

# III.4. DECODIFICACIONDE DISPOSITIVOS.

En esta sección se realiza la selección de los dispositivos digitales que se encuentran en la tarieta.

La decodificación se lleva a cabo de la siguiente manera : Cuando se intenta decodificar un puerto cualquiera es

porque se quiere leer, o blen se quiere escribir un dato en algún dispositivo. Entonces, si se quiere leer un dato se debe enviar una señal que habilite los puertos (\*10RQ) y una dirección válida para el puerto de donde se quiere obtener dicho dato. De manera semejante, cuando se desea escribir un dato, se debe de enviar la señal de habilitación de puertos, una dirección válida y el dato que se desea escribir (8 bites).

Debido a que está reservado en el CUI un bloque de direcciones para puertos externos de 0000K a 3FFFH entonces, tenemos de la linea A7 a A12 para realizar la decodificación de cada tarjeta.

La tarjeta, al recibir la señal de habilitación de puertos (\*IORQ), permite que las lineas de direcciones entren directamente, entonces se toman las lineas A12 a A7 (dirección base) y se alimenta con ellas al circuito comparador binario (U9, Figura III.D) el cual realiza una comparación entre dichas lineas y una dirección base de 6 bites filiada por los microinterruptores SVI.

La señal \*P=Q se encarga de habilitar al decodificador de 3x8 (U10). La selección de los dispositivos que habrán de habilitarse o programarse se hace por medio de los lineas A6, A5 y A4 del bus de direcciones (dirección relativa).

Las señales de salida del decodificador son todas activas bajas y son usadas para habilitar los circuitos que programan las características de operación de la tarjeta, como el modo de entrada ( simple o diferencial), las ganancias, programar el dispositivo que se encarga de habilitar las interrupciones, para hacer el muestreo de la señal analógica de entrada e iniciar su conversión, para habilitar los latches de salida del convertidor y leer el dato convertido, para programar el tipo de entrada (voltaje o corriente), y para leer la palabra de status.

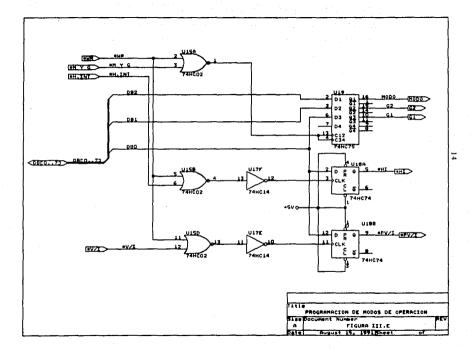

Para programar las características de operación de la tarjeta como el modo, el tipo y la ganancia de la señal analógica de entrada, se hace uso de circuitos que almacenan información binaria (flip-flop's). Estos circuitos son

habilitados por las lineas \*M Y G y \*V/I que provienen del decodificador (ver figura III.E).

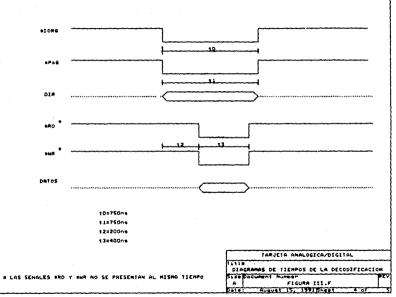

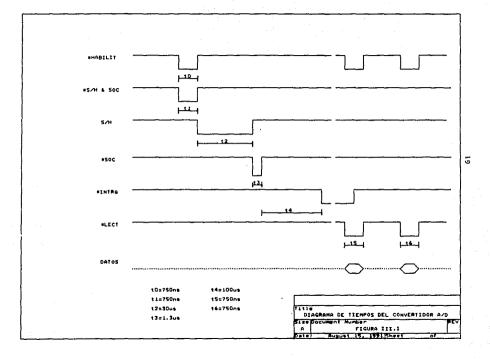

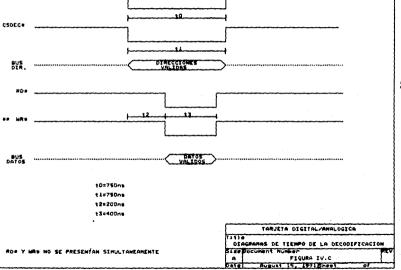

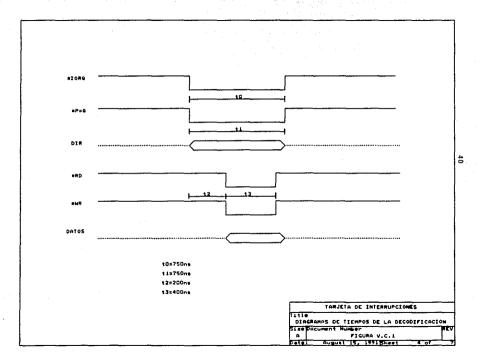

El diagrama de tiempos de la Figura III.F muestra la secuencia de las señales involucradas en el proceso de decodificación.

# III.5. PROCESO DE CONVERSION.

La conversión de la señal de entrada se inicia direccionando la tarjeta y logrando que la linea S/H & SOC del decodificador de 3x8 (UIO), haga la transición de alto a bajo (ver Figura III.B). Esta acción provoca que se dispare el primer monoestable (UIIA), el cual mediante su salida negada (S/H) realiza un muestreo de la señal que sale del amplificador programable durante el periodo que dura la constante de tiempo fijada por C2 y R24 (ver Figura III.G). Una vez transcurrido este tiempo y con el flanco de bajada de la salida complementaria del primer monoestable, se realiza el disparo del segundo monoestable (UIIB), el cual se encarga de habilitar al convertidor por medio de la señal "HABILIT e iniciar la conversión por medio de la señal "SOC. La constante de tiempo del segundo monoestable es fijada por C3 y R25.

El proceso de conversión dura 100µs. Al término de este tiempo el convertidor envia una señal de interrupción (\*INT) para indicar que tiene en sus registros de salida los dos octetos que contienen el código digital equivalente a la señal analógica de entrada (ver Figura III.H). La señal de interrupción transfère la ejecución actual del programa a una subrutina donde se atiende a dicha interrupción. Esta subrutina se encarga de realizar la lectura del dato convertido y de almacenario en alguna variable.

Basicamente la subrutina debe realizar lo siguiente:

El procesador direcciona de nuevo la tarjeta para bajar la señal \*LECT del decodificador (UiO, Figura III.D) que es la encargada de habilitar de nuevo al convertidor por medio de

\*HABILIT y de hacer la lectura del registro de salida del convertidor, habilitando además al buffer (U14) que pondrá la palabra extraída en el bus de datos. Debido a que el bus de datos es de sólo 8 bites, la lectura del dato convertido se debe de hacer en dos procesos como los anteriormente descritos. El primer octeto leído es el que contiene, en sus cuatro bites más significativos, la información sobre el signo y en los cuatro restantes contiene los bites más significativos del código convertido. La segunda palabra completa el código.

En el diagrama de tiempos de la Figura III.I se muestra la secuencia de generación de las señales que intervienen en el proceso de conversión.

# IV. DISENO DEL MODULO D/A.

# IV.1. DESCRIPCION DEL MODULO.

El objetivo de éste módulo es, escencialmente, servir de forma analógica como medio de comunicación entre el microprocesador y un proceso externo (medio ambiente).

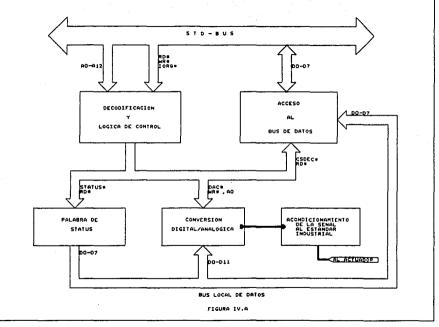

El funcionamiento de esta tarjeta puede simplificarse en el diagrama de bloques de la Figura IV.A. A continuación se hace la descripción de su funcionamiento.

Esta tarjeta está constituída por cinco secciones, que son:

- a) Decodificación de dispositivos. Esta sección es la encargada de determinar qué función realizará la tarjeta, es decir, es quien rige y decide cuáles de los dispositivos internos deben habilitarse para realizar funciones específicas.

- b) Palabra de status. Este módulo, para su identificación, posee una palabra de status que al ser leída por el microprocesador, éste puede conocer qué tipo de tarjeta se ha direccionado y saber qué características tiene la tarjeta direccionada. Dicha palabra de status es una palabra de ocho bites, con los cuales la tarjeta se identifica e informa de su forma de operación; es decir, si puede o no realizar interrupciones y en caso de que sí pueda interrumpir, poder informar que requiere de atención. La distribución de los bites correspondientes a la palabra de status se hace de la siguiente manera, utilizando el bus de datos:

D7 : INT. Indicación de que se ha realizado una interrupción.

D6 : HI. Bit de habilitación de interrupción.

D5 : 3. Bit que denota la existencia de tarjeta.

Bites de identificación de la tarjeta.

c) Acceso al bus de datos. En esta sección se realiza el

D4-D0 :

intercambio de señales para que microprocesador y proceso externo lleven a cabo la transferencia de información.

- d) Conversión Digital/Analògica. En esta sección se realiza la conversión de un dato digital a un voltaje analógico. La conversión se realiza sediante un converitor D/A de 12 bites. En este sódulo el dato a convertir es un dato digital que consta de dos palabras, de ocho y cuatro bites respectivamente.

- e) Acondicionamiento de la señal analógica. La señal analógica obtenida a la salida del convertidor puede ser proporcionada en forma de voltaje (±5 V) o corriente (4 a 20 mA). Esto se realiza para cuapiir con normas utilizadas comúnmente en la industria.

# IV. 2. CONVERTIDOR DAC1230.

Esta etapa cuenta con un convertidor Digital/Analógico y un conjunto de amplificadores operacionales para obtener las distintas salidas, va sean de corriente o de voltaje.

Para esto, se eligió el convertidor Digital/Analógico DAC1230, que tiene una resolución de 12 bites y maneja datos de entrada de 8 bites; este convertidor también posee 4 líneas analógicas de salida para la obtención del voltaje. El DAC1230 cuenta con otras 5 entradas digitales, las cuales son señales de control.

Este convertidor es compatible con tecnologías TTL, CMOS y puede ser interfaz directa con una amplia variedad de microprocesadores (8088, 8048, 8085, Z-80, etc). Sus registros de entrada y su control asociado permiten a este convertidor operar como un "stack" de dos octetos en la memoria del sistema o en el espacio reservado para dispositivos I/O sin que se requiera de una iógica adicional para la interfaz.

El DAC1230 puede usarse directamente con un bus de datos

de 8 bites tal como lo indica su constitución interna a partir de sus 8 líneas de entrada. Este DAC1230 acepta datos justificados a la izquierda provenientes del procesador.

La sección analógica comprende a una red de escalera R-2R de precisión y a 12 interruptores CMOS de corriente. Una estructura de escalera R-2R invertida se usa con las corrientes ponderadas alternadas entre las salidas Iouri e Ioura, manteniendo una corriente constante en cada brazo de la escalera independientemente del estado del interruptor. Una circuitería especial permite la compatibilidad con niveles de voltaje de entrada para lógica TTL.

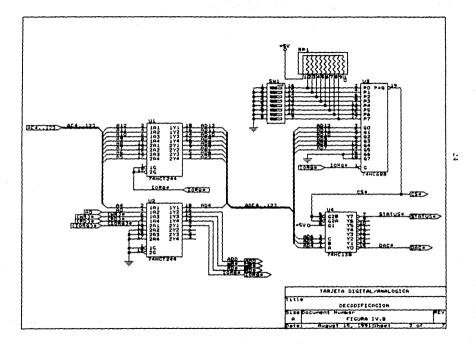

# IV.3. DECODIFICACION DE DISPOSITIVOS.

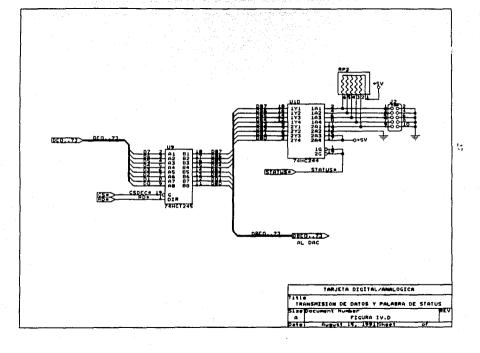

En esta etapa se realiza la selección de cada uno de los dispositivos que forman parte de la tarjeta (Figura IV.B). La selección de dichos dispositivos se ileva a cabo mediante el envío de una dirección válida por el bus de direcciones a través de buffers con salida tres estados (U1 y U2), éste integrado fué utilizado porque tiene entradas compatibles con tecnología TTL y salidas compatibles con CMOS.

Las direcciones que son utilizadas para direccionar periféricos mediante el CUI (Ver Apéndice A.2) son las comprendidas de la A7 a la A12 y de la A0 a la A6 para direccionar dispositivos internos en los periféricos. Lo anterior se determinó de acuerdo con las especificaciones de diseño dei CUI donde se aclara que e) bloque de direcciones desde la 0000H a la 3FFFH está reservado para expansión de periféricos de I/O.

En la tarjeta D/A la decodificación se realiza de acuerdo con la siguiente secuencia (Figura IV.C): al enviar una dirección válida, ésta es comparada con una palabra de 8 bites (dirección base) en un circuito comparador en magnitud de 8 bites (U3, Figura IV.B), el cual entrega una señal activa baja cuando la palabra enviada por el bus de

PIORG

direcciones es igual a la palabra fija en el comparador mediante un DIP-Switch. El resultado de la comparación, a su vez, habilita a un decodificador de 3x8 (U4), el cual utiliza las direcciones A6, A5 Y A4 para seleccionar los dispositivos internos de la tarjeta. Con la salida del decodificador se realizan dos actividades : que se dé la orden de conversión, habilitando al convertidor D/A con la señal DAC°; o que se lea la palabra de status de la tarjeta mediante la señal STATUS°.

Cuando es elegida la opción para leer la palabra de status de la tarjeta (Figura IV.D), se habilita un buffer con salidas tres estados (UIO), el cual permite la salida de una palabra alambrada en jumpers o fijada con un DIP-Switch. Dicha palabra se envía al bus de datos a través de un circulto bidireccional con salida tres estados transceiver (U9) que es habilitado por la señal CSDECº que es resultado el a comparación. El transceiver determina el sentido en que se envían los datos de acuerdo con la señal de RDº del STD-BUS, la cual, cuando se presenta, permite la lectura de la palabra de status.

Cuando el procesador selecciona al convertidor D/A, con la señal DAC\*, habilita al circuito y puede realizar la conversión de los datos de acuerdo con la secuencia de señales que se describe en la sección de Conversión Digital/Analógica. Los datos son enviados al convertidor a través del transceiver, el cual determina el sentido de los datos con la señal RD\*, la cual, al estar en un estado alto permite la escritura de los datos en los registros internos del convertidor.

# IV. 4. PROCESO DE CONVERSION.

La conversión de los datos digitales se lleva a cabo de acuerdo con la siguiente secuencia :

De acuerdo con los diagramas de tiempos proporcionados por

direcciones es igual a la palabra fija en el comparador mediante un DIP-Svitch. El resultado de la comparación, a su vez, habilita a un decodificador de Jx8 (U4), el cual utiliza las direcciones A6, A5 Y A4 para seleccionar los dispositivos internos de la tarjeta. Con la salida del decodificador se realizan dos actividades : que se dé la orden de conversión, habilitando al convertidor D/A con la señal DAC°; o que se lea la palabra de status de la tarjeta mediante la señal STATUS°.

Cuando es elegida la opción para leer la palabra de status de la tarjeta (Figura IV.D), se habilita un buffer con salidas tres estados (UIO), el cual permite la salida de una palabra alambrada en jumpers o fijada con un DIP-Switch. Dicha palabra se envía al bus de datos a través de un circuito bidireccional con salida tres estados transceiver (U9) que es habilitado por la señal CSDECº que es resultado de la comparación. El transceiver determina el sentido en que se envían los datos de acuerdo con la señal de RDº del STD-BUS, la cual, cuando se presenta, permite la lectura de la palabra de status.

Cuando el procesador selecciona al convertidor D/A, con la señal DAC\*, habilita al circuito y puede realizar la conversión de los datos de acuerdo con la secuencia de señales que se describe en la sección de Conversión Digital/Analógica. Los datos son enviados al convertidor a través del transceiver, el cual determina el sentido de los datos con la señal RD\*, la cual, al estar en un estado alto permite la escritura de los datos en los registros internos del convertidor.

#### IV.4. PROCESO DE CONVERSION.

La conversión de los datos digitales se lleva a cabo de acuerdo con la siguiente secuencia :

De acuerdo con los diagramas de tiempos proporcionados por

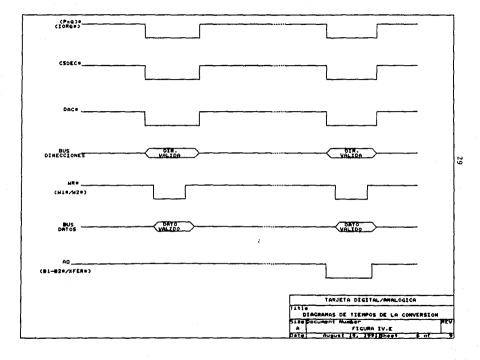

el fabricante, para esta configuración las señales deben generarse de la siguiente manera (Figura IV.E) : Cada vez que la tarjeta D/A es direccionada, se presenta la señal DAC\* que activa al convertidor; con la orden de escritura a puerto obtenemos también la señal de WRº, la cual activa W1º/W2º, con lo que se realiza la escritura al registro del DACº: al direccionar el bit menos significativo del bus de direcciones en alto (AO=1) la señal B1-B2\*/XFER\* también estará en alto con lo que se escribe el octeto más significativo en el registro de 8 bites del DACº, cuando se direcciona nuevamente la escritura a puerto se presenta la señal DAC° y con WR° volvemos a activar la señal W1°/W2°. pero ahora se direcciona AO en bajo con lo que la señal B1-B2\*/XFER\* permite la escritura del octeto significativo en el latch de 4 bites del DACº, y realiza la transmisión de la palabra completa de 12 bites al registro interno de convertidor liniciando con ello la conversión.

Para enviar los datos al convertidor, estos tienen que ser acondicionados para que le lleguen en el orden adecuado, es decir, tienen que estar justificados hacia la izquierda, que es como se explica en las hojas de especificaciones del fabricante. Esta justificación hacia la izquierda indica que los 16 bites que llegan ai convertidor, deben ser recorridos cuatro sitios a la izquierda de como fueron enviados por el microprocesador, así los dos datos se envían de la manera siguiente:

D11 D10 D9 D8 D7 D6 D5 D4

OCTETO 2 D3 D2 D1 D0 • • • •

# Salida de Voltaje.

OCTETO 1

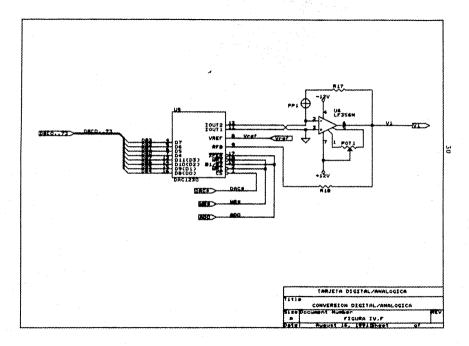

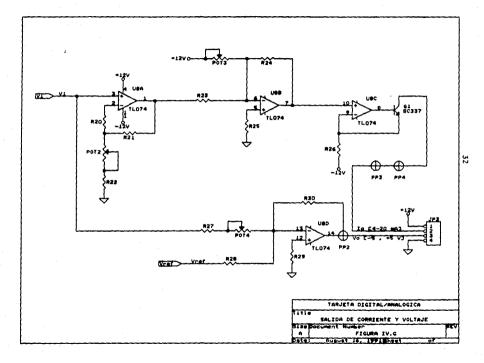

En esta etapa se realizó la adaptación de la corriente (entregada por el convertidor) a una escala de voltaje adecuada para ser utilizada por el actuador (Figura IV.F).

Esta escala de voltaje se basa en una norma estándar industrial que es de ± 5 volts.

Para implementar esta salida de voltaje (Figura IV.G), primero se tuvo que convertir la salida de corriente a una salida de voltaje mediante la utilización de un amplificador operacional (U6, Figura IV.F) en configuración convertidora de corriente a voltaje. Este amplificador entrega una salida de voltaje, para escala completa, de O a -5 V, con una resolución de 1.22 mV por bit del dato de entrada al convertidor. Posteriormente se utiliza un amplificador operacional en configuración sumador-inversor (U8D), en el cual se suman la señal de (O a -5 V) y un voltaje de referencia de +5 volts para obtener así la señal de -5 a + 5 volts.

Con esta configuración, el voltaje de salida (PP2) está dado por la siguiente expresión :

$$V_0 = V_{ref} \left[ \begin{array}{c} D - 2048 \\ \hline 2048 \end{array} \right]$$

Donde D es el dato digital de 12 bites en valor decimal. 0 < D < 4095

Por ejemplo :

$$D = 0$$

,  $V_0 = -5 \text{ V}$

$D = 2047$  ,  $V_0 = 0.48 \text{ mV}$

$D = 4095$  ,  $V_0 = 4.997 \text{ V}$

# Salida de Corriente.

Para obtener esta salida, a partir de la señal entregada por el amplificador U6 (Figura IV.G), se utiliza un arreglo de amplificadores operacionales para poder acondicionar el voltaje de tal manera que un transistor NPN (Q1) trabaje en la región de conducción (activa directa), y proporcione una corriente equivalente a las variaciones de voltaje en su

base. Dicho acondicionamiento se lleva a cabo por medio de un amplificador operacional en configuración no inversora con ganancia variable (USA) y otro amplificador configuración de sumador-inversor (USB). A continuación de este último amplificador se realiza una conversión de voltaje a corriente, este circuito consiste amplificador operacional en configuración de no inversor (USC) el cual utiliza como lazo de realimentación negativa a un transistor NPN cuya base se conecta a la salida del último operacional y su emisor a la entrada negada del mismo. Este transistor interpreta las variaciones de voltaje en su base como variaciones de corriente a través del lazo de realimentación y con esta variación de corriente en la base se puede obtener una variación de corriente en el colector, equivalente al voltaje de entrada. Dicha corriente de colector se obtuvo con un rango de 4 a 20 mA para una impedancia de carga de 250 Q. Esta resistencia de carga debe ser conectada entre los bornes 1 y 2 del conector JP3.

### V. DISEÑO DEL MODULO DE INTERRUPCIONES.

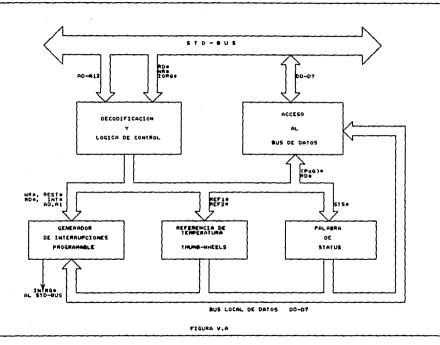

#### V.1. DESCRIPCION DEL MODULO.

Este módulo está diseñado con la finalidad de establecer el tiempo en el cual se debe de realizar una actividad específica, es decir, crear una señal que a través del SID-BUS (mediante interrupciones) indique al microprocesador que debe atender cierta subrutina que enlazarse con un proceso externo con el proceso que se esté efectuando.

En esta tarjeta se realizan las siguientes actividades :

- a) Fijar el periodo de muestreo del sistema.

- b) Tomar la referencia de la temperatura

- c) Leer el STATUS de la tarjeta

La primera actividad se lleva a cabo en un circuito generador de interrupciones programable (Figura V.A), cuyo funcionamiento se describirá posteriormente, así como la manera en que se programa.

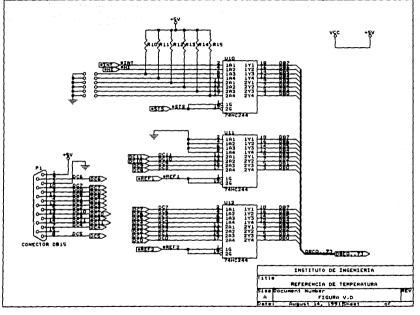

La segunda actividad se puede realizar con la utilización de un selector rotatorio BCD, cuya función es entregar en código BCD la referencia de temperatura; esta referencia se puede fijar por medio de tres selectores que indican un valor de tres dígitos al CUI. Una vez que se tiene el número en binario, éste es enviado a través de un buffer al STD-BUSpara su manejo por programa.

La tercera actividad se lieva a cabo por medio de un buffer, el cual en su entrada tiene un status programado utilizando jumpers. El status indica si la tarjeta puede interrumpir al procesador del CUI, si hay una interrupción, indica también la existencia de tarjeta, y contiene el identificador de la tarjeta.

A continuación se presenta el formato de la palabra de

un octeto de datos constituido de la siguiente forma :

|     |     |     |     |    |    |    | DO  |

|-----|-----|-----|-----|----|----|----|-----|

| SC1 | SCO | RL1 | RLO | M2 | MI | MO | BCD |

A continuación se describirá la función de cada bit de la palabra de control.

Los bites D7 y D6 (SC1, SC0) permiten la selección del contador como se muestra en la siguiente tabla.

| SC1 | SC0 | ACCION               |

|-----|-----|----------------------|

| 0   | 0   | Selección contador O |

| 0   | 1   | Selección contador 1 |

| 1   | 0   | Selección contador 2 |

| 1   | 1   | Ilegal               |

Los bites D5 y D4 (RL1,RL0) son utilizados para la operación de escritura y lectura en el registro del contador.

A continuación se detallan las funciones.

| RL1 | RLO | ACCION                                                                                          |

|-----|-----|-------------------------------------------------------------------------------------------------|

|     |     |                                                                                                 |

| 0   | 0   | Lectura al vuelo                                                                                |

| 0   | 1   | Escribir/leer el octeto<br>más significativo                                                    |

| 1   | 0   | Escribir/leer el octeto<br>menos significativo                                                  |

| 1   | 1   | Escribir / leer primero<br>el octeto menos signifi-<br>cativo y después el más<br>significativo |

Los bites D4, D3 y D2 (M2,M1,M0) se utilizan para seleccionar los modos de operación de los contadores como se muestra a continuación.

#### status :

## DO D1 D2 D3 D4 D5 D6 D7

DO-D4 : Identificación de la tarjeta

D5 : 3. Existencia de tarjeta

D6 : HI. Habilitación de interrupción

D7: 1NT. Interrupción

### V.2. TEMPORIZADOR PROGRAMABLE 8253.

El dispositivo temporizador utilizado en el módulo de interrupciones es el 8253 el cual es un contador programable de tecnología nMOS. Está constituido por tres contadores independientes de 16 bites y un registro de control (para programar el modo de operación).

Este circuito resuelve uno de los problemas comunes en cualquier sistema de microcomputadora que es la generación de retrasos exactos de tiempo bajo un control de software, al implementar ciclos de espera por programa. El programador configura al 8253 para que cumpia con sus requerimientos de diseño. La programación de este circuito es similar a la de un puerto de entrada-salida.

La definición funcional completa del 8253 es programada por software. Un conjunto de palabras de control deben ser enviadas por el CPU para inicializar cada contador con el modo de operación deseado y la información de la cuenta.

Una vez programado el 8253 esta listo para realizar cualquier labor de temporización.

La operación actual de conteo de cada contador es completamente independiente.

La programación del 8253 se realiza en dos operaciones básicamente: establecer el modo de operación y cargar un número base en cada contador. Esto se hace por medio de una palabra de control enviada al circuito la cual consiste en

| M2 | Mi | мо | HODO | ACCION                             |

|----|----|----|------|------------------------------------|

| 0  | ō  | 0  | a    | Interrumpir al fin de la<br>cuenta |

| 0  | 0  | 1  | 1    | Monoestable programable            |

| 0  | 1  | 0  | 2    | Contador divisor entre n           |

| 0  | 1  | 1  | 3    | Generador de onda cuadrada         |

| 1  | O  | 0  | 4    | Strobe disparada por<br>programa   |

| 1  | 0  | ī  | 5    | Strobe disparada por<br>hardware   |

Por último, el bite DO específica si el número de contador esta en código binario (BCD=0) o código BCD(BCD=1).

## V.3. DECODIFICACION DE DISPOSITIVOS.

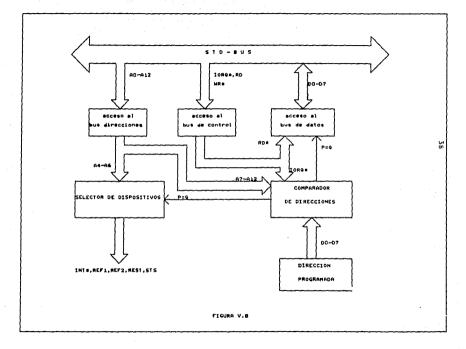

La decodificación en la interfaz se efectúa cuando un grupo de direcciones enviadas por programa correspondan a las direcciones de uno de los dispositivos de la tarjeta.

El proceso de decodificación de dispositivos de éste módulo se lleva a cabo siguiendo la secuencia mostrada en el diagrama de bloques de la Figura V.B.

La decodificación se realiza comparando las direcciones del STD BUS con la programada en la tarjeta; esto lo realiza el circulto comparador de magnitud de ocho bites (U4, Figura V.C). Este dispositivo compara las direcciones A7-A12 con las de un microinterruptor programable (SW1). El resultado de esta comparación es una señal que permite enviar o recibir información a la interfaz y a su vez habilitar a un decodificador el cual por medio de las direcciones A4-A6 son generadas las siguientes señales de selección: \*INT, REF1, REF2, REST y STS (Figura V.C). La forma en que se presentan las señales mencionadas, puede observarse en el diagrama de tiempos de la Figura V.C.1.

Cuando se presenta la señal \*CONT (Figura V.C) se habilita el generador de interrupciones programable lo que indica que se ha presentado a éste dispositivo una señal de escritura por medio la línea del WR o una lectura por medio del RD.

Las señales "REF1 y "REF2 permiten seleccionar a dos buffers de ocho bites (U11 y U12, Figura V.D) los cuales, junto con un selector rotatorio BCD permiten obtener la referencia de temperatura (en código BCD). Estas señales nos indica que se ha presentado una señal de lectura.

La señal "REST sirve para restaurar al flip-flop que interrumpe al procesador, permitiendo de esta manera una nueva interrupción al procesador.

Cuando la señal \*STS se presenta, se habilita el buffer (U10) que contiene la palabra de status y así poder ser enviada al STD-BUS a través del bus de datos.

Resumiendo, en esta sección se realiza la selección de los dispositivos que componen al módulo. Se divide en las siguientes partes :

- Selección del generador de interrupciones programable.

- Selección de los dispositivos para la lectura de la referencia.

- Selección del registro de la palabra de status.

- Restauración de la señal de interrupción.

#### V. 4. PROCEDIDINIENTO DE INTERRUPCION.

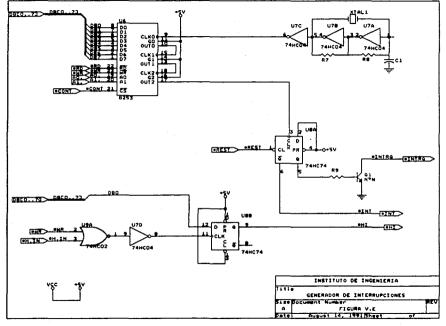

En esta parte se fija el periodo de muestreo de el sistema, esto se logra mediante el generador de interrupciones programable (U6, Figura V.E). Este generador es un circuito CMOS de alta integración y consta de tres contadores binarios de 16 bites cada uno, con modos de funcionamiento programables.

Para hacer que funcione el generador de interrupciones se tiene una base de tiempo de 1 Mhz, que es generada por un circuito oscilador a cristal (U7), implementado con

inversores, capacitores, resistencias y un cristal de 1 Mhz.

Este proceso se inicia direccionando la tarjeta para generar la señal \*CONT, que se encarga de seleccionar el generador de interrupciones programable; al mismo tiempo se presenta la señal de escritura o lectura, lo cual permite enviar o recibir datos al generador de interrupciones programable. En este circuito los contadores 0 y 1 están programados en modo 3 y el contador 2 está programado en modo 2; estos contadores se encuentran conectados en cascada. Así sus periodos de muestreo van desde 1 µs hasta 78 horas (Figura V.F).

El contador 2 se programó de tal forma que al finalizar la cuenta se genere un pulso bajo (CUT2), cuya duración es un pulso de reloj. Esta señal es utilizada como reloj por un filp-flop tipo D (USA Figura V.E), que se dipara con flanco de subida, su salida maneja un transistor NPN (Q1, Figura V.E), el cual envía la señal de interrupción al procesador del CUI (INTRO).

Cuando se atlende la solicitud de interrupción se va a una rutina de atención de interrupción la cual debe enviar una dirección para generar una señal llamada \*REST cuya función es la de restaurar al flip-flop para que se esté en condiciones de enviar la siguiente señal de interrupción (período de muestreo programado).

#### VI. PROGRAMACION DE LOS MODULOS.

### VI.1. PROGRAMACION DEL MODULO ANALOGICO/DIGITAL.

En esta sección se describe la manera en la cual debe ser programada la tarjeta, según las características de la señal de entrada.

La finalidad de la programación en este caso es la de evitar lo más posible el uso de interruptores y jumpers en el área de la tarjeta, para hacer más versátil el uso de la misma.

Por medio de la programación inicial podemos elegir si la entrada será de corriente o de voltaje, si será entrada simple o diferencial, el valor de la ganancia y habilitar las interrupciones para el sistema.

El sistema tione reservadas las direcciones A12 a A7 para accesar a los dispositivos de entrada/salida. Estas direcciones son comparadas con una dirección base de 6 bites cada vez que se direccionan los dispositivos de entrada/salida. Dicha dirección base es seleccionable por medio de micro-interruptores (SWI Figura III.B). Las direcciones más bajas ( de A6 a A0) se pueden usar para direccionar los diferentes dispositivos que se encuentran en la tarjeta. En el caso de esta tarjeta sólo se usaron las direcciones A6 a A4 (dirección relativa).

En la siguiente tabla se puede ver la finalidad de cada direccionamiento:

| *RD | WR | A6 | ÁS | A4 | FUNCION                          |

|-----|----|----|----|----|----------------------------------|

| 1   | 0  | 0  | 0  | 0  | Registro de modo y ganancia      |

| 1   | 0  | 0  | 0  | 1  | Habilitación de interrupciones   |

| •   | •  | Ð  | 1  | 0  | Orden de muestreo y conversión   |

| 0   | 1  | 0  | 1  | 1  | Registro de dato convertido      |

| 1   | 0  | 1  | ٥  | 0  | Selecc. de tipo de entrada (V/I) |

|     |    | 1  | 0  | 1  | Sin uso.                         |

|     |    | 1  | 1  | 0  | Sin uso.                         |

| 0   | 1  | 1  | 1  | 1  | Registro de la palabra de status |

En el caso de la programación del modo y ganancia, habilitación de interrupciones y la selección entre entrada de corriente o de voltaje, es necesario, además, enviar por el bus de datos las palabras adecuadas para su programación.

# Selección de Tipo de Entrada (Corriente o Voltaje).

Esta selección se hace mediante una instrucción de escritura a puerto, direccionando la linea \*V/I del decodificador 3x8 (UIO Figura III.B).

La información para programar el tipo de entrada está manejada por el bit menos significativo del bus de datos (DO). Si se va a trabajar con entrada de voltaje es necesario cargar un cero en dicho bite. En caso de ser entrada de corriente, se carga con un uno lógico. Esta información es almacenada por un flip-flop tipo D (U18B), cuya salida (\*PV/I) mantiene la selección del tipo de entrada hasta que es nuevamente programado.

# Programación del Nodo y la Ganancia.

El modo de entrada de la señal analógica puede ser de dos formas: simple o diferencial. En el caso de estar trabajando con señales de entrada de corriente, el modo deberá ser fijado como simple, mientras que si la entrada es de voltaje podemos elegir entre alguno de los dos. Con respecto a la ganancia, podemos elegir entre cuatro distintas: 0.5, 1, 10 y 100.

En el caso de la programación de modo y ganancia, la información se envía en los tres bites menos significativos del bus de datos, de la siguiente manera:

D7 D6 D5 D4 D3 D2 D1 D0

• • • • • M G2 G1

Donde si:

М

O.... Modo simple

1.... Modo diferencial

G2 G1 Ganancia

0 0 .... 0.5

0 1 .... 1.0

1 0 .... 10.0

1 1 .... 100.0

Esta información es almacenada en un conjunto de flip-flops tipo D (U19 Figura III.C). Las salidas de dichos flip-flops mantendrán la selección del modo y la ganancia hasta una nueva programación.

Para realizar ésta programaciónse debe direccionar la linea <sup>9</sup>M Y G del decodificador UIO mediante una orden de escritura a la tarjeta.

# Mabilitación de Interrupciones.

Para la habilitación o deshabilitación de las interrupciones por parte de la tarjeta hacia el sistema se procede de manera similar a la selección del tipo de entrada. Se seleccina la linea °H. INT del decodificador UIO mediante una instrucción de escrituraa la tarjeta.

Si deseamos que la tarjeta sea atendida al dar una interrupción al sistema, debemos enviar por el bus de datos, en el bit menos significativo, un cero lógico. En caso contrario, un uno lógico. Esta información se almacena en el flip-flop UISA.

Esta información queda registrada en el séptimo bit de la palabra de status.

#### PROGRAMACION DEL MODULO DIGITAL/ANALOGICO.

La programación de esta tarjeta se lleva a cabo enviando la dirección adecuada por el bus de direcciones, es decir, la operación que realizará la tarjeta depende de que la dirección enviada sea decodificada correctamente como se indicó en la parte de decodificación de esta tarjeta.

Las direcciones adecuadas para realizar las distintas operaciones del módulo son enviadas por el bus de direcciones y son comparadas con la palabra contenida en el comparador de magnitud de 8 bites (dirección base), en el cual siempre están fijos los bites desde A7 a A12 (con un microinterruptor), una vez que la comparación fué efectuada satisfactoriamente se habilita el decodificador de dispositivos internos, quien es direccionado por los bites desde A4 a A6 (dirección relativa).

Las operaciones de la tarjeta son especificadas de acuerdo con la tabla siguiente :

| RD* | WR* | DIR<br>A6 |   |   |   | FUNCTION                                  |

|-----|-----|-----------|---|---|---|-------------------------------------------|

| 0   | 1   | 1         | 1 | 1 | 0 | Leer registro de status                   |

| 1   | 0   | 0         | 0 | 0 | 1 | Escribir el MSB en el registro del DAC    |

| 1   | 0   | 0         | 0 | 0 | 0 | Escribir el LSB en el<br>registro del DAC |

En esta tarjeta, la programación de la palabra de identificación está dada por medio de microinterruptores (SW1 Figura IV.B) y puede ser modificada. La habilitación de interrupciones y el bit de existencia de la tarjeta se alambraron por hardware y son un estado alto y otro bajo respectivamente.

### PROGRAMACION DEL MODULO DE INTERRUPCIONES

A continuación se da un mapa de direcciones, así como la función que se realiza en la interfaz.

| •RD | •WR | DIR. REL. | FUNCION                                                           |

|-----|-----|-----------|-------------------------------------------------------------------|

| 1   | 0   | ОН        | Cargar contador O                                                 |

| 1   | 0   | 111       | Cargar contador 1                                                 |

| 1   | 0   | 2H        | Carga: contador 2                                                 |

| i   | 0   | 31(       | Escribir el modo de operación del registro de control.            |

| 0   | 1   | 10H       | Leer parte más significativa<br>de la referencia de temperatura   |

| 0   | 1   | 2011      | Leer parte menos significativa<br>de la referencia de temperatura |

| 0   | 1   | 30Н       | Restaurar la señal de<br>interrupción                             |

| 0   | 1   | 70H       | Leer el status                                                    |

Las direcciones A7-A12 son enviadas por el bus de direcciones y comparadas con la palabra programada en el comparador de magnitud de 8 bites (dirección base), en el que siempre están fijos los bites desde A7 a 12, una vez que la comparación resultó exitosa se habilita el decodificador de dispositivos internos, el cual es direccionado por los bites desde A0-A6 (dirección relativa). La programación de los contadores se describió en la sección V.2.

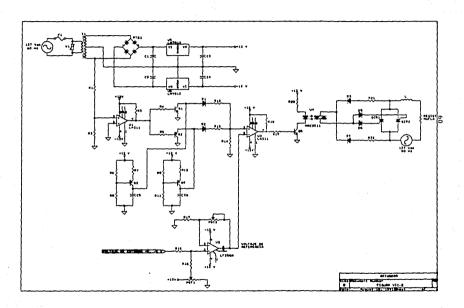

# VII. PLANTEAMIENTO DEL PROSLEMA: Control de un horno eléctrico de 1000 C.

Para probar el sistema en una aplicación de control real y poder evaluar su desempeño, se eligió el control de un horno eléctrico de 1000 •C que se utiliza en algunos laboratorios para la calcinación de muestras químicas y biológicas.

El controlador que se implementó para dicho propósito es del tipo Proporcional-Integral (PI).

El sistema fue diseñado para el manejo y control de cualquier tipo de variable física, solo es necesario contar con las etapas electrónicas del sensado y acondicionamiento de dicha señal y el actuador encargado de regular el sistema. En el caso del control propuesto, fue necesario desarrollar dichas etapas electrónicas.

### VII.1 ACONDICIONAMIENTO DE LA SERAL.

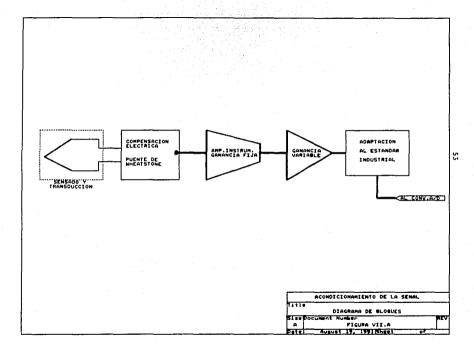

El acondicionamiento de la señal está dividido en tres etapas.

- -Sensado

- -Transducción

- -Amplificación

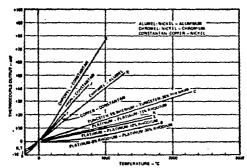

La primera etapa consiste en la elección del sensor adecuado, en este caso, como se va a sensar temperatura en un rango de O·C hasta 1000·C, se llegó a la conclusión de escoger como elemento sensor un termopar tipo K.

La etapa de transducción, que nos da una señal analógica proporcional a la variable física que se está sensando, se incluye también como parte del termopar, ya que este elemento entrega variaciones de voltaje proporcionales a los cambios de temperatura.

En la tercer etapa, que es la de amplificación, se tuvo especial cuidado para realizarla, porque el voltaje

entregado por el termopar es del orden de µV y se requiere amplificarlo con ganancia alta e inmunizarla a fuentes externas de ruido. Por lo anterior, la mejor manera de lograr este objetivo fué utilizando un amplificador de instrumentación, el cual posee una alta razón de rechazo en modo común.

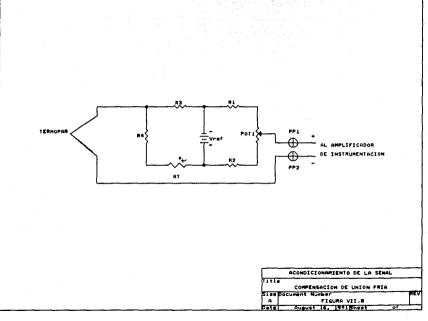

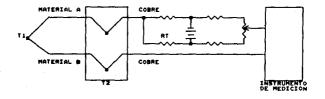

Un diagrama de bloques que ilustra la implementación de la etapa de acondicionamiento de la señal, es mostrado en la figura VII.A.

A continuación se hace una descripción del acondicionamiento, basado en dicho diagrama.

### a) Sensado y transducción.

El funcionamiento esencial del mismo ya se describió en parrafos anteriores.

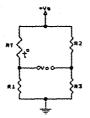

## b) Compensación.

Como nuestro sensor elegido fué un termopar, éste también se ve afectado — de acuerdo con sus propiedades termoeléctricas — en el voltaje entregado, de manera directa por las variaciones de temperatura del ambiente que lo rodea. Para poder contrarrestar el efecto anterior, se realizó un proceso de compensación eléctrica denominado "compensación de unión fría". Esta acción de compensación se lleva a cabo por medio de un circuito eléctrico (Figura VII.B) que incluye un elemento térmoléctrico (termistor) que sirve como agente compensador a las variaciones de temperatura en las uniones del termopar; dicho circuito es un puente de Wheatstone y su función es de linealizar la salida del sensor.

Para determinar el valor de los elementos del puente, desde de un análisis de sensibilidad, se tomó en cuenta el efecto que provocaba cada uno de dichos componentes en la salida de voltaje del puente. Entonces, de la función del voltaje de salida del puente y realizando el análisis de sensibilidad de los elementos se conluyó que que los

parámetros que mayor peso tienen en la estabilidad del voltaje entregado por el puente son los siguientes:

- El voltaje de polarización del puente y

- la resistencia del brazo contiguo al del termistor.

El termistor elegido fué de tipo NTC de valor nominal muy pequeño a la temperatura ambiente (5 Ω a 25 °C). Esto permite tener variaciones de resistencia muy pequeñas cuando cambia la temperatura que rodea al circuito y consecuentemente variaciones muy pequeñas (casi nulas) en el voltaje entregado por el puente, lográndose así el objetivo de compensar a los voltajes inducidos en el termopar debido a los cambios de temperatura ambiente.

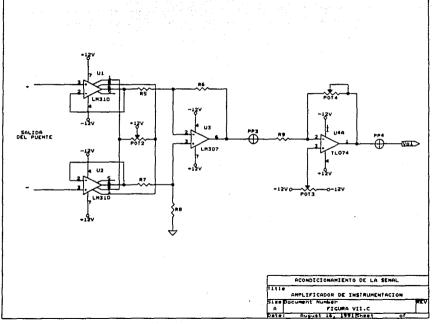

## c) Amplificación y adaptación.

Esta etapa se dividió en dos secciones, una conformada por un amplificador de instrumentación y otra que comprende una etapa de ganancia variable (ajustable).

Para esta etapa, se tomaron como parámetros de diseño a los voltajes normalizados que entrega el termopar para el rango de temperatura de O a 1000 °C, los cuales son O y 41.115 mV respectivamente; además se toma en cuenta las condiciones con las que debía cumplir la señal de salida, de acuerdo con normas preestablecidas para industria (4 a 20 mA).

El amplificador de instrumentación (Figura VII.C) se configuró tomando en cuenta que para tener una señal que cumpliera con la norma industrial de 4 a 20 mA, se debía tener una señal de voltaje acondicionada de tal manera que comprendiera un rango para toda la escala de voltajes que entrega el termopar. Con esto se determinó tener una salida de voltaje final de 0 a -5 V y con ello determinar la ganancia total de la etapa completa de amplificación, que resultó ser de 121.447. Lo anterior corresponde a que a un voltaje de 41.115 mV, a la salida de la etapa se tenga un voltaje de 45 V.

Para poder lograr la ganancia deseada se optó por que el amplificador de instrumentación tuviera una ganancia fija (se eligió una ganancia de 100) para que posteriormente se tuviera un control de ganancia más exacto y poder tener la señal deseada. En la segunda etapa de amplificación se tiene una ganancia de 1.21447 ajustada con un potenciómetro.

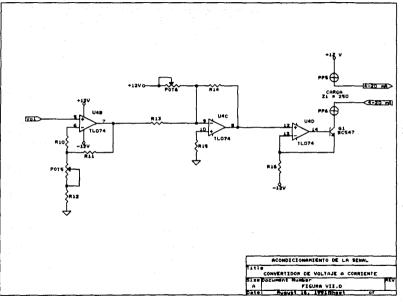

Una vez que se tiene acondicionada la señal a una escala de O a -5 V, se procede a realizar la conversión de voltaje a corriente (Norma de 4-20 mA). Para obtener esta salida, se parte de la señal entregada por el amplificador a la salida del de instrumentación (U4A, Figura VII.C), se utiliza un arregio de amplificadores operacionales para acondicionar el voltaje de tal manera que un transistor NPN (Q1, Figura VII.D) trabaje en la región de conducción (activa directa) y proporcione una corriente equivalente a las variaciones de volta le en su base. Dicho acondicionamiento se lleva a cabo por medio de un amplificador operacional en configuración no inversora con ganancia variable (U4B) y otro amplificador en configuración de sumador-inversor (U4C). A continuación de este último amplificador se realizó el convertidor de voltaje a corriente. que consiste de un amplificador operacional en configuración de no inversor el cual utiliza como lazo de realimentación negativa a un transistor NPN cuya base se conecta a la salida del último operacional. Este transistor interpreta las variaciones de voltaje en su base como variaciones de corriente a través del lazo de realimentación y con esta variación de corriente en la base se puede obtener una variación de corriente en el colector, equivalente al voltaje de entrada. Dicha corriente de colector se obtuvo con un rango de 4 a 20 mA para una impedancia de cargo de 250 O.

# VII.2. DISEÑO Y CONSTRUCCION DEL ACTUADOR.

Se diseñó un dispositivo electrónico capáz de reguiar el suministro de energía al horno eléctrico por medio de una

señal analógica proveniente de la tarjeta de control del sistema (Módulo D/A). Para realizar lo anterior, se desarrolló un circulto basado en el control de los periodos de conducción de un dispositivo semiconductor de potencia (Triac). Este dispositivo es el encargado de dejar pasar mayor o menor energía de la linea de alimentación hacia el horno, debido a que se encuentra en serie con la resistencia eléctrica que realiza el calentamiento del mismo. El control se lleva a cabo modificando el ángulo de disparo o de conducción del triac (ver Figura VII.E).

Para alimentar la circuitería encargada de realizar esta función se construyeron dos fuentes de voltaje (±12 Volts). Para ello se utilizó un transformador reductor de 127 Vrms a 36 Vrms con tap central, una etapa de rectificación de onda completa, filtros y regulación independiente de cada fuente (TI, PTEI, US y U6, Figura VII.E).

## Circuito de control de disparo.

Se deriva la señal senoidal de la linea de alimentación a la salida del transformador, y se le hace pasar por un divisor de voltaje para tenerla en un nivel de voltaje adecuado. Esta señal se introduce a un detector de cruce por cero, el cual conmuta cada vez que la señal de entrada cruza la linea de referencia. Estos cambios en el detector se dan cada 180. de la señal de entrada (120 ciclos por segundo), esta señal cuadrada se utiliza para crear una señal diente de sierra mediante dos fuentes de corriente constante que cargan a dos capacitores (C5 y C6), cada fuente genera un diente de la sierra alternadamente, de tal forma que se presentan de forma sincronizada cada 180. Estas dos señales se unen en un "punto suma", a la salida de este punto tenemos la señal de diente de sierra que está sincronizada con la señal de la linea de alimentación. Esta señal es introducida a la entrada no inversora de un circuito comparador. Por la entrada inversora del comparador se introduce un voltaje de referencia: la modificación en

este voltaje de referencia provoca la variación del nivel de comparación, el cual hará que el comparador conmute cuando la pendiente de subida de cada una de las rampas del diente de sierra alcance el nivel de la señal de comparación. La salida del comparador alimenta a un dispositivo optoeléctrico (optotriac), el cual alsia la etapa de control de la de potencia (formada por SCR1 y SCR2).

La sallda del optotriac maneja a la compuerta (gate) del triac de potencia.

El propósito de hacer commutar al comparador en distintos puntos de la rampa, se traduce en un control sobre el ángulo de disparo del triac de potencia, y como ya se dijo, en sincronía con la linea de alimentación.

Para poder hacer la variación del voltaje de comparación, el circuito cuenta con una etapa que realiza la conversión del rango de voltaje de entrada de ± 5 V a un rango de 0 a 10 V ( voltaje de referencia, U3).

### VII.3. IMPLEMENTACION DEL ALGORITMO DE CONTROL.

En la tarea de controlar un proceso, la teoría de control requiere de los modelos matemáticos de los dispositivos involucrados. En esta sección se muestra el proceso de obtención de los modelos que representan tanto a la planta (horno eléctrico) como al controlador.

La planta fué modelada con base en su respuesta a una entrada escalón.

Para llevar a cabo el proceso de control se eligió un controlador Proporcional-Integral discreto, ya que con este tipo de control se logra que el error en estado estable tienda a cero.

Para obtener el algoritmo de control se realizaron las siguientes actividades :

- a) Obtención de la función de transferencia de la planta mediante la respuesta temporal a una entrada escalón.

- b) Obtención de la función de transferencia del controlador proporcional-integral.

- c) Sintonización óptima de los parametros del control.

- d) Obtención de la función de transferencia del sistema.

- e) Obtención del algoritmo recursivo.

Los incisos a) y b) se desarroliaron para realizar una simulación en computadora. Esta simulación fué útil para observar la respuesta de los parámetros del controlador obtenidos analíticamente, sin embargo, éstos no resultaron óptimos. Basándose en esos valores se hicieron modificaciones hasta obtener resultados esperados dentro de la simulación.

#### Función de Transferencia de la Planta.

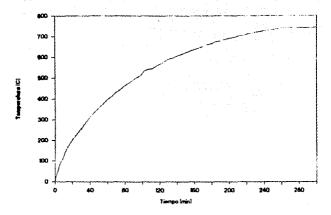

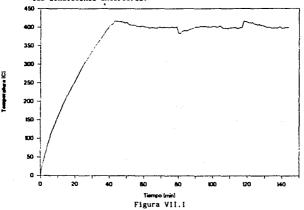

Para encontrar un modelo matemático aproximado de nuestra planta a controlar, se aplicó una entrada escalón para observar su comportamiento en el dominio del tiempo (Figura VII.F). Dicho comportamiento es el de una respuesta de primer orden con tiempo muerto y su función de transferencia se obtiene de la siguiente manera.

De la respuesta temporal de la planta se extraen los parámetros para la construcción del módelo. Estos son : la constante de tiempo, el valor máximo en estado estable, el valor inicial y el tiempo muerto.

Figura VII.F.

Los valores de los parametros son : Constante de tiempo  $\{\tau\} \approx 4860 \text{ s}$  Valor máximo  $(T_{\text{max}}) \approx 742 \cdot \text{C}$  Valor inicial  $(To) = 22 \cdot \text{C}$  Tiempo de levantamiento  $\{t_r\} \approx 175 \text{ min}$  Tiempo muerto  $\{t_r\} \approx 45 \text{ s}$

En el desarrollo del modelo matemático se despreció la contribución del tiempo muerto debido a que resultó muy pequeño comparado con la constante de tiempo, esto facilita la elaboración del modelo.

En el dominio del tlempo la respuesta de la planta puede aproximarse al siguiente modelo:

$$p(t) = 1440 (1-e^{-t/4860}) + 22 \dots (1$$

<sup>\*</sup> No se logra apreciar en la Figura VII.F.

derlyando

$$dp(t)/dt = (1440/4860) (e^{-t/4860})$$

...(2)

aplicando la transformada de Lapiace

$$Z\left(\frac{dp(t)}{dt}\right) = G(S) = \frac{0.2962}{S + 1/4860} \dots (3)$$

pasando al dominio discreto (por tablas) y considerando un periodo de muestreo (ΔT) igual a 300 s.

$$Z \{G(S)\} = G(z) = \frac{0.2962 z}{z - e^{-300/4860}} \dots (4)$$

la función de transferencia de la planta en la variable z queda :

$$G(z) = \frac{0.2962 z}{z - 0.9401} \dots (5)$$

Obtención de la Función de Transferencia del Controlador.

En un control Proporcional-Integral (PI), la señal de salida del controlador u(t) queda definida de la siguiente manera:

$$u(t) = K_c e(t) + K_c/T_1 \int_0^t e(t) dt$$

...(6

y

$$e(t) = r(t) - y(t)$$

...(7)

donde

Ke = ganancia proporcional

Ti = tlempo integral

e(t) = error (entrada al controlador)

r(t) = valor de la referencia (set point)

y(t) = valor de la variable controlada

u(t) = valor de la variable manipulada (salida)

Pasando la ec.(6) a términos del dominio discreto y tomando en cuenta el período de muestreo  $(\Delta T)$  tenenemos :

$$ek = e(k\Delta T)$$

,  $uk = u(k\Delta T)$ ,  $rk = r(k\Delta T)$  y  $ck = c(k\Delta T)$

donde k es un número entero, k= 0.1.2.3....

Entonces, la ec.(6) en el dominio discreto queda:

$$uk = Kc \left\{ ek + 1/T_1 \left[ \frac{e0 + e1}{2} + \dots + \frac{ek-1 + ek}{2} \right] \Delta T \right\}$$

...(8)

donde la integración del tiempo para la acción integral me reemplazó por una aproximación, que es una sumatoria basada en la regla trapezoidal.

Debido a que se utilizará un algoritmo recursivo, la ecuación anterior se maneja por diferencias, así:

entonces, la ec.(8) queda :

$$\Delta u_k = Kc \left\{ (e_k - e_{k-1}) + 1/T_1 \left( \frac{e_{k-1} + e_k}{2} \right) \Delta T \right\} \dots (9)$$

Aplicando el operador discreto:

$$U(z)(1-z^{-1}) = Kc \left\{ \left[ E(z)-z^{-1}E(z) \right] + \Delta T/2Ti \left[ z^{-1}E(z) + E(z) \right] \right\}$$

...(10)

agrupando términos

$$U(z)(1-z^{-1})=E(z)\left\{\left(\frac{\Delta T}{2Ti}+Kc\right)+z^{-1}\left(\frac{\Delta T}{2Ti}-Kc\right)\right\}\ldots(11)$$

si consideramos que

$$a = \frac{\Delta T \ Kc}{2T_1} + Kc \dots (12) \ y \ b = \frac{\Delta T \ Kc}{2T_1} - Kc \dots (13)$$

entonces la función de transferencia del controlador queda:

$$C(z) = \frac{U(z)}{E(z)} = \frac{az + b}{z - 1}$$

...(14)

Sintonización Optima de los Parámetros de Control.

Las fórmulas de sintonización óptimas obtenidas por

Ziegler y Nichols para un controlador PI continuo están dadas por,

$$K_c = 0.9/RL...(15) y Ti = L/0.3 ...(16)$$

donde R es la pendiente más pronunciada de la recta tangente trazada a la gráfica de la respuesta temporal a una entrada escalón, y L es el tiempo en que la tangente cruza el ele del tiempo.

De la Figura VII.F se obtuvo una pendiente R=0.666 y el cruce de la recta con el eje del tiempo es L=40 s (no se aprecia en la figura).

El algoritmo que se propone a continuación se tomó de un ensayo experimental propuesto por Y. Takahashi, C.S. Chan y D.M. Auslander (Ref.11).

Para cumplir con dicho algoritmo, los parámetros del controlador se calculan a partir de la respuesta temporal de la planta a controlar. Las ecuaciones experimentales son las siguientes:

$$K_{L} = \frac{0.27 \text{ AT}}{R \left(L + \Delta T/2\right)^{2}} \qquad \dots (17)$$

$$K_p = \frac{0.9}{R(L + \Delta T/2)} - K_1/2$$

...(18)

La relación entre los parámetros experimentales anteriores y los parámetros del control PI (Kc y Ti) es:

$$K1 = (K_0/T_1)\Delta T \qquad ...(19)$$

$$K_P = K_C - K_1/2$$

...(20)

Tomando los valores de R y L. Considerando  $\Delta T = 300 \text{ s}$  y sustituyendo en las ecs. (17) y (18)

$$K_P = 5.4229 \times 10^{-3}$$

y  $K_1 = 3.3659 \times 10^{-3}$

sustituyendo en las ecs.(19) y (20), obtenemos los valores de Ti y  $K_{\rm c}$ .

Con estos valores podemos obtener los coeficientes (a y b) de la función de transferencia del controlador (ec.(14)).

Sustituyendo Ti y Kr en las ecs. (12) y (13),

$$a = 8.7887 \times 10^{-3}$$

y  $b = -5.4228 \times 10^{-3}$

entonces la primera aproximación de la función de transferencia del controlador PI queda:

$$C(z) = \frac{U(z)}{F(z)} = \frac{8.7887 \times 10^{-3} z - 5.4228 \times 10^{-3}}{z - \frac{1}{2}} \dots (21)$$

#### Obtención de la Función de Transferencia del Sistema.

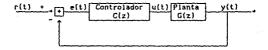

Para encontrar la función de transferencia del sistema se utiliza el siguiente esquema:

$$F(t) = \frac{C(z)G(z)}{1 + C(z)G(z)} \qquad y(t)$$

La ecuación de transferencia total usando (5) y (21) queda:

$$H(z) = \frac{2.596 \times 10^{-3} z (z - 0.617)}{(z - 0.9654)(z - 0.9712)} \dots (22)$$

#### Obtención del Algoritmo Recursivo.

Para las aplicaciones de control digital es necesaria una ecuación de recurrencia para cuantificar el error entre muestras y generar una señal actuadora (u(t)).

De la ec. (9), sustituyendo ek = rk-yk y asumiendo que

FE = FE-1 = FE-2, obtenemos

$$\Delta u(k) = Kc \left\{ \left( y_{k-1} - y_k \right) + \left( r_k - (y_{k-1} + y_k)/2 \right) \Delta T/T_1 \right\} \dots (23)$$

quedando entonces la ecuación en forma canónica (ec. recursiva)

$$u_k = K_P (y_{k-1} - y_k) + K_I (r_k - y_k) + u_{k-1} \dots (24)$$

La ecuación anterior es la que se incluye en el programa de control (sección VIII.2).

#### VII.4. RESULTADOS DE LAS PRUEBAS.

Con base en el algoritmo de control implementado fueron realizadas algunas pruebas para observar su desempeño.

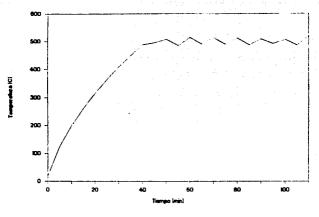

El objetivo de la primera prueba fué el observar el efecto de los parámetros anteriores en la respuesta escalón y cuantificar el porcentaje de error en estado estable. En la Figura VII.G se tiene la respuesta obtenida para las condiciones citadas.

Esta prueba se realizó con los siguientes parámetros :

Tref = 500 .C

ΔT = 300 s

Kp = 9.6 x 10<sup>-3</sup>

$K_1 = 4.8 \times 10^{-3}$

Figura VII.G

Como se observa en la figura anterior, con los parámetros de control utilizados ( $K_P$  y  $K_I$ ) se obtiene una respuesta que presenta un tiempo de asentamiento  $t_P$  = 37.5 min; un tiempo de levantamiento  $t_P$  = 32 min y pequeñas oscilaciones presentes alrededor de la temperatura de referencia.

La segunda prueba consistió en modificar el valor de la referencia después de alcanzado el estado estable. Los parámetros empleados fueron:

Treff = 300 •C Tref2 = 250 •C(a los 50 min.)  $\Delta T$  = 300 s  $K_p$  = 7.014 x 10<sup>-3</sup>  $K_1$  = 3.546 x 10<sup>-3</sup>

Los resultados de esta prueba son mostrados en la Figura VII.H.

Figura VII.H

En la gráfica anterior, se observa que de acuerdo con los nuevos parámetros de control la respuesta fué más rápida (tri = 17.5 min) y se presentó un pequeño sobrepaso. Se obtuvo un tiempo de asentamiento (tsi) de 30 min. Al establizarse a la primera temperatura de referencia se obtuvo un error en estado estable del 1 %. Después se modificó la referencia a Trerz (en to = 50 min) y se observó que la respuesta fué igual de rápida que para la primera referencia (trz = 17.5 min), el tiempo de asentamiento (tez) de 27.5 min. medidos después del cambio de referencia.

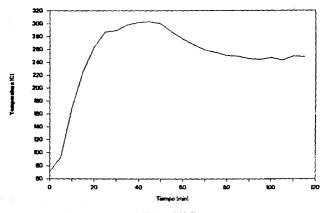

En la última prueba se sometió a la planta a perturbaciones externas. Estas consistieron en permitir el escape del calor abriendo la puerta del horno, para después cerrarla. Esto representa perturbaciones de tipo escaión. La prueba se desarrolló usando los siguientes parámetros :

Tref = 400 °C  $\Delta T$  = 60 s  $K_P$  = 9.6 × 10<sup>-3</sup>  $K_1$  = 2.516 × 10<sup>-3</sup> 1<sup>a</sup> Perturbación t1= 79 min. 2<sup>a</sup> Perturbación t2= 117 min.

La Figura VII.I muestra el comportamiento del sistema bajo las condiciones anteriores.

La respuesta anterior presenta un sobrepaso del 4.25% y un error en estado estable del 0.5 %. Como se observa, al presentarse las perturbaciones, el algoritmo de control corrige las variaciones de la temperatura hasta forzarla a

alcanzar de nuevo la de referencia.

Se realizaron cambios en los parámetros del algoritmo de control para lograr distintas respuestas y poder determinar los valores óptimos.

Los cambios realizados en las constantes  $K_P$  y  $K_I$  en cada una de las pruebas, muestran los efectos de ellas en la

respuesta del sistema. Entonces, con la modificación de dichos parámetros se logra alterar la velocidad de respuesta, así como las oscilaciones alrededor de la referencia.

#### VIII. CONCLUSIONES

El desempeño de cada uno de los módulos desarrollados permiten concluir que el sistema es bastante versátil, debido a la facilidad para modificar los modos de operación de cada módulo con el fin de adaptarse a distintas aplicaciones de control.

El hecho de poder conectarse a una terminal de video logra, en gran medida, la versatilidad antes mencionada, debido a que permite la visualización directa de la información y la modificación de los programas; así como el poder guardar dicha información en medios masivos de almacenamiento (discos flexibles, duros y cintam magnéticas). Si la aplicación de control no justifica el tener permanentemente una terminal de video conectada al sistema, se tiene la opción de grabar el programa de aplicación en memoria ROM.

El sistema presenta la ventaja de operar bajo una norma industrial que permite la compatibilidad con otros sistemas comerciales para crear uno más complejo.

Como se menciona en los capítulos anteriores, todos los módulos desarrollados utilizan tecnología HCMOS, lo cual proporciona rapidez y un bajo consumo de energía.

Las señales analógicas de entrada para el módulo A/D y las señales de salida para el módulo D/A cumplen con características ampliamente usadas en la industria (±5 volts y 4 a 20mA). Lo cual permite la conexión con una amplia gama de dispositivos actuadores y acondicionadores de señal.

El sistema cuenta con la opción de manejar una referencia externa (sel point) con el fin de que el usuarlo pueda modificarla según sus necesidades de control.

En lo que respecta al control realizado y tomando en cuenta las pruebas efectuadas en el capítulo anterior, se

concluye que éste tiene un comportamiento bastante bueno ya que siempre es posible modificar los parámetros de la prueba para poder obtener la respuesta que más se acerque a las necesidades del control. Además, que el algoritmo utilizado corrige cualquier alteración de la temperatura debido a perturbaciones o a un cambio en la referencia. Los porcentajes de error en estado estable son lo suficientemente pequeños como para decir que se obtuvieron resultados bastante satisfactorios.

Estamos concientes de que cualquier proceso de importancia involucra más de una variable física a controlar. Sin embargo, este trabajo tiene además un fin didáctico, aunque bastarían algunos pequeños cambios en cuanto a la circuitería y otros tantos en la programación para poder manejar mayor número de variables.

#### IX. BIBLIOGRAFIA

- Sánchez Guzmán. USO DE TERMOPARES EN MEDICIONES DE TEMPERATURA, TESIS, Fac. de Química, UNAM. 1987.

- Cadena Delgado. DISEÑO Y CONSTRUCCION DE UN CONTROL POR MICROCOMPUTADORA PARA UN PROCESO TERMICO. TESIS. Fac. de Ingeniería, UNAM. 1987.

- Gon Wong/Alvarez Icaza. CONTROLADOR UNIVERSAL INDUSTRIAL. Instituto de Ingeniería, UNAM. Sept. 1989.

- IEEE Standard for an 8-Bit Microcomputer Bus System: STD bus. IEEE Std 961-1986. The Institute of Electrical and Electronics Engineers. Inc. New York. 1988.

- Ogata Katsuhiko. <u>INGENIERIA DE CONTROL HODERNA.</u>

Ed. Prentice Hall. 1980.

- Carrera Méndez/García Cruz. 11ACDA-21 INTERFAZ PC-COMPATIBLE PARA MANEJO DE SEÑALES ANALOGICAS Y DIGITALES. Informe Interno. Instituto de Ingeniería, UNAM. Marzo 1990.

- Carrera Méndez/Guevara Garay. DESARROLLO DE UN EQUIPO DE ADQUISICION DE DATOS EN CAMPO. Informe interno. Instituto de Ingenieria. UNAM. Junio 1989.

- TRANSDUCER INTERFACING HANDBOOK. A guide to analog signal conditioning. Ed. Daniel H. Sheingold. Published by Analog Devices, Inc. 1980.

- Chase Donald. CONSIDER EVERY ERROR SOURCE FOR DATA ACQUISITION DESIGN. <u>Control Engineering</u>. Junio 1980.

- Jaeger/ Auburn University, TUTORIAL: ANALOG DATA ACQUISITION TECHNOLOGY.

- Part I.- Digital-to-Analog Conversion. Mayo 1982.

- Part III.- Sample-and-Holds. Instrumentation Amplifiers, and Analog Multiplexers. Noviembre 1982.

- Part IV.- System Design, Analisis and Performance. Febrero 1983.

- IEEE MICRO.

- Takahashi Y., Chan C.S., Auslander D.M. PARAMETER TUNING OF LINEAR DDC ALGORITHMS. ASME, 1971.

# A. APENDICES.

### A.1 REVISION DE LA NORMA 1EEE-961 (STD-BUS).

# Descripción del estándar

Este estándar, como toda norma internacional, está especificada en todas sus características tanto eléctricas como mecánicas. La norma fué aprobada por la directiva de estándares de la IEEE (The Institute of Electrical and Electronics Engineers, Inc.) el 10 de diciembre de 1987. El estándar es la descripción de un sistema basado en un microprocesador de 8 bites y es conocido como STD-BUS.

Tanto el tamaño del bus como su organización se seleccionaron para servir como interfaz entre cualquier microprocesador de 8 bites y una amplia variedad de dispositivos de memoria y de entrada/salida.

El propósito de este estándar es el de definir las características físicas, lógicas, eléctricas y los requerimientos de tiempo en sus señales para asegurar el mayor grado de compatibilidad en cualquier tarjeta que se quiera conectar al sistema. Ofrece además una distribución ordenada de las señales del bus que facilitan la incorporación de interfaces.

Esta especificación define un sistema estándar donde el tamaño reducido de las tarjetas, en conjunto con la tecnología de alta integración (LSI), da por resultado un sistema modular por funciones orientado al control de procesos industriales.

La norma define un conector tipo peine de 56 postes por el cual se realizan las conexiones con cada una de las tarjetas, de tal forma que es posible agregar funciones completas de manera modular a un sistema con sólo instalar

#### la tarjeta en el bus.

La forma de operación del STD-BUS se basa en suponer que en un instante dado solamente existe un dispositivo capáz de enviar direcciones validas al sistema.

# Distribución de los postes según su función.

La disposición de los postes en el STD-BUS está organizada en cuatro grupos funcionales:

| - Lineas de polarización | postes 1-6 y 53-56 |

|--------------------------|--------------------|

| - Bus de datos           | postes 7-14        |

| - Bus de direcciones     | postes 15-30       |

| - Bus de control         | postes 31-52       |

Tabla A.1.1

# Descripción de las señales del STD-BUS.

## Lineas de polarización (postes 1-6 y 53-56)

Estas lineas incluyen las fuentes de alimentación para el sistema. Se tiene la posibilidad de conectar cuatro fuentes distintas con dos tierras separadas.

# Bus de datos (DO a D7, pines 7-14).

Este és un bus de 8 bites, bidireccional de tres estados. La dirección en la que se dan los datos es afectada por señales tales como la de lectura (\*RD), la escritura (\*WR) y por el reconocimiento de una interrupción (INTAK\*).

EL bus de datos emplea lógica activa alta y cuando no es empleado debe estar en estado de alta impedancia. Cuando algún sistema alterno exiga el manejo del bus de datos (BUSRQ\*), éste podrá ser entregado a dicha solicitud.

# Bus de direcciones (AO a A15, postes 15 al 30).

Este bus es de 16 bites, activo alto, tres estados; las direcciones las envía el dispositivo que tiene el control

del bus, el cual también puede ser liberado a algún controlador alterno.

Estas 16 lineas de direcciones pueden decodificar tanto a puertos de entrada/salida como a memoria, mediante las lineas de control IORQ\* y MEMRQ\*, respectivamente.

#### Bus de control (postes 31 a 52).

De este bus depende en gran medida la flexibilidad del STD-BUS. Sus señales se agrupan en cinco grupos: Control de memoria y puertos, temporización de periféricos, reloj y reset, interrupción y control del bus, además del encadenamiento de prioridad serie. A continuación, una breve explicación de cada grupo de señales:

Control de memoria y puertos. En este grupo de señales se encuentran aquellas que sirven para realizar operaciones básicas a memoria o puertos. Normalmente se requieren de las siguientes señales:

- WRº Escritura a memoria o puertos.

- RD\* Lectura a memoria o puertos.

- IORO® Habilitación de puertos.

- MEMRO\* Habilitación de memoria.