# UNIVERSIDAD LA SALLÉ

ESCUELA DE INGENIERIA INCORPORADA A LA UNIVERSIDAD NACIONAL AUTONOMA DE MEXICO

"DISEÑO DE UNA INTERFAZ PARA EL CONTROL DE INSTRUMENTOS EN UNA ESTACION DE TRABAJO AUTOMATIZADA"

T E S I S

QUE PARA OBTENER EL TITULO DE

INGENIERIO MECANICO-ELECTRICISTA

CON AREA PRINCIPAL EN ELECTRONICA

PRESENTA

IGNACIO CRISTERNA GUZMAN

TESIS CON FALLA DE ORIGEN

MEXICO, D. F.

1988

UNAM – Dirección General de Bibliotecas Tesis Digitales Restricciones de uso

# DERECHOS RESERVADOS © PROHIBIDA SU REPRODUCCIÓN TOTAL O PARCIAL

Todo el material contenido en esta tesis esta protegido por la Ley Federal del Derecho de Autor (LFDA) de los Estados Unidos Mexicanos (México).

El uso de imágenes, fragmentos de videos, y demás material que sea objeto de protección de los derechos de autor, será exclusivamente para fines educativos e informativos y deberá citar la fuente donde la obtuvo mencionando el autor o autores. Cualquier uso distinto como el lucro, reproducción, edición o modificación, será perseguido y sancionado por el respectivo titular de los Derechos de Autor.

# INDICE

| INTRODUCCION                                       | 1            |

|----------------------------------------------------|--------------|

|                                                    |              |

| CAPITULO I. PANORAMICA GENERAL DEL TRABAJO         | 14.          |

|                                                    | 200          |

| I.I PROPOSITO Y JUSTIFICACION                      | 1-1          |

| 1.2 ANTECEDENTES                                   | 1-1          |

| 1.3 CARACTERISTICAS DE LA NORMA ILEE-488           | 1-2          |

| 1.3.1 GENERALIDADES                                | I-2          |

| 1.3.2 ARQUITECTURA DEL BUS IEEE-488                | I-4          |

| 1.4 CARACTERISTICAS DE LA MEDICION AUTOMATIZADA    | 1-10         |

|                                                    |              |

| CAPITULO II, PROCEDIMIENTOS DEL BUS IEEK-488       | 1.12.        |

|                                                    | /:: <u>.</u> |

| 11.1 CARACTERISTICAS DEL PROTOCOLO IEEE-488        | 1-1          |

| II.1.1 LINEAS COMPONENTES DEL BUS                  | 1-1          |

| 11.1.2 TRANSPERENCIA DE DATOS EN EL BUS IREE-488 ; | 143          |

| ****** Innarenchia De Daiva en eu oua lees 400!    | 3            |

| II.1.3 DIRECCIONAMIENTO EN EL BUS                         |

|-----------------------------------------------------------|

| II.1.4 CARACTERISTICAS ELECTRICAS                         |

| II.1.5 CARACTERISTICAS MECANICAS                          |

| II.1.6 LA NORMA JEEE-488 CON RESPECTO A LA NORMA          |

| IEC-625                                                   |

| 11.2 CONCEPTUALIZACION DE UNA TARJETA DE INTERPAZ .11-36  |

| II.3 DEFINICION DE LAS FUNCIONES À REALIZAR POR LA        |

| TARJETA                                                   |

| II.4 DIAGRAMA A BLOQUES DE LA TARJETA                     |

|                                                           |

| CAPITULO III. DISEÑO DE LA INTERFAZ Y CARACTERISTICAS     |

| DE ACOPLAMIENTO AL COMPUTADOR.                            |

|                                                           |

| III.1 GENERALIDADES                                       |

| III.2 ACOPLAMIENTO A LA COMPUTADORA PERSONAL III-4        |

| III.2.1 CARACTERISTICAS DEL CONECTOR DE EXPANSION. III-4  |

| III.2.2 RELACIONES DE TIEMPO EN EL CONECTOR DE            |

| EXPANSION                                                 |

| III.3 DISEÑO DE LA TARJETA                                |

| III.3.1 INTERACCION DE LOS REGISTROS DE LA TARJETA        |

| CON LA COMPUTADORA                                        |

| III.3.2 CIRCUITO DE SINCRONIZACION                        |

| III.3.3 ACOPLAMIENTO DE LA TARJETA AL BUS IEEE-488 III-52 |

| 11.310 Decembers of the result of the 1880-400 files      |

| CAPITULO IV. ESPECIFICACIONES SOBRE EL AMBIENTE           |

| V ODERACION DE LA TARISMA                                 |

|                                                           |

| •   |                                                     |        |

|-----|-----------------------------------------------------|--------|

|     | IV.1 CARACTERISTICAS DE LA COMPUTADORA EN LA QUE    |        |

|     | SE USARA LA INTERFAZ                                | . IV-1 |

|     | IV.1.1 GENERALIDADES                                | IV-1   |

|     | IV.1.2 ALGUNAS CONSIDERACIONES SOBRE COMPATIBILIDAD | 1V-3   |

|     | IV.2 PROGRAMAS PARA LA TARJETA                      | IV-7   |

| 100 | IV.2.1 ARQUITECTURA INTERNA DEL CONTROLADOR PD7210. | 1V-7   |

|     | IV.2.2 CARACTERISTICAS DEL MICROPROCESADOR 8088     | IV~17  |

|     | IV.2.3 DESCRIPCION DE LAS RUTINAS DE PRUEBA         | IV-21  |

|     |                                                     |        |

|     | CAPITULO V. ARMADO Y PRUEBA DE LA TARJETA.          |        |

| •   |                                                     |        |

|     | V.1 ARMADO DEL EQUIPO                               | V-1    |

|     | V.1.1 CONSIDERACIONES SOBRE LA CONSTRUCCION         | V-1    |

| •   | V.1.2 CONSTRUCCION DE LA TARJETA,                   | V-2    |

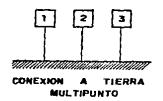

|     | V.1.3 DISMINUCION DE RUIDO                          | V-3    |

|     | V.1.3.1 SISTEMA DE TIERRAS                          | V-3    |

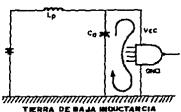

|     | V.1.3.2 DESACOPLAMIENTO DE LA FUENTE                | V-6    |

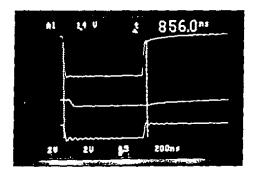

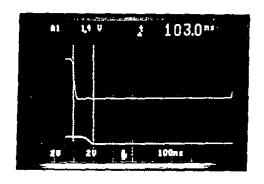

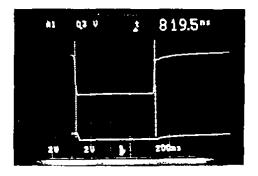

|     | V.2 PRUEBA FUNCIONAL                                | V-9    |

|     | V.2.1 PRUEBA MEDIANTE PROGRAMA DEL SISTEMA          | V-9    |

|     | V.2.2 MEDICION DE LOS TIEMPOS DE ACCESO             | 7-12   |

|     | •                                                   |        |

|     | CAPITULO VI. CONEXION DE UN INSTRUMENTO COMPATIBLE  |        |

|     | CON EL BUS IEEE-488 A LA COMPUTADORA.               |        |

|     |                                                     |        |

|     | VI.1 CARACTERISTICAS DEL MODULO                     | VI-1   |

| •   | VI.1.1 ATRIBUTOS GENERALES                          | VI-1   |

|     | VI.1.2 CARACTERISTICAS DE USO                       | VI-4   |

|     | 4-1                                                 |        |

|     |                                                     |        |

|     |                                                     | •      |

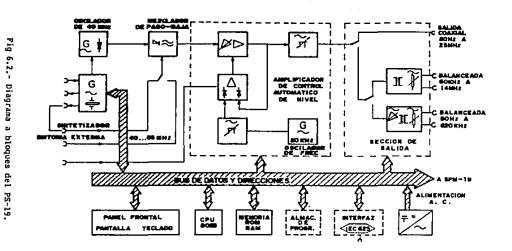

| VI.2 DIAGRAMA A BLOQUES DEL INSTRUMENTO VI-      |

|--------------------------------------------------|

| VI.3 ESPECIFICACIONES DEL ACOPLAMIENTO A         |

| LA COMPUTADORA VI-                               |

| VI.3.1 GENERALIDADES                             |

| VI.3.2 FUNCIONAMIENTO DEL INTERFAZ DEL PS-19 VI- |

| VI.3.3 FUNCIONES DEL BUS                         |

| VI.4 PROGRAMACION DEL PS-19                      |

|                                                  |

| CONCLUSIONES                                     |

|                                                  |

| APENDICE 1                                       |

|                                                  |

| APENDICE 2                                       |

|                                                  |

| ANEXO                                            |

|                                                  |

| REFERENCIAS                                      |

# INTRODUCCION

La proliferación de las computadoras personales proporcionado una gran capacidad de manejo de información a instituciones que, antaño, habían sido relegadas de las ventajas inherentes al uso de la computación. Esto es especialmente cierto para los laboratorios de investigación, los cuales dependian de instalaciones de cómputo centralizadas (Cuyo control les era ajeno) y generalmente saturadas lo que significaba un tiempo de respuesta bastante grande y la imposibilidad de usar estos recursos de cómputo en procesos que requieran toda la atención del procesador. Con las computadoras personales, cualquier laboratorio podrá contar con recursos de computo de los que se podrá disponer en forma total, de bajo costo y que podrán usarse para el control de experimentos que requieren de completa atención por parte de la computadora. Te ahi la necesidad de construir los elementos que permitan adaptar estas computadoras a las necesidades de instituciones de investigación.

En este trabajo se abordará el diseño y construcción de un circuito que adapta una de estas computadoras personales a una aplicación relacionada con el control y adquisición de datos de instrumentos. En el capítulo 1 se describe el propósito específico de este trabajo mencionando las razones del enfoque dado, especialmente el por que de la utilización de un cierto formato de

manejo de datos. En el capítulo 2 se describe el protocolo usado para la comunicación de datos, mencionando sus características funcionales, eléctricas y mecánicas. En el capítulo 3 se describe el diseño de la tarjeta haciendo énfasis en las relaciones de tiempo presentes en el conector de expansión de la computadora. En el capítulo 4 se describen las rutinas usadas para manejar algunas de las operaciones ejecutables por la tarjeta. En el capítulo 5 se describen los procedimiemtos usados en el armado de la tarjeta para su conexión a la computadora personal. En el capítulo 6 se describe una aplicación para el circuito diseñado, incluyendo un programa para el control de un instrumento de laboratorio.

# CAPITULO I. PANORAMICA GENERAL DEL TRABAJO

#### I.1 PROPOSITO Y JUSTIFICACION

El propósito de este trabajo es diseñar una tarjeta por medio de la cual conectar una computadora personal a un sistema de medición que funcione de acuerdo al protocolo IEEE-488. Este proyecto surgió debido a la necesidad de lograr una mayor flexibilidad en la realización de mediciones utilizando instrumentos programables e integrar los recursos de una computadora personal proporcionando capacidades de almacenamiento y programación a bajo costo.

## 1.2 ANTECEDENTES

El problema del acoplamiento entre computadoras e instrumentos de medición con capacidades de comunicaciones digitales surgió tan pronto como éstos fueron puestos en uso. La posibilidad de obtener el equivalente binario del resultado de una medición sugirió la posibilidad de acoplar los instrumentos que contaran con esa capacidad a sistemas de cómputo que facilitaran la realización de pruebas y la captura de resultados así como el almacenamiento posterior de las configuraciones de los instrumentos a fin de poder recrear una prueba sin necesidad de realizar nuevamente los ajustes necesarios.

Uno de los primeros modos de comunicación entre instrumentos digitales, y actualmente el más utilizado en estas aplicaciones, es el bus IEEE-488 para el que actualmente se pueden encontrar aparatos capaces de medir toda clase de magnitudes eléctricas.

## I.3 CARACTERISTICAS DE LA NORMA IEEE-488

#### I.3.1 GENERALIDADES.

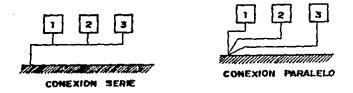

El bus IEEE-488 fue establecido en 1975 con el nombre formal de "IEEE Standard Digital Interface for Programmable Instrumentation". Este tuvo una revisión mayor en 1978, en la cual, de acuerdo al comité encargado de la normalización, "...se han realizado cambios de naturaleza técnica, [Y] estos proporcionan claridad a los enunciados potencialmente ambiguos"... Este fue diseñado en base a una serie de objetivos que definirían las características principales del bus. Estas son:

- a) Estructura de linea compartida

- b) Velocidad de transferencia de datos menor a un millón de bytes por segundo (aunque la velocidad de operación típica de dispositivos reales fluctúa entre 25 y 100 mil bytes por segundo.

- c) Transferencia de bits en paralelo, bytes en serie

- d) La longitud máxima del cable de interconexión entre instrumentos conectados al bus será de 20 metros o dos veces el número en metros de los dispositivos conectados; lo que resulte en la menor distancia

Además, de acuerdo al comité encargado de establecer la norma, se adoptó una estructura que permitiera reducir los costos en la circuiteria necesaria para construir la interfaz dentro de un instrumento.

Otra consideración importante fue la búsqueda de flexibilidad, es decir la capacidad de utilizar el bus no solo para el intercambio de datos y comandos entre los controladores y los instrumentos de medición sino también contar con la posibilidad de accesar periféricos de impresión y almacenamiento masivo de información.

# 1.3.2 ARQUITECTURA DEL BUS 1EEE-488

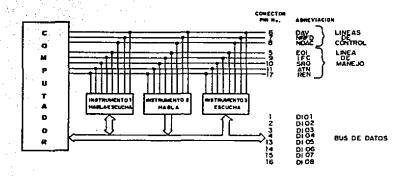

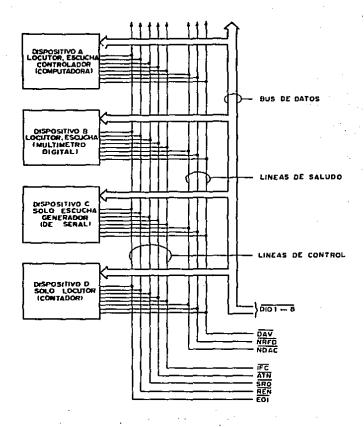

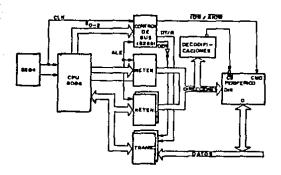

La figura 1.1 muestra la estructura general del bus agrupando las lineas de acuerdo con sus características funcionales.

Fig. 1.1.-Estructura general del bus IEEE-488.

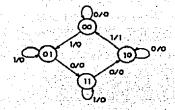

El documento en el que se enuncian las características del protocolo es sumamente detallado, especialmente en lo referente a las transacciones en el bus. Dicho protocolo de comunicaciones se basa en jun conjunto de funciones llamadas funciones de interfaz y que son independientes de las capacidades y aplicación del instrumento. Cada una de estas funciones está encargada de realizar una tarea dentro del sistema. Como ejemplo de esto, una función se encarga de recibir un dato para el dispositivo mientras que otra se encarga de enviar un dato a otro dispositivo componente del sistema y otra más se encargará de la generación de los mensajes a enviarse a través del sistema. La operación de cada una de las funciones está compuesta de estados que se verifican a medida que se presentan una o más condiciones (y en algunos casos una vez que ha transcurrido un cierto intervalo de tiempo, mientras que en otros casos la activación del estado deberá ocurrir antes de que transcurra un cierto intervalo de tiempo). El funcionamiento de estos estados es similar al seguido durante la operación de una función construida a base de circuitos biestables (flip-flops), es decir realiza una operación secuencial. La figura 1.2 muestra el diagrama de estado de un circuito secuencial. En este diagrama cada estado se representa por un circulo y las transiciones entre los estados se indican con líneas dirigidas que conectan estos circulos.

Fig. 1.2.- Estados en un circuito secuencial.

El número binario contenido en cada círculo identifica al estado representado y las lineas dirigidas están marcadas con dos números binarios separados por una diagonal (/). El número escrito a la izquierda de la diagonal representa al valor que provoca la transición al siguiente estado mientras que el número colocado a la derecha es el valor de salida durante el estado presente. Así, la linea que conecta el estado 00 con el 01 tiene junto a clla la expresión (1/0), significando que el circuito secuencial está en el estado presente mientras X=l y que la salida en este estado es Y=0; al terminar el siguiente pulso de reloj el circuito pasa al estado 01. En el diagrama de estados, una linea dirigida que conecta al estado consigo mismo indica que en esas condiciones no ocurre cambio de estado. Como se puede observar, el diagrama de estados representa claramente los estados en que puede incurrir el. circuito durante su operación, las condiciones requeridas para efectuar una transición y los valores de salida que se presentarán en cada uno de los estados. La característica más importante de

este tipo de diagramas es que nos brinda una representación gráfica del comportamiento del circuito al indicarnos el orden de ocurrencia de los estados (es decir la secuencia de operación).

La norma IEEE-488 utiliza diagramas similares para describir funcionamiento de cada una de las funciones de interfaz aunque la notación usada muestra algunas diferencias respecto de los diagramas de estado mencionados anteriormente. En los diagramas de las funciones de la interfaz cada estado se representa por medio de circulo y el estado se nombra con un palabra nemotécnica de 4 letras mayúsculas siendo la última letra una S (que indica que se está refiriendo a un estado). Las transiciones se representan por lineas dirigidas pero a diferencia del tipo anterior de diagramas, utilizan expresiones en lugar de valores binarios para determinar las transiciones de un estado a otro. function de interfaz deberá permanecer en su estado presente si todas las expresiones que determinan transiciones a otros estados son falsas y se permitira la transición unicamente cuando alguna de dichas expresiones sea verdadera; la transición puede ocurrir en cualquier momento a menos que se especifique una restricción de tiempo. expresión que califica la transición consiste de uno o más mensajes locales, mensajes remotos, encadenamientos de estado (ocurrencia de ciertos estados en otras funciones de la interfaz) y límitos tiempo junto con los operadores AND (^), OR (v) y NOT (-). igual que en los diagramas de estado de los circuitos digitales en general, el documento de la normalización especifica, mediante una tabla separada, los mensajes de salida de cada uno de los estados

que componen las funciones de interfaz. Dichos mensajes son en realidad el estado que adoptará alguna de las líneas del bus (alto o bajo). De esta manera se detalla el funcionamiento de cada una de las funciones de interfaz proporcionando la secuencia de estados y las condiciones para la verificación de dichos estados.

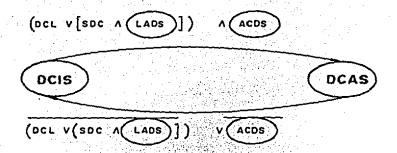

Para ejemplificar esto, en la figura 1.3 se reproduce el diagrama de estados de la función "LIMPIAR DISPOSITIVOS" (DC):

Fig. 1.3. - Funcionamiento de la función DC

Como se puede observar en el diagrama, la función consta de dos estados liamados DCIS (Device Clear Idle State) que es el estado inactivo o de inicio de la función de interfaz y DCAS (Device Clear Active State).

Sin lugar, a dudas una de las principales particularidades del documento en el que se específica el protocolo es el gran detalle con que se describen las funciones, interacciones, señales, estados, mensajes y características especiales de la interfaz, lo que se vuelve sumamente monótono y en algunas ocasiones redundante.

La representación de las funciones de la interfaz por medio de diagramas de estado tiene tres conclusiones directas para la persona encargada de diseñar un dispositivo que deba acoplarse al bus IEEE-488:

- (a) El circuito se deberá construir en base a circuitos digitales secuenciales

- (b) La inclusión de funciones de interfaz con una gran cantidad de estados resultará en un circuito con gran Cantidad de componentes.

- (c) La realización de varias (o todas) las funciones de la interfaz es una excelente aplicación para los circuitos de alta escala de integración (VLSI).

## I.4 CARACTERISTICAS DE LA MEDICION AUTOMATIZADA.

El objetivo de este trabajo, como ya se mencionó anteriormente, es el diseñar una interfaz para una computadora personal. El fin de esto es el de automatizar las mediciones en un laboratorio de electrónica o cualquier instalación que cuente con instrumentos programables de tal forma que permita almacenar los resultados de dichas mediciones utilizando los recursos de la computadora personal.

Uno de los principales usos de los procesos automáticos es en el campo de las pruebas y las mediciones. Estas son de particular importancia en el diseño de circuitos electrónicos y en su posterior mantenimiento.

En México, las mediciones automatizadas se encuentran, todavia, en su fase inicial. Esto se ha debido principalmente al hecho de que, hasta principios de esta decada, la configuración de un sistema de medición requerta de un controlador dedicado con un costo sumamente elevado, lo que significa que la mayoría de los laboratorios y centros de investigación, sin contar a las escuelas y universidades, con presupuestos siempre limitados, quedaban fuera de los beneficios originados del queo de los instrumentos programables.

Con la popularización, de las computadoras personales, especialmente del tipo compatible con la computadora personal de IBM (cuyas características se discutirán en un capítulo posterior) se incrementó la adquisición de éstas por parte de los centros de investigación lo que trajo como consecuencia el uso de ellas en una gran cantidad de actividades.

Es necesario tener en mente que las grandes computadoras con que contaban algunos centros de investigación podrían, también, utilizarse para la automatización de mediciones y otros procesos. Sin embargo las compañías fabricantes de estas máquinas siguen una

política de ocultamiento de información con respecto de los esquemas de direccionamiento, tipos de acceso, señales de control, tamaño del dato. Esto fue lo que evitó que se construyeran interfaces que pudieran aplicar estas grandes máquinas a usos particulares o diferentes del procesamiento de datos. Además, para asegurar la rentabilidad del uso de ellas es necesario que sean utilizadas por varias personas simultaneamente, impidiendo su utilización en procesos que requieran la atención completa del procesador.

# CAPITULO II

# PROCEDIMIENTOS DEL BUS

#### II.1 CARACTERISTICAS DEL PROTOCOLO IEEE-488

## 11.1.1 LINEAS COMPONENTES DEL BUS.

En el capítulo 1 se anotaron las características fundamentales del bus IEEE-488. En esta parte del capítulo 2 se hará una revisión más profunda de este protocolo como base para la descripción del funcionamiento de una tarjeta cuyo objetivo es acoplar una computadora personal a un sistema IEEE-488

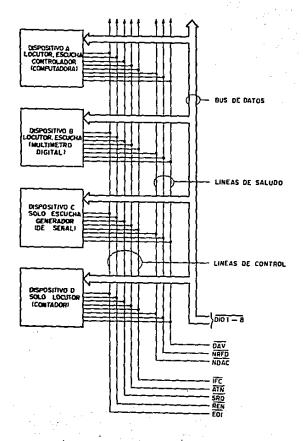

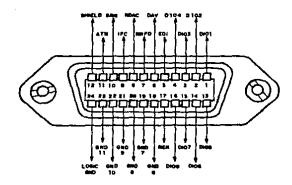

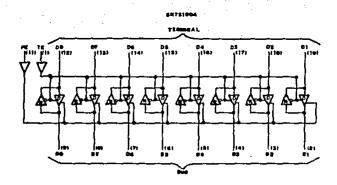

La figura 2.1 (sig. hoja) muestra un esquema general de las lineas que forman parte del bus IEEE-488, también llamado GPIB (General Purpose Interface Bus).

Fig. 2.1.- Diagrama general del bus IEEE-488.

Fig. 2.1.- Diagrama general del bus IEEE-488.

Las lineas de la figura anterior pueden agruparse de acuerdo a la función que realizan dentro del protocolo. Existen tres grupos de lineas dentro del bus IEEE-488

- a) Bus de datos (formado por 8 lineas)

- b) Lineas de control de transferencia (formado por 3 lineas)

- c) Lineas de manejo de interfaz (formado por 5 lineas)

Estas 16 lineas (junto con C lineas adicionales de retorno o tierra) forman el bus mediante el cual se conectarán los instrumentos para integrar un sistema IEEE-488.

El grupo del bus de datos está integrado por las líneas DIO 1-8, siendo estas bidireccionales y utilizadas para transmitir datos o direcciones.

El grupo de control de transferencia está formado por 3 lineas encargadas de realizar el proceso conocido como saludo (que se explicará más adelante). Estas lineas reciben los nombres de DAV, NDAC y NRFD. Estos nombres vienen del mensaje que transfieren los estados (alto o bajo) de estas lineas:

- (1) DAV: DAta Valid (dato válido).

- (2) MRFD: Not Ready For Data (no listo para recibir datos).

- (3) NDAC: Not Data ACcepted (dato no aceptado)

El grupo de administración de interfaz está formado por las siguientes líneas:

- (1) ATN: Attention (Atención)

- (2) IFC: InterFace Clear (Limpiar interfaz)

- (3) REN: Remote ENable (Activa operación remota)

- (4) SRO: Service ReQuest (Solicita servicio)

- (5) EOI: End Or Identify (Fin o Identifica)

La linea DAV se activa (estado bajo) por un "parlante" para indicar que la información, presente en las lineas de datos (DIO 1-8) es válida.

La linea NRPD, cuando es activa, indica que no todos los dispositivos del sistema están listos para aceptar información. Cada instrumento, de acuerdo a su capacidad de procesamiento, libera esta línea pero ésta no podrá regresar a su estado alto (falso) hasta que todos los dispositivos la hayan liberado.

La linea NDAC es controlada por los dispositivos que reciben los datos (al igual que NRFD). Se mantiene activa hasta que todos los dispositivos "escuchas" (receptores) hayan capturado la dirección o dato enviado.

La linea ATN es manejada unicamente por el controlador activo durante la secuencia de envio de direcciones o comandos. El controlador a cargo activa esta linea (la pone en estado bajo) para indicar que la información que se encuentra en el bus en ese momento corresponde al protocolo; es decir, se trata de una dirección o una orden dirigida a todos los instrumentos. Cuando ATN regresa al estado alto sólo el "parlante" y el o los "escuchas" que hayan sido seleccionados tomarán parte en el intercambio de datos subsecuente.

La linea IFC es una señal de reestablecimiento activable unicamente por el controlador del sistema y se utiliza para reiniciar la operación de las funciones del sistema de interfaz y es importante asentar que no todos los instrumentos conectables tienen la capacidad de responder al estado activo de IFC (algunos no tienen conexión interna para ella).

La linea REN es activable sólo por el dispositivo controlador del sistema. Cuando es verdadera indica a los instrumentos conectados al bus que atenderán unicamente a los comandos y datos enviados a través del bus. Si esta linea regresa a su estado inactivo, los instrumentos conectados al sistema volverán al

control del panel frontal.

La linea llamada SRQ, cuando está activa (estado bajo), indica que uno o más de los dispositivos conectados al bus requieren atención especial del controlador. Este sería el caso de que un instrumento haya terminado una medición o que haya detectado un error de operación (dependiendo del dispositivo de que se trate).

La linea EOI puede activarse por el controlador activo o por el "parlante" seleccionado previamente. Esta linea se lleva a su estado verdadero (bajo) por un "parlante" durante la transferencia del último dato. Esta operación puede complementarse con el envio de un carácter de fin de transmisión. Esta linea tiene otra función dentro del protocolo: Si se activa al mismo tiempo que se activa la linea ATN, significa el inicio de una secuencia de encuesta en paralelo.

En la figura 2.1 aparece un sistema tipico que está conectado mediante el bus IEEE-488. En esta figura se puede observar, además de las líneas de conexión, ejemplos de instrumentos conectables al sistema. En la figura aparecen cuatro tipos de instrumentos; instrumentos capaces de hablar, escuchar y controlar (por ejemplo una computadora); instrumentos capaces sólo de hablar y escuchar (por ejemplo un osciloscopio muestreador); instrumentos capaces sólo de escuchar (por ejemplo un generador de funciones) e instrumentos capaces sólo de hablar (contador de frecuencia). Aquí es conveniente hacer notar que un sistema que funcione de acuerdo al protocolo mencionado puede contar con más de un dispositivo con la capacidad de controlar aunque solo uno de ellos podrá estar activo en un momento determinado.

#### 11.1.2 TRANSFERENCIA DE DATOS EN EL BUS IEEE-488.

El comité encargado de la normalización del protocolo estableció que la transferencia de datos se haría siguiendo dos directrices:

- a) Comunicación de bits en paralelo

- b) Comunicación de bytes en serie.

El bus funciona en base al envio de dos tipos principales de mensajes: Mensajes unilínea (transferidos por la acción de una sola linea del bus) y mensajes multilínea (transferidos por la acción de dos o másilineas del bus).

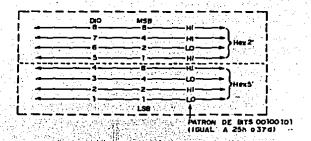

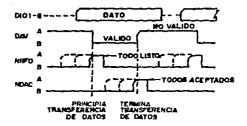

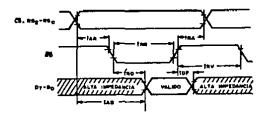

En la figura 2.2 se representa el envio del número 25H (H-hexadecimal). En la figura se ven las lineas de datos llevando los digitos binarios que corresponden a este número hexadecimal.

Fig. 2.2.- Transferencia de bits en paralelo.

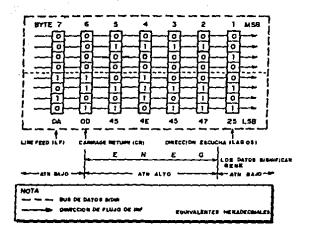

Aqui resalta una de las principales distinciones de la comunicación de datos en este protocolo. A diferencia de la representación "normal", el "1" lógico se representa por un nivel bajo y el "0" lógico se representa por un nivel alto. Los niveles usados en esta transferencia son compatibles con los niveles utilizados por los circuitos TTL (lógica transistor-transistor). La figura 2.3 representa la característica de transferencia de bytes en serie. En ella se representa el envío de la palabra GENE utilizando el codigo ASCII (American Standard Code for Information Interchange) para la representación de cada uno de los carácteres.

Fig. 2.3.~ Transferencia de bytes en serie

La transferencia de datos en el protocolo IEEE-488 puede conceptualizarse como un enlace entre un "parlante" y al menos un "escucha". Esto se representa en la siguiente figura.

Pig. 2.4.- Esquema básico de comunicación en el bus.

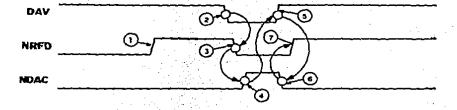

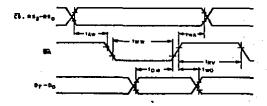

La comunicación de datos en el bus se realiza mediante un proceso de validación y aceptación de cada byte transferido. Este proceso se conoce como "saludo" (aunque es más familiar el nombre en inglés de "handshaking"). Para la realización del "saludo" se utilizan tres lineas dependientes entre si. Estas son las lineas del grupo de control de transferencia: DAV, NDAC y NRFD. Para llevar a cabo la transferencia del dato, el "parlante" deberá indicar cuando es válida la información presente en el bus de datos. A su vez el "escucha" debe informar al "parlante" que ha aceptado la información. La figura 2.5 muestra un diagrama de tiempos simplificado del "saludo" mostrando la interacción entre las tres señales que forman el grupo de control de transferencia. La linea DAV es manejada por el dispositivo "parlante" mientras que las lineas NDAC y NRFD son activadas por el o los dispositivos "escuchas". El "escucha" usa NRPD para indicar que está listo para recibir datos y NDAC indica que el dato enviado ha sido recibido.

Fig. 2.5.- Diagrama de tiempos del proceso de "saludo"

Asumiendo que se ha verificado la presencia del instrumento y se enviaron direcciones de forma tal que se ha elegido un "parlante" para enviar un dato y un "escucha" para recibirlo, la transferencia de datos consta de las siguientes etapas (referidas a la figura 2.5):

(1) El "escucha" levanta la linea NRFD indicando así que está listo para recibir datos (hay que recordar que la linea se llama NO LISTO PARA RECIBIR DATOS y es activa en nivel bajo). En este momento el "parlante" coloca el dato en las lineas Dio 1-8.

- (2) Después de permitir, un tiempo para que las lineas se estabilicen, el "parlante" pone en bajo la linea DAV indicando que el dato presente en las lineas de datos es válido.

- (3) Despues de detectar la linea DAV en bajo, el "escucha" activa la linea NRPD para indicar que no puede recibir más datos inmediatamente.

- (4) Despues de alimentar el dato a su memoria interna, el "escucha" levanta la linea NDAC para indicar que ha aceptado el dato que le fue enviado.

- (5) El "parlante", al reconocer que se ha aceptado el dato que envió, levanta DAV para anunciar que los datos presentes en el bus ya no son válidos.

- (6) Cuando el "escucha" detecta DAV en alto, baja la linea NDAC, reconociendo que se está cambiando la información presente en el bus.

- (7) El "escucha" levanta la linea NRPD indicando que está listo para recibir el siguiente dato.

Esta es toda la secuencia. El "escucha" está listo para recibir el siguiente dato y las líneas de control se encuentran como al principio del proceso. Todo el funcionamiento del bus IEEE-488 se basa en la secuencia detallada anteriormente. Es muy importante notar que la naturaleza asincrona de las señales permite

tomar en cuenta los retrasos debidos a la propagación en las lineas y el tiempo de procesamiento tanto del "escucha" como del "parlante".

En el protocolo existen dos formas de transmitir un mensaje. Estas dos formas se conocen como transferencia activa y transferencia pasiva. Resumiendo, transferencia activa significa que una linea o grupo de lineas adopte un nivel bajo para transmitir un mensaje. La transferencia pasiva significa que una linea o grupo de lineas adopte el nivel alto para transmitir el mensaje. Este esquema se diseñó con el propósito de resolver conflictos entre dispositivos que envien mensajes opuestos. El bus está diseñado electricamente de tal manera que en todo conflicto entre valores opuestos del mensaje, uno de ellos se transferirá activamente y el otro lo hará pasivamente, predominando en todo caso el mensaje activo. Esto es lo que sucede en el caso de varios instrumentos conectados dentro de un sistema IEEE-488. Cuando uno de ellos envía al "parlante" el mensajo RFD (listo para recibir datos) verdadero (transferencia pasiva) y otro envia el mensale RFD falso (transferencia activa), el mensaje dominante, y el que el "parlante" detecta, es el mensaje RFD falso el cual se trans irió activamente. Algo semejante ocurre con el mensaje DAC (dato aceptado). Esta estructura de envio de mensajes, junto con la naturaleza asincrona del bus, permite que el protocolo pueda acomodar tanto dispositivos lentos como rápidos. La figura 2.6 muestra detalladamente la interacción de estas lineas.

Fig. 2.6.- NRFD y NDAC con respecto a DAV.

Como se observa en la figura anterior la velocidad de la transferencia de datos está determinada por la velocidad del instrumento más lento que interviene en ese intercambio. En la figura las líneas de puntos representan las líneas de control de transferencia a medida que son liberadas por cada uno de los instrumentos de acuerdo a la capacidad de cada uno. El controlador puede pasar a la siguiente fase unicamente cuando todos los instrumentos hayan liberado la línea.

Dentro del protocolo los mensajes se dividen en mensajes remotos y mensajes locales. Los mensajes locales son aquellos que se transfieren entre las funciones del dispositivo y las funciones de la interfaz. Los mensajes remotos son aquellos transferidos entre las funciones de la interfaz y pueden ser mensajes propios de la interfaz o mensajes específicos de los instrumentos.

Las funciones del dispositivo son aquellas capacidades no contempladas por el protocolo y que son dependientes de la aplicación (por ejemplo, alcance de un multimetro, precisión, tipo de corriente que se mide, etc.)

Las funciones de la interfaz son aquellas contenidas en el protocolo y que son independientes de la aplicación. Por ejemplo el envio de un dato, la recepción de un dato, la generación de interrupciones, etc.

Los mensajes remotos multilinea se codifican usando, cuando más, las 8 líneas de datos. Además de esto la línea ATN deberá estar activa, lo que los distingue como mensajes remotos (entre funciones de interfaz). El uso de las 8 líneas permite un máximo de 256 (28) combinaciones. Primeramente hay que mencionar que la mayoría de estos mensajes no usa el octavo bit (bit más significativo).

En el apéndice 2 se reproduce la tabla 38 de la norma, llamada codificación de mensajes remotos. En ella aparecen los estados que deberán asumir las 16 lineas del bus para transmitir un cierto mensaje. Estudiando esta tabla notamos en la columna denominada "Type" (tipo) los dos tipos de mensajes mencionados anteriormente: unilinea (U) y multilinea (M). En la columna denominada "Class" (clase) aparecen las varias categorías de mensajes presentes en el protocolo. Estas son:

AC - comando direccionado

AD - dirección

UC = comando universal

DD - dependiente del dispositivo

HS = "saludo"

SE = secundario

ST = estado

Así pues, en esta tabla aparecen mensajes unilínea y mensajes multilínea. No es posible estudiar la codificación de los mensajes dependientes de dispositivos (DD) ya que no existe un caso general aplicable a todos los instrumentos pues dependen de las funciones del dispositivo en cuestión (características de programación, formato de envío de datos, etc.)

Los mensajes remotos multilinea se utilizan para realizar la secuencia de operación de las funciones de la interfaz contenidas en los varios dispositivos de un sistema. Estos pueden ser:

- Comandos universales (dirigidos a todos los dispositivos).

- Comandos dirigidos o direccionados (a todos los dispositivos seleccionados para escuchar).

- Direcciones (a todos los dispositivos).

- Direcciones o comandos secundarios (a todos los dispositivos habilitados por una dirección o comando primario).

Considerando la utilización de 7 bits, se usa un cierto arreglo de los 2 bits más significativos para distinguir que tipo de comando se encuentra en el bus. De esta manera se tendrán los siguientes formatos para la codificación de mensajes remotos:

| Lineas de datos<br>DIO |     |    |   |   | 203 | Significado |                                   |   |  |  |  |  |  |

|------------------------|-----|----|---|---|-----|-------------|-----------------------------------|---|--|--|--|--|--|

| 8                      | • 7 |    |   | 4 | 3   | ,2          |                                   | ٠ |  |  |  |  |  |

| N                      | 0   | 0  | 0 | C | C   | C           | C Comando dirigido o direccionado |   |  |  |  |  |  |

| И                      | O.  | 0  | 1 | C | C   | C           | C Comando universal               |   |  |  |  |  |  |

| N                      | 0   | 1  | A | Å | A   | A           | A Dirección de "escucha"          |   |  |  |  |  |  |

| N                      | 1   | ٥, | ٨ | A | , λ | A           | A Dirección de "parlante"         |   |  |  |  |  |  |

| N                      | 1   | 1  | S | 5 | s   | S           | S Direction secundaria            |   |  |  |  |  |  |

Si se agrupan los bits de un cierto comando para formar los equivalentes hexadecimales y se asume que el bit 8 se envia como 0 (estado alto o pasivo), entonces todos los comandos direccionados tienen como dígito hexadecimal más significativo al 0 mientras que los comandos universales tienen al 1 como dígito hexadecimal más significativo. Así, el comando SDC (selective device clear), el cual indica a un dispositivo en especial que debe regresar a su configuración inicial, se codifica como:

B 7 6 5 4 3 2 1 X 0 0 0 0 1 0 0

Dado que el bit 8 generalmente se envia como 0, entonces este código correponde al número hexadecimal 04.

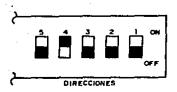

#### II.1.3 DIRECCIONAMIENTO EN EL BUS.

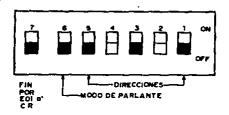

A fin de clarificar la codificación de direcciones de "escuchas" y "parlantes", es necesario detallar una de las características de las funciones de la interfaz en un dispositivo real. Una de las funciones que no pueden realizarse remotamente en un sistema IEEE-488 es la asignación de las direcciones de los dispositivos. Es por esto que debe usarse un método local (y manual) de realizar esta asignación. Para esto se usa un grupo de interruptores en el instrumento. En la figura 2.7 se muestra un grupo de estos interruptores junto con la nomenclatura normalmente utilizada para cada uno de ellos.

Fig. 2.7.- Interruptores para direcciones

La configuración mostrada es el caso más general y por lo tanto el más ilustrativo. Los 5 interruptores colocados a la derecha se usan para seleccionar la dirección del dispositivo. Dado que se tienen 2 posiciones para cada interruptor y 5 interruptores, se puede tener cualquiera de 32 (25) opciones lo

que define un máximo de 32 direcciones en el procesador central del instrumento se encarga de leer estos interruptores, normalmente hale momento de encenderlo, y esta dirección será la utilizada en las transacciones con la interfaz. El siquiente interruptor hacia la izquierda se denomina EOI y con este se indica al procesador central del instrumento cual será el modo de señalar el fin de transmisión de un bloque de datos. Las dos opciones son utilizar el caracter LP (linefeed) cuyo código es OAH o la activación de la linea EOI. Los dos interruptores colocados a la izquierda del anterior determinan el modo operación del dispositivo cuando sea controlado remotamente. segundo interruptor de izquierda a derecha, cuando está activo (hacía arriba) ordena al procesador que opere en modo "sólo 'parlante'", mientras que el interruptor de la extrema izquierda habilita el modo de operación de "solo éscucha". Supóngase que se colocan los interruptores en la posición ilustrada a continuación:

Pig. 2.8.- Interruptores de instrumento 8.

Esta configuración corresponderá a la dirección 01000B u 8 decimal. El formato para los mensajes presentado anteriormente deberá realizar la transferencia de esta dirección así como distinguir entre direcciones de "escucha" y de "parlante". De acuerdo a la tabla de codificación de mensajes, la dirección de "escucha" tiene el siguiente formato:

### N O 1 A A A A A,

donde AAAAA es la dirección del dispositivo. Si se sustituye AAAAA por 01000, se obtendrá el siguiente byte:

N 0 1 0 1 0 0 0.

Este será el byte enviado por el controledor, con la línea ATN activa, para habilitar al instrumento 8 como "escucha". Si el bit 8 se envía como 0, este byte corresponde al número hexadecimal 28. Si se deseara habilitar a este mismo dispositivo como "parlante", se sustituye el valor 01000 en el formato de la dirección de "escucha" resultando:

N 1 0 0 1 0 0 0,

lo que será el byte enviado para habilitar al dispositivo 8 como "parlante". Dado que el octavo bit generalmente no se envia, esta dirección corresponderá al numero 48K. Esta es la forma en que el dispositivo distingue entre el "permiso para hablar" (dirección de "parlante") y la "orden de escuchar" (dirección de "escucha"). Cada una de ellas se codifica de manera diferente.

Aún cuando los 5 bits de selección de dirección permiten 32 combinaciones, una de ellas no deberá usarse: Esta combinación corresponde al número 3FH para los intrumentos "escucha", se le llama UNL y se envía para devolver a los dispositivos "escuchas" a su estado inactivo. En el caso de los dispositivos "parlantes" está combinación es 5FH, se llama UNT y se utiliza para devolver a los dispositivos "parlantes" a , su estado inactivo (en el que liberan las líneas de datos.

Para un cierto dispositivo; el código correspondiente a su dirección de "escucha"; se denomina MLA (my listen address) mientras que el código correspondiente a un dispositivo "parlante" se llama MTA (my talk address).

HER TO BUT SURSE TO THE TANK OF

Además de estas direcciones de un byte, lamadas direcciones primarias, existen direcciones codificadas mempleando 2 bytes liamadas direcciones secundarias. A los dispositivos que cuentan con capacidad de reconocer estas direcciones se les liama dispositivos extendidos (TE en el caso de "parlantes" y LE en el caso de escuchas"). Debe mencionarse que los instrumentos con

direcciones secundarias son poco comunes debido sobre todo a que el uso de microprocesadores facilita la programación a partir de direcciones primarias unicamente.

Un dispositivo que realiza funciones tanto de "escucha" como de "parlante" puede tener la misma combinación de los 5 bits menos significativos de su dirección de "escucha" y de su dirección de "parlante". lo que permite usar un solo grupo de interruptores para configurar, simultaneamente, las direcciónes de "escucha" y "parlante".

Una manera sencilla de encontrar el byte que transferirse como dirección de un cierto dispositivo es usar la tabla ASCII modificada que se reproduce en el apéndice 2. En esta aparecen los códigos correspondientes a las direcciones de "escuchas", "parlantes" y direcciones secundarias así como mensajes remotos multilinea. Para saber el código correspondiente a una cierta dirección, por ejemplo el byte para la dirección de "escucha" 16, se localiza este número en el grupo correspondiente. Este es LAG (listen address group). Los nombres de los grupos se encuentran en el extremo inferior de la tabla. En la parte superior de la columna donde se encuentra este número aparece el (el signo \$ indica que se trata de un número **53** hexadecimal) y es el dígito más significativo del byte correspondiente (es decir los 4 bits más significativos). A la extrema izquierda de 16 aparece el símbolo \$0 correspondiente al dígito menos significativo del byte. Por lo tanto, el código de la

dirección de "escucha" 16 es 30H.

Un comando remoto universal cualquiera se localiza en el grupo

UCG (universal command group); por ejemplo el comando SPE

(habilitación de encuesta en serie). En el extremo superior de

este comando se encuentra \$1 correspondiente al digito más

significativo mientras que a la extrema izquierda se encuentra \$8

que el digito menos significativo. Por lo tante SPE se codifica

como 18H.

Es importante saber el origen de la codificación de estos mensajes y direcciones dado que en el capítulo 4 se usarán estos códigos en la escritura de algunas rutinas de demostración para la tarjeta controladora.

El bus IEEE-488 sólo específica las características eléctricas de los mensajes a transmitir a través del bus y los mensajes propios de la interfaz; sin embargo no dicta ninguna regla en cuanto al formato de los datos dependientes de los dispositivos. El formato más utilizado, aunque no es aceptado unánimemente, consta de las siguientes características:

- (1) Toda la información se transfiere usando el código ASCII.

- (2) La información se transmite de izquierda a derecha; por ejemplo la palabra DATO se transfiere como:

(3) Todas las secuencias de transmisión de datos concluyen con el número ODH (símbolo ASCII llamado "line feed") en vez de utilizar la linea EOI.

#### II.1.4 CARACTERISTICAS ELECTRICAS.

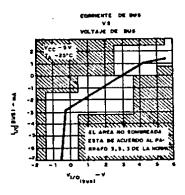

La normalización del protocolo incluye, también, las principales características eléctricas que existirán dentro de un sistema IEEE-488. El documento específica que estas características eléctricas están basadas en la tecnología TTL aunque el uso de ésta no es forzoso.

El protocolo funcions en base al envio de mensajes que se codifican por medio de los voltajes presentes en las lineas. Esta codificación ocurre mediante el empleo de "lógica negada". La relación entre estados lógicos y voltajes en la linea se muestra en la tabla 2.1

Tabla 2.1

| Est | ado 1 | ógico |  | N      | ivel | elécti | ico |

|-----|-------|-------|--|--------|------|--------|-----|

|     | 0     |       |  |        | 2    | .o v.  |     |

|     | . 1   | 227,  |  | Battle |      | .8 V.  |     |

Los niveles descritos en la tabla 2.1 están referidos a tierra lógica.

De acuerdo a la norma se pueden utilizar dos tipos de excitadores en las lineas de señal del bus: De colector abierto y de tres estados. Se específica que se deberá utilizar excitadores de colector abierto para las lineas SRQ, NRFD y NDAC. Para las lineas DIO 1-8, DAV, IFC, ATN, REN y EOI se podrán utilizar

excitadores de tres estados o de colector abierto de acuerdo a la velocidad de transferencia requerida, con excepción de la respuesta a una encuesta en paralelo en cuyo caso se deberá alimentar las líneas de datos mediante excitadores de colector abierto. Las características eléctricas de estos transceptores se resumen en las secciones 3.3 y 3.4 de la norma IEEE-488.

La manera de lograr que la tarjeta cumpla con estas Características eléctricas se abordará en el capitulo 3.

## II.1.5 CARACTERISTICAS MECANICAS.

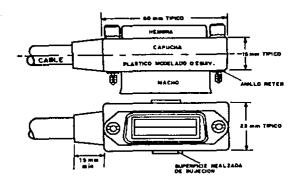

El protocolo cuenta también con una serie de requisitos mecánicos a los que se deberá ajustar cualquier dispositivo que se conecte al bus. Entre estas se específica el tipo de conector utilizado, la asignación de contactos para las líneas del bus, las dimensiones del cable, la construcción de éste, etc. La figura 2.9 muestra la asignación de contactos en el conector así como una aproximación de la forma que tiene este conector.

Fig. 2.9.- Asignación de lineas IEEE-488

El documento especifica de manera detallada las consideraciones eléctricas que deberán influir en la elección del conector así como las especificaciones de tipo mecánico que deberán

cumplir estos mismos.

Las principales características mecánicas son:

- Número de contactos: 24

- Superficie de los contactos: auto-limpiable

- Durabilidad: mayor o iqual a 1000 inserciones.

La figura 2.10 muestra un extremo del cable que se utilizará para realizar la conexión entre los dispositivos conectados al bus. La parte superior de la figura muestra una de las principales características de estos cables: Cada una de las terminaciones permite la conexión de más de un instrumento pues por un lado el conector es hembra y por el otro lado es macho, permitiendo así la conexión en cadena (daisy-chain) para formar un sistema IEEE-488.

Fig. 2.10.- Conector IEEE-488 tipico.

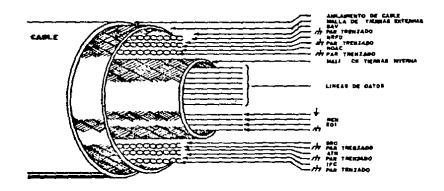

El cable de interconexión del bus IBEE-488 tiene también características especiales que permiten operar en ambiente de ruido relativamente alto. Se especifica que el cable deberá tener por lo menos 24 conductores de los cuales 16 deberán ser líneas de señal y el resto serán retornos a tierra lógica y conexión entre los chasises de los instrumentos integrantes del sistema.

Se establece que la capacitancia máxima (medida a 1 kHz) entre cualquier línea de señal y todas las demás líneas conectadas a tierra deberá ser de 150 pf. por metro.

La figura 2.11 muestra un corte del cable de conexión típico en el

que se puede apreciar la distribución de las lineas.

Fig. 2.11.- Cable para bus IEEE-488

Entre las principales características de construcción del cable destaca la separación en dos grupos, cada uno contenido por una malla de protección. En la periferia de este grupo central aparecen las líneas de control de transferencia y de manejo de interfaz, cada una trenzada con su retorno individual a tierra. Todo este grupo está cubierto por otra malla la que a su vez está protegida por el aislamiento externo. Opcionalmente las líneas de datos podrían estar trenzadas alrededor de la conexión de tierra física y la tierra lógica junto con las líneas REN y EOI. El

objetivo de esta construcción tan especial es el de minimizar los efectos de interferencia (crosstalk) entre las varias lineas de señal, disminuir la susceptibilidad de estas líneas al ruido externo y evitar la transmisión de las señales de la interfaz al Irônicamente, la construcción tan especial del ambiente externo.: cable de conexión del bus IEEE-488 es una de las razones por las qué el bus no ha logrado la aceptación total de los fabricantes de instrumentos y esto ha propiciando la aparición de otros buses de control de instrumentos; esto se debe a que el alto precio que alcanza el cable (superior a los 100 dólares) es desproporcionado con el costo de la circuiteria del instrumento de medición por lo que algunos fabricantes han decidido adoptar otro tipo de conexiones (que funcionen de acuerdo a otro tipo de protocolos) que se puedan integrar con costos menores, usando, por ejemplo, el cable plano.

raginatalogum kemingin hadda kang megapagang kaop megimendiga baharan menghilipan bahasan, mengam megabungan me

## II.1.6 LA NORMA IEEE-488 CON RESPECTO A LA NORMA IEC-625.

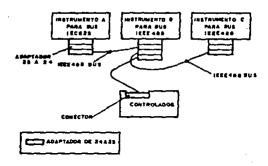

Existe una versión internacional del protocolo de control de instrumentos programables. Esta es la norma 625-1 de la Comisión Electro-técnica Internacional (IEC)". Ambas especificaciones son en la práctica idénticas en sus especificaciones eléctricas y funcionales. En la versión internacional, IEC-625-1, existen 25 señales que están asignadas de manera diferente, con excepción de las primeras 4 líneas (DIO1-4).

La unica linea que no existe en ambos conectores es la tierra de la linea 12 de la norma IEC-625 (ATN), lo que es consecuencia del uso de 25 lineas en vez de 24 (IEEE). La figura 2.12 muestra la representación de un sistema IEEE-488 en el que se incluye un instrumento programable cuya conexión se ajusta a la norma IEC-625. Normalmente estos instrumentos cuentan con conectores "macho" de 25 patas montados en la parte trasera para realizar la conexión al bus. En la figura se representa (sombreado) el adaptador que permite esta conexión entre IEC-625 y IEEE-488.

Fig. 2.12.-Compatibilidad entre IEC-625 e IEEE-488.

## II.2 CONCEPTUALIZACION DE UNA TARJETA DE INTERFAZ

COMPATIBLE CON EL BUS IEEE-488.

La tarjeta que se diseñó en este trabajo puede concebirse como un "puente" entre dos ambientes de trabajo, cada uno de funcionamiento diferente. Por un lado se tiene una computadora que se comunica con el exterior mediante el envio de datos ya sea en serie o en paralelo. Esta conexión con la computadora se abordará posteriormente. Por otro lado tenemos un ambiente de aplicaciones muy específicas y que funciona en base a reglas ajenas a cualquier tipo de computadora.

Como se vió en la parte anterior, el bus IEEE-488 funciona en base a mensajes tanto específicos de la interfaz como dependientes del dispositivo. Una tarjeta que permita la conexión de una computadora a un sistema de este tipo deberá encargarse de tomar los mensajes enviados a la computadora (el cual contará con direcciones de "escucha" y "parlante") y pasarlos al procesador central. También deberá tomar los mensajes enviados por el procesador central de la computadora y enviarlos al bus cumpliendo el protocolo establecido para ello. Más aún, si lo que se busca es diseñar un controlador IEEE-488 (explicado en la parte anterior), la tarjeta deberá responder a las peticiones de servicio, leer palabras de estado generadas por los instrumentos, asignar dispositivos "parlantes" y "escuchas", (pudiendo direccionarse a si mísmo para ejecutar alguna de estas funciones) y realizar encuestas

en paralelo, entre otras cosas.

## 11.3 DEFINICION DE LAS FUNCIONES A REALIZAR POR LA TARJETA.

Por lo tanto desde el punto de vista de la computadora, la tarjeta representará uno o más puertos de entrada/salida o una o más localidades de memoria; esto dependerá de la configuración y esquema de decodificación utilizados.

Desde el punto de vista del bus, las funciones a realizar por la tarjeta son un poco más complejas y requieren, por lo tanto, de una mayor explicación.

Como se mencionó anteriormente la interfaz funciona en base a la transferencia de mensajes que podrán ser unilines o multilinea (estos fueron definidos en la sección 2.2). Cada mensaje se enviará falso o verdadero dependiendo del estado en que se encuentre la función de la interfaz.

El dispositivo incurre en estos estados de acuerdo a las funciones del bus que contenga. En el documento se han definido tanto las funciones como los estados que pueden ocurrir dentro de ellas.

Cada una de las funciones de interfaz recibe un nombre especial (y que al principio podrá parecer un poco ambiguo). Además, el nombre de la interfaz tendrá una abreviatura (el documento de la normalización llama a esta abreviatura símbolo).

La abreviatura es la forma más común de designar las funciones de la interfaz. La sección 2 del documento IEEE-488 define las funciones de la interfaz discutiendo las capacidades de cada una de ellas.

El documento describe cada una de las funciones utilizando diagramas de estado que representan en forma detallada la secuencia de ejecución de cada una de estas funciones. Como se describió en el capitulo 1, cada una de las funciones se conceptúa como una maquina de estados. La realización física de esta maquina se dificulta a medida que crece el número de estados dentro de una función, especialmente si en algunos de los estados se envian mensajes a la interfaz (definidos estos en las tablas de salida de mensajes). A fin de disminuir las dificultades en la construcción de estas funciones, y entendiendo que no es necesario contar con todas las funciones en un dispositivo, el comité estableció un subconjuntos de las funciones. Cada uno de grupo đe subconjuntos se nombra por la letra de la función a que pertenece y un número que define la capacidad de ejecución con respecto a la operación completa de la función. Un caso especial (y el de mayor interes para este trabajo) es de la función Controlador (C).

Para un controlador se escoge una o más de las capacidades parciales C1 a C4 en combinación con uno, y sólo uno, de los subconjuntos C5 a C28. La notación típica para describir un controlador consiste de la letra C seguida de uno o más de los números que indican los subconjuntos disponibles (por ejemplo C1,

## 2, 3, 4, 8).

La complejidad del funcionamiento de la interfaz cuando se requiere contar con varias de las funciones de la misma dió origen a dos tendencias seguidas por los fabricantes de equipo adaptable al bus:

- a) Muchos fabricantes decidieron incorporar en sus productos una compatibilidad parcial ignorando algunas de las líneas de manejo de interfaz, utilizando principalmente las líneas de datos y las tres líneas de control de transferencia, ignorando la realización de las funciones más complejas como la encuesta en paralelo.

- b) La mayoría de los fabricantes comenzó a usar en sus diseños de acoplamientos al bus los circuitos integrados que aparecieron un poco despues de la revisión 1978 de la norma, los cuales cumplen con la mayoría de las funciones del protocolo, simplificando grandemente la tarea del diseñador de instrumentos programables.

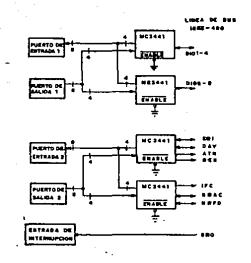

El segundo enfoque usado es la realización de la interfaz por medio de programación. Para esto se elabora un grupo de subrutinas que se encarguen de la generación de mensajes, estado de las señales, reconocimiento de errores, etc. Estas rutinas serían ejecutadas por un microprocesador. La figura 2.13 muestra un

esquema de circuito de este tipo.

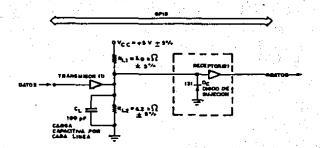

Pig. 2.13.- Conexión IEEE-488 usando up.

Los puertos señalados en la figura pueden ser simples circuitos "cerrojo" (latches) del tipo 74373 o 74374 (por citar el tipo más común) o puertos programables del tipo 6522, 8255 o similares. El circuito anterior no incluye la lógica de decodificación necesaria para lograr la conexión de estos puertos de entrada/salida, pero si se incluyen los circuitos transceptores necesarios para cumplir/las especificaciones de tipo eléctrico señalados por la norma. Estos son necesarios puesto que la mayoria de puertos de entrada/salida del microprocesador no tienen la capacidad de corriente necesaria.

Estos pueden ser del tipo MC3446, SN75160 o cualquier otro tipo similar.

a sarah mandah darih indi sarah bir adap darip di kasagkar da sa dikasah bandah dan bandah bandah parah jarah da isarah

Sin embargo, a pesar de los ventajoso que resulta la flexibilidad obtenida, la realización de las funciones de la interfaz puede resultar en un programa demasiado grande y cuya ejecución consuma un tiempo excesivo del microprocesador lo que ocasionaría que se requiriera de otro procesador (más circuitos, mayor costo, mayor consumo de energía) para realizar las función de control central del dispositivo de medición.

A últimas fechas se han desarrollado un grupo de circuitos de alta escala de integración que incorporan la mayoría de las funciones del protocolo IEEE-488 incluyendo los cambios específicados por la revisión de 1978, lo que ha simplificado grandemente la tarea de acopiar un instrumento al bus.

El uso de estos circuitos integrados resulta en un acoplamiento al bus que es una combinación de circuitería con programación que resulta eficiente en estos dos aspectos.

A la fecha existen varios circuitos que realizan estas funciones, cada uno de ellos con ventajas y desventajas que determinarán la selección de ellos por parte del diseñador. La referencia [9] describe algunos de los problemas que han tenido varios diseñadores en el diseño de interfaces al bus usando algunos de los circuitos disponibles.

El uso de estos circuitos facilita enormemente el diseño del acoplamiento al bus reduciendolo al diseño de subrutinas que se encarguen de verificar el estado del bus por medio de estos circuitos y tomen decisiones en base a esto.

El uso de estos circuitos integrados simplificará el envío.

El controlador sólo tiene que escribir el dato a un registro específico del controlador. Despues de esto, el circuito, en forma totalmente independiente del procesador central, revisará el estado del bus esperando a que los "escuchas" estén listos para aceptar el dato, enviará el dato y usperará hasta que los "escuchas" lo hayan aceptado.

En general estos circuitos funcionan de manera muy similar por lo que son bastante parecidos en sus configuraciones y conexiones. La mayoria de ellos tienen la característica de inversión de nivel. Con esto se libera al procesador central de la tarea de realizar la conversión necesaria (recuerdese que en el bus las señales se manejan como activo bajo). Tienen además una serie de terminales para la conexión al bus IEEE-488. Estas incluyen las lineas de datos, las lineas de control de transferencia y las lineas de manejo de interfaz. Todos cuentan con un bus de datos de 8 bits realizar la conexión al procesador central, líneas de habilitación de lectura y escritura (/RD y /WR), una o más lineas de habilitación general del circuito, una línea para el reestablecimiento (RESET) y una o dos entradas para un circuito de sincronización de algun tipo. Además, estos circuitos normalmente

tienen una línea conectable a la lógica de generación de interrupciones del procesador. Por medio de esta se puede indicar al procesador central cuando exista alguna condición en el bus que requiera atención especial del procesador (por ejemplo la activación de la señal SRQ). Además pueden contener lógica de arbitraje de transferencias directas a memoria. Para el procesador central estos circuitos se comportan como un grupo de registros contiguos de los cuales algunos son sólo de escritura y otros sólo de escritura.

El circuito utilizado como parte central de la tarjeta de acoplamiento al bus es capaz de realizar los siguientes subconjuntos de funciones de interfaz:

- SH1 (capacidad completa)

- AH1 (capacidad completa)

- L3 (Escucha básico con dirección de un byte, operación en modo de "solo escucha" y deshabilitación de direccionamiento cuando se recibe MTA)

- LE3 ("escucha" extendido básico con dirección de dos bytes, operación de "solo escucha" y deshabilitación de direccionamiento cuando se recibe MTA o MSA y se ha recibido la primera parte de la dirección).

- T5 ("parlante" básico con dirección de un byte, operación de encuesta en serie, operación en modo de "sólo parlante" y deshabilitación de dirección cuando se recibe MLA).

- TES ("parlante" básico extendido con dirección de dos bytes, operación de encuesta en serie, operación en modo de "solo parlante" y deshabilitación de direción cuando se recibe MSA y se ha recibido la primera parte de la dirección).

- SR1 (capacidad completa)

- RL1 (capacidad completa)

- PP1 o PP2 (configuración remota o local)

- DC1 (capacidad completa)

- DT1 (capacidad completa)

- C1, C2, C1, C4 o C5 (todas las capacidades de controlador).

Al ser este un controlador programable significa que para que se realicen todas las funciones mencionadas arriba será necesario programar al dispositivo en la manera apropiada. Los alcances de este trabajo en este aspecto se discutirán en el capitulo 4.

## II.4 DIAGRAMA A BLOQUES DE LA TARJETA.

Tomando en cuenta las características de los circuitos mencionados y los problemas presentados por algunos de ellos, en este trabajo se decidió utilizar el controlador NEC pPD7210 debido a las consideraciones de espacio, cantidad de circuitería adicional requerida y velocidad. Este controlador integra en un solo encapsulado las funciones de la interfaz necesarias para el diseño de dispositivos "parlantes", "escuchas" y controladores (pudiendo combinarse las tres características en un solo dispositivo).

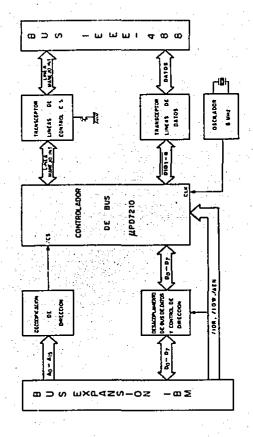

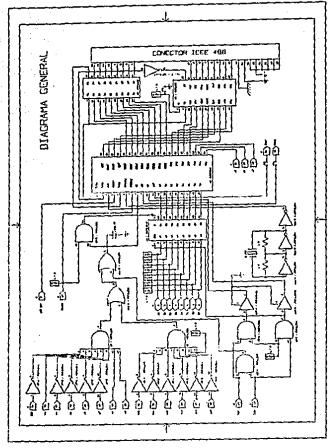

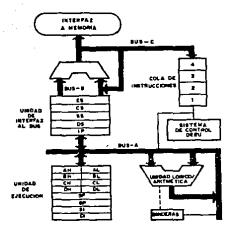

En la figura 2.14 (sig. hoja) se muestra el diagrama a bloques de la tarjeta controladora.

Fig. 2.14.- Diagrama a bloques de la tarjeta.

El elemento fundamental es el pPD7210 señalado como el bloque mayor. Para la activación de éste dentro de un cierto grupo de direcciones se requiere decodificar las líneas de direcciones para obtener a partir de ellas la línea de activación del circuito (llamada genéricamente "chip select"). Esto se realiza en el bloque llamado DECODIFICACION DE DIRECCIONES que tiene como entradas las direcciones originadas en el bus de la computadora y cuya salida es una o más líneas de habilitación. No todas las líneas de dirección pasan por el proceso de decodificación. Hay que recordar que estos circuitos controladores cuentan con varios registros internos y para seleccionar uno de ellos se requerirá de algunas líneas de dirección las cuales, si las especificaciones eléctricas lo permiten, podrán conectarse directamente al circuito.

El bus de datos de la computadora se alimenta al bloque liamado de DESACOPLAMIENTO Y AMPLIFICACION DE CORRIENTE. Este bloque tiene dos funciones: primeramente se encarga de que las líneas de datos de la tarjeta no sobrecarguen al bus de datos de la computadora en caso de que existan muchas compuertas conectadas a éste. Además de esto, sirve para controlar la dirección de los datos ya que estos son bidireccionales.

Las lineas de control del bus de la computadora personal se alimentan al bloque denominado CONTROL DE DIRECCION. De este bloque se obtienen una o más señales que manejan la dirección del flujo de datos en base al estado de las líneas de control del bus del computador. Adicionalmente se obtienen algunas de las líneas de control afectadas unicamente por retrasos necesarios para lograr la conexión adecuada al circulto. Esto se detalla en el capítulo

El bloque denominado OSCILADOR tiene como salida una señal periodica de 6 MHz. Como se mencionó anteriormente, estos circuitos controladores requieren una señal de reloj para regular sus funciones internas y cumplir algunas restricciones de tiempo impuestas por la norma.

La Conexión del controlador al bus no puede hacerse directamente. Se debe tener presente que el PPD7210 es en realidad un microprocesador y por lo tanto no cuenta con la gran capacidad de manejo de corriente para poder conectarse al bus y alimentar el máximo de dispositivos conectables. Es por esto que se requiere de adaptadores (llamados transceptores) que cumplan con las especificaciones eléctricas tan especiales del protocolo IEEE-488. Dado que existen 16 lineas en el bus y que los transceptores manejan 8 líneas cada uno, se deberán utilizar dos de Los dos transceptores utilizados no son iquales entre si: Uno de ellos está diseñado especialmente para manejar el bus de datos (todos los canales de éste son iguales), mientras que el otro maneja en forma independiente cada una de las lineas del bus de control de interfaz. En el capítulo 3 se describe detalladamente el diseño de la tarjeta.

#### CAPITULO III

# DISEÑO DE LA INTERPAZ Y CARACTERISTICAS DE ACOPLAMIENTO AL COMPUTADOR.

## III.1 GENERALIDADES.

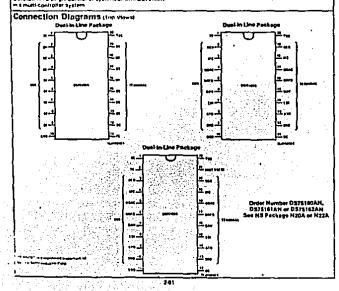

Se decidió utilizar uno de los circuitos especializados como parte central de la tarjeta de conexión al bus IEEE-488. Se trata del pPD7210 fabricado por NEC. Este puede actuar en los tres tipos de dispositivos definidos en la norma: "parlantes", "escuchas" y controladores. La disposición de conexiones de este circuito así como sus principales características eléctricas se detallan en el apéndice 1.

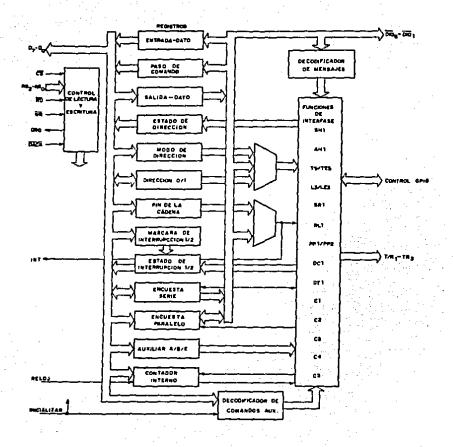

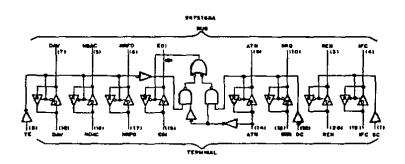

La figura 3.1 (sig., hoja) muestra el diagrama a bloques de este circuito. En este se puede observar la representación de los l6 registros internos de este circuito y la representación de las funciones de la interfaz realizables por el:

Fig. 3.1.- Controlador PPD7210 a bloques.

Las funciones y modos de operación de cada uno de los registros se describirán más adelante. Por ahora es suficiente decir que por medio de éstos se pueden realizar directamente la mayoría de las funciones de la interfaz.

#### III.2 ACOPLANIENTO A LA COMPUTADORA PERSONAL.

## 111.2.1 CARACTERISTICAS DEL CONECTOR DE EXPANSION

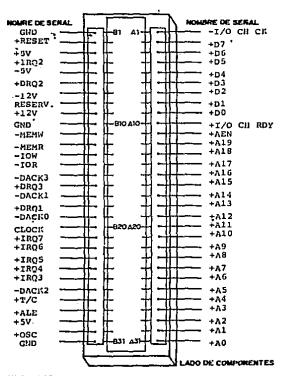

La figura 3.2 muestra el esquema del conector de expansión de la computadora personal IBM. Este conector de expansión es el conjunto de la mayoría de las líneas del microprocesador provistas de la suficiente capacidad de manejo de corriente. Como un antecedente sobre este esquema hay que decir que la computadora personal IBM tiene como su procesador central un microprocesador INTEL 8088 que es una versión del microprocesador 8086 del mismo fabricante.

Las principales características del conector de expansión son:

- 8 lineas de datos

- 20 lineas de dirección

- 6 lineas de petición de interrupción

- 4 canales de Acceso Directo a Memoria (DMA)

- 4 lineas de habilitación de lectura y escritura (memoria y entrada/salida)

- Sefales de control varias (ALE, RESET, CHRDY, CHCHK, AEN)

- 2 señales de reloj (14.318 MHz y 4.77 MHz)

- 8 lineas de alimentación y tierra (para voltajes de +5, -5,

+12 y -12 v.)

CANAL E/S

Pig. 3.2.- Conector de expansión IBM.

Como se puede observar, la conexión a este bus de expansión logra una interacción más directa con el microprocesador. Por medio de esta expansión podremos conectar dispositivos que existan tanto en el espacio de memoria como de entrada/salida del microprocesador, tener acceso a las interrupciones del sistema, líneas de alimentación, etc. Debido a esto se escogió realizar el diseño para ser conoctado a estas ranuras de expansión.

A fin de generar una base "válida" para el diseño se utilizó la figura llamada SYSTEM BOARD DATA FLOW presentada en la referencia [2] y se calcularon los tiempos utilizando las ecuaciones presentadas en la referencia [4]; usando este diagrama a bloques y calculando los retrasos generados por la circuitería adicional conectada al grupo del microprocesador (formado por el microprocesador 8088, el controlador de reloj 8284 y el controlador de bus 8288) fue posible obtener el marco de referencia requerido. El diagrama a bloques en el que se basó este cálculo se representa en la figura 3.3

Fig 3.3.- Diagrama a bloques del conjunto del procesador.

En la figura 3.3 destacan, ademas del procesador funcionando a 5 MHz en modo máximo, los siguientes circuitos adicionales:

- ~ Generador de reloj 8284.

- Controlador de bus 8288 encargado de generar la mayoría de las señales de control.

- Los circuitos denominados LATCH encargados de retener las direcciones una vez que han sido removidas por el microprocesador.

- Los circuitos denominados BUFFER encargados de aumentar la capacidad de corriente para cada una de las señales del microprocesador.

- Los circuitos denominados TRANSCEPTORES que aumentan la capacidad de corriente al mismo tiempo que controlan la dirección del flujo de datos.

La referencia [2] específica que el bus de expansión proporciona la suficiente corriente para alimentar las 5 ranuras de expansión asumiendo 2 cargas TTL por cada ranura.

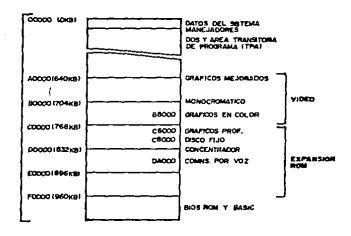

En la parte anterior se mencionó que el circuito encargado de realizar el protocolo utiliza para su operación 16 registros internos accesables mediante tres líneas de dirección. Esto quiere decir que, desde el punto de vista del microprocesador, la tarjeta ocupará, por lo menos, 8 localidades contiguas.

La referencia (21. pagina 1-10, indica las localidades ocupadas por los varios dispositivos conectados o conectables al bus de entrada/salida. La méquina personal IBM, y cualquier otra que proclame un alto grado de compatibilidad (ver capitulo 4), hace una distinción entre los dispositivos de entrada/salida localizados la tarjeta principal (o tarjeta madre) y aquellos que se encuentren acoplados a los conectores de expansión. primeros se asignan direcciones cuyo bit A9 sea 0 mientras que para los segundos asigna direcciones cuyo bit A9 es 1. Esto quiere decir aue no podrán asignarse dispositivos externos a las direcciones comprendidas entre 0000H y GIFFH, sino sólo direcciones entre 0200H v 3FFH (según la Referencia Técnica IBM). En este documento se indica que el espacio localizado entre 0300H y 031FH está destinado a tarjetas cuyas funciones no estén comprendidas dentro de las listadas (se les llama tarjetas prototipo). será el espacio asignado a las direcciones de la tarjeta de acoplamiento al bus IEEE-488.

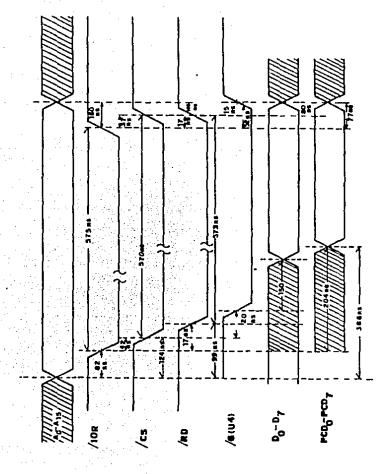

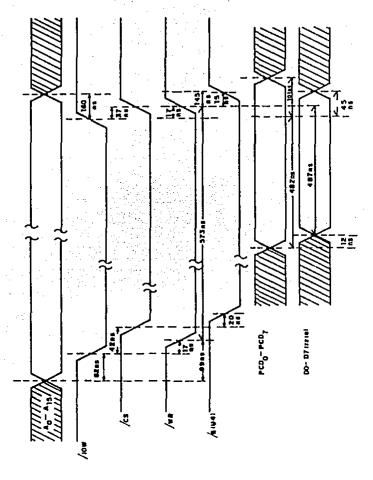

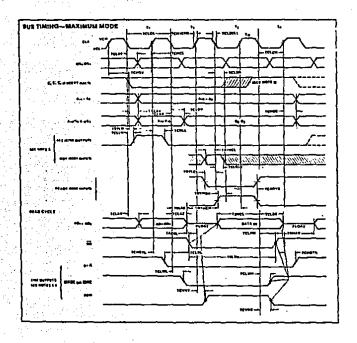

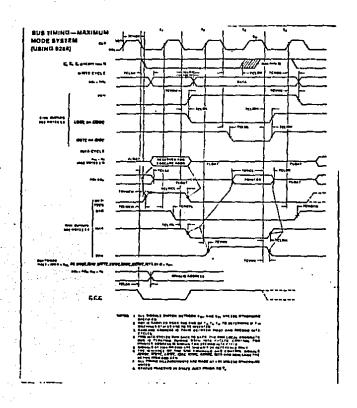

### III.2.2 RELACIONES DE TIEMPO EN EL CONECTOR DE EXPANSION.

Debido a la amplia variedad de maquinas compatibles funcionando a varias velocidades, es necesario establecer un común denominador que permita calcular los tiempos requeridos de tal forma que los valores sean aplicables a la mayor cantidad de máquinas. Para esto se considerará que el bus de expansión es manejado por un microprocesador 8088 funcionando a 5 MHz.

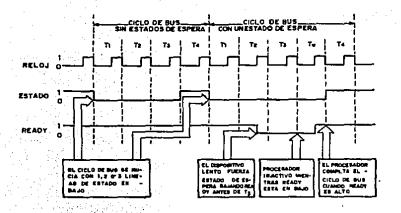

Antes de detallar las características de tiempo del procesador se describirá en forma somera el desarrollo de un ciclo de bus del procesador. El tiempo necesario para transferir una unidad de datos desde o hacia la CPU se llama ciclo de bus. En el 8088 la unidad de datos se llama "byte" y la longitud mínima de un ciclo de bus es de 4 cíclos de reloj (1 ciclo = 200 ns. @ 5 MHz.). Estos ciclos se denominan T1 a T4. Cada ciclo de reloj realiza diferentes actividades. La figura 3.4 representa en forma simplificada el ciclo de bus, tanto sin estados de espera como con un estado de espera.

Fig. 3.4.- Ciclo de bus del 8088 en una IBM-PC

- Durante T1, la CPU emite una petición de transferencia de bus en las lineas de estado junto con una dirección en las lineas de datos/direcciones. Las lineas de estado indican el tipo de accesc (memoria o un puerto de entrada/salida) y si se trata de entrada o salida. La dirección se almacena en un circuito "cerrojo" para que se mantenga durante el resto del ciclo de bus.

- En T2, el procesador quita las direcciones de las patas correspondientes a las lineas de datos y direcciones y en el caso de un ciclo de escritura, coloca los datos de salida en estas mismas lineas. Si se trata de un ciclo de lectura, las lineas se desconectan de la CPU para ser usadas por los

dispositivos de memoria o de entrada/salida pera transmitir los datos. Mientras tanto, los circuitos de decodificación de direcciones conectan las líneas de datos de los dispositivos de memoria o de entrada/salida y los transceptores de datos establecen la dirección de la transferencia (desde o a la CPU).

- Durante T3 el dispositivo de memoria o de entrada/salida realiza la transferencia mientras que la CPU permanece inactiva.

- En T4, último ciclo de reloj, el procesador se desconecta de las líneas de datos y deshabilita todas las señales de control, regresando a su estado inactivo. Para un ciclo de lectura la CPU se reconecta a las líneas de datos para obtener los datos presentes ahí.

Este proceso de 4 pasos representa un ciclo de bus mínimo, sin estados de espera. Nominalmente, el tiempo de transferencia de datos desde o a los dispositivos externos es un ciclo de reloj (200 ns. a 5 MHz) por lo que la mayoría de los dispositivos que se conectan al bus de expansión de la PC son capaces de realizar esta transferencia en un tiempo aproximado de 200 ns.

Si un dispositivo de memoria o de entrada/salida no puede responder con la suficiente velocidad para realizar la transferencia en poco más de un ciclo de reloj, se diseña el circuito para que inserte estados de espera entre T3 y T4. Esto se hace utilizando la línea RDY del procesador. Durante un ciclo de bus, la CPU no entra al estado T4 si RDY no tiene el nivel alto. Cuando se selecciona un

dispositivo lento por la lógica de decodificación de direcciones (durante T2), éste deberá bajar inmediatamente la línea RDY la cual se alimenta al 8088 por medio del controlador de reloj 8284, usado para sincronizar las transiciones en esta línea con los ciclos de reloj. La línea RDY no tiene efecto en T3 sino que a partir del final de éste, el procesador permanecerá inactivo, en decir en estado de espera, por cada ciclo de reloj en que RDY permanezca en bajo. Despues de que ha transcurrido un número determinado de ciclos de reloj, suficientes para completar la transferencia, el dispositivo levanta la línea RDY permitiendo que el procesador avance a T4 para completar el ciclo de bus.

La PC basada en el 8088 se diseñó con cero estados de espera en accesos a memoria y un estado de espera en accesos a entrada/salida. Este estado de espera se inserta sin considerar la velocidad de operación del dispositivo que está siendo direccionado por lo que el ciclo de entrada/salida no podrá completarse en menos de 5 ciclos de reloj (equivalente a 1000 ns. @ 5 MHz.). Debido a la dificultad de conocer la configuración exacta de la circuitería adicional para todas las máquinas existentes, es necesario hacer el cálculo de los tiempos para una frecuencia igual o mayor a 4.77 MHz (existente en la máquina IBM) para obtener una aproximación de los tiempos de interacción de todas las líneas (datos, direcciones y control). Para lograr un cálculo mucho más fidedigno se utilizan los diagramas de una computadora cuyo bus de expansión es compatible con el de la IBM-PC. Estos diagramas se publicaron en la referencia [6]. En el apéndice l aparece la hoja de datos del

microprocesador 8088. Los tiempos pertinentes a la frecuencia de operación de 5 MHz aparecen en la columna denominada 8088. En la hoja correspondiente se especifica el significado de cada uno de los parámetros. Es importante tener en mente que existen restricciones de tiempo que no pueden alterarse por la inserción de estados de espera.

Tabla 3.2.- Tiempos para un 8088 0 5 MHz

| Nombre común | Nombre/microprocesado | Valor     |

|--------------|-----------------------|-----------|

| LAR          | TAVRL                 | 100 nseg. |

| LRR          | TRLRH                 | 375 nseg. |

| tRD          | TRLDV                 | 335 nseg. |

| tRA          | TRHAX                 | 160 nseg. |

| tDF          | TRHDZ                 | 175 nseg. |

| tAD          | TAVDV                 | 460 nseg. |

| · tRV        | TRLRL                 | 800 nseg. |

| TAW          | TAVKLA                | 100 nseg. |

| TWA          | TWHAX                 | 160 nseq. |

| Thu          | TWLWHA                | 375 nseq. |

| TDW          | TOVWH                 | 300 nseg. |

| TWD          | TWHDX                 | 93 nseg.  |

| TRV          | TWLCLA                | 800 nseg. |

Estos son los tiempos del microprocesador funcionando sin estados de espera, es decir realizando sus operaciones en 4 ciclos de reloj. Algunos de estos valores se modifican cuando se inserta un ciclo de reloj adicional como en el caso de la computadora personal. Especificamente los parámetros que se modifican y los valores que éstos asumen son:

| TRR   |                  | TRLRH  |                 | 575 | nseg.   |

|-------|------------------|--------|-----------------|-----|---------|

| TRD   |                  | TRLDV  | الربيعين المتحا |     | nseq.   |

| TAD   | and the state of | TAVDV  | 2 · · · · · ·   |     | nseg.   |

| TRV : |                  | TRLRL  | · .             | 100 | 0 nseg. |

| Tww   |                  | TWLWHA |                 |     | nseq.   |

| TOW   |                  | TOVWH  |                 |     | nseg.   |