# UNIVERSIDAD NACIONAL AUTONOMA DE MEXICO

Facultad de Ingeniería

## DISEÑO Y REALIZACION DE UN CONTROLADOR ELECTRONICO DE PROYECTORES

T E S I S

Que para obtener el Título de:

INGENIERO MECANICO ELECTRICISTA

P R E S E N T A N:

ALEJANDRO N. GALVAN ESPINOSA

EVA MARIANA GARCIA GOMEZ

DIRECTOR DE TESIS: ING. ANTONIO SALVA CALLEJA

## UNAM – Dirección General de Bibliotecas Tesis Digitales Restricciones de uso

## DERECHOS RESERVADOS © PROHIBIDA SU REPRODUCCIÓN TOTAL O PARCIAL

Todo el material contenido en esta tesis está protegido por la Ley Federal del Derecho de Autor (LFDA) de los Estados Unidos Mexicanos (México).

El uso de imágenes, fragmentos de videos, y demás material que sea objeto de protección de los derechos de autor, será exclusivamente para fines educativos e informativos y deberá citar la fuente donde la obtuvo mencionando el autor o autores. Cualquier uso distinto como el lucro, reproducción, edición o modificación, será perseguido y sancionado por el respectivo titular de los Derechos de Autor.

## INDICE

|                        |        |          |                         | Págin |

|------------------------|--------|----------|-------------------------|-------|

| INTRO                  | DUCCIO | IN       |                         | 1     |

| ı.                     | DESCRI | PCION F  | UNCIONAL                | 4     |

|                        | 1.     | INTROD   | UCCION                  | 4     |

|                        | 2.     | •        | PCION DE LAS ETAPAS     | 5     |

|                        |        | 1.       | ETAPA DE GRABACION      | 5     |

|                        |        | 2.       | ETAPA DE REPRODUCCION   | 12    |

|                        |        | 3.       | ETAPA DE CONTROL        | 15    |

|                        | 4.     | 4.       | INTERFASE A PROYECTORES | 20    |

| 100                    |        |          | Y AUXILIARES            |       |

|                        |        | - 150    |                         |       |

| II.                    | ETAPA  | DE GRABI | ACION                   | 21    |

|                        | 1.     | INTROD   | JCCION                  | 21    |

|                        | 2.     | BLOOUE   | DE TECLAS PROGRAMABLES  | 22    |

|                        |        |          | LA INSTRUCCION A TRAVES | 22    |

| a Arte                 |        |          | DEL TECLADO             |       |

|                        |        | 2.       | ALAMBRADO DEL TECLADO   | 25    |

| de la serie            | 3.     | BLOQUE   | CODIFICADOR DE TECLA    | 31    |

|                        | 4.     | •        | DE REGISTRO DE FORMA-   | 35    |

|                        |        | •        | PALABRA                 |       |

|                        | 5.     |          | DE MEMORIA              | 38    |

| 1,11 <del>1,1</del> 11 | 6.     | •        | CONVERTIDOR PARALELO -  | 39    |

|                        |        | SERIE    |                         |       |

|                        | 7.     | BLODUE   | ACONDICIONADOR DE       | 42    |

|                        | • •    | •        | GRABAR                  |       |

| III.   | ETAPA                   | DE CONTROL                              | 50   |

|--------|-------------------------|-----------------------------------------|------|

|        | 1.                      | INTRODUCCION                            | . 50 |

|        | 2.                      | BLOQUE DE TECLAS DE CONTROL             | 51   |

|        | 3.                      | BLOQUE CONTROLADOR                      | 53   |

|        |                         | 1. LINEAS DE DIRECCION DE               | 53   |

|        | $\frac{1}{2}(x) = 2(x)$ | . LA MEMORIA EPROM                      |      |

|        |                         | 2. LINEAS DE DATOS DE LA                | 61   |

|        |                         | MEMORIA EPROM                           |      |

|        | 4.                      | BLOQUE DE EXHIBICION DE NUME            | 76   |

|        |                         | RO DE INSTRUCCION                       |      |

|        | 5.                      | BLOQUE DE EXHIBICION DE INS-            | 76   |

|        |                         | TRUCCION                                |      |

| e fare |                         |                                         |      |

| TV     | FTAPA                   | DE REPRODUCCION                         | 82   |

|        |                         | INTRODUCCION                            | 82   |

|        |                         | BLOQUE ACONDICIONADOR DE                | 83   |

|        |                         | SEÑAL RECUPERADA                        |      |

|        |                         | BLOQUE SELECTOR DE EJECUCION            | 94   |

|        | ٠,٠                     | DIRECTA                                 | 74   |

|        | , .                     | · -                                     |      |

|        | 4.                      | • • • • • • • • • • • • • • • • • • • • | 96   |

|        |                         | PARALELD                                |      |

|        |                         | 1. SEPARACION DE SEÑALES                | 96   |

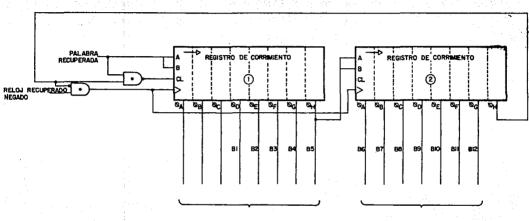

|        |                         | 2. CONVERSION SERIE -                   | 98   |

|        |                         | PARALELD                                |      |

|        | 5.                      | BLOQUE DE REGISTRO DE PALABRA           | 101  |

|        |                         | PARA INTERFASE                          |      |

| 14<br>15<br>17<br>18<br>11<br>14 |

|----------------------------------|

| 17<br>18<br>11<br>14             |

| 18<br>11<br>14                   |

| 14                               |

| 4<br> 4                          |

| 7                                |

| 7                                |

| 7                                |

| 7                                |

|                                  |

|                                  |

|                                  |

|                                  |

| 3                                |

| 5                                |

|                                  |

| 7                                |

|                                  |

| 0                                |

|                                  |

| 2                                |

| 3                                |

|                                  |

| 6                                |

|                                  |

|                                  |

|                                  |

| 3                                |

### INTRODUCCION

El controlador electrónico de proyectores, objeto del presente trabajo, fué diseñado con dos propósitos fundamentales. El primero, resultado de una experiencia académica de varios semestres, es la creación de un aparato que conjuntamente con proyectores y auxiliares forme un equipo adecuado para la realización y exhibición de audiovisuales de apoyo didáctico. El segundo, un propósito común a todos los estudiantes en búsqueda de la conclusión de sus estudios profesionales, es el de presentar una tesis que refleje la asimilación de conceptos y criterios que han constituído nuestra formación como universitarios.

La idea inicial del controlador de proyectores surgió en el Departamento de Control de la Facultad de Ingeniería de la U.N.A.M., como parte de un proyecto en el cual se pretendía la proyección de materiales audiovisuales elaborados en el propio Departamento, de manera automática, sincronizando el movimiento de las diagonsitivas con la cinta de audio.

Tomando así esta idea como base, propusimos el diseño de un controlador de proyectores con mayores capacidades, teniendo en consideración aspectos tales como au utilidad en el área docente, su similitud con los equipos existentes en el mercado en cuanto a capacidades y su compatibilidad con los proyectores más comúnmente empleados.

Como resultado, definimos las características funcionales del sparato. Este aspecto constituye el primer capítulo de esta tesis bajo el título de DESCRIP-CION FUNCIONAL, y pretende dar una descripción compl<u>e</u> ta y concreta de las capacidades del controlador, así como una explicación, a nivel de bloques, del funcion<u>a</u> miento del mismo.

En los capítulos II, III y IV se describen las soluciones de diseño empleadas en la realización de las tres etapas fundamentales del controlador: ETAPA DE -GRABACION, ETAPA DE CONTROL y ETAPA DE REPRODUCCION.

En cuanto a la ETAPA DE GRABACION se presentan las soluciones de diseño para la captura de instrucciones introducidas por el usuario a través del teclado, el almacenamiento de las mismas y su grabación en la cinta magnética.

La ETAPA DE CONTROL contiene las secuencias de operación interna del aparato llevadas a cabo mediante microprogramación en memoria EPROM. También se presentan aquí las soluciones de diseño para los desplie-ques de INSTRUCCION y de NUMERO DE INSTRUCCION, ventanas para el usuario hacía su interacción con el con-trolador.

En la ETAPA DE REPRODUCCION se presentan soluciones de diseño para la recuperación de las instrucciones de la cinta magnética y su paso hacia la interfase -que comunica al controlador con los elementos finales. que realizarán las diferentes acciones: los proyectores v los auxiliares.

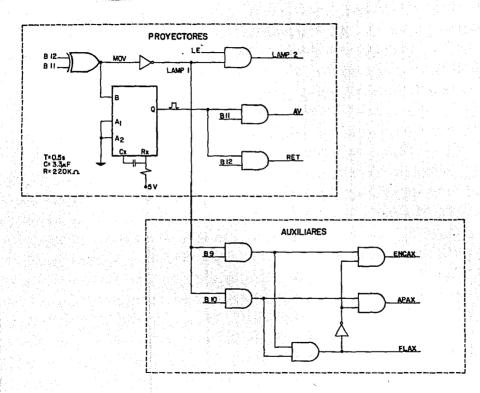

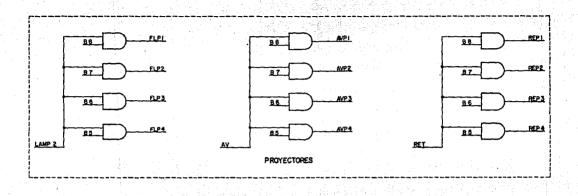

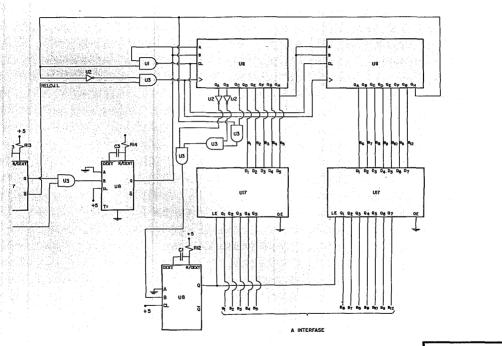

La INTERFASE A PROYECTORES Y AUXILIARES constituye el capítulo V, último del trabajo. En éste se hace una descripción funcional de dicha interfase y se presentan las soluciones de diseño empleadas para su realización. No se pretende un análisis detallado de las soluciones, sino proporcionar una idea clara de la forma de operación de la interfase.

En las páginas siguientes se expone el resultado del trabajo realizado durante el diseño de controlador electrónico de provectores.

E.M.G.G.

A.N.G.F.

Así, cada vez que se reproduzca la cinta de audio a través del controlador, éste hará actuar a los proyectores en la forma deseada.

#### 2. DESCRIPCION DE LAS ETAPAS

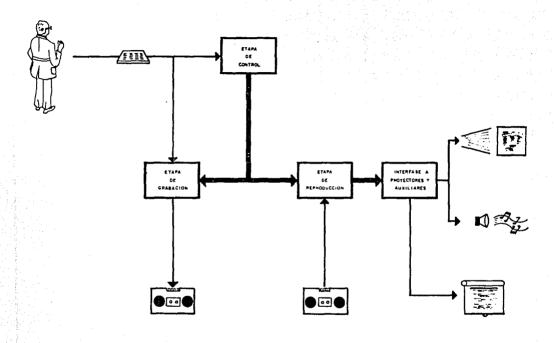

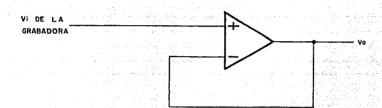

El controlador de proyectores, para su mejor comprensión, se puede dividir en cuatro etapas fundamentales, las cuales se describen en el presente capítulo (Fig. 1).

#### 2.1 ETAPA DE GRABACION

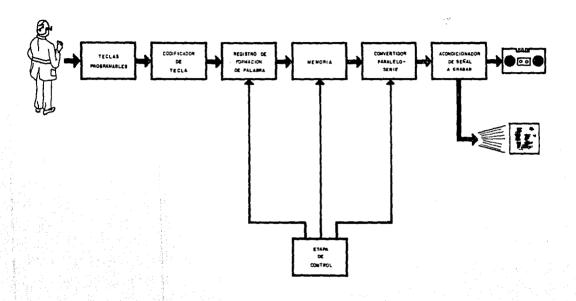

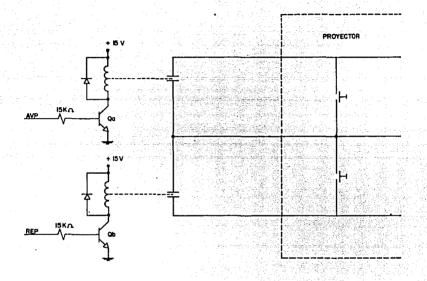

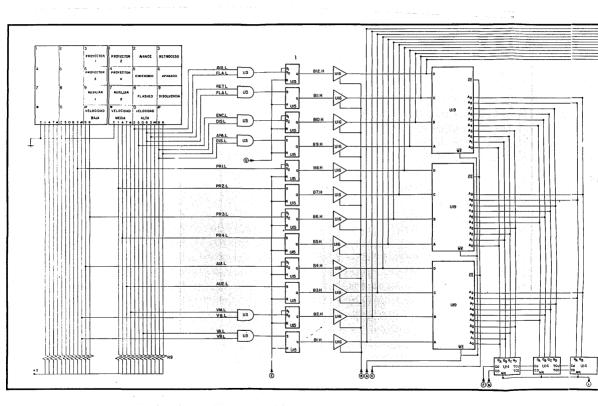

Esta etapa constituye el inicio de la operación del aparato. Por medio de ella el usuario programa la secuencia de su audiovisual en el controlador y posteriormente la graba en la cinta magnética. La etapa de grabación se divide en seis bloques funcionales (Fig. 2):

- 1. BLOQUE DE TECLAS PROGRAMABLES.

- 2. BLOQUE CODIFICADOR DE TECLA.

- 3. BLOQUE DE REGISTRO DE FORMACION DE LA PALABRA.

- 4. BLOQUE DE MEMORIA.

- 5. BLOQUE CONVERTIDOR PARALELO SERIE.

- 6. BLOQUE ACONDICIONADOR DE SEÑAL A GRABAR.

A continuación se da una descripción funcional de estos bloques.

Figura 1. ETAPAS FUNDAMENTALES DEL CONTROLADOR

Figura 2. ETAPA DE GRABACION

#### 2.1.1 BLOQUE DE TECLAS PROGRAMABLES

Mediante el uso de las teclas programables con que cuenta el teclado del aparato, el usuario tiene la posibilidad de formar una instrucción con ciertas características:

- A. Función a realizar por proyectores o auxiliares:

El aparato posee capacidad de hacer que uno o

varios proyectores ejecuten cualquiera de las 6

siguientes funciones en cada instrucción.

- Avance, que es poner en posición de ser exhibida la siguiente transparencia (adelantar el carro del proyector).

- Retroceso, que es poner en posición de ser exhibida la transparencia anterior (retroceder el carro del proyector).

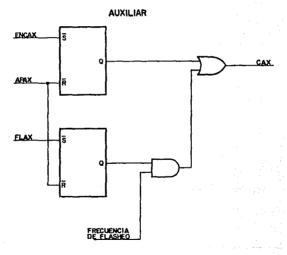

- Encendido, que es la activación de la lámpara del proyector a su máxima intensidad, sin cambio de transparencia.

- Apagado, que es la desactivación total de la lámpara del proyector, sin cambio de transparencia.

- Flasheo, que es un encendido intermitente de la lámpara a la más alta velocidad posible, sin cambio de transparencia;

- Disolvencia, que es el encendido de un proyector simultáneamente con el apagado de otro, sin cambio de transparencia.

- B. Dispositivo que realizará la función: El aparato da la posibilidad de ejecutar cualquiera de las cinco primeras funciones mencionadas anteriormente en hasta cuatro proyectores a la vez. La última función, disolvencia, sólo se puede llevar a cabo por parejas de proyectores.

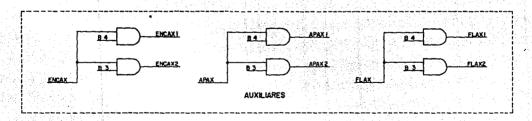

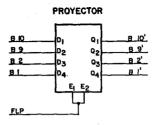

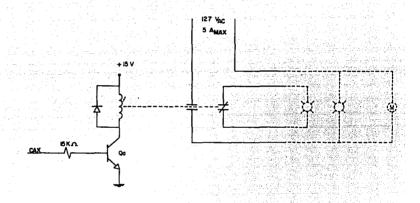

Además, se cuenta con dos líneas auxiliares que pueden ejecutar las funciones de encendido, apagado y flasheo. Estas líneas tienen como finalidad el manejo de elementos que contribuyan a la presentación del audiovisual, tales como focos, pantallas, telones, etc.

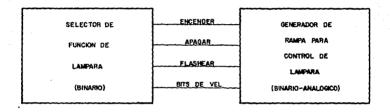

- C. Velocidad de ejecución de la función: En las funciones que manejan las lámparas de los proyectores (encendido, apagado y disolvencia) se tiene la opción de seleccionar una de cuatro velocidades disponibles:

- Velocidad instantánea, que está determinada por el tiempo de respuesta de la lámpara.

- Velocidad alta, que realiza el cambio de estado de la lámpara en 2 segundos.

- Velocided media, que lo realize en 4 segundos.

- Velocidad baje, que lo realiza en 8 segundos.

Cuando la función sea ejecutada por los auxiliares, sólo se hará uso de la veloci-

Una vez que el usuario ha seleccionado una función, uno o varios dispositivos que la ejecutarán y una velocidad (cuando se tenga esta opción), entonces ha formado una instrucción.

#### 2.1.2 BLOQUE CODIFICADOR DE TECLA

Este bloque tiene la función de convertir la inétrucción que está siendo tecleada, en una palabra de control comprensible y manejable para el aparato.

#### 2.1.3 BLOQUE DE REGISTRO DE FORMACION DE PALABRA

En este registro se almacena la palabra de control a medida que va siendo creada por el usuario. Al terminar de teclear todas las características de la instrucción, la palabra de control correspondiente queda completa y presente en el registro.

#### 2.1.4 BLODUE DE MEMORIA

Cada palabra de control que es creada se almacena en la memoria del aparato, formándose una secuencia de palabras correspondiente a la secuencia de instrucciones que constituye el audiovisual.

## 2.1.5 BLOQUE CONVERTIDOR PARALELO - SERIE

Este bloque se encarga de tomar cada una de las pa-

labras que se encuentran en la memoria y cuya salida son líneas en paralelo, y convertirla en una salida que va en forma seriada por una sola línea.

#### 2.1.6 BLOQUE ACONDICIONADOR DE SEÑAL A GRABAR

El acondicionador de señal a grabar modifica características de nivel y duración a la señal seriada, de manera que al entrar dicha señal a la grabadora, sea captada de una forma adecuada.

Este bloque cuenta también con una salida adicional que va hacia los proyectores y auxiliares, para que el usuario pueda ejecutar directamente una instrucción que está en la memoria, sin tener que grabarla en la cinta magnética.

Esta opción de ejecución directa es de gran utilidad ya que elimina el paso de la palabra de control por la grabadora y la envía al bloque selector de ejecución directa de la etapa de reproducción.

Si se quiere probar la operación de una instrucción, mediante la función de control "Ejecutar" se hace pasar la palabra de control asociada a dicha instrucción de la etapa de grabación a la etapa de reproducción sin hacer uso de la cinta magnética para su transmisión.

Mediente la etapa de grabación se logra que toda una secuencia de instrucciones quede registrada en un canal de cinta magnética, en sincronía con el otro (audio).

La sincronía consiste en grabar las palabras de control en lugares previamente seleccionados de acuerdo a la música o texto del audiovisual.

Es importante señalar que varios de los bloques de la etapa de grabación están manejados o apoyados por la etapa de control.

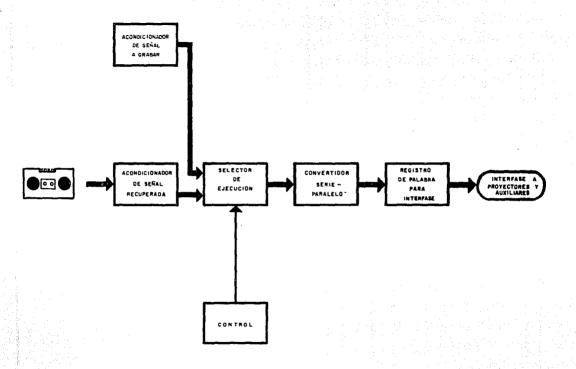

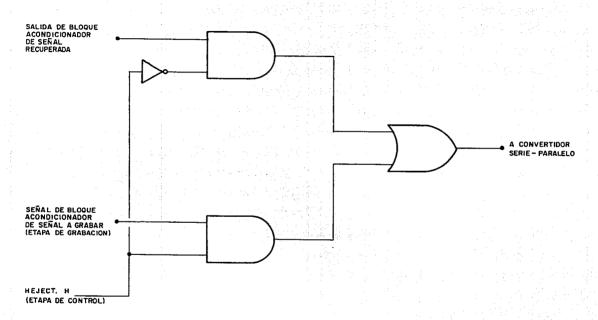

### 2.2 ETAPA DE REPRODUCCION

Comprende la recuperación y el procesamiento de las palabras de control provenientes de la grabadora. Su finalidad es hacer ejecutar a los proyectores y auxiliares las funciones correspondientes a las instrucciones grabadas por el usuario en la etapa de grabación. Los bloques que constituyen la etapa de reproducción son cuatro (Fig. 3):

- 1. BLOQUE ACONDICIONADOR DE SEÑAL RECUPERADA.

- BLOQUE SELECTOR DE EJECUCION.

- 3. BLOQUE CONVERTIDOR SERIE PARALELO.

- 4. BLOQUE DE REGISTRO DE PALABRA PARA INTERFASE.

Se describe a continuación la función de cada uno de los bloques.

Figura 3. ETAPA DE REPRODUCCION

#### 2.2.1 BLOQUE ACONDICIONADOR DE SEÑAL RECUPERADA

Mediante este bloque, las palabras de control que se encuentran grabadas en la cinta magnética son recuperadas por el aparato, y acondicionadas para su menejo en el resto de los bloques de la etapa.

#### 2.2.2 BLOQUE SELECTOR DE EJECUCION

Su función es seleccionar, según lo indique el usuario por medio del control, si la instrucción que se desea ejecutar proviene de la grabadora, o de la opción de ejecución directamente de la memoria.

#### 2.2.3 BLOQUE CONVERTIDOR SERIE - PARALELO

Este bloque tiene como finalidad convertir la palabra de control de la forma seriada en que se encuentra grabada en la cinta magnética y en que pasa por el acondicionador de señal recuperada, a salidas en paralelo por diferentes líneas.

#### 2.2.4 BLOQUE REGISTRO DE PALABRA PARA INTERFASE

Constituye el final de la etapa de reproducción. Tie ne por objeto retener la información de la palabra de control durante el tiempo necesario para que sea ejecutada la instrucción correspondiente por los proyectores y auxiliares, y permanece hasta la llegada de la siguiente palabra.

En forma global, la etapa de reproducción hace que las palabras de control que han sido grabadas en la cinta magnética pasen a los dispositivos encargados de ejecutar las instrucciones (proyectores y auxiliares).

El bloque selector de ejecución directa es el único de esta etapa que requiere de la etapa de control para su operación.

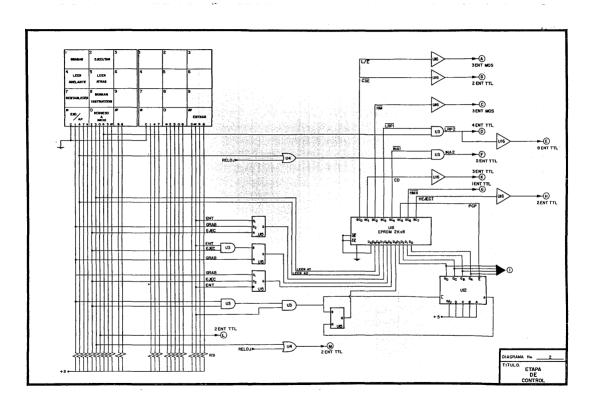

#### 2.3 ETAPA DE CONTROL

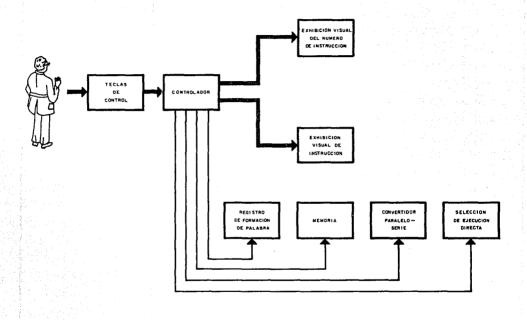

Constituye la parte fundamental del aparato, ya que es quien dirige sus acciones principales. Está forma da por cuatro bloques, y relacionada con varios bloques de las otras etapas (Fig. 4).

Los bloques que la constituyen se describen a continuación, y son los siguientes:

- 1. BLOQUE DE TECLAS DE CONTROL.

- 2. BLOQUE CONTROLADOR.

- 3. BLOQUE DE EXHIBICION DEL NUMERO DE INSTRUCCION.

- 4. BLOQUE DE EXHIBICION DE INSTRUCCION.

## 2.3.1 BLOQUE DE TECLAS DE CONTROL

Con las teclas de control el usuario tiene la opción de seleccionar una de varias funciones que el controlador puede realizar. Estas funciones son diferentes de las comprendidas en el bloque de teclas de funciones programables, ya que las primeras las ejecuta el

Figura 4. ETAPA DE CONTROL

aparato para la selección de su forma de operación, mientras que las segundas las ejecutarán los proyectores y los auxiliares después de haber sido almacenadas en la memoria del aparato, grabadas y reproducidas.

#### Las funciones de control son:

- Entrer.- Una vez que el usuario ha formado una instrucción, esta tecla le permite almacenarla en la memoria del aparato bajo un cierto número de instrucción. Posteriormente este número se incrementa para recibir la siguiente instrucción.

- 2. Grabar.- Ya almacenadas todas las instrucciones en la memoria, esta tecla permite al usuario grabarlas en la cinta magnética de manera secuencial, una cada vez que se oprima la tecla. Todo esto ocurre mientras la cinta está avanzando, de tal forma que la posición en que se grabe cada instrucción sea seleccionada en base al audio.

- Ejecutar.- Esta tecla da la opción al usuario de que una vez formada una instrucción o tomándola de la memoria, ésta se ejecute directamente, sin la necesidad de ser grabada.

- 4. Borrar instrucción.- Si el usuario, al formar una instrucción y antes de darle entrada a memoria, comete un error o desea modificarla, podrá borrarla y empezar a formarla nuevamente mediante el uso de esta tecla.

- 5. Leer adelante.- Todas las instrucciones que constituyen el audiovisual, llevan asociado un "número de instrucción" consecutivo y único para cada una. La tecla leer adelante hace que se muestre al usuario, mediante tres dígitos luminosos, un número y las características de la instrucción asociada a éste (función, dispositivo, velocidad). Si se mantiene oprimida la tecla durante un segundo o se suelta y oprime nuevamente el controlador incrementará el número, aparecien do en los indicadores el nuevo número y la instrucción correspondiente.

- 6. Leer atrás.- La función de esta tecla es similar a la de leer adelante, con la diferencia de que al mantener la tecla oprimida por un segundo o soltarla y volver a oprimirla, el controlador decrementará el número de instrucción, mostrándose al usuario el número anterior al que se estaba exhibiendo, y su instrucción asociada.

Con las dos teclas "leer", el usuario puede seguir de principio a fin o viceversa todas las instrucciones que forman su audiovisual, mediante el incremento o decremento del número de instrucción. Esto brinda la oportunidad de realizar modificaciones al audiovisual tecleando una nueva instrucción y dándole entrada a memoria en un número ya utilizado, con lo cual la nueva instrucción reemplazará a la anterior.

7. Regreso a inicio.- Esta tecla permite al usuario colocar el número de instrucción en el inicio de la secuencia de su audiovisual, mostrándose también el contenido de la primera instrucción.

8. Restablecer.- Si por alguna causa el usuario pierde el control del aparato, o si desea borrar toda la información almacenada en la memoria, al oprimir esta tecla iniciará de nuevo toda la operación del controlador. Su función es equivalente al encendido del aparato.

#### 2.3.2 BLOQUE CONTROLADOR

Este bloque es propismente quien realiza las acciones de control sobre los dispositivos que así lo requieren, para llevar a cabo una cierta función del aparato.

Tiene acción directa sobre los bloques de registro de formación de palabra (etapa de grabación), memoria (etapa de grabación), convertidor paralelo-serie (etapa de grabación) y selección de ejecución directa (etapa de reproducción).

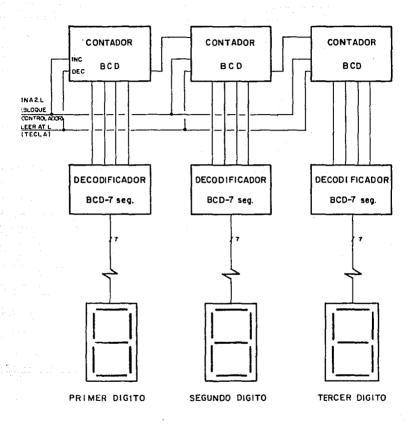

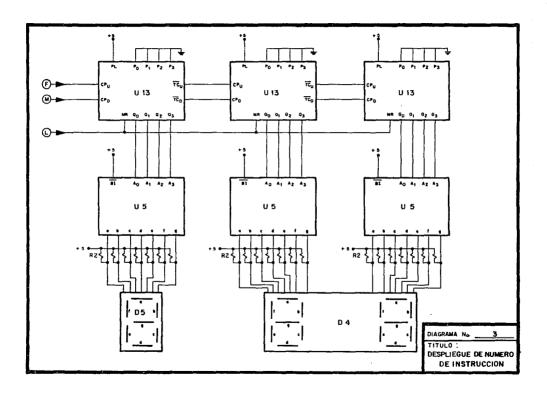

#### 2.3.3 BLOQUE DE EXHIBICION DEL NUMERO DE INSTRUCCION.

Mediante este bloque el usuario puede ver el número que posee una instrucción en particular, del número total que constituye el audiovisual. El méximo número de instrucciones que se puede almacenar en la memoria es 1000.

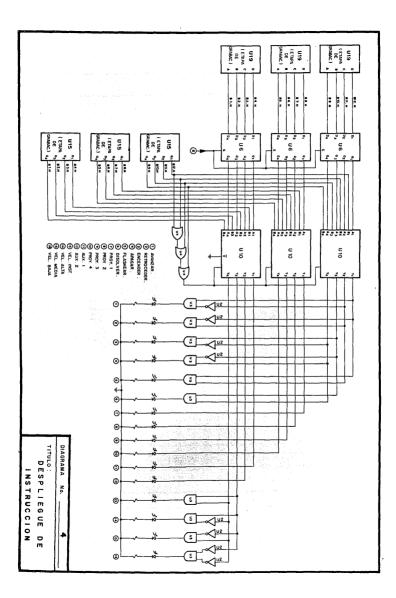

#### 2.3.4 BLOQUE DE EXHIBICION DE INSTRUCCION

Por medio de este bloque el usuario tiene la opción de ver como se va formando una instrucción antes de darle entrada a memoria, o bien de ver el contenido de la instrucción (función, dispositivos y velocidad) asociada al número que aparece en los digitos luminosos del número de instrucción.

La función de la etapa de control es, mediante su interacción con las otras dos etapas y con el usuario, permitirle a este último el manejo total del aparato, con la finalidad de crear un audiovisual con opciones variadas en proyectores y auxiliares y que sea reproducible en forma automática.

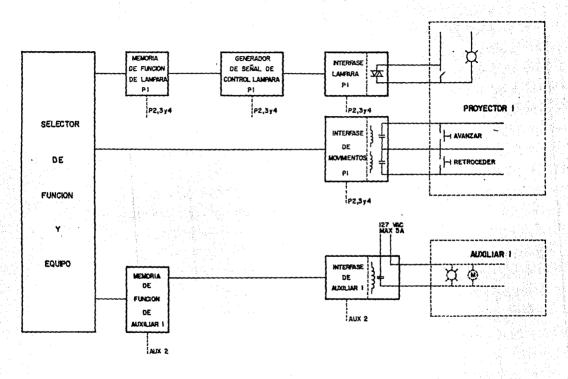

### 2.4 INTERFASE A PROYECTORES Y AUXILIARES

Esta interfase no constituye en sí una etapa del controlador. Su función es hacer compatibles las señales de salida del aperato con las señales que requieren los proyectores para generar las acciones tanto en las lámparas como en el avance y retroceso de las transparencias.

#### ETAPA DE GRABACION

#### INTRODUCCION

La primera etapa del controlador electrónico de proyectores, en lo que se refiere a su secuencia de operación, es la etapa de grabación.

Para reproducir un audiovisual automáticamente a tra vés del aparato, es necesario que las instrucciones a ejecutarse en dicho audiovisual hayan sido previamente grabadas en una cinta magnética.

A su vez, para ser grabadas las instrucciones en la cinta magnética, éstas deben ser primeramente forma das mediante el teclado y almacenadas en la memoria del controlador. Así, la etape de grabación comprende desde la creación de una instrucción por medio del teclado, hasta su grabación en la cinta magnética.

Los bloques funcionales que componen esta etapa son los siquientes (Cap. I. Fig. 2):

- 1. BLOQUE DE TECLAS PROGRAMABLES.

- 2. BLOQUE CODIFICADOR DE TECLA.

- 3. BLOQUE DE REGISTRO DE FORMACION DE LA PALABRA.

- 4. BLOQUE DE MEMORIA.

- 5. BLOQUE CONVERTIDOR PARALELO SERIE.

- 6. BLOQUE ACONDICIONADOR DE SEÑAL A GRABAR.

### BLODUE DE TECLAS PROGRAMABLES

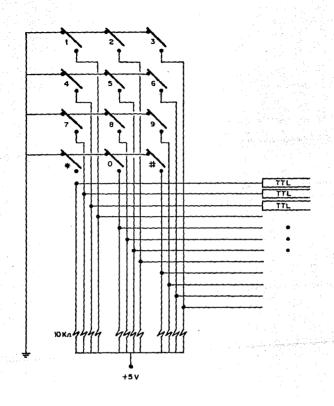

Este bloque está constituído por dos teclados de membrana de conexión paralelo y 12 teclas cada uno, y una resistencia limitadora de corriente de 10 K.n.para cada tecla.

#### 2.1 LA INSTRUCCION A TRAVES DEL TECLADO

Funcionalmente el teclado se presenta como un conjunto de 24 teclas de membrana de las cuales 15 están asignadas a las diferentes opciones que forman la instrucción (Fig. 1).

Una instrucción es un conjunto de datos que el usua rio debe seleccionar y proporcionar al controlador pulsando ciertas teclas, para ser convertido en una palabra de control. Las partes de una instrucción son tres y se agrupan por secciones del teclado:

FUNCION. Se debe seleccioner solamente una función por instrucción. Las opciones que se presentan en el teclado son:

AVANZAR

RETROCEDER

ENCENDER

APAGAR

FLASHEAR

DISOLVER

DISPOSITIVO. Se pueden seleccionar uno o más de los dispositivos presentados en el teclado, oprimiendo la o las teclas correspondientes:

PROYECTOR 1

PROYECTOR 2

PROYECTOR 3

PROYECTOR 4

AUXILIAR 1 (excepto avance, retroceso, disolvencia)

AUXILIAR 2 (excepto avance, retroceso, disolvencia)

VELOCIDAD. Les funciones asociades a les lémperes de les proyectores (encender, apager, flashear, disolver) pueden realizarse en distintes velocidades, de acuerdo a las necesidades particulares de cada audiovisual. La característica de velocidad sólo es aplicable a proyectores, ya que los auxiliares tienen asignada una velocidad fija para sus funciones. Las opciones que se presentan en el teclado, en cuanto a velocidades son:

VEL. BAJA B segundos

VEL. MEDIA 4 segundos

VEL. ALTA 2 segundos

VEL. INSTANTANEA No esté en el teclado. Es la que se esigna si no se selecciona alguna de las otras. Velocidad máxima de cambio de estado de la

lámpara.

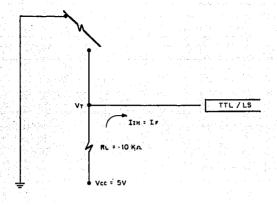

#### 2.2 ALAMBRADO DEL TECLADO

El tipo de teclado seleccionado es de membrana de 12 teclas en paralelo RAPID CIRCUIT 1200. Sus características eléctricas son:

Vmax = 30 ·V Imax = 100 mA Rcontacto = 50 a 100  $\Omega$

El bloque siguiente, codificador de tecla, está alimentado por las salidas del teclado y lo constituyen circuitos integrados TTL/LS con las siguientes características:

$V_{IH} = 2V \text{ min.}$   $V_{IL} = 0.8V \text{ max.}$

$I_{IH} = 20 \text{ M}^{Q} \text{ V}_{IH} = 2.7 \text{V}$

IIL =-0.4 mA @ VIL = 0.4V

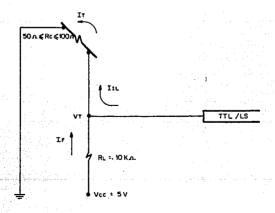

De acuerdo a las características anteriormente mencionadas se propuso el arreglo eléctrico de teclado (Fig. 2) que se considera más adecuado en cuanto a niveles TTL, corriente drenada y compatibilidad con la lógica de las etapas siguientes.

La conexión seleccionada es el común del teclado a tierra y cada tecla a la fuente de +5V a través de una resistencia limitadora de corriente.

Al permanecer el contacto abierto, la corriente que circula por el circuito está sujeta únicamente a la

Figure 2. CONEXION DEL TECLADO

Figura 3. TECLA SIN OPRIMIR

Figura 4. TECLA OPRIMIDA

Analizando los requerimientos de corriente del teclado y la corriente que debe entregar la fuente a las entradas TTL debido al arreglo propuesto, al mantener el contacto abierto es demandada tan sólo I<sub>IH</sub> de la fuente hacia el circuito integrado asociado a la sal<u>i</u> de de cada tecla.

Con la tecla oprimida se demanda una corriente limit<u>a</u> da por las resistencias que constituyen la malla de - la tecla:

$$I_F = \frac{v_{CC}}{R_L + R_C}$$

Suponiendo la menor resistencia de contacto, la mayor corriente que la fuente debe entregar está dada por:

La corriente a través del teclado para esta condición está dada por la corriente de la fuente más la corriente que drena el circuito integrado TTL en estado bajo:

$$I_T = I_F + I_{IL}$$

$$I_T = 0.497 \times 10^{-3} + 0.4 \times 10^{-3}$$

$$I_T = 0.897 \text{ mA.}$$

De los resultados de  $I_F$  (contacto abierto y cerrado), e  $I_T$  se observa que la demanda de corriente a la fuente es muy pequeña, y que la corriente que circula por los contactos del teclado está dentro del rango especificado por el fabricante:

Demanda de corriente a la fuente por cada tecla oprimida = 0.497 mA

Demanda de corriente a la fuente sin teclas oprimidas = 0.48 mA

Corriente máxima circulando a través de cada contacto del teclado

- 0.897 mA

Por último, la lógica del teclado como salida hacia circuitos integrados TTL ae muestra en la siguiente tabla.

| 4 6 70            | ESTADO DE<br>La Tecla   | NIVEL DE ENTRADA<br>A TIL |  |

|-------------------|-------------------------|---------------------------|--|

| The second second | OPRIMIDA<br>NO OPRIMIDA | BAJO:<br>ALTO             |  |

Teble

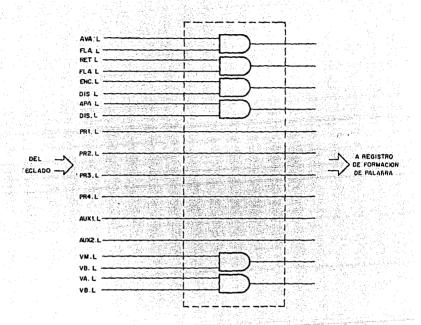

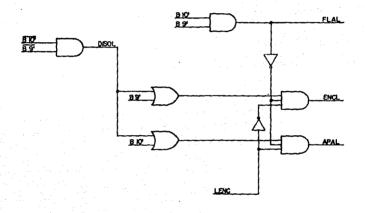

#### 3. BLOQUE CODIFICADOR DE TECLA

El bioque codificador está formada por 6 compuertas lógicas AND de 2 entradas (74LSO8), las cuales constituyen el paso intermedio entre la instrucción tecleada por el usuario y la palabra de control asociada que se registrará en el siguiente bloque. (Fig. 5)

Mientras el teclado se mantenga sin ser oprimido, todas sus líneas presentan un estado elto (+ 5V). Después, a medida que el usuario vaya formando su instrucción, irá apareciendo una línea en estado bajo por cada tecla que sea oprimida.

La secuencia en que se debe teclear la instrucción es:

FUNCION.- Selectionar y teclear una sola fu<u>n</u> ción por instrucción.

DISPOSITIVO(S).- Selectionar y teclear todos los dispositivos asignados a realizar le función, uno a la vez.

VELOCIDAD.- Seleccionar y teclear, en las funciones que se requiera, una sola v<u>e</u> locidad. La omisión de selección de velocidad causará la asignación de la velocidad instantánea.

En la selección de la función, el codificador, mediante 4 compuertas AND, convierte el contenido de 6 líneas del teclado (las 6 funciones) en 4 líneas

Figure 5. BLOQUE CODIFICADOR DE TECLA

hacia el bloque de registro, con la finalidad de red<u>u</u> cir la palabra de control.

Las líneas de dispositivos no son alteradas por el codificador, ya que esto facilitará su detección en los actuadores sin necesidad de una posterior decodificación.

Las 3 velocidades a que se tiene acceso en el teclado, y la omisión de ellas, son convertidas en 2 líneas hacia el bloque de registro mediante 2 compuertas AND.

Las siguientes tablas muestran la correspondencia entre las líneas del teclado y la salida del bloque codificador, para las diferentes partes de la instrucción.

| FUNCION     | AV. |   | TE | EAS<br>CL<br>AP. | ADO |     | 8L<br>B12 |     | IDA<br>CODIF<br>B10 | DE<br>ICADOR<br>89 |

|-------------|-----|---|----|------------------|-----|-----|-----------|-----|---------------------|--------------------|

| NO OPERA    | 1   | 1 | 1  | 1                | 1   | 1   | 1         | 1   | 1                   | 1                  |

| AVANCE      | o   | 1 | .1 | 1                | 1   | 1 - | 0         | . 1 | 1                   | 1                  |

| RETROCESO   | 1   | 0 | 1  | 1                | 1   | 1   | 1         | 0   | 1                   | 1                  |

| ENCENDIDO   | 1   | 1 | 0  | 1                | 1   | 1   | 1         | 1   | 0                   | 1                  |

| APAGADO     | 1   | 1 | 1. | 0                | 1   | 1   | 1         | 1   | 1                   | 0                  |

| FLASHED     | 1   | 1 | 1  | 1                | 0   | 1   | 0         | 0   | 1                   | 1                  |

| DISOLVENCIA | 1   | 1 | 1  | 1                | 1   | 0   | 1         | 1   | 0                   | 0                  |

Tabla 2

| DISPOSITIVO | P1 | L<br>P2 | TE | CLA |    | _ | BB  | 81.00<br>87 | UE C | IDA<br>ODIF<br>85 | ICAD |    |  |

|-------------|----|---------|----|-----|----|---|-----|-------------|------|-------------------|------|----|--|

| NO OPERA    | 1  | 1       | 1  | 1   | 1  | 1 | 1   | 1           | 1    | 1                 | 1    | 1  |  |

| PROYECTOR 1 | o  | 1       | 1  | 1   | 1  | 1 | 0   | 1           | 1    | 1                 | 1    | 1  |  |

| PROYECTOR 2 | 1  | 0       | 3  | 1,  | 1  | 1 | 1   | 0           | 1    | 1                 | 1    | 1  |  |

| PROYECTOR 3 | 1  | 1       | 0  | 1   | 1. | 1 | 1   | 1           | 0    | 1                 | 1    | 1  |  |

| PROYECTOR 4 | 1  | 1       | 1  | 0   | 1  | 1 | 1   | 1           | 1    | 0                 | 1    | 1  |  |

| AUXILIAR 1  | 1  | 1       | 1  | 1   | Ġ  | 1 | 115 | 1           | 1    | 1                 | 0    | 1  |  |

| AUXILIAR 2  | 1  | 1       | 1  | 1   | 1  | 0 | 1   | 1           | 17   | i <b>1</b> j      | 1    | 0- |  |

Tabla 3

| VELOCIDAD.  |   | NEAS<br>TECLAC<br>VM. |     | SALIDA A<br>BLOQUE CODIFICADOR<br>B2 B1 |

|-------------|---|-----------------------|-----|-----------------------------------------|

|             |   | •                     |     |                                         |

| INSTANTANEA | 1 | 1                     | 1   | 1 1                                     |

| ALTA        | 0 | 1                     | 1   | 1 0                                     |

| MEDIA       | 1 | 0                     | 1.1 | 0 1                                     |

| BAJA        | 1 | . 1                   | 0   | 0 0                                     |

Tabla 4

A la salida del bloque codificador de tecla se presentan ya los bits que constituyen la palabra de control. Esta palabra contiene toda la información necesaria para que se ejecute la instrucción teclada por el usuario.

### 4. BLOQUE DE REGISTRO DE FORMACION DE PALABRA

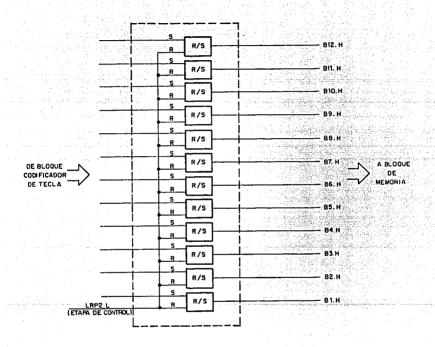

Lo forman 12 latches del tipo RS (74LS279), los cuales den entrada y guardan la información que se va generando en las salidas del bloque codificador (Fig. 6).

La tabla de verdad que siguen los latches empleados es:

| ENTRADAS                     | SALIDA         |

|------------------------------|----------------|

| 5∙ ह                         | a              |

| 0. 0                         | ND OP.         |

| 0 1                          | 1              |

| 1 0                          | 0              |

| 1 1                          | Q <sub>0</sub> |

| • Para latches 1 = Ambas S a |                |

Tabla 5

O = Una o embas 5 bajas

Figura 6. REGISTRO DE FORMACION DE PALABRA

Las entradas 5 de los latches son tomadas del bloque codificador.

Les entrades  $\overline{R}$ , por otre perte, son tomades en forme común de una línea especial ( $\overline{LRPZ}$ ) proveniente de la etapa de control.

La menera en que opera el bloque de registro de form<u>a</u> ción de palabra es la siquiente:

Mientras no es oprimida ninguna tecla programable del teclado, todas sus líneas permanecen en estado alto, al igual que las salidas del bloque coficador. Además la etapa de control mantiene la línea LRP2 en estado alto. Así, de acuerdo a la tabla de verdad de los latches, lo que se encuentra en las salidas de éstos es el estado Qo (estado anterior), que previamente se ha garantizado por el control, serán niveles bajos.

Al iniciar el usuario la formación de una instrucción, teclea una de las 6 funciones que se presentan en el teclado. Mientras se mantenga oprimida la tecla seleccionada, aparece en una o en dos de las cuatro primeras líneas de salida del bloque codificador, un nivel bajo. La correspondencia entre líneas del teclado y salidas del bloque codificador se encuentra en la tabla 2.

Entonces, al presentarse un nivel bajo en las entradas  $\overline{S}$  de algunos de los latches, y seguirse presentando un nivel alto en las entradas  $\overline{R}$ , se genera un cambio a nivel alto en la salida de estos latches,

permaneciendo este nivel en forma inalterable, aún cuando la tecla que produjo el cambio deje de ser corimida.

Continuando con la formación de la instrucción, el usuario selecciona uno o varios dispositivos, los cuales desea que ejecuten la función ya tecleada. Al oprimir en forma consecutiva las teclas de los dispositivos seleccionados, el latch correspondiente a cada dispositivo (cualesquiera de las 6 siguientes líneas de salida del bloque codificador) cambia su estado a alto, y así permanece incluso una vez soltada la tecla (Ver tabla 3).

Por último, al seleccionarse una de las velocidades de que dispone el teclado, una o ambas salidas del bloque codificador correspondientes a velocidades (últimas dos líneas del bloque codificador) presentan un cambio a nivel bajo (Ver tabla 4). El nivel bajo que se genere, se presenta en la entrada  $\overline{S}$  del latch y permaneciendo en la entrada  $\overline{R}$  un nivel alto, el latch modifica su salida a nivel alto. Este nivel permanece así aún después de soltada la tecla.

De la manera anteriormente descrita, al terminar de ser tecleada una instrucción, su palabra de control correspondiente quedará almacenada en el conjunto de 12 latches que constituye el bloque de registro de formación de la palabra.

## 5. BLOQUE DE MEMORIA

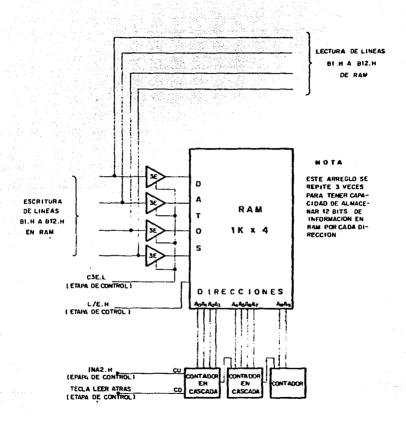

Este bloque está constituído por dos circuitos integrados de tres estados (74LS367), tres memorias tipo RAM (2114) de 1K x 4 y tres contadores (74LS193). La forma de conexión de estos elementos y las líneas asociadas se muestran en la figura 7.

La forma de operación del bloque es la siguiente:

Una vez que se tiene presente una palabra de control completa, el usuario puede darle entrada a memoria - mediante la tecla ENTRAR. Al oprimir esta tecla, - se genera una secuencia de control de la etapa de - control, la cual hace que los circuitos 3 estados - permitan el paso de las salidas de los latches hacia la memoria, y en seguida habilita la memoria en modo de escritura. La secuencia completa ENTRAR se deta lla en el Capítulo III.

Los contadores tienen como finalidad determinar la dirección de las memorias RAM. Su conexión es en cascada, y las líneas de incremento y decremento de contador son activadas por diferentes condiciones tales como las teclas LEER ADELANTE, LEER ATRAS, EN-TRAR, EJECUTAR, GRABAR y otras. Esto se explica con detalle también en el Capítulo III.

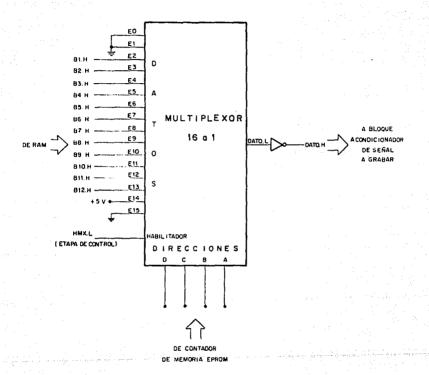

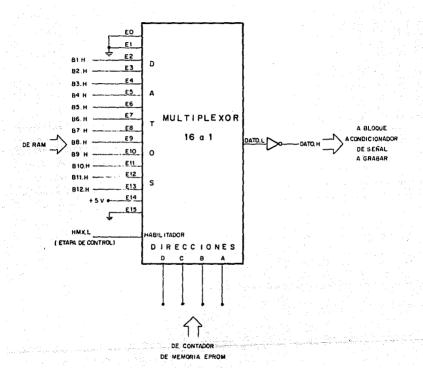

# BLOQUE CONVERTIDOR PARALELO - SERIE

Está constituído por un multiplexor (74LS150) de 16 a 1, el cual toma como entradas las 12 líneas de salida de las memorias RAM y 4 valores fijos de potocolo, y los pone en forma seriada en su salida, durante la cuenta de sus 4 líneas de direcciones. Esta cuenta es activada en forma descendente mediante el contador del bloque controlador al oprimirse la tecla GRABAR

Figura 7. BLOQUE DE MEMORIA

(ver Capítulo III). A la salida del multiplexor se encuentra un inversor (74LSO4), ya que el multiplexor presenta en su salida el negado de las entradas.

La activación o desactivación del multiplexor está determinada por una línea del bloque controlador dependiendo de la secuencia que se esté realizando en él. Las secuencias del bloque controlador se describe en detalle en el Capítulo siquiente.

La tabla de verdad que sigue el multiplexor se muestra a continuación, y de acuerdo a ella se genera la palabra serie.

|          |     |    | ENTR | ADAS | SALIDA     | SALIDA   |

|----------|-----|----|------|------|------------|----------|

| DI       |     |    | NES  | HAB. | M⊔X        | INVERSOR |

| <u>D</u> | C   | Ð  | A    | S    |            |          |

| ×        | X   | X  | x    | 1    | 1          | . 0      |

| 0        | 0   | 0  | 0.   |      | ĒŪ         | E٥       |

| ٥        | 0   | 0  | 1    | 0    | <b>E</b> 1 | E1       |

| 0        | 0   | 1  | 0    | 0    | Ē2         | E2 -     |

| 0        | 0   | 1  | 1    | 0    | E3         | E3       |

| 0        | 1   | ٥  | 0    |      | <u>E4</u>  | E4       |

| 0        | 1   | 0  | 1    | 0    | E5         | E5       |

| 0        | 1   | 1  | 0    | 0    | <u>E6</u>  | E6       |

| 0        | . 1 | 1  | 1    | 0    | Ē7         | E7       |

| 1        | 0   | 0  | 0    | O    | E8         | E8       |

| 1,       | ۵   | 0  | 1    | 0    | <u>E9</u>  | E9       |

| 1        | 0.  | 1  | 0    | 0    | E10        | E10      |

| 1.       | Π.  | 1  | 1    | 0    | E11        | E11      |

| 1        | 1   | 0  | 0    | 0    | E12        | E12      |

| 1        | 1   | 0  | 1    | 0    | E13        | E13      |

| 1        | 1   | 1. | 0    | 0    | E14        | E14      |

| 1        | 1   | 1  | 1    | 0    | E15        | E15      |

Tebla 6

La forma de conexión de las entradas del multiplexor se muestra en la figura 8. Para la cuenta decreciente que se genera en sus direcciones, la palabra serie a la salida del bloque convertidor es de la siquiente manera:

# PALABRA DE CONTROL

0 0 81 82 83 84 85 86 87 88 89 810 811 812 1 0 EO E1 E2 E3 E4 E5 E6 E7 E8 E9 E10 E11 E12 E13 E14 E15

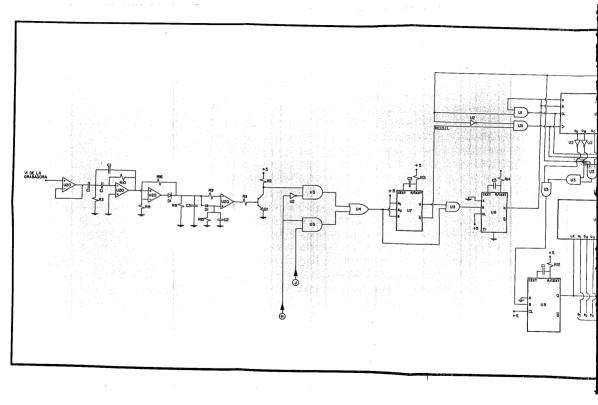

# 7. BLOQUE ACONDICIONADOR DE SEÑAL A GRABAR

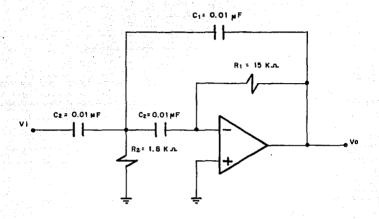

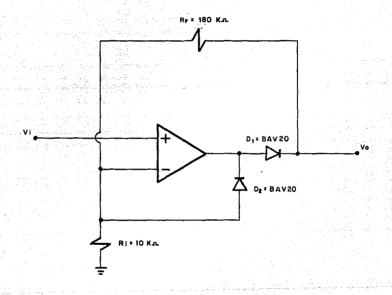

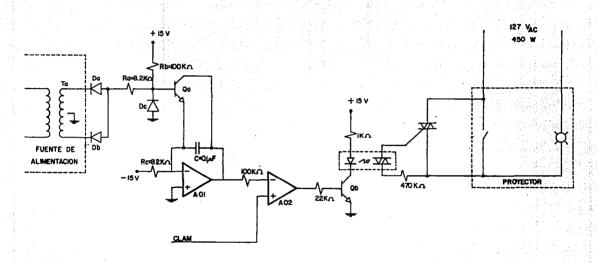

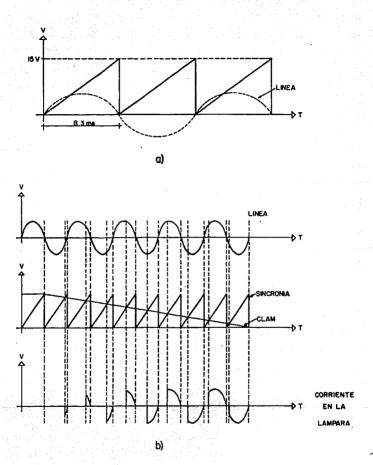

El bloque acondicionador, última parte de la etepa de grabación, tiene como finalidad generar la señal que será grabada en la cinta magnética partiendo de la palabra de control serializada en el bloque anterior.

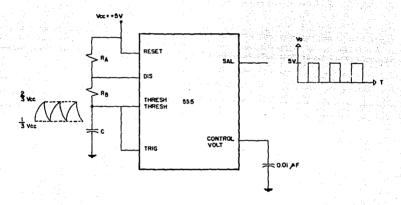

Este bloque está constituído por tres temporizadores (74LS121, 74LS123), un amplificador operacional (741) y los componentes pasivos requeridos para configurar a los circuitos integrados de manera adecuada.

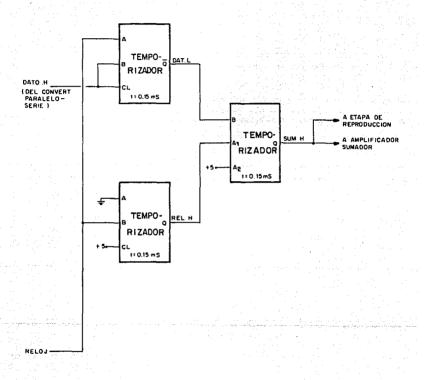

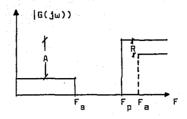

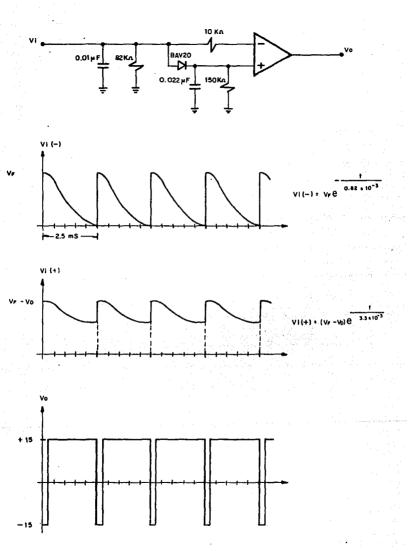

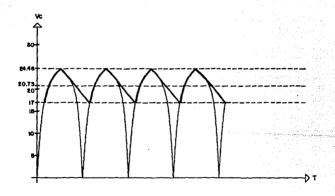

La forma en que el bloque lleva a cabo su función es la siguiente (Fig. 9):

Se tiene un temporizador (74LS123) alimentado por el reloj de señal cuadrada de 200 Hz. el cual está configurado para generar un pulso de 0.15 mS. por cada ciclo de reloj (R = 4.7 Ka, C = 0.1  $\mu$ F, t = 0.28RC(1 + 0.7/R)). La salida del temporizador se denomina -- REL.H.

Figura 8. CONVERTIDOR PARALELO-SERIE

Figura 8. CONVERTIDOR PARALELO-SERIE

Figuro 9. TEMPORIZADORES DE SEÑAL A GRABAR

Por otra parte, otro temporizador (74LS123) tiene como entradas al reloj y a la palabra de control serializada que proviene del bloque de conversión paralelo-serie. En este temporizador se detecta el borde de bajada del reloj y si en ese instante se está presentando un nivel alto en la salida del convertidor (dato = 1) se generará un pulso de 0.15 mS. (R = 4.7 KA, C = 0.1/AF, t = 0.28RC(1 + 0.7/R)). Si la señal que sal del convertidor es un nivel bajo (dato = 0) no a parecerá ningún pulso a la salida del temporizador. Esta salida se denomina DAT.H.

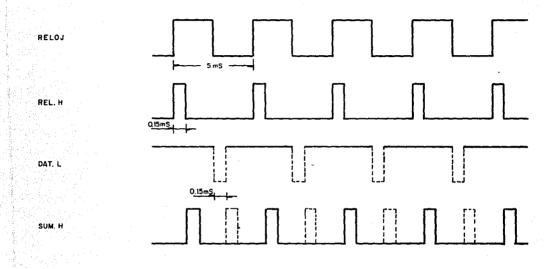

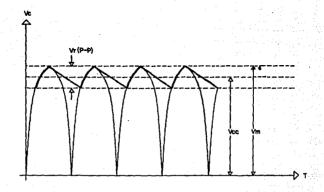

Las señales REL.H y DAT.L (salida negada de DAT.H) entran al último temporizador (74LS121), del cual se obtiene como salida la suma de ambos, SUM.H, con la misma duración para cada pulso (0.15 mS.). La señal - SUM.H tiene una derivación hacia la etapa de reproducción para llevar a cabo la función de ejecución directa de una instrucción, sin pasar por la cinta magnética. Las formas que siguen todas las señales se muestran en la figura 10.

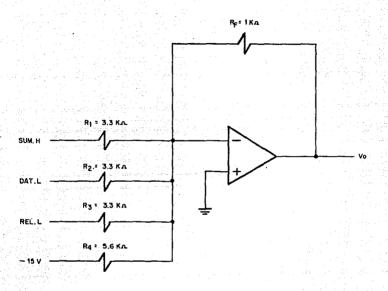

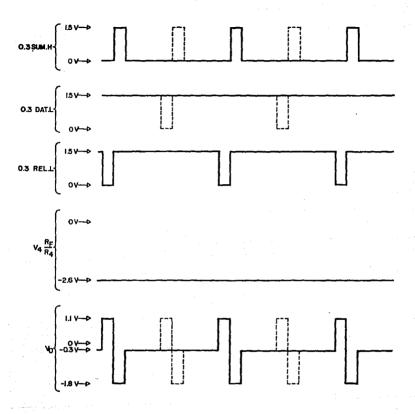

Una vez que se tiene ya el tren de pulsos de reloj y dato (SUM.H), éste debe ser acondicionado a una magnitud adecuada para la grabación en la cinta magnética. Mediante el amplificador operacional del bloque, configurado como sumador, se obtiene un tren de pulsos - bipolar de aproximadamente ±1.5 V., el cual es grabado en la cinta magnética (Fig. 11).

Las señales que se suman son SUM.H, DAT.L, REL.L y un valor fijo de -15 V., con los siguientes pesos dentro de la suma:

Figura 10. SENALES DE TEMPORIZADORES

$$\begin{split} \mathbf{v}_0 &= -(\frac{R_F}{R_1} \ \mathbf{v}_1 \ + \frac{R_F}{R_2} \ \mathbf{v}_2 \ + \frac{R_F}{R_3} \ \mathbf{v}_3 \ + \frac{R_F}{R_4} \ \mathbf{v}_4) \\ \\ \frac{R_F}{R_1} \ \mathbf{v}_1 &= \frac{1000}{3300} \ \text{SUM.H} = 0.3 \ \text{SUM.H} \\ \\ \frac{R_F}{R_2} \ \mathbf{v}_2 &= \frac{1000}{3300} \ \text{DAT.L} = 0.3 \ \text{DAT.L} \\ \\ \frac{R_F}{R_3} \ \mathbf{v}_3 &= \frac{1000}{3300} \ \text{REL.L} = 0.3 \ \text{REL.L} \\ \\ \frac{R_F}{R_4} \ \mathbf{v}_4 &= \frac{1000}{5600} \ (-15) \ = -2.68 \ \text{V}. \end{split}$$

La figura 12 muestra la suma realizada por el amplif<u>i</u> cador en forma gráfica.

En la grabación que se realice del audiovisual siempre se encontrará señal de reloj, y las palabras de control se grabarán de manera secuencial al oprimir el usuario la tecla GRABAR, con lo cual sale una pala

bra hacia la grabadora, y queda la siguiente preparada para salir. Así, las palabras de control que -constituyen el audiovisual quedarán grabadas en la -cinta magnética en las posiciones que el usuario determine, en sincronía con el audio.

Figura 11. SUMADOR DE SENAL A GRABAR

Figura 12. SEÑAL A GRABAR

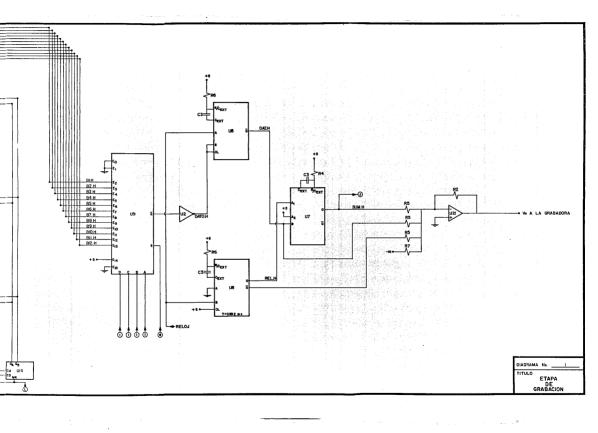

# ETAPA DE CONTROL

#### INTRODUCCION

La operación global del controlador electrónico de proyectores se lleva a cabo por medio de un conjunto de acciones realizadas en la etapa de control. Ejemplos de estas acciones son el almacenamiento secuencial de las instrucciones en la memoria, la grabación de las palabras de control en la cinta magnética en sincronía con el audio, la ejecución directa de una instrucción y otras.

For otra parte, la etapa de control realiza el des-pliegue luminoso de las instrucciones y sus números para el usuario, y le permite revisar y modificar las instrucciones que contiene su audiovisual tanto al  $t\underline{e}$  clearlas como ya almacenadas en la memoria del aparato.

Los bloques funcionales que constituyen la etapa de control son los siguientes (Cap. I, Fig. 4):

- 1. BLOQUE DE TECLAS DE CONTROL.

- 2. BLOQUE CONTROLADOR.

- 3. BLOQUE DE EXHIBICION DE NUMERO DE INSTRUCCION.

- 4. BLOQUE OF EXHIBICION DE INSTRUCCION.

## 2. BLOQUE DE TECLAS DE CONTROL

Este bloque está formado por 9 teclas pertenecientes a los 2 teclados de membrana descritos en el capítulo anterior. Las 9 teclas de control y las 15 teclas programables hacen el total de las 24 teclas comprendidas por los 2 teclados de configuración paralelo de 12 teclas cada uno (Fig. 1).

Eléctricamente la conexión de las teclas de control - es idéntica a la de las teclas programables (Ver Cap. II.2.2). Lógicamente también ambos tipos de teclas son iguales (Ver tabla II.1).

Funcionalmente, las teclas de control se dividen en dos grupos:

Teclas que generan una secuencia de acciones en la etapa de control, las cuales son:

> ENTRAR GRABAR EJECUTAR

Teclas que generan un conjunto de acciones simultánes en la etapa de control, que son:

BORRAR INSTRUCCION

LEER ADELANTE

LEER ATRAS

REGRESO A INICIO

RESTABLECER

ENCENDIDO/APAGADO

| GRABAR            | EJECUTAR               |  |   |        |

|-------------------|------------------------|--|---|--------|

| LEER<br>ADEL ANTE | LEER<br>ATRAS          |  | 3 |        |

| RESTABLECER       | BORRAR<br>INSTRUCCION  |  |   |        |

| ENC. / AP.        | REGRESO<br>A<br>INICIO |  |   | ENTRAR |

TECLADO 1 TECLADO 2

Figura 1. TECLAS DE CONTROL

La descripción funcional detallada de todas las tecclas de control se encuentra en el Capítulo I.

## 3. BLOQUE CONTROLADOR

Este bloque constituye la parte fundamental de la etepa de control, ya que es dentro del cuál se encuen-tran programadas las acciones que deben seguirse para la operación del aparato.

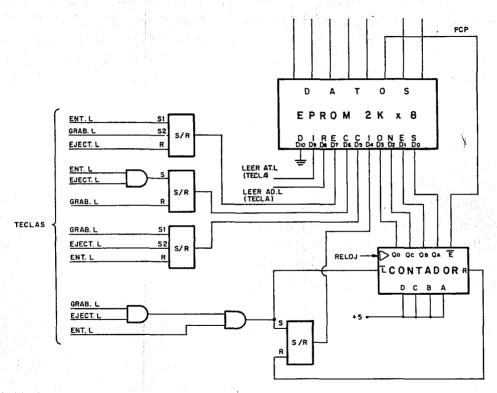

El bloque está formado por una memoria de tipo EPROM de 2K x 8 (2716) y la lógica asociada a las líneas de direcciones y de datos de la memoria, tal como compuertas (74L508, 74L532), latches (74L5279), drivers (74L5367) y un contador binario (74L5191).

## 3.1 LINEAS DE DIRECCION DE LA MEMORIA EPROM

La memoria EPROM 2716 cuenta con 11 líneas de dirección, 8 líneas de datos, una línea de habilitación de salidas de datos y una línea de habilitación del propio circuito integrado.

Las lineas de dirección de la memoria (denotadas por el fabricente como AO a A1O, y denominadas en estetrabajo como DO a D1O) se encuentran asociadas a las diferentes opciones del teclado de la siguiente manera (Fig. 2):

- D10 Nivel bajo permanente

- D9 Conectada a tecla LEER ATRAS

- D8 Conectada a tecla LEER ADELANTE

- D7 Asociada a secuencia EJECUTAR

- D6 Asociada a secuencia GRABAR

- D5 Asociada a secuencia ENTRAR

- D4 Asociada a bit de acarreo de contador

Figura 2. LINEAS DE DIRECCION DE LA EPROM

D2 Conectadas a contador para D1 generación de secuencias D0

Las lineas D9 y D8 presentarán niveles altos permane<u>n</u> tes y sólo bajará de nivel D9 al oprimir la tecla -LEER ATRAS. De igual manera sólo bajará de nivel D8 al ser oprimida la tecla LEER ADELANTE.

Las lineas D7, D6 y D5 se activan de manera excluyente entre si, bajo la condición de que sólo puede estar una tecla oprimida a la vez, o ninguna tecla oprimida. De esta forma, a través de las teclas ENTRAR, GRABAR o EJECUTAR como entradas hacia los latches se obtiene la siquiente tabla:

| TECLA                                 | DIRECCIONES                                                |

|---------------------------------------|------------------------------------------------------------|

| ENTRAR GRABAR EJECUTAR                | D5 D6 D7.                                                  |

| 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 | D5 ant D6 ant D7 ant C 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 |

Tabla 1

Las lineas D3, D2, D1 y D0 están conectadas a las lineas de salida  ${\bf Q}_{\rm D}$ ,  ${\bf Q}_{\rm E}$ ,  ${\bf Q}_{\rm B}$  y  ${\bf Q}_{\rm A}$  de un contador binario alambiado en forma de contador programado.

El contador programado funciona de la siguiente manera:

Al seleccionar el usuario una de las tres secuencias, ENTRAR, GRABAR o EJECUTAR, la lógica formada por dos compuertas AND genera un nivel bajo mediante el cual el contador recibe la orden de realizar la carga de datos en paralelo (niveles altos). Por otra parte, el latch de bit de scarreo de contador (D4) es llevado a nivel alto.

El contador inicia su cuenta descendente desde 1111 - hasta 0000. En la última cuenta se presenta un pulso de nivel bajo en el RIPPLE CLOCK, lo cual causa, junto con la condición de ninguna tecla oprimida, que el latch de acarreo cambie a nivel bajo. La cuenta reinicia y es detenida cuando la secuencia llega a su fin deshabilitando al contador a través de una de las líneas de dato (SC5) de la memoria EPROM.

Se mantienen a las salidas del contador los valores - que se encontraban presentes al momento de ser deshabilitado, y en la salida del latch de acarreo el valor posterior a su último cambio. De esa forma permanecen las líneas de dirección OO a D4 de la EPROM, hasta que se genere una nueva secuencia o instrucción por medio del teclado.

Las lineas de dirección D8 y D9, conectadas a las teclas LEER ADELANTE y LEER ATRAS respectivamente, posicionan a la EPROM en direcciones cuyo contenido genere las acciones correctas en los diferentes circuitos integrados que intervienen en la lectura de palabras de control almacenadas en la RAM. Al programar el -

contenido de las instrucciones LEER ADELANTE y LEER A TRAS se ha tomado en consideración que las líneas DO a D4 pueden presentar diferentes valores, dependiendo de la secuencia con la cual se haya detenido el contador.

A continuación se muestran las tablas de direcciones en memoria EPROM asociadas a cada secuencia e instrucción.

| ſ |                         |      | SECI | JENO                 | IA EN         | TRAF | planya sigili.<br>Mananasi |    |             |

|---|-------------------------|------|------|----------------------|---------------|------|----------------------------|----|-------------|

| - | D10 (                   | 9 DI | 3 D7 | D6                   | D5 D4         | D3   | D2 D1                      | DO | HEXADECIMAL |

| ľ | n                       | 1    | 1 1  | 1                    | 0 1           | 1    | 1 1                        | 1  | 3DF         |

| ľ | 0                       | 1 -  | 1 1  | -1                   | 0 1           | 1    | 1 1                        | 0  | 3DE         |

| ŀ | 0                       | 1    | 1 1  | 1                    | o 1           | 1    | 1 0                        | 1  | 3DD         |

| ı | . 0                     | 1    | 1 1  | 1                    | 0 1           | 1    | 1 0                        | 0  | 3DC         |

| ŀ | 0                       | 1    | 1 1  | 1                    | 0 1           | 1    | 0 1                        | 1  | 3DB         |

| ١ | 0                       | 1    | 1 1  | 1                    | 0 1           | 1    | 0 1                        | 0  | 3DA         |

| l | 0                       | 1    | 1 1  | 1                    | 0 1           | 1    | 0 0                        | 1  | 309         |

| 1 | 0                       | 1    | 1 1  | 1                    | 0 1           | 1    | 0 0                        | 0  | 308         |

| l | 25, 27 47<br>- 51, 4 14 |      |      | er 1825<br>2017 (d.) | 9-7-0<br>1-21 |      |                            | 54 |             |

Tabla 2

| T.,   |     | 58  | CUI | ENC) | À ( | SRAI | BAR        |     |          |     |             |

|-------|-----|-----|-----|------|-----|------|------------|-----|----------|-----|-------------|

| D 10  | D9  | DB  | D7  | D6   | D5  | D4   | D3         | D2  | D 1      | DO  | HEXADECIMAL |

| 0     | 1   | 1   | 1   | 0    | 1   | 1    | 1          | 1   | 1        | 1   | 38F         |

| . 0   | 1   | 1   | 1   | 0    | 1   | 1    | 1          | . 1 | 1        | 0   | 3BE         |

| 0     | 1   | . 1 | 1   | 0    | 1   | 1    | 1          | 1   | 0        | 1   | 38D         |

| 0     | 1   | 1   | 1   | 0    | 1   | 1    | 1          | 1   | 0        | 0   | 38C         |

| 0     | 1.  | 1   | 1   | 0    | 1   | 1    | 1          | 0   | 1        | 1   | 388         |

| 0     | 1   | 1   | 1   | 0    | 1   | 1    | 1          | 0   | 1        | 0   | 38A         |

| 0     | 1-1 | 1   | 1   | 0    | 1.1 | . 1  | 1          | . 0 | ۵        | 1   | 389         |

| 0     | 1   | 1   | 1   | 0    | 1   | . 1  | 1          | . 0 | 0        | 0   | 388         |

| : O   | 1   | 3.1 | . 1 | . 0  | 1.  | . 1  | 0          | _ 1 | _1       | 1   | 387         |

| . 0   | . 1 | 1   | 11. | .0   | 1   | 1    | D          | . 1 | 1        | 0   | 386         |

|       | 1   | 1   | 1   | . 0  | 1   | 1    | 0          | 1   | 0        | 1   | 385         |

| . · O | 1   | 1   |     | . 0  | 1   | 1    | <b>0</b>   | 1   | 0        | 0   | 3B4         |

| . 0   | . 1 | 1   | 1   | 0    | 1   | 1    | . 0        | 0   | .1       | 1   | 3B3         |

| · / O | 1   | 1   | - 1 | 0    | -1  | .1   | . 0        | 0   | <b>1</b> | 0   | 382         |

| 0     | 1   | -1  | 1   | Ō    | 1   | 1    | <b>,</b> 0 | 0   | 0        | 1   | 381         |

| . O.  | 1   | 1   | 1   | . 0  | -1  | -1   | 0          | 0   | 0        | 0   | 380         |

| . 0   | 1   | 1   | .1  | 0    | 1   | 0    | 1          | 1.  | 1        | 1   | 3AF         |

| 0     | . 1 | 1   | 1   | ٥    | 1   | 0    | 1          | 1   | 1        | 0   | 3AE         |

| . 0   | 1   | 1,  | 1   | 0    | 1   | 0    | 1.         | 1   | ្ល       | · 1 | 3AD         |

Tabla 3

|            |          | SE | CUE                | NCI     | A E  | JEC    | UTA   | R            |     |         |             |

|------------|----------|----|--------------------|---------|------|--------|-------|--------------|-----|---------|-------------|

| D 10       | D9       | DB | D7                 | 06      | D5   | D4     | D3    | D2           | 01  | DO      | HEXADECIMAL |

|            |          |    |                    | •       |      |        |       |              |     |         |             |

| 0          | 1        | 1  | 0                  | 1       | 1    | 1      | 1     | 1            | 1   | 1       | 37F         |

| a          | 1        | 1  | 0                  | 1       | 1    | 1      | . 1   | 1            | 1   | 0       | 37E         |

|            | 1        | 1  | 0                  | 1       | 1    | 1      | 1     | 1            | 0   | - 1     | 370         |

| 0          | . 1      | 1  | 0                  | 1       | 1    | 1      | 1     | 1            | 0   | 0       | 37C         |

| <b>O</b> _ | 1-       | 1. | _0                 | 1       | -1   | 1      | 100   |              | 1   | _1      | 378         |

| . 0        | 1.       |    | MATERIAL PROPERTY. | 1       | 1    | 1      | 经证明   |              | 1   | 100 P   | 37A         |

| 0          | 1        | 1  | 0                  | 1       | 1    | 1      | 1     |              | _ 0 | 1       | 379         |

| 0          | 1        |    | 0                  | . 1     | 1    | 1      |       | _0           | .0  | 116.1   | 378         |

| 0          | 1        | 1  | 0                  | 1       | 1.1  | 1      | 0     | 223          | 1   | 100     | 377         |

| 0.         | 1        | _1 | 0                  | 1       | 1    | 1      | 72700 | 1            | 1   | 0.<br>1 | 376<br>375  |

| 0          | -1<br>-1 | 1  | 0                  | .1<br>1 | . 1  | 1<br>1 |       | 1            | . 0 | 0       | 374         |

| 0          | 1        |    | 0                  | 1       | 1    | 1      | 100   | 0            | 1   | 198     | 373         |

| 0          | 1        | 1  | 0                  | 1       | 1    | 1      | 0     | 0            |     | 0       | 372         |

| 0          | 1        | 1  | 0                  | 1       |      | 1      | Ö     | O            |     | 1       | 371         |

| 0          | 1        | 1  | 0                  | 1       | 1.75 | 1      | 0     | 0            | 0   | 0       | 370         |

| 0          | 1        | 1  | 0                  | 1       | 1    | 0      | 1     | $x_{2n+1,k}$ | 1   |         | 36F         |

| 0          | 1        | 1  | 0                  | 1       | 1    | 0      | 1     | 1            | 1   | 0       | 36E         |

| 0          | 1        | 1  | 0                  | 1       | 1    | 0      | 1     | . 1          | 0   | 1       | 36D         |

| 0          | 1        | 1  | 0                  | 1       | 1    | 0      | 1     | 1            | 0   | . 0     | 36C         |

|            | . 2      |    |                    |         |      |        |       |              |     |         |             |

Tabla 4

|     | IN                          | STR | UCC | ION | LE  | ER  | ADE | LAI | VTE |    |                                                 |

|-----|-----------------------------|-----|-----|-----|-----|-----|-----|-----|-----|----|-------------------------------------------------|

| 010 | D9                          | DB  | D7  | D6  | 05  | D4  | D3  | D2  | D 1 | 00 | HEXADECIMAL                                     |

| Des | Después de secuencia ENTRAR |     |     |     |     |     |     |     |     |    |                                                 |

| 0   | 1                           | 0   | 1   | 1   | 0   | 1   | 1   | 8   | 0   | 0  | 208                                             |

| Des | pués                        | dе  | 88  | cne | nci | a G | RAE | AR  |     |    | in the beau                                     |

| 0   | 1                           | 0   | 1   | O   | 1   | 0   | 1   | 1   | 0   | 1  | 2AD                                             |

| Des | pués                        | de  | se  | cns | nci | a E | JE  | UT  | IR. |    |                                                 |

| 0   | 1                           | 0   | 0   | 1   | 1,  | 0   | 1   | 1   | 0   | 0  | 260                                             |

| ٠   |                             |     |     |     |     |     |     |     |     |    | Lavaren eta |

Tabla 5

|      |      |     |     |     |      |     |     |     |    |                   | <del></del>  |

|------|------|-----|-----|-----|------|-----|-----|-----|----|-------------------|--------------|

| 1    | IN.  | STR | UCC | 104 | I LE | E₽  | ATR | RAS |    |                   |              |

| D 10 | D9 ( | B0  | D7  | D6  | D5   | D4  | D3  | DZ  | D1 | DO.               | HEXADEC IMAL |

| Deat | ués  | dе  | 96  | cue | nci  | a E | NTA | AR  |    |                   |              |

|      | D    | 1   | 1   | 1   | O    | 1   | 1   | 0   | 0  | 0                 | 108          |

| 1    |      |     |     |     |      |     |     |     |    |                   |              |

| Dear | ués  | de  | SE  | cne | nci  | a G | RAB | AR  |    |                   |              |

| 0    | 0    | 1   | 1   | 0   | 1    | 0   | 1   | . 1 | 0  | 1                 | 1AD          |

| 1    |      |     |     |     |      | 1.  | 4.5 |     |    |                   |              |

| Deat | ués  | ₫€  | se  | cue | nci  | a E | JEC | UTF | R  | ر شورو ده از<br>ا |              |

| 0    | Q    | 1   | 0 - | 1   | 1    | 0   | 1   | 1.  | 0  | 0                 | 16C          |

| 1.   |      |     |     |     |      |     |     |     |    |                   | e da Section |

Table 6

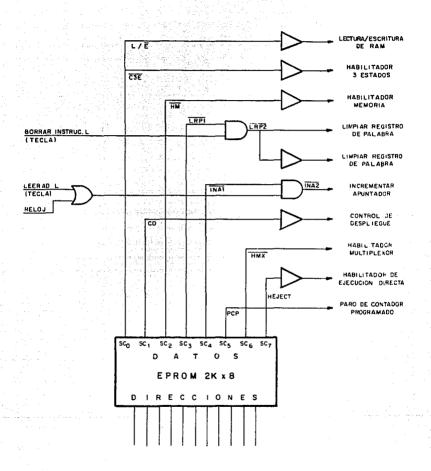

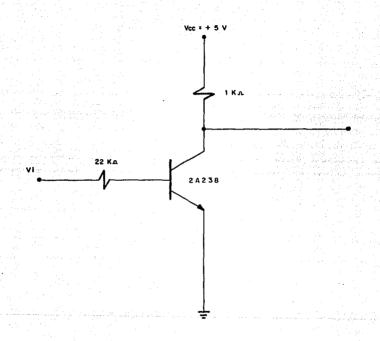

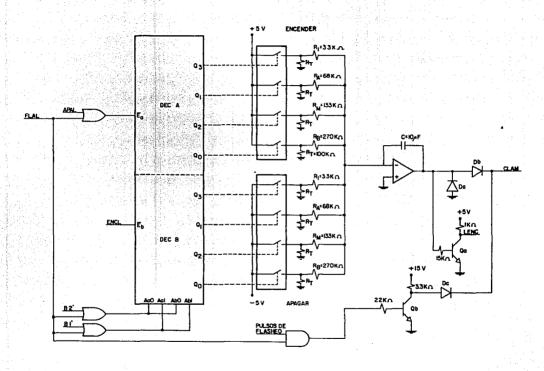

### 3.2 LINEAS DE DATOS DE LA MEMORIA EPROM

Las líneas de datos con las que cuenta la memoria -EPROM 2716 son 8. Estas líneas (denotadas por el fa

bricante como QO a Q7 y denominadas en este trabajo como SCO a SC7) son las salidas de control que comandan la acción de diferentes circuitos integrados de manera conjunta, con la finalidad de realizar las fun

ciones que el aparato está diseñado para poder llevar

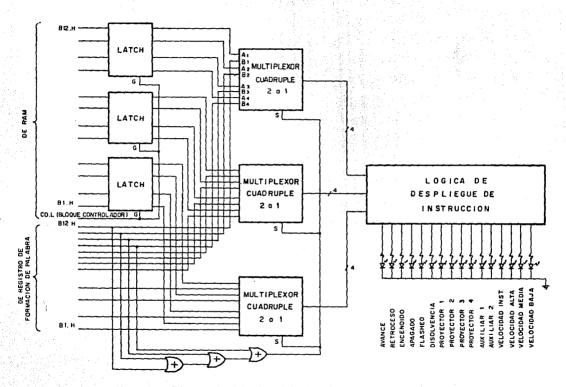

Las lineas de señales de control (SC) están asociadas a los diferentes circuitos integrados de la siguiente manera (Fio. 3):

- SCO Controla la lectura y escritura a la memoria RAM (L/E) y habilità el circuito tres estados que está conectado a las líneas de datos de la memoria (C3E) según se trate de leer o de escribir.

- SC1 Tiene por función el control de despliegue de las instrucciones que están almacenados en la memoria RAM (CD), de acuerdo al despliegue de número de instrucción.

- SC2 Habilita la memoria RAM cuando en la secuencia que se está ejecutando se leerá o escribirá en ella (HM).

- SC3 Su función es limpiar el registro de formación de pelabra una vez que se ha terminado de teclear una instrucción y se da entrada a memoria (LRP1), o bién si el usuario desea eliminar lo que ha tecleado y reiniciar la formación de su

Figura 3. LINEAS DE DATOS DE LA EPROM

instrucción (LRP2).

- SC4 Una vez que se ha tecleado ENTRAR, GRABAR o EJE

CUTAR, esta línea incrementa la dirección de la

memoria RAM (INA1), o si el usuario desea se-guir el contenido de la memoria, va incremen-tando la dirección a una cierta velocidad fijada en un reloj.

- SC5 Detiene al propio contador de dirección de la memoria EPROM una vez que la secuencia ejecuta-da ha terminado (PCP).

- SC6 Habilita el multiplexor que realiza la función de convertidor paralelo-serie (HMX).

- SC7 Habilita la ejecución directa de la instrucción en lugar de que sea grabada a cinta magnética y posteriormente reproducida (HEJECT).

Todas estas líneas de control son pasadas a través de drivers de acuerdo al tipo y cantidad de circuitos integrados que haya que alimentar, para protección de la memoria EPROM.

A continuación se presenta una tabla que resume las funciones de cada una de las líneas de control.

| LINEA DE<br>CONTROL | SEÑAL QUE<br>GENERA | FUNCION                                              |

|---------------------|---------------------|------------------------------------------------------|

| sco                 | L/Ē<br>C3E          | Selección lect./esc. RAM<br>Control 3Est. lineas RAM |

| SC1                 | CD                  | Control de despliegue                                |

| SC2                 | нм                  | Habilitar RAM                                        |

| SC3                 | LRPT                | Limpiar reg. formac. pal.                            |

| SC4                 | INA 1               | Incrementar direc. RAM                               |

| SC5                 | PCP                 | Parar contador programado                            |

| 506                 | HMX<br>·            | Habilitar multiplexor                                |

| SC7                 | нејест              | Habilitar ejec. directa                              |

|                     | <u>l</u>            |                                                      |

Tabla 6

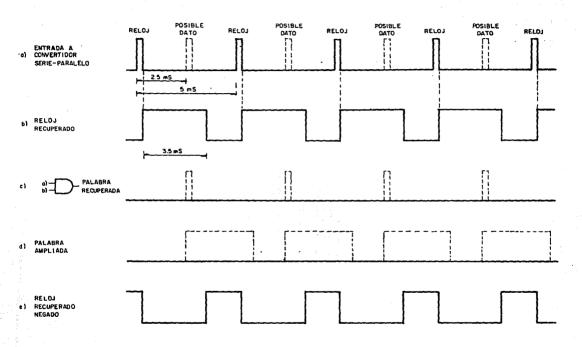

Las tres secuencias programadas en la mamoria EPROM para control del aparato son ENTRAR, GRAPAR y EJECU-TAR.

ENTRAR tiene como función dar entrada a la memoria RAM a una instrucción, una vez que ya ha sido tecleada por el usuario. Esta secuencia se activa oprimiendo la tecla del mismo nombre.

GRABAR tiene como función sacar la instrucción de una localidad de la memoria RAM, hacerle la conversión paralelo-serie y enviarla hacia el acondicionador de señal a grabar. Se activa a través de la tecla del -mismo nombre.

EJECUTAR tiene como función tomar una instrucción que ya ha sido tecleada por el usuario e introducida a me moria, y paserla hacia los actuadores. Esto permite comprobar el efecto de cierta instrucción sobre los proyectores y auxiliares sin tener que grabarla y reproducirla. Se activa mediante la tecla del mismo prombre.

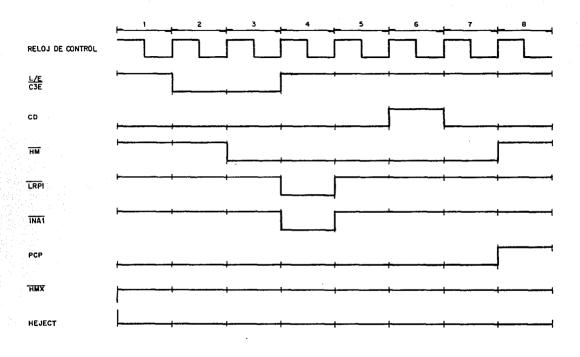

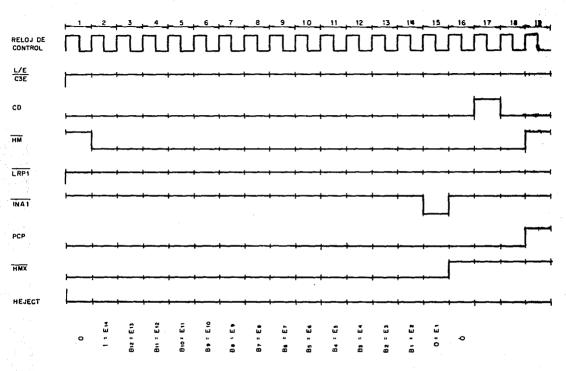

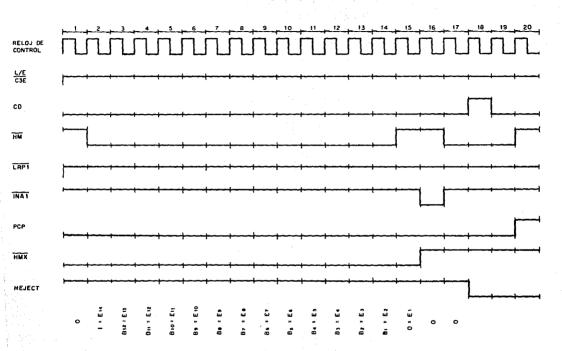

A continuación se presentan las tablas que siguen cada una de las tres secuencias en las líneas de control de la memoria EPROM. Se muestran también los cronogramas correspondientes a cada secuencia en las figuras 4, 5 y 6 respectivamente, en relación al reloj que genera la cuenta en las líneas de direcciones D3, D2, D1 y D0 de la EPROM.

Figuro 4. CRONOGRAMA DE SECUENCIA ENTRAR

Figura 5. CRONOGRAMA DE SECUENCIA GRABAR

Figura 6. CRONOGRAMA DE SECUENCIA EJECUTAR

| DIRECCION | LINEAS DE CONTROL               | ACCIONES QUE SE GENERAN                                    |

|-----------|---------------------------------|------------------------------------------------------------|

| EPROM     | SC0 SC1 SC2 SC3 SC4 SC5 SC6 SC7 | SECUENCIA ENTRAR                                           |

| 3DF       | 1 0 1 1 1 0 1 0                 |                                                            |

| 3DE       | <u> </u>                        | Hab. Esc. RAM/Hab. 3 estados                               |

| 300       | 0 0 <u>0</u> 1 1 0 1 0          | Hab. RAM                                                   |

| 3DC       | 1 0 0 0 0 1 0                   | Deshab. Esc. RAM/Deshab. 3<br>est./Limpiar Reg./Inc. Apunt |

| 30B       | 1 0 0 1 1 0 1 0                 |                                                            |

| 3DA       | 1 <u>1</u> 0 1 1 0 1 0          | Gen. despliegue sig. instr.                                |

| 309       | 1 0 0 1 1 0 1 0                 |                                                            |

| 3DB       | 1 0 1 1 1 1 1 0                 | Deshab. RAM/Parar contador                                 |

Table 7

| DIRECCION<br>EPROM | sco      | SC1 | LINE<br>SC2 | AS DE<br>SC3 |          | ROL<br>SC5 SC6 | EC7 | ACCIONES QUE SE GENERAN<br>SECUENCIA GRABAR |  |

|--------------------|----------|-----|-------------|--------------|----------|----------------|-----|---------------------------------------------|--|

| 38F                | .,       | G   | 1           | 1            | 1        | <u>0</u> 0     |     | Hab. Mux./Multiplexaje                      |  |

| 38E                | 111      |     | . 0         | 1            | 1        | 0 0            | 0   | Hab. RAM/ Multiplexaje                      |  |

| 380                | 12.00 MA | ū   | 0           | 1            | 1        | 0 0            | 0   | Multiplexaje                                |  |

| 38C                | 1        | Ö   | 0           | 1            | 1        | 0 0            | 0   | Multiplexaje                                |  |

| 38B                | 1        | . 0 | 0           | 1,1          | 1        | 0 0            | 0   | Multiplexaje                                |  |

| 3BA                | 1        | 0   | .0          | 1.           | 1        | 0 0            | a   | Multiple×aje                                |  |

| 389                | 1        | D   | ا و         |              | 1        | 0 0            | 0   | Multiplexaje                                |  |

| 388                | 1        | 0   | 0           | 1            | 1 1      | 0 0            | 0   | Multiplexaje                                |  |

| 387                | 1        | 0   | . 0 -:      | 1            | 1        | 0 0            | 0   | Multiplexaje                                |  |

| 386                | 1        |     | 0           | 1            | 1 1      | 0 0            | 0   | Multiple×aje                                |  |

| 385                | 1        | 0   | 0           | ì            | 1        | 0 0            | 0   | Multiplexaje                                |  |

| 3B4                | 1        | 0   | 0.          | 1 :          | 1        | 0 0            | 0   | Multiplexaje                                |  |

| 383                | 1        | . 0 | . o         | 1            | . 1      | .0 0           | 0   | Multiplexaje                                |  |

| 3B2                | 1        | 0.  | 0           | 1            | 1        | 0 0            | 0   | Multiplexaje                                |  |

| 381                | 1        | 0   |             | 1            | <u>o</u> | 0 0            | 0   | Inc. Apunt. RAM/Multiplexaj                 |  |

| 380                | 1        |     | " <b>D</b>  | 1            | 1        | 0 1            | 0   | Deshab. Mux.                                |  |

| 3AF                | 1        | 1   | 0           | 1.           | 1        | 0 1            | 0   | Gen. despliegue sig. instr.                 |  |

| 3AE                | 1        | 0   | o.          | 1            | 1        | 0 1            | 0   |                                             |  |

| 3AD                | 1        | . 0 | 1           | 11           | 1        | 1 1            |     | Deshab RAM/Parar contador                   |  |

Tabla 8

| DIRECCION |      |      | LINE           | AS DE | CONT         | ROL |          |     | ACCIONES QUE SE GENERAN                        |

|-----------|------|------|----------------|-------|--------------|-----|----------|-----|------------------------------------------------|

| EPROM     | SCO  | SC1  | SC2            | 503   | SC4          | SC5 | SC6      | 5¢7 | SECUENCIA EJECUTAR                             |

| 1111      |      |      |                | -     |              |     |          |     |                                                |

| 37F       | 1    | ۵    | 1              | . 1   | . 1          | . 0 | 0        | 1   | Hab. Mux/Hab. Ejec. Dir./Mu<br>tiplexaje       |

| 37E       | 1    | 0    | 0              | - 1   | 1            | 0   | ٥        | 1   | Hab. RAM/Multiplexeje                          |

| 37D       | 1    | 0    | Ð              | 1     | 1.           | 6   | 0        | 1   | Multiplexaje                                   |

| 37C       | 1    | 0    | 0              | - 1   | 1            | 0   | 0        | 1   | Multiplexaje                                   |

| 378       | 1    | ĪO . | 0              | 1     | . 1          | 0   | 0        | 1   | Multiple×aje                                   |

| 37A       | 1    | 0    | . 0            | 1     | 1            | . 0 | 0        | 1   | Multiplexaje                                   |

| 379       | 1    | 0    | 0              | 1     | 1            | 0   | D        | 1   | Multiplexaje                                   |

| 378       | 1.1  | 0    | 0              | 1     | 1            | 0   |          | 1   | Multiplexaje                                   |

| 377       | 1.   | 0    | 0              | 1,    | 1            | 0   | Ð        | 1   | Multiplexaje                                   |

| 376       | 1    | 0    | 0              | 1     | 1            | 0   | 0        | 1   | Multiplexaje                                   |

| 375       | 1    | 0 :  | 0              | 1.1   | 1            | . 0 | 0        | . 1 | Multiple×aje                                   |

| 374       | 1    | 0    | 0              | 1     | 1            | 0   |          | 1   | Multiplexaje                                   |

| 373       | 1    | 0    | • 0            | 1     | 1            | - 0 | 0        | 1   | Multiplexaje                                   |

| 372       | 1    | 0 :  | . 0            | . 1   | 1            | . 0 | D        | 1   | Multiplexaje                                   |

| 371       | 1    | 0    | 1              | 1     | 1            | 0   | ß        | 1   | Deshab. RAM/ Multiplexaje                      |

| 370       | 1    | - O  | 1              | 1     | <u>o</u>     | 0   | <u>i</u> | 1   | Deshab. Mux./Inc. Apunt. RA                    |

| 36F       | 1.   | 0    | <u>. o</u> ::  | 1     | 1            | 0   | 1        | 1   | Hab. RAM                                       |

| 36E       | 1    | 1.,  | 0              | .1    | 1            | 0   | 1        | 0   | Gen. despl. sig. inst./Des-<br>hab. Ejec. Dir. |

| 36D       | 1.1. | 0    | . <b>a</b> .(1 | 1     | (1) <b>1</b> | 0   | 1        | 0   |                                                |

| 36C       | 1    | 0    | 1              | 1     | 1            | 1   | 1        |     | Deshab. RAM/Parar contador                     |

Tabla 9

Además de las tres secuencias ya descritas, en la -EPROM están también programadas las acciones que se deben ejecutar al oprimir el usuario las teclas LEER

ADELANTE o LEER ATRAS.

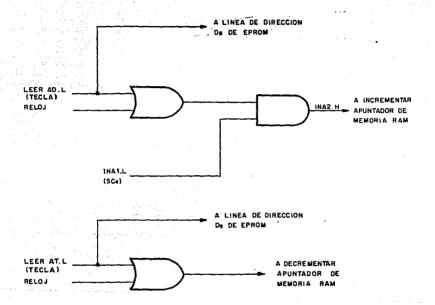

LEER ADELANTE tiene como función incrementar la dirección de la memoria RAM y presentar al usuario mediante los despliegues, el número de esa siguiente instrucción y el propio contenido de la misma. Si se oprime la tecla instantaneamente, se incrementará

en uno la dirección de la memoria, y si se mantiene o

primida, el incremento se vuelve continuo a la veloci

dad que se fije en un reloj empleado para lograr esto

(Fig. 7).

La función de LEER ATRAS difiere de la de LEER ADELAN TE únicamente en que decrementa la dirección en lugar de incrementarla.

La memoria EPROM después de ejecutar alguna de sus tres secuencias se encuentra en una de las siguientes direcciones (Tablas 2, 3 % 4):

> 308 Final de ENTRAR 3AD Final de GRABAR 36C Final de EJECUTAR

Como la tecla LEER AOELANTE se encuentra conectada a D8 y LEER ATRAS a D9, al oprimirse alguna de estas teclas se presentarán las direcciones mostradas en las tablas 5 (para LEER ADELANTE) y 6 (para LEER ATRAS).

En la tabla 10 se muestra el contenido de las líneas de control para las instrucciones de LEER ADELANTE y LEER ATRAS.

Figuro 7. LEER ADELANTE Y LEER ATRAS

| ۰ |   |  |

|---|---|--|

| 4 | ↘ |  |

|   |   |  |

| LINEAS DE CONTROL<br>SCO SC1 SC2 SC3 SC4 SC5 SC6 SC7 | ACCIONES QUE SE GENERÂN                                                                               |

|------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

|                                                      |                                                                                                       |

|                                                      |                                                                                                       |

|                                                      | [ ] [ ] - [ ] - [ ] - [ ] - [ ] - [ ] - [ ] - [ ] - [ ] - [ ] - [ ] - [ ] - [ ] - [ ] - [ ] - [ ] - [ |

|                                                      | Hab. RAM/Parar contador/                                                                              |

| 1 1 0 1 1 1 1 0                                      | Gen. despliegue sig. inst.                                                                            |

| 는 '' - '' - '' - '' - '' - '' - '' - ''              |                                                                                                       |

|                                                      |                                                                                                       |

| r : [ - 기급 (호텔 전략 전략 기계 :                            |                                                                                                       |

|                                                      | [                                                                                                     |

|                                                      | Hab. RAM/Parar contador/                                                                              |

|                                                      |                                                                                                       |