300617

# UNIVERSIDAD LA SALLE

# ESCUELA DE INGENIERIA

INCORPORADA A LA

UNIVERSIDAD NACIONAL AUTONOMA DE MEXICO

DISEÑO DE UN MICROCOMPUTADOR PARA UN CONTROLADOR DE PROCESOS DE PROPOSITO GENERAL

T E S I S

QUE PARA OBTENER EL TITULO DE

INGENIERO MECANICO ELECTRICISTA (AREA PRINCIPAL EN ELECTRONICA)

PRESENTA:

JOSE GUILLERMO ARANDA PEREZ

TESIS CON FALLA DE ORIGEN

MEXICO, D. F.

1986

# UNAM – Dirección General de Bibliotecas Tesis Digitales Restricciones de uso

# DERECHOS RESERVADOS © PROHIBIDA SU REPRODUCCIÓN TOTAL O PARCIAL

Todo el material contenido en esta tesis está protegido por la Ley Federal del Derecho de Autor (LFDA) de los Estados Unidos Mexicanos (México).

El uso de imágenes, fragmentos de videos, y demás material que sea objeto de protección de los derechos de autor, será exclusivamente para fines educativos e informativos y deberá citar la fuente donde la obtuvo mencionando el autor o autores. Cualquier uso distinto como el lucro, reproducción, edición o modificación, será perseguido y sancionado por el respectivo titular de los Derechos de Autor.

# INDICE

|                                                           | PAGINA |

|-----------------------------------------------------------|--------|

| CAPITULO 1.                                               |        |

| INTRODUCCION.                                             |        |

| a) Alcances                                               | 05     |

| b) Aplicaciones                                           | 08     |

| CAPITULO II.                                              |        |

| DESCRIPCION GENERAL DEL MICROCOMPUTADOR.                  |        |

| a) Alternativas del Diseño                                | 10     |

| b) Selección y Justificación de la Alternativa a Realizar | 11     |

| CAPITULO III.                                             |        |

| DISERO DE LA TARJETA HADRE.                               |        |

| a) Descripción                                            | 14     |

| b) Especificación de las Señales                          | 16     |

| CAPITULO IV.                                              |        |

| disero de la tarjeta de procesamiento.                    |        |

| a) Descripción y Especificaciones Generales               | 19     |

| b) Dimeño del Circuito                                    | 21     |

| CAPITULO V.                                               |        |

| DISEÑO DE LA TARJETA DE MEMORIA.                          |        |

| a) Descripción y Especificaciones Generales               | 40     |

| b) Diseño del Circuito                                    | 40     |

# CAPITULO VI.

| DISEÑO DE LA TARJETA DE ENTRADAS Y SALIDAS DE SEÑALES DIGITALES.                                   |   |

|----------------------------------------------------------------------------------------------------|---|

| a) Descripción y Especificaciones Generales                                                        | 4 |

| b) Diseño del Circuito                                                                             | 4 |

| CAPITULO VII,                                                                                      |   |

| DISEÑO DE LA TARJETA DE ENTRADAS Y SALIDAS DE SEÑALES ANALOGICAS.                                  |   |

| a) Descripción y Especificaciones Generales                                                        | 5 |

| b) Diseño del Circuito                                                                             | 6 |

| CAPITULO VIII.                                                                                     |   |

| TEORIA DE OPERACION                                                                                | 7 |

| CAPITULO IX.                                                                                       |   |

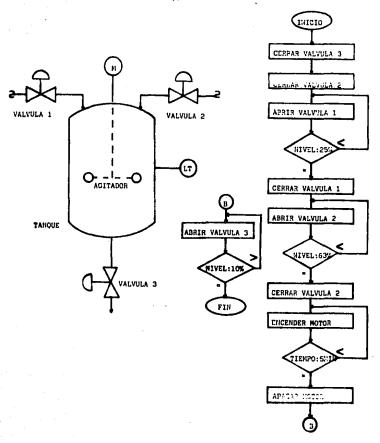

| EJEMPLO DE CONTROL DE UN PROCESO                                                                   | 7 |

| CONCLUSIONES                                                                                       | 8 |

| BIBLIOGRAFIA                                                                                       | 8 |

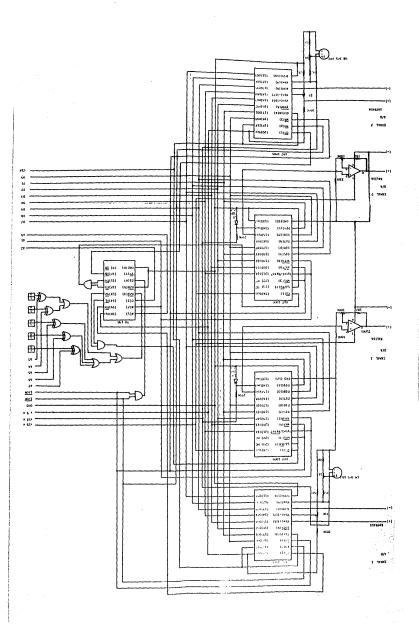

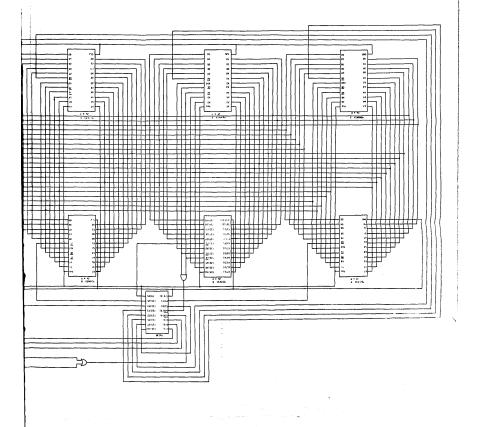

| APENDICE A. Diagrama del Circuito de la Tarjeta de Procesamiento.                                  |   |

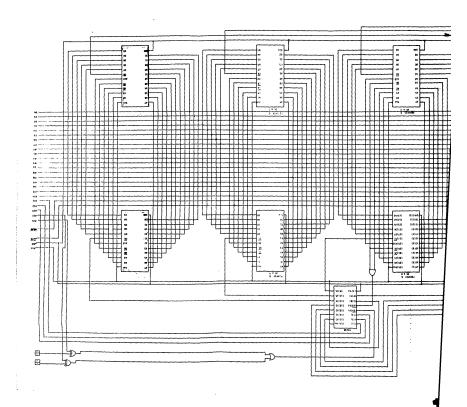

| APENDICE B. Diagrama del Circuito de la Tarjeta de Memoria.                                        |   |

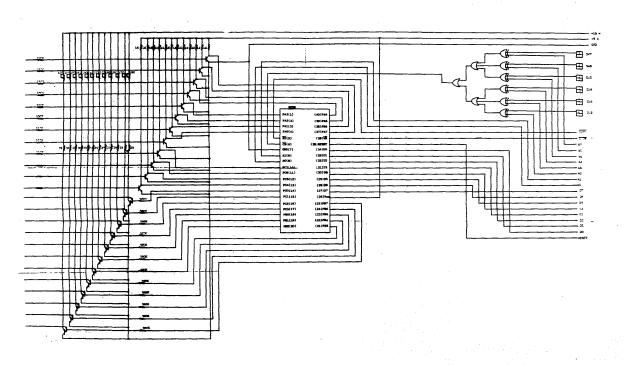

| APENDICE C.<br>Diagrama del Circuito de la Tarjeta de<br>Entradas y Salidas de Señales Digitales.  |   |

| APENDICE D.<br>Diagrama del Circuito de la Tarjeta de<br>Entradas y Salidas de Señales Analógicas. |   |

# CAPITULO I

#### INTRODUCCION

#### a) Alcances

Debido al gran desarrollo de las computadoras en la década pasada y en lo que va de ésta, el uso de ellas es cada vez más frecuente en diferentes aplicaciones. El control y monitoreo de procesos no podía ser la excepción y es por ésto que se utiliza para aplicaciones que van desde la adquisición de datos a través de una computadora central, hasta el control de variables de proceso por medio de un microcomputador localizado en campo (control distribuido).

El uso de computadoras y microcomputadoras en el control de procesos permite obtener el producto manufacturado en la cantidad prevista por los diseñadores para su proceso de obtención y con la calidad esperada por el cliente, lo cual capturará la mayoría del mercado permitiendo mejores precios al consumidor y más utilidades para el empresario. Coordinar el volumen de producción con la mejor calidad requiere de un riguroso control de cada una de las etapas del proceso, además del empleo de buenas materias primas.

El propósito de este trabajo es el diseño de un microcomputador para el control de procesos. Básicamente un microcomputador está constituído por uno o más circuitos integrados, usando tecnología de semiconductores y lógica digital para implementar funciones de alto nivel computacional en un volumen pequeño.

Existen tres elementos principales en una microcomputadora, los cueles son: la unidad central de procesamiento (CPU); la memoria y los dispositivos de entrada y salida (I/O).

La CPU es el corazón del sistema microcomputador y ejecuta los processos numéricos, las operaciones lógicas y las funciones de tiempo. Una CPU típica consiste de tres unidades funcionales que son: los registros; la unidad aritmética lógica (ALU) y la circuiteria de control. Los registros permiten almacenar temporalmente direcciones de memoria, códigos de estado y alguna otra información necesaria para la ejecución de un programa. La unidad aritmética lógica contiene un suador para ejecutar operaciones aritméticas en forma binaria de los datos obtenidos de memoria, los registros u otras entradas. Algunas unidades aritmética lógicas ejecutan operaciones más complejas, tales como: multiplicación y división. También contienen bits de bandera que señalan el estado de los resultados de los procesos aritméticos y lógicos, tales como signo, cero, carry e información de paridad.

La circuiteria de control coordina las actividades del microprocesador. Usando pulsos de reloj, la circuiteria de control mantiene la secuencia propia de los eventos en un proceso. También decodifica las instrucciones y edita las señales de control para los dispositivos externos e internos a la CPU.

Las microcomputadoras generalmente usan dispositivos semiconductores para almacenar programas y datos. Para expander el espacio de memoria se usan algunas clases de almacenamiento masivo, tales como discos y cintas magnéticas.

Los dispositivos de entrada y salida, también llamados periféricos, son la forma como la CPU se comunica con el medio exterior.

La CPU es conectada a la memoria y dispositivos de entrada y salida por un conjunto de lineas en paralelo llamados Bus o Canal. Se tienen tres diferentes canales dentro del sistema microcomputador, los cuales son: el canal de datos, el canal de direcciones y el canal de control.

Los datos viajan entre la CPU, la memoria y los dispositivos de entrada y salida en el canal de datos. Estos datos pueden ser instrucciones para la CPU o información que ésta debe transferir a memoria o a los puertos de entrada y salida. La CPU usa el canal de direcciones para seleccionar la localidad de memoria o el dispositivo de entrada y salida deseado. El canal de control lleva las señales de control a memoria y a los dispositivos de entrada y salida, especificando si los datos fluyen desde o hacia la CPU y el tiempo en que deben de fluir.

Cada instante de tiempo en el que un dato es transferido de una parte a otra del sistema microcomputador se le denomina ciclo de máquina. La temporización de estos ciclos se realiza por la señal de reloj de la CPU. Las operaciones como la busqueda de instrucciones, lectura de memoria, escritura en memoria, lectura de un puerto de entrada o escritura en un puerto de salida son realizados en uno o más ciclos de máquina, cuya longitud en tiempo está determinada por la frecuencia de la señal de reloj de la CPU.

Ciertas operaciones pueden interrumpir la secuencia normal de las instrucciones en un programa. Por ejemplo un estado de espera (Mait), el cuel es colocado para dar más tiempo a la memoria o a un dispositivo de entrada y salida para poder comunicarse con la CPU. Los estados de espera son necesarios cuando la velocidad de transferencia de datos es mayor en la CPU que en la memoria. En estos casos, cuando la memoria recibe una instrucción de la CPU, envia a ésta una

petición para un tiempo de espera; una vez que la memoria ha ejecutado la acción, envia su respuesta a la CPU, ésta termina el estado de espera y continúa con el programa.

Otra situación que altera la secuencia de ejecución de algún programa son las llamadas interrupciones, en las cuales un dispositivo de entrada y salida pide a la CPU un cierto servicio. Cuando la CPU termina de proporcionar este servicio, regresa a lo que estaba realizando antes de la cPU. Generalmente más de un dispositivo puede usar a la CPU, es por ésto que existe una jerarquía de interrupciones, es decir; cuando dos interrupciones llegan al mismo tiempo a la CPU, ésta primero dará servicio a la de mayor jerarquía y luego a las demás, conservando siempre una prioridad.

Otra función que permite incrementar la eficiencia del microcomputador es el acceso directo a memoria (DMA). En la operación normal de entrada/salida, la CPU supervisa la transferencia de información desde un dispositivo de entrada y salida hacia una localidad de memoria o viceversa. En el acceso directo a memoria, el dispositivo periférico se encarga de esta transferencia de información para ello, la CPU permite que dicho dispositivo controle los canales del sistema. Una vez terminada esta operación, la CPU reasume el control y continúa con la ejecución del programa previamente detenido.

Una microcomputadora que se encargue del control de las variables de proceso debe contener, además de lo mencionado anteriormente, tarjetas de interfase, las cuales son manejadas como dispositivos de entrada y salida y cuya función es la de acondicionar las señales provenientes de campo, así como las que van hacia él.

La minicomputadora diseñada es capaz de manejar procesos de tipo secuencial, lógico, etc., además de, mediante la programación adecuada, ejecutar controles de tipo proporcional, derivativo e integral.

El desarrollo del diseño del sistema microcomputador se dividió en 5 partes principales, constituyendo cada una de establece cuáles van a ser las funciones principales del sistema, el tipo de arquitectura utilizado, el número y la especificación de las señales a manejar por los canales del sistema. En la segunda parte se diseña la tarjeta de procesamiento; en la tercera, la tarjeta de memoria; en la cuarta y quinta, la tarjeta de entradas y salidas de señales analógicas, respectivamente.

En el Capítulo VII se explica la teoría de operación y en el VIII un breve ejemplo de aplicación del controlador.

## b) Aplicaciones.

Prácticamente este tipo de controlador programable puede ser utilizado para controlar cualquier clase de procesos, es decir, se utilizan varios de ellos para controlar cada una de las partes de dicho proceso. Por ejemplo, el control de una planta termoeléctrica puede ser ejecutado por varios de estos sistemas colocados directamente en campo, cada uno de los cuales puede controlar parcial o totalmente los diferentes procesos manejados en dicha planta. También se pueden controlar procesos de refinación, de fundición, etc. de la misma forma como se mencionó anteriormente.

En los demás capítulos se desarrolla el diseño del sistema microcomputador explicando en cada uno de ellos las partes constitutivas del sistema.

# CAPITULO II

#### DESCRIPCION GENERAL DEL MICROCOMPUTADOR

#### a) Alternativas del Diseño

En este capítulo se presentan algunas de las alternativas de diseño, la selección y justificación de una de ellas y una breva descripción de la arquitectura del controlador.

En primera instancia se consideró tener una arquitectura modular, debido principalmente a la flexibilidad que se presenta al aplicar este controlador para diferentes procesos. De esta forma se idearon 3 tarjetas, las cuales fueron: la tarjeta madre, la tarjeta de procesamiento y la tarjeta de entradas y salidas de señales digitales.

La tarjeta madre permite tener la estructura modular; ya que en esa tarjeta se insertan las demás, es decir, esta tarjeta es la portadora de los canales del sistema y las alimentaciones de voltaje necesarias para el funcionamiento de las mismas. Estas señales se conectan a las tarjetas que forman el controlador por medio de peines, lo cual asegura que sólo las meñales necesarias para el buen funcionamiento de la tarjeta, fluyan a éstas.

La tarjeta de procesamiento se diseñó para tener el circuito del microprocesador, circuitos de memoria y un circuito temporizador. Posteriormente los circuitos de memoria se colocaron en una nueva tarjeta, permitiendo de esta forma tener la capacidad de memoria necesaria para una aplicación específica. Cada una de estas tarjetas de memoria contiene 16 Kb., por tanto 4 de ellas alcanzan la capacidad total de direccionamiento del microprocesador. El circuito temporizador es necesario debido a que se manejan procesos en tiempo real; muchos de ellos requieren tiempos de espera, los cuales son generados por medio de este circuito sin tener necesidad de usar al microprocesador para producirlos.

Como segunda opción se presentó tener en esta tarjeta a un controlador de ciclos de acceso directo a memoria, el cual permite enviar bloques de datos a un dispositivo periférico sin que el microprocesador tenga necesidad de controlar esta transferencia de información. El dispositivo periférico que permitiera los ciclos de acceso directo a memoria, requiere de una tarjeta de interfase que permita acoplar las señales que maneja este sistema y el periférico, sin embargo esta tarjeta no fue considerada en este diseño.

La tarjeta de entradas y salidas de señales digitales forma parte de este diseño, debido a que muchos de los

procesos industriales presentan características digitales, como puede ser la apertura o cierre de un relevador. El número de salidas y entradas digitales en un principio era de ocho y posteriormente se incrementó a doce ocupando, de esta forma, toda la capacidad del circuito integrado que constituye a esta tarjeta.

Como la mayoría de los procesos tienen como variables principales a señales analógicas, fue necesario considerar que una tarjeta manejara dichas señales, por tal motivo se diseñó la tarjeta de entradas y salidas de señales analógicas. Esta tarjeta contiene 4 canales, 2 de entrada y 2 de salida, en un principio sólo contenía 2 canales, uno de salida y otro de entrada; pero como se observó que existía suficiente espacio para conectar el doble de circuitos, así se llevó a cabo.

## b) Selección y Justificación de la Alternativa a Realizar.

La selección que se hizo de las alternativas de diseño, fue en primer lugar, que el controlador tuviera una arquitectura modular, permitiendo gran versatilidad en la implementación de diferentes esquemas de aplicación, en segundo lugar, que las tarjetas que constituyen al controlador fueran de cinco tipos: la tarjeta madre, la tarjeta de procesamiento, las tarjetas de memoria, la tarjeta de entradas y salidas de señales digitales y la tarjeta de entradas y salidas de señales analógicas.

La tarjeta madre es la base de la arquitectura modular y contiene 50 pistas que manejan 44 señales, quedando 6 para aplicaciones futuras.

La tarjeta de procesamiento permite generar tiempos de espera y cíclos de acceso directo a memoria sin control del microprocesador, lo cual permite incrementar la velocidad de trabajo del microprocesador debido a la descarga de trabajos repetitivos.

Las tarjetas de memoria fueron separadas de le tarjeta de procesamiento, porque de esta forma se logra tener la cantidad de memoria necesaria para una aplicación específica, además las bases de los circuitos de memoria son compatibles para cualquier tipo de memoria que tenga una capacidad de memoria de 2 K por 8 bits. La tarjeta de entradas y salidas de señales digitales contiene 12 lineas de entrada y 12 de salida, cubriendo la capacidad total de esta tarjeta, además estas salidas y entradas tienen un rango de voltajes de 0 y 10 Volts, dado que estas señales son estandard para cualquier tipo de proceso.

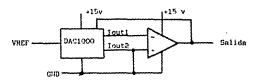

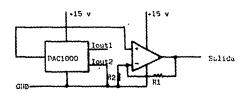

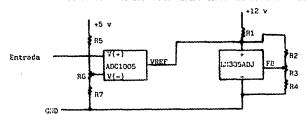

La tarjeta de entradas y salidas de señales analógicas contiene 2 canales de entrada y 2 de salida. Las entradas manejan voltajes entre 1 y 5 volts, que corresponden a la diferecia de potencial que existe en una resistencia de 250 ohms., por la cual circula una corriente comprendida entre 4 y 20 mA. Esta señal de corriente es manejada por la mayoría de los equipos de transmisión y conversión de señales. Las salidas manejan voltajes entre 0 y 10 volts.

Todas estas tarjetas serán colocadas en una canasta capaz de soportar hasta 12 tarjetas, es decir, la tarjeta madre que contiene a las demás, una tarjeta de procesamiento, hasta 4 tarjetas de memoria, N tarjetas de entradas y salidas de señales digitales y N tarjetas de entradas y salidas de señales analógicas. Varias canastas pueden ser conoctadas en serie con la condición de que sólo en una de ellas exista la tarjeta de procesamiento. Esto permite conectar hasta 64 tarjetas de entradas y salidas de señales digitales o 42 tarjetas de entradas y salidas de señales analógicas.

Se ascogió como microprocesador al INTEL 8085, dado que es un procesador bastante versátil, rápido y de fácil manejo; tanto a nivel componente como a nivel programación. Por ello también se usó la familia de periféricos, de este microprocesador como son el 8257 controlador de acceso directo a memoria, el 8253 temporizador programable y el 8255 interfase programable para periféricos. En cuanto a memorias, pueden usarse cualesquiera, siempre y cuando tengan una capacidad de 2 Kb.

Los convertidores A/D y D/A de la tarjeta de entradas y salidas de señales analógicas, son circuitos que presentan compatibilidad con microprocesadores de 8 bits, en este caso con el 8085. Se escogieron dos circuitos debido a que son los más idóneos para la aplicación que se maneja, es decir, son rápidos, presentan un pequeño error de linealidad, son compatibles con los canales del 8085 y son fáciles de manejar, además de que necesitan poca circuitería externa para su funcionamiento.

En los capítulos subsecuentes se presenta el diseño de las tarjetas que constituyen al controlador.

CAPITULO III

# DISEÑO DE LA TARJETA MADRE

### a) Descripción.

La tarjeta madre está constituída por 50 pistas en paralelo por donde circulan las señales de los canales del sistema. En esta tarjeta se encuentran conectados una serie de peines, en los cuales se insertan las tarjetas que forman al controlador. Cada pista está numerada de tal forma que sólo las pistas necesarias son conectadas a cada tarjeta, a su vez cada una de las tarjetas que forma al controlador poseen en uno de sus extremos la parte complementaria del peine, es decir, la parte que se inserta dentro del mismo. De las 50 pistas que forman la tarjeta madre, sólo 44 son usadas en este diseño, quedando las restantes 6 para usos futuros.

En la siguiente tabla se indica el número de pista, la señal que maneja y el canal del cual forma parte.

| NUMERO<br>DE PISTA | SERAL | CANAL   |

|--------------------|-------|---------|

| 0                  | HENRD | CONTROL |

| 1                  | I/ORD | CONTROL |

| 2                  | HENW  | CONTROL |

| 3                  | Ī/OW  | CONTROL |

| 4                  | DO    | DATOS   |

| 5                  | Dl    | DATOS   |

| 6                  | D2    | DATOS   |

| 7                  | D3    | DATOS   |

| 8                  | D4    | DATOS   |

| ļ<br>ļ 9           | D5    | DATOS   |

| 10                 | D6    | DATOS   |

| NUMERO<br>DE PISTA | SEÑAL       | CANAL     |

|--------------------|-------------|-----------|

| 11                 | D7          | DATOS     |

| 12                 | ADO         | DIRECCION |

| 13                 | AD1         | DIRECCION |

| 14                 | AD2         | DIRECCION |

| 15                 | <b>A</b> D3 | DIRECCION |

| 16                 | AD4         | DIRECCION |

| 17                 | AD5         | DIRECCION |

| 18                 | AD6         | DIRECCION |

| 19                 | AD7         | DIRECCION |

| 20                 | AD8         | DIRECCION |

| 21                 | AD9         | DIRECCION |

| 22                 | AD10        | DIRECCION |

| 23                 | AD11        | DIRECCION |

| 24                 | AD12        | DIRECCION |

| 25                 | AD13        | DIRECCION |

| 26                 | AD14        | DIRECCION |

| 27                 | AD15        | DIRECCION |

| 28                 | RESET       |           |

| 29                 | + 5 V.      |           |

| 30                 | GND         |           |

| 31                 | +12 V.      |           |

| 32                 | +15 V.      |           |

| 33                 | 1.5 Mhz.    |           |

| NUMERO<br>  DE PISTA | SEÑAL  | CANAL |

|----------------------|--------|-------|

| 34                   | DACKO  |       |

| 35                   | DRQO   |       |

| 36                   | DACKI  |       |

| 37                   | DRQ1   |       |

| 38                   | DACK2  |       |

| 39                   | DRQ2   |       |

| 40                   | DACKI  |       |

| 41                   | DRQ3   |       |

| 42                   | TC     |       |

| 43                   | MARK   |       |

| 44                   | FUTURO |       |

| 45                   | FUTURO |       |

| 46                   | FUTURO |       |

| 47                   | FUTURO |       |

| 48                   | FUTURO |       |

| 49                   | FUTURO |       |

# b) Especificaciones de las señales.

Cada una de las señales mencionadas anteriormente, está especificada de acuerdo al tiempo de duración máximo y mínimo, y a los voltajes máximos y mínimos permisibles, así como en el caso de voltajes de alimentación, el rango de variación que se acepta sin afectar el funcionamiento de los circuitos.

$\lambda$  continuación se menciona cada una de estas señales con su respectiva especificación.

| SENAL       | DURAC     | (an) NO |      | voltajes                              |       |       |

|-------------|-----------|---------|------|---------------------------------------|-------|-------|

|             | MAX   MIN |         |      | )                                     |       |       |

|             | <br> <br> |         | MAX  | MIN                                   | MAX   | MIN   |

| RD          | İ         | 420     | 0.45 |                                       |       | 2.4   |

| WR          |           | 420     | 0.45 |                                       |       | 2.4   |

| D0-D7       | ļ<br>ļ    | 333     | 0.8  | -0.5                                  | 5.5   | 2.0   |

| ADO-AD15    |           | 608     | 0.45 |                                       |       | 2.4   |

| RESET       |           |         | 0.45 |                                       |       | 2.4   |

| + 5 V.      | !         |         |      |                                       | 5.25  | 4.75  |

| GND         | !         |         |      |                                       | 0     | 0     |

| +12 V.      |           |         |      |                                       | 12.6  | 11.4  |

| +15 V.      |           |         |      |                                       | 15.75 | 14.25 |

| 1.5 Mhz.    |           |         | 0.4  |                                       |       | 2.4   |

| DACKO-DACK3 | 250       |         | 0.45 |                                       | Vcc.  | 2.4   |

| DRQ0-DRQ1   | 160       |         | 0.0  | -0.5                                  | 5.5   | 2.0   |

| TC          | 500       |         | 0.45 |                                       | Vcc.  | 2.4   |

| HARK        | 500       |         | 0.45 |                                       | Vcc.  | 2.4   |

| İ           | 1         | l       | l    | · · · · · · · · · · · · · · · · · · · |       |       |

En el capitulo siguiente se presenta a la tarjeta da procesamiento, que es la parte principal del microprocesador.

# CAPITULO IV

## DISEÑO DE LA TARJETA DE PROCESAMIENTO

## a) Descripción y Especificaciones Generales.

La tarjeta de procesamiento se basa en un microprocesador INTEL 8085, que permite realizar las tareas programadas por el usuario en la tarjeta de memoria, dependiendo de la aplicación específica; cuenta además con la habilidad de ejecutar ciclo de acceso directo a memoria (DMA por sus siglas en inglés), por medio de un controlador de acceso directo a memoria que es el INTEL 8257 y de programar tiempos de espera a través de un temporizador programable que es el INTEL 8253.

A continuación doy una breve descripción de los principales circuitos integrados usados en esta tarjeta, ya mencionados anteriormente.

#### 1) Microprocesador 8085A.

Es un microprocesador de 8 bits, canal N, con el canal de datos y de direcciones multiplexado. Cuenta con una salida para habilitar el latch de direcciones (ALE), con una entrada de READY, que permite el uso de memorias lentas, una entrada de HOLD para realizar fácilmente, sin ayuda de más hardware, peticiones de ciclos de acceso directo a memoria, una salida de HOLD ACKNOWLEDGE (HLDA), que indica al dispositivo encargado de manejar el acceso directo a memoria, que su petición de HOLD ha sido reconocida, una salida de reloj para ser usada como reloj del sistema, una entrada y una salida para la transmisión de datos en serie (SID y SOD), una entrada de RESET, una salida de RESET, capacidad de direccionamiento directo hasta 64 KD. de memoria y 5 niveles jerárquicos de interrupción, entre los que se encuentran:

- INTERRUPT REQUEST Que es la interrupción de nivel jerárquico más bajo y es usada como una interrupción de propósito general. Se activa con nivel alto y es mascarillable.

- RESTART 5.5 Tiene mayor prioridad que el anterior y causa que el contador de programa se cargue con una dirección específica (2CH). Se activa con nivel alto y es mascarillable.

- RESTART 6.5 Tiene mayor prioridad que las dos anteriores y causa que el contador de programa se carque con una dirección específica (34H). Se activa con nivel alto y es mascarillable.

- \* RESTART 7.5 Tiene mayor prioridad que las tres anteriores y causa que el contador de programa se carque con una dirección específica (3CH). Se activa con una transición positiva y es mantenida hasta que sea servida, en ese momento se apaga automáticamente. Es mascarillable.

- \* TRAP Es la interrupción de mayor prioridad. Se recomienda cuando se presenta algún error catastrófico como la falla de la fuente de poder. Causa que el contador de programa se cargue con una dirección específica (24H). Se activa con nivel alto y debe permanecer alta para ser reconocida, pero no será reconocida nuevamente si no ocurre una transición negativa antes. No es mascarillable.

Este circuito trabaja con un cristal de cuarzo de 6 Mhz. para un ciclo de instrucción de 1.33 microsegundos.

# 2) Controlador de Acceso Directo a Memoria 8257.

Este controlador de acceso directo a memoria simplifica la transferencia de datos en alta velocidad. Su función primaria es la de generar, debido a la petición de un dispositivo periférico, una secuencia de direcciones de memoria, que permita a dicho periférico escribir o leer datos en o desde memoria, para ello el controlador se convierte en el amo de los canales del sistema microcomputador mediante la petición de HOLD al microprocesador.

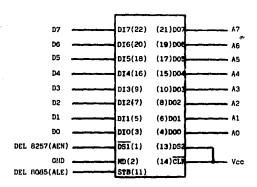

El 8257 poses 4 canales para la transferencia de información organizados jerárquicamente de acuerdo a una prioridad. Junto con un circuito integrado de puertos de entrada y salida de 8 bits (8212), el cual realiza las funciones de latch para el byte más significativo del canal de direcciones, proves un controlador de acceso directo a memoria (DMA).

## 3) Temporizador Programable \$253.

El 8253 es un temporizador programable que resuelve uno de los problemas más comunes de cualquier sistema microcomputador y que es la generación de tiempos de espera bajo control de software. Cuenta con 3 contadores independientes de 16 bits cada uno, los cuales pueden generar frencuencias desde 0 hasta 2 MRE., contar en forma binaria hasta 2 a la 16 o en BCD hasta 4 décadas (10,000) y en 5 modos de operación según sea programado.

### b) Diseño del Circuito.

Para el diseño del circuito es necesario, en primera instancia, determinar qué direcciones manejará la CPU para cada circuito que compone la tarjeta de procesamiento, por tanto, comenzaré con el controlador de acceso directo a memoria.

Para cada canal del 8257 (4 en total) existen dos registros, los cuales son: El registro de direcciones de 16 bits y el registro de cuenta de 16 bits, también incluye dos registros generales ambos de 8 bits; uno, el registro de programación y otro el registro de estado. El bit 3 de la dirección específica que registros serán seleccionados, si es "0" se escoge un registro de canal, si es "1" se escoge el registro de programación o el registro de estado. Los 3 bits manos significativos A0-A2, específican el registro de saleccionar. Cuando se seleccions el registro de programación o el de estado, desde A0 hasta A2 son todos cero. Cuando se selecciona algún registro de algún canal, el bit A0 diferencia entre el registro de dirección (A0 = 0) y el registro de cuenta (A0 = 1), mientras que los bits A1 y A2 seleccionan alguno de los 4 canales.

En la siguiente tabla se muestran los valores de los 4 bits menos significativos y su respectiva función, así como el valor hexadecimal correspondiente.

| FUNCION                                             |   | BIT      |     |       |   |

|-----------------------------------------------------|---|----------|-----|-------|---|

|                                                     | 3 | 2        | 1   | 0     | H |

| Selecciona Registro de Programación o<br>de Estado. | 1 | 0        | 0   | 0     | • |

| Selecciona Registro de Dirección                    |   |          |     |       | Ì |

| Canal O                                             | 0 |          | 0   | 0     | 0 |

| Canal 2<br>Canal 3                                  | 0 | 1        | 1   | 0     | 6 |

| Selecciona Registro de Cuenta                       |   | <u> </u> |     | !     |   |

| Canal 0 Canal 1 Canal 2 Canal 3                     | 0 | 0 1 1    | 0 1 | 1 1 1 |   |

Debido a que los registros de cada canal poseen 16 bits, dos ciclos de instrucciones de programa son requeridos para escribir o leer un registro entero. El 8257 contiene un filp-flop de primero/último, el cual es modificado después de cada operación de lectura o escritura de algún registro, es por esto que todas las instrucciones de comando de operación deben ocurrir en pares, con el byte menos significativo del registro siempre accesado primero.

El 8257 controlador de acceso directo a memoria, será tratado como un puerto de entrada y salida por lo que se escogieron las direcciones 00H hasta la 08, cubriendo todos los registros de este circuito.

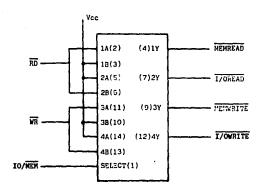

Como este circuito presenta entradas para dispositivos de entrada y salida (I/O W e I/O R) y salidas para memoria (MEM W y NEM R), es necesario tenerlas de las salidas de lectura, escritura e I/O/NEM del microprocesador. Esto se consigue por medio de un selector cuáruple de dos líneas a una línea, este circuito es el 74257 y posee salidas de 3 estados, las cuales permiten conectarlo directamente al canal de control del sistema. La siguiente tabla representa la "tabla de verdad" de este circuito:

| SEÑAL DE CONTROL                     | EΝ                                | TRADA                       | A S                         | SALIDA                                          |

|--------------------------------------|-----------------------------------|-----------------------------|-----------------------------|-------------------------------------------------|

| CONTROL                              | SELECTOR                          | A                           | В                           | У                                               |

| Alto<br>Bajo<br>Bajo<br>Bajo<br>Bajo | X<br>Bajo<br>Bajo<br>Alto<br>Alto | X<br>Bajo<br>Alto<br>X<br>X | X<br>X<br>X<br>Bajo<br>Alto | Alta Impedancia<br>Bajo<br>Alto<br>Bajo<br>Alto |

#### X - Irrelevante

El 74257 será conectado como se muestra en la Fig. 4.1 con el fin de obtener las 4 lineas de control necesarias para el funcionamiento del 8257.

El 8212, como ya había mencionado antes, es un puerto de 8 bits en paralelo, que funciona para este caso como latch para la dirección, cuenta con dos entradas para habilitarlo, las cuales son DS1 y DS2, para este diseño se utilizan dos circuitos 8212, debido a que cuando no se maneja el 8257, es decir el microprocesador es el amo de los canales del sistema, un circuito 8212 funciona para latchar la parte baja de la dirección. Cuando se utiliza el 8257, es decir cuando se utiliza el 8257 es el amo de los canales del sistema, el otro

FIG. 4.1 CONEXION DEL 74257.

FIG. 4.2 CONEXION DEL 8212 PARA LATCHAR LA PARTE BAJA DE LA DIRECCION.

circuito 8212 funciona para latchar la parte alta de la dirección, deshabilitando al mismo tiempo al primer 8212. La forma de conexión del primer 8212 se muestra en la Fig. 4.2. La Fig. 4.3 muestra la forma de conexión del otro circuito 8212.

El controlador de acceso directo a memoria 8257, posea 8 líneas de interconexión bidireccionales para el canal de datos, una entrada de reloj, una entrada de RESET, dos entradas bidireccionales I/O R e I/O M, dos salidas MEM Ry MEM W, una salida de AEN (Address Enable), la cual sirve para deshabilitar al canal de datos del sistema cuando se realizan ciclos de DMA, una salida de ADSTB (Address Strobe), la cual sirve para mandar los 8 bits más significativos de la dirección al 8212, una salida de HRQ (HOLD REQUEST), una entrada de HLDA (HOLD ACRNOELEDGE), una entrada de READY, 4 líneas bidireccionales para los 4 bits menos significativos de la dirección, una salida de cuenta Terminada (TC) y una salida de marca, la cual notifica que el ciclo corriente de acceso directo a memoria es el 128vo. desde la salida de marca previa. Este circuito se conecta a los canales del sistema como se muestra en la Fig. 4.4

A continuación doy una breve explicación sobre la operación de los circuitos que comprenden al controlador de acceso directo a memoria.

En condiciones normales de operación, es decir, cuando el microprocesador es el amo de los canales del sistema, si se requiere leer o escribir un dato de o en memoria, las salidas RD o WR serán "0", según sea el caso y la salida I/O/MEM será también "0", indicando de esta forma que se va a trabajar con memoria, estas señales pasarán al salector cuádruple de dos lineas a una línea 74257, el cual enviará un "0" lógico al canal de control por la linea de MEM RO MEM W (según sea el caso). Posteriormente la salida de ALE del microprocesador será colocada en "1" para ser enviada al 2212, indicándole que la parte baja de la dirección ha sido enviada y se encuentra en esos momentos en el canal de datos del microprocesador. Al mismo tiempo, la parte alta de la dirección es mandada al canal de dirección del sistema.

Una ves que ésto ocurre, la señal de ALE es colocada en "0", indicando al 8212 que las señales subsecuentes que fluyan a él serán datos y por tanto, no deberá tomarlos en cuenta; además esta señal de ALE permite que el 8212 mantenga la información previa (parte baja de la dirección) en sus salidas (ésto es latchar la parte baja de la dirección). Cuando los pasos anteriores han sido ejecutados, el dispositivo de memoria seleccionado manda la información deseada por el canal de datos del sistema hacia el microprocesador.

FIG. 4.3 CONEXION DEL 8212 PARA LATCHAR LA PARTE ALTA DE LA DIRECCION.

| MEMR -              | MEMR         | READY          |             |

|---------------------|--------------|----------------|-------------|

| MENV                | MEIN         | A7<br>A6       |             |

| 1/OR                | I/OR         | A5             |             |

| 1/0W                | I/OW         | A4<br>A3<br>A2 |             |

| D7<br>D6<br>D5      | 87           | A1<br>A0       |             |

| · 05                | D5           | DROO           | <del></del> |

| D3                  | <b>——</b> 03 | DACKO<br>DRQ1  |             |

| D2<br>D1            | D2           | PACE1<br>DRO2  |             |

| DO                  | <b></b> ₽º   | DACE2<br>DRO3  |             |

| AL 8085 (HOLD)      | IRQ          | DACK3          |             |

| DEL 8085 (HLDA)     | HLDA         | TC             |             |

| DEL 8085 (CLXOUT)   | CLK          | MARK           |             |

| DEL 3085 (RESETOUT) | RESCT        | ADDSTB<br>CS   |             |

| A LOS 3212          | AEII         | CS.            |             |

FIG. 4.4 CONEXION DEL 8257.

Cuando se requiere escribir o leer un dato en o desde un puerto de entrada y salida, la salida de I/O/MEM del microprocesador se encontrará en "1", activándose la salida deseada del 74257 (I/O R ó I/O W), después de lo cual los pasos a seguir son iguales que cuando se trabaja con memoria, la unica diferencia que existe es que sólo se manejan 8 bits de dirección.

Cuando se va a manejar al controlador de acceso directo a memoria 8257, el primer paso a realizar es la inicialización de dicho dispositivo, la cual se realiza escribiendo en el registro de programación la palabra de control, que está formada por los siguientes parámetros:

| BIT | FUNCION                           |

|-----|-----------------------------------|

| 0   | Habilita canal 0                  |

| 1   | Habilita canal 1                  |

| 2   | Habilita canal 2                  |

| 3   | Habilita canal 3                  |

| 4   | Habilita prioridad rotatoria      |

| 5   | Habilita write extendido          |

| 6   | Habilita paro en cuenta terminada |

| 7   | Habilita autocarga                |

| j.  |                                   |

El bit 4 de prioridad rotatoria específica la forma de servicio a los cuatro canales. Si es "l", la prioridad de servicio se va rotando conforme un ciclo de DMA ha sido terminado, es decir, si se ha dado servicio al canal 0, luego se dará servicio al canal 1 y así sucesivamente hasta el canal 3.

El bit 5 de write extendido se usa cuando se tienen memorias cuya señal de READY se genera con el retraso de las señales de I/O W o HEN W, lo que ocasiona que el 8257 entre en estado de espera, de tal forma que este bit cuando es "l", extiende el tiempo de la señal de write, previniendo que esto pueda ocurrir.

El bit 6 que habilita el paro en cuenta terminada sirve para deshabilitar el canal donde se ha estado ejecutando la operación de acceso directo a memoria, cuando la salida de cuenta terminada está en O lógico.

El bit 7 de autocarga habilita la operación de bloques de ciclo directo a memoria encadenados, es decir, cuando un bloque de ciclos de DMA ha terminado comienza uno nuevo, no presentando necesariamente las mismas características del bloque anterior.

Es importante hacer notar que la palabra de control sólo puede ser escrita y no leida. Para enviar la palabra de control al registro de programación, se requiere de la instrucción de OUT, la cual envía el contenido del acumulador a la dirección seleccionada, en este caso 08H y el contenido del acumulador será la palabra de control previamente establecida. Una vez que dicha palabra de control ha sido programada dentro del 8257, se requiere inicializar cada canal con la dirección específica de comienzo del bloque de ciclos de DMA y el número de ciclos de DMA a realizar. Para explicar este procedimiento utilizaré como ejemplo al canal O; por tanto vamos a cargar al acumulador con el byte menos significativo de la dirección en que comienzan los ciclos de DMA, para posteriormente con la instrucción de OUT y la dirección 00H cargar la mitad del registro de direcciones del canal 0, en seguida cargamos la parte alta de la dirección en el acumulador y la enviamos por medio de la instrucción de OUT y de la dirección OOH al registro de direcciones del canal O. En este momento, el registro de direcciones del canal O está completo. Para cargar el registro de cuenta es necesario conocer antes que los 14 bits menos significativos de este registro establecen el número de ciclos de DMA a realizar menos 1, es decir, si N es el número de ciclos de DMA a realizar, N - 1 deberá ser cargado en los 14 bits menos de ciclos de DMA a realizar, N - 1 deberá ser cargado en los 14 bits menos de ciclos de DMA a realizar. significativos del registro de cuenta. Los bits 14 y 15 establecen el tipo de operación a realizar de acuerdo a la siquiente tabla:

| BIT 15 | BIT 14 | OPERACION                    |

|--------|--------|------------------------------|

| 0      | 0      | Ciclo de verificación de DMA |

| 0      | 1      | Ciclo de escritura de DMA    |

| 1      | 0      | Ciclo de lectura de DMA      |

| 1      | 1 1    | Inválido                     |

La operación de escritura, como su nombre lo indica, escribe los datos provenientes del dispositivo que hizo la petición de DMA. La operación de lectura indica la lectura de datos hacía el dispositivo que hizo la petición de DMA. La operación de verifica no involucra la transferencia de datos, debido a que no envía señales de control como son: I/O R, I/O W, MEM R y MEM W; sin embargo toma control de los canales del sistema y reconoce la petición de DMA del dispositivo periférico. Esto permite que el dispositivo periférico pueda verificar si los datos que va a enviar son los correctos para el ciclo de DMA deseado.

La forma de programar al registro de cuenta es igual a la forma de programar al registro de direcciones, es decir, primero se carga el acumulador con el byte menos significativo y luego se envía al registro de cuenta por medio de la instrucción de OUT y la dirección olk, posteriormente se carga el byte más significativo en el acumulador y se envía al registro de cuenta de la misma forma que se envió el byte menos significativo, en este momento el registro de cuenta está completo.

Cuando los pasos anteriores han sido ejecutados, si un dispositivo periférico solicita una operación de DMA mediante las líneas de DMA REQUEST, el 8257 enviará una petición de HOLD al microprocesador, el cual responderá con la señal de HOLD ACKNOWLEDGE (HLDA), haciendo al 8257 amo de los canales del sistema. Si se van a leer datos de memoria, el 8257 envia la señal de MEN R al canal de control del sistema; posteriormente envia los 8 bits más significativos de la dirección al 8212, junto con la señal de ADDRESS STROBE, indicándole a éste último que se trata de una dirección y por tanto debe aceptarla, los 8 bits menos significativos de la dirección se obtienen de las salidas AO hasta A7 del 8257. Cuando la señal de ADDRESS STROBE es retirada, el canal de datos en él y sean enviados al periférico que solicitó el acceso directo a memoria. Después de haber realizado el primer ciclo de DMA, el registro de cuenta terminada decrementa en 1 su valor y la dirección de la siguiente localidad de memoria es enviada al canal de dirección del sistema, repitiéndose el mismo proceso hasta finalizar el numero de ciclos de DMA, lo cual corresponde cuando el registro de cuenta terminada es enviada al corresponde cuando el registro de cuenta terminada es enviada al canal de dirección del sistema, repitiéndose el mismo proceso hasta finalizar el registro de cuenta terminada es o.

Si se quiere escribir en memoria, el proceso descrito anteriormente es el mismo, solo que la señal enviada al canal de control será NEM M. Para terminar este circuito sólo es necesario discutir la palabra de estado, la cual indica qué canales han terminado los ciclos de acceso directo a memoria y está formada por los siguientes parámetros:

| BIT | FUNCION                         |

|-----|---------------------------------|

| 0   | Estado de la cuenta del canal 0 |

| 1   | Estado de la cuenta del canal 1 |

| 2   | Estado de la cuenta del canal 2 |

| 3   | Estado de la cuenta del canal 3 |

| 4   | Bandera de Update               |

| 5   | o                               |

| 6   | 0                               |

| 7   | o                               |

| 1   | <u> </u>                        |

Cuando algún canal ha alcanzado el fin de los ciclos de DMA programados, el bit correspondiente a dicho canal se colocará en "l". El bit 4 funciona cuando se maneja el modo de autocarga e indica, cuando es "l" si un nuevo valor de ciclos de DMA ha sido cargado.

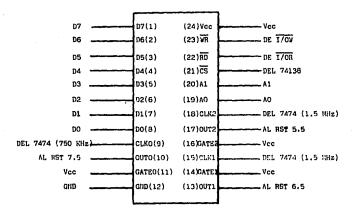

A continuación trataré el temporizador programable 8253, que como ya había mencionado antes, está organizado en tres contadoras descendentes programables de 16 bite cada uno, los cuales son inicializados con el valor deseado de cuenta e interruspen a la CPU cuando ésta ha sido finalizada. Cuenta con un registro de modo de control, el cual es inicializado con las características de cuenta deseada. Cada contador posee un registro de cuenta, el cual es cargado con el valor de cuenta deseado y además cada uno posee una dirección específica en función de los 2 bits menos significativos de la dirección. Los valores de estos 2 bits que seleccionan uno de los contadores, se muestran a continuación junto con la operación a realizar de acuerdo a las señales de RD o MR.

| RD  | i | WR | Al | AO | OPERACION                  |

|-----|---|----|----|----|----------------------------|

| 1   |   | 0  | 0  | 0  | Carga contador No. 1       |

| 1   |   | 0  | 0  | 1  | Carga contador No. 2       |

| 1   |   | 0  | 1  | 0  | Carga contador No. 3       |

| 1   |   | 0  | 1  | 1  | Escribe palabra de control |

| 0   |   | 1  | 0  | 0  | Lee contador No. 1         |

| 0   |   | 1  | 0  | 1  | Les contador No. 2         |

| . 0 |   | 1  | 1  | 0  | Lee contador No. 3         |

| 0   |   | 1  | 1  | 1  | Inválido. Alta impedancia  |

| 1   |   | 1  | x  | x  | Inválido. Alta impedancia  |

| 1   |   |    |    |    |                            |

# Para este circuito seleccioné las siguientes direcciones:

| BINARIO  | HEXADECIMAL | OPERACION                  |

|----------|-------------|----------------------------|

| 00001100 | ос          | Carga o lee contador No. 1 |

| 00001101 | 0D          | Carga o les contador No. 2 |

| 00001110 | 05          | Carga o lee contador No. 3 |

| 00001111 | OF          | Çarga palabra de control   |

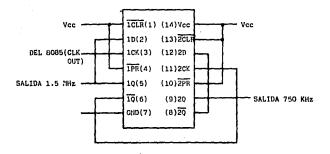

Una caracteristica importante de este circuito es que funciona con frecuencias menores o iguales a 2 MHZ., es decir, la señal de reloj debe tener una frecuencia menor o igual de 2 MHZ., por tanto, si el microprocesador trabaja a una frecuencia de 3 MHZ., es necesario reducir esta frecuencia a la misa (1.5 MHZ.). Esto se consigue intercalando un divisor de frecuencias entre dos, para esto se usa un filip-flop tipo D, cuya salida Q negada es retroalimentada a la entrada D. El filip-flop tipo D usado es el circuito integrado 7474, que contiene dos filip-flops.

Para no desperdiciar uno de los dos flip-flops se usarán ambos, permitiendo de éste modo que dos de los contadores del 8253 trabajen a una frecuencia de 1.5 MHZ. y otro a 750 KHZ. Esta última frecuencia se obtiene alimentando uno de los flip-flops con la frecuencia de salida del otro, ésto nos dá mayor flexibilidad en el conteo de tiempos de muestreo mayores.

El 7474 se conectará como se muestra en la Fig. 4.5.

La palabra de inicialización del registro de modo de control específica los siguientes datos:

| D7 | D6  | D5 | D4 | D3 | D2 | D1 | סם ן |

|----|-----|----|----|----|----|----|------|

| İ  | sco |    |    |    |    |    |      |

SC1 y SC0 seleccionan el contador deseado de acuerdo a la siguiente tabla:

| SC1 | SC0      | SELECCION      |

|-----|----------|----------------|

| 0   | i<br>! 0 | Contador No. 0 |

| 0   | 1        | Contador No. 1 |

| 1   | 0        | Contador No. 2 |

| 1   | ı        | Inválido       |

|     | <br>     | !<br>          |

RL1 y RLO seleccionan la forma de cargar los registros de cuenta de cada contador, de acuerdo a la siguiente tabla:

FIG. 4.5 CONEXION DEL 7474.

FIG. 4.6 CONEXION DEL TEMPORIZADOR 8253.

| • |     |     |                                                                                                 |  |  |  |  |  |  |

|---|-----|-----|-------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|   | RL1 | RLO | SELECCION                                                                                       |  |  |  |  |  |  |

|   | 0   | 0   | Operación de Latch de los<br>contadores.                                                        |  |  |  |  |  |  |

|   | 0   | 1   | Lee o carga el byte más<br>significativo.                                                       |  |  |  |  |  |  |

|   | 1   | 0   | Les o carga el byte menos<br>significativo.                                                     |  |  |  |  |  |  |

|   | 1   | 1   | Lee o carga, primero el<br>byte menos significativo,<br>y luego el byte más sig-<br>nificativo. |  |  |  |  |  |  |

M2, M1 y M0 seleccionan el modo de operación.

| M2 | MI | MO | SELECCION |

|----|----|----|-----------|

| 0  | 0  | 0  | Modo -0   |

| 0  | 0  | 1  | Modo 1    |

| x  | 1  | 0  | Nodo 2    |

| x  | 1  | 1  | Modo 3    |

| 1  | 0  | û  | Nodo 4    |

| 1  | 0  | 1  | Nodo 5    |

X = Irrelevante

Cada modo está definido como e continueción se menciona:

Modo O. Interrupción al finalizar la cuenta.

Cuando el contador es cargado y comiensa la cuenta, la selida del contador permanecerá baja, en el momento de finalizar la cuenta la selida se mantiene alta hasta que un nuevo velor sea cargado o la palabra de control sea renovada. Modo 1. Un tiro programable por Hardware.

La salida del contador permanecerá en estado bajo durante la siguiente transición positiva de la señal que alimenta a la entrada de GATE. En este caso la entrada de GATE funciona como disparador del inicio de cuenta y si se presenta una transición positiva cuando la cuenta no termina aún, ésta no será afectada.

entre en la composição de la composição de la composição de la composição de la composição de la composição de

Modo 2. Contador divisor por N.

La salida permanecerá baja por un período de la entrada de reloj y permanecerá alta según el valor del número inicial en el registro de cuenta.

Modo 3. Generador de onda cuadrada.

La salida permanecerá baja por la mitad de la cuenta y alta para la siguiente mitad para números de cuenta pares, y para números impares la salida será alta para (N+1)/2 y baja para (N-1)/2, siendo N el número inicial de la cuenta.

- Nodo 4. Después de que la palabra de control es cargada, la salida permanecerá alta. Inmediatamente después que el valor de la cuenta es cargado, el contador comenzará a contar, al final de la cuenta la salida estará baja durante un período de reloj, después del cual volverá a estar alta.

- Modo 5. La cuenta comenzará cuando exista una transición positiva en la entrada de GATE, al finalizar la cuenta la salida permanecerá alta durante un período de reloj, después del cual volverá a estar alta.

BCD especifica cuando es "0", que la cuenta es binaria, y si es "1", la cuenta es binaria codificada a decimal.

Cuando se quiere leer el valor de la cuenta sin afectarla, se utiliza la pelabra de control para latchar los contadores, la cual es la siguiente:

| A   |     |    |    |     |    |     |    |   |  |  |

|-----|-----|----|----|-----|----|-----|----|---|--|--|

| D7  | D6  | D5 | D4 | D3  | D2 | D1  | DO | 1 |  |  |

|     |     |    |    |     |    |     |    | i |  |  |

| i i | İ   |    |    | i   | i  |     | ì  | ĺ |  |  |

| SC1 | SC0 | 0  | 0  | X   | X  | X   | X  | ĺ |  |  |

|     | l   | j  | ĺ  | j : | ĺ  | j I |    | Ì |  |  |

SC1 y SC0 seleccionan el contador a leer. La lectura del valor del contador se realiza de esta forma debido a que si se lee el valor en cualquier momento, Este cambiará constantemente si no se deshabilita el conteo previamenta.

والعاط الكاميات وكيبتوا والت

En esta operación no es necesario deshabilitar el contador, debido a que el conteo permanecerá durante la lectura y el valor de la cuenta permanecerá constante a consecuencia del latcheo.

La salida de los contadores estará conectada a las tres interrupciones de RESTART, de esta forma el canal 0 se conectará al RESTART 7.5; el canal 1 al RESTART 6.5; y el canal 2 al RESTART 5.5.

La entrada de GATE de cada contador se conecta a Voc para habilitar la cuenta en cualquier modo de operación. La Fig. 4.6 presenta la forma de conexión del temporizador programable 8253.

La operación del circuito temporizador en condiciones normales es la siguienta:

En primer lugar, debe inicializarse el circuito temporizador programable \$253, escribiendo la palabra de control dentro del registro del mismo nombre y el valor de la cuenta dentro del registro de cuenta del canal seleccionado, para ésto la selide de I/O W del 74257 deberá estar en O lógico y la dirección del 8253 deberá ser seleccionada, es decir, en el caso de escribir la palabra de control la dirección será OFM. Si se escoga el contador l se envía la señal de control de I/O W en el canal de control y la dirección OCH en el canal de direcciones y dependiendo del modo, la cuenta comenzará autosticamente.

Si se desea leer el valor de la cuenta en cualquier instante sin que ésta se vea afectade, se deberá cargar la palabra de control especial para el latcheo de la cuenta dentro del registro de control.

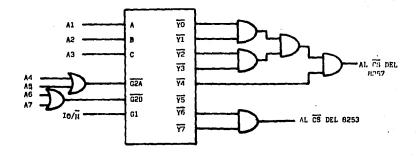

Para concluir este capítulo, sólo es necesario tratar el tema de la selección de cada circuito integrado. Para ello se utiliza un decodificador de 3 á 8, que es el 74138, que posse tras entradas para habilitarlo, las cuales son: G2A, G2B y G1, esí como salidas negadas. Como el 8257 y el 8253 possen direcciones cuyos 4 bits más significativos son 0 se ascoge un arreglo de compuertas OR para habilitar dicho decodificador. Las entradas A, B y C del decodificador serán conectadas a los bits de direcciones A1, A2 y A3 respectivamente, como se muestra en la Fig. 4.7.

FIG. 4.7. CONEXION BEL DECODIFICATION 74136.

| DIR | A7 | A6 | A5 | M | A3 | A2 | A1 | AO | G2A | G28 | G1 | YO  | Ϋ́I | <b>Y2</b> | <del>73</del> | ¥4 | ¥8 | <u>Y6</u> | <b>Y7</b> | SELECCION |

|-----|----|----|----|---|----|----|----|----|-----|-----|----|-----|-----|-----------|---------------|----|----|-----------|-----------|-----------|

| 00  | 0  | 0  | 0  | 0 | 0  | 0  | 0  | 0  | 0   | 0   | 1  | 0   | 1   | 1         | 1             | 1  | 1  | 1         | 1         | 8257      |

| 01  | 0  | 0  | 0  | 0 | 0  | 0  | 0  | 1  | 0   | 0   | 1  | 0   | 1   | 1         | 1             | 1  | 1  | 1         | 1         | 8257      |

| 02  | 0  | 0  | 0  | 0 | 0  | 0  | 1  | 0  | 0   | 0   | 1  | 1   | 0   | 1         | 1             | 1  | 1  | 1         | 1         | 8267      |

| 03  | 0  | 0  | 0  | Ö | 0  | ō  | 1  | 1  | 0   | 0   | 1  | 1   | Ö   | 1         | 1             | 1  | 1  | 1         | 1         | 8257      |

| 04  | 0  | 0  | 0  | 0 | 0  | 1  | 0  | 0  | O   | 0   | 1  | 1   | 1   | 0         | 1             | 1  | 1  | 1         | 1         | 8257      |

| 05  | 0  | Ó  | 0  | 0 | 0  | 1  | 0  | 1  | 0   | 0   | 1  | 1   | 1   | 0         | 1             | 1  | 1  | 1         | 1         | 8257      |

| 06  | 0  | 0  | 0  | 0 | 0  | 1  | 1  | 0  | 0   | Ó   | 1  | 1   | 1   | 1         | Ó             | 1  | 1  | 1         | 1         | 8257      |

| 07  | 0  | 0  | 0  | Ö | Ö  | 1  | 1  | 1  | 0   | 0   | 1  | 1   | 1   | 1         | Ô             | 1  | 1  | 1         | 1         | 8257      |

| 08  | 0  | 0  | 0  | Ó | 1  | 0  | 0  | 0  | 0   | 0   | 1  | 1   | 1   | 1         | 1             | 0  | 1  | 1         | 1         | 8257      |

| 09  | 0  | 0  | 0  | D | •  | 0  | 0  | 1  | 0   | 0   | 1  | 1   | 1   | 1         | 1             | 0  | 1  | 1         | 1         | INVALIDO  |

| OA  | 0  | 0  | 0  | 0 | 1  | 0  | 1  | 0  | 0   | 0   | 1  | 1   | 1   | 1         | 1             | 1  | 0  | 1         | 1         | INVALIDO  |

| OB  | 0  | 0  | 0  | 0 | 1  | 0  | 1  | 1  | 0   | 0   | 1  | 1   | 1   | 1         | 1             | 1  | 0  | 1         | 1         | MVALIDO   |

| DC  | 0  | 0  | 0  | 0 | 1  | 1  | 0  | 0  | 0   | 0   | 1  | 1   | 1   | 1         | 1             | 1  | 1  | 0         | 1         | 8253      |

| OD  | 0  | Ŏ  | ō  | ŏ | i  | i  | ŏ  | 1  | Ō   | Ŏ   | i  | - i | i   | 1         | 1             | 1  | 1  | Õ         | 1         | 8253      |

| ΟE  | 0  | Ō  | 0  | Ď | 1  | 1  | 1  | Ó  | 0   | 0   | 1  | 1   | 1   | 1         | 1             | 1  | 1  | 1         | 0         | 8253      |

| 0F  | 0  | Ō  | 0  | ō | 1  | 1  | 1  | 1  | 0   | 0   | 1  | 1   | 1   | 1         | 1             | 1  | 1  | 1         | Ó         | 8253      |

Fig. 4.5 "Tabla de Verdad" del 74138

Como se puede observar las salidas Y0 hasta la Y4 están arregladas de tal forma que siempre se tenga un 0 cuando se presentan las direcciones 00H hasta la 08H en las entradas del decodificador, dichas direcciones corresponden al controlador de acceso directo a memoria 8257. Las salidas Y6 Y7 también se encuentran arregladas de forma tal que se obtenga un 0, siempre y cuando se presenten las direcciones 0CH hasta la 0FH, que corresponden al temporizador programable 8253. La salida Y5 queda libre, ya que corresponde a las direcciones 0AH y 0BH que no son usadas en este diseño. La dirección 09H tampoco está contenida dentro de este diseño y aunque habilita al 8257, no corresponde a ningun registro. La entrada G1 de habilitación está alimentada por la señal I/O/MEM, debido a que ambos circuitos son manejados como puertos de entrada y salida.

En la Fig. 4.8 se presenta la "tabla de verdad" correspondiente al arregio del decodificador y compuertas mostrado anteriormente.

El circuito completo de la tarjeta de procesamiento se muestra en el Apéndice A, al final del presente trabajo.

En el siguiente capítulo se tratará el diseño de la tarjeta de memoria; la cual forma, junto con la tarjeta de procesamiento, la parte principal del sistema microcomputador.

CAPITULO V

### DISEÑO DE LA TARJETA DE MEMORIA

## a) Descripción y Especificaciones Generales.

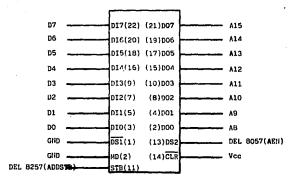

La tarjeta de memoria está formada por 8 circuitos integrados de memoria estática de 2,048 por 8 bits cada uno, 10 cual permite almacenar en una sola tarjeta hasta 16,384 palabras de 8 bits cada una. Las bases de estos circuitos son compatibles para memorias de tipo RAM, PROM, EPROM y EEPROM de la misma capacidad y cuyos tiempos de acceso no sean mayores de 400 nanosegundos, permitiendo de esta forma una gran flexibilidad en el manejo de información.

Cada tarjeta cuenta con un decodificador de 3 á 8 que selecciona uno de los 8 circuitos de mamoria por medio de algunas de las lineas de dirección. El decodificador que se usa es el 74138, que posee tres entradas para ser habilitado (G2A, G2B y G1) y salidas negadas.

La configuración de cada circuito de memoria se muestra en la Fig. 5.1, en la cual se observan los siguientes parámetros:

A7 hasta A0 - Entradas de direcciones.

W = Entrada que habilita la escritura en memoria RAM.

Vpp y PGN = Entradas que habilitan la escritura en EPRON y EEPRON.

CS F E = Entrada que habilita al circuito.

OE F G = Entrada que habilita la lectura.

# b) Diseño del Circuito.

Para el diseño del circuito es necesario conocer qué bits de los 16 que forman la dirección no varían en cada 16 Kb. de memoria. A continuación se muestra la distribución hexadecimal de los 64 Kb. de memoria por cada 16 Kb. de capacidad de cada tarjeta de memoria, además se muestra el valor binario de los 4 bits más significativos.

|          | DIRECCION             |     |     |     |     |     |     |             |     |  |  |

|----------|-----------------------|-----|-----|-----|-----|-----|-----|-------------|-----|--|--|

| HEXAD    | HEXADECIMAL   BINARIO |     |     |     |     |     |     |             |     |  |  |

| INICIO   | <br>  FIN             |     | IN  | CIO |     | FIN |     |             |     |  |  |

| INICIO   | <br>                  | A15 | A14 | A13 | A12 | A15 | A14 | <b>A</b> 13 | A12 |  |  |

| 0000     | 3FFF                  | 0   | 0   | 0   | 0   | 0   | 0   | 1           | 1   |  |  |

| 4000     | 7 <b>FFF</b>          | 0   | 1   | 0   | 0   | 0   | 1   | 1,          | 1   |  |  |

| 8000     | BFFF                  | 1   | 0   | 0   | 0   | 1   | 0   | 1           | 1   |  |  |

| COOO     | PFFF                  | 1   | 1   | 0   | 0   | 1   | 1   | 1           | 1   |  |  |

| <u> </u> | l                     | 1   |     |     |     | l   |     |             |     |  |  |

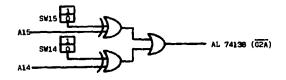

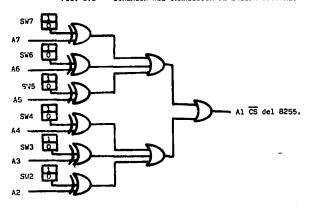

Como se puede observar, los bits A15 y A14 no varían en el rango de los 16 Kb., por tanto éstos se pueden ocupar para la selección del decodificador que maneja el arreglo de los 8 circuitos de memoria por tarjeta. Esta selección se realiza por medio de un arreglo de compuertas y switches, el cual es mostrado en la Fig. 5.2.

Cada switch está representado por el rectángulo vertical con los bits "1" y "0" dentro de él, ésto significa que están conectados físicamente a Vcc y a tierra (dos polos, un tiro). Las compuertas OR exclusivo funcionan como comparadores entre los bits de la dirección y el valor determinado por el switch, de tal forma que si ambos valores son iguales, a la salida de la compuerta tendramos un "0"; si son diferentes tendramos un "1". Cuando los dos bits de direcciones sean iguales a los valores marcados por los switches, el decodificador será activado, debido a que a la salida del arreglo se tendrá un "0". Si algún bit es diferente al valor marcado por el switch, el decodificador no será habilitado puesto que en la salida del arreglo se tendrá un "1".

Desglosando una tarjeta de 16 Kb. en sus componentes de 2 Kb. y tomando los bits Al4, Al3, Al2 y Al1 de la dirección, se tiene:

| A7(1)   | (24)Vcc         |

|---------|-----------------|

| AG(2)   | (23)A8          |

| A5(3)   | (22)49          |

| A4(4)   | (21)₩           |

| A3(5)   | (20) <u>0E</u>  |

| -A2(6)  | (19)A10         |

| A1(7)   | (18)05          |

| (B)0A   | (1 <b>7</b> )D7 |

| 00(9)   | (16)06          |

| -D1(10) | (15)D5          |

| -D2(11) | (14)D4          |

| GND(12) | (13)03          |

|         |                 |

FIG. 5.1 CONFIGURACION DE UN CIRCUITO DE MEMORIA CON CAPACIDAD DE 2K x 8.

FIG. 5.2 ARREGLO DE COMPUERTAS Y SWITCHES.

FIG. 5.4 CONEXION DEL DECODIFICADOR 74138.

| EN  |     |     | S  | SELECCION        |                |    |                       |    |                       |   |          |

|-----|-----|-----|----|------------------|----------------|----|-----------------------|----|-----------------------|---|----------|

| A13 | A12 | A11 | Yo | $\overline{Y_1}$ | Y <sub>2</sub> | Ys | <b>Y</b> <sub>4</sub> | Ys | <b>Y</b> <sub>6</sub> | * |          |

| 0   | 0   | 0   | 0  | 1                | 1              | 1  | 1                     | 1  | 1                     | 1 | MEMORIA1 |

| 0   | 0   | 1   | 1  | 0                | 1              | 1  | 1                     | 1  | 1                     | 1 | MEMORIA2 |

| 0   | 1   | 0   | 1  | 1                | 0              | 1  | 1                     | 1  | 1                     | 1 | MEMORIA3 |

| 0   | 1   | 1   | 1  | 1                | 1              | 0  | 1                     | 1  | 1                     | 1 | MEMORIA4 |

| 1   | 0   | 0   | 1  | 1                | 1              | 1  | 0                     | 1  | 1                     | 1 | MEMORIA5 |

| 1   | 0   | 1   | 1  | 1                | 1              | 1  | 1                     | 0  | 1                     | 1 | MEMORIA6 |

| 1   | 1   | 0   | 1  | 1                | 1              | 1  | 1                     | 1  | 0                     | 1 | MEMORIA7 |

| 1   | 1   | 1   | 1  | 1                | 1              | 1  | 1                     | 1  | 1                     | 0 | MEMORIA8 |

Fig. 5.3 "Table de Verded" del 74138.

|        | DIRECCION    |           |     |     |     |     |             |     |     |  |  |

|--------|--------------|-----------|-----|-----|-----|-----|-------------|-----|-----|--|--|

| HEXADI | CIHAĻ        | BINARIO   |     |     |     |     |             |     |     |  |  |

| INICIO | FIN          |           | IN: | CIO |     |     | FI          | N   |     |  |  |

| INICIO | FIN          | A14 A13 J |     | A12 | All | A14 | <b>A</b> 13 | A12 | All |  |  |

| 0000   | 07 <b>FF</b> | 0         | 0   | 0   | 0   | 0   | 0           | 0   | 0   |  |  |

| 0800   | off <b>f</b> | 0         | 0   | 0   | 1   | 0   | 0           | 0   | 1   |  |  |

| 1000   | 17 <b>FF</b> | 0         | 0   | 1   | 0   | ٥   | 0           | 1   | 0   |  |  |

| 1800   | 1777         | 0         | 0   | 1   | 1   | 0   | 0           | 1   | 1   |  |  |

| 2000   | 2777         | 0         | 1   | 0   | 0   | 0   | 1           | 0   | 0   |  |  |

| 2800   | 2777         | 0         | 1   | 0   | 1   | 0   | 1           | 0   | 1   |  |  |

| 3000   | 37 <b>77</b> | 0         | 1   | 1   | 0   | 0   | 1           | 1   | 0   |  |  |

| 3800   | 3 <b>FFF</b> | 0         | 1   | 1   | 1   |     | 1           | 1   | 1   |  |  |

Como se observa, los bits All, Al2 y Al3 no cambian para el rango de los 2 Kb., por tanto, sirvan para alimentar al decodificador y de esta manera seleccionar uno de los 8 circuitos de memoria. La "tabla de verdad" correspondiente al decodificador se muestra en la Fig. 5.3. En la Fig. 5.4 se muestra el diagrama de conexiones del decodificador junto con el arreglo de compuertas y switches mencionado anteriormente.

La operación de esta tarjeta es muy sencilla, sin embargo, requiere una breve explicación. Cuando se desea almacenar o extraer un dato, el microprocesador, en base al programa previamente establecido, envía la dirección al canal de direcciones, posteriormente envía las señales de control MEM R F MEM W según sea el caso y por último envía la señal de I/O/MEM, con lo cual la memoria seleccionada escribe los datos enviados o vierte sus datos en el canal de datos del sistema.

El circuito completo de memoria se muestra en el Apéndice B al final de este trabajo.

CAPITULO VI

### DISEÑO DE LA TARJETA DE ENTRADAS Y SALIDAS DE SEÑALES DIGITALES

a) Descripción y Especificaciones Generales.

Debido a que muchos de los procesos industriales poseen características digitales, la tarjeta de entradas y salidas digitales forma parte integrante de cualquier controlador y sistema de adquisición de datos.

Esta tarjeta contiene doce entradas digitales y doce salidas digitales, las cuales manejan voltajes de 0 y 10 volts; drenando, en las salidas, una corriente máxima de 50 mA.

La tarjeta de entradas y salidas digitales se basa principalmente en el circuito integrado de INTEL 8255, que es una interfase programable de periféricos y que posee entre otras las siguientes características: 24 bits de entradas o salidas, divididas en tres puertos A, B y C de 8 bits cada uno y en dos grupos A y B de 12 bits cada uno, de tal forma que a cada grupo le corresponde un puerto entero y la mitad del puerto C; es decir, al grupo A le corresponde el puerto A y la mitad superior del puerto C y al grupo B le corresponde el puerto B y la mitad inferior del puerto C, pudiendo ser programados en tres modos de operación. En el primer modo de operación o modo "O" cada grupo puede ser programado en juegos de 4 bits para ser salidas o entradas. En el modo "l" cada grupo puede ser programado para tener 9 bits de entradas o salidas y 3 bits para señales de control. En el modo "2" sólamente el grupo A puede ser programado para formar un canal bidireccional correspondiendo 8 bits de entradas y salidas y 4 bits para señales de control, en este modo se necesita una señal de control más, la cual es tomada del bit 3 del puerto C.

Cada puerto posee características propias como son:

Puerto A: un buffer o latch de salida de 8 bits y un latch de entrada de 8 bits.

Puerto B: un buffer o latch de salida/entrada de 8 bits y un buffer de entrada de 8 bits.

Puerto C: un buffer o latch de salida de 8 bits y un buffer de entrada de 8 bits.

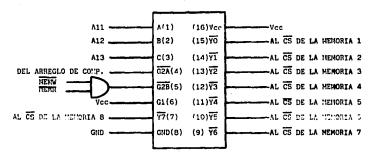

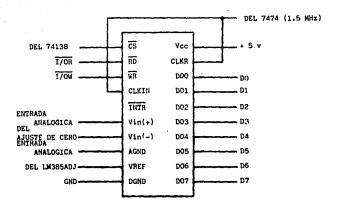

En la Fig. 6.1 se muestra la configuración de entradas y salidas del 8255.

## b) Diseño del Circuito.

Las direcciones que puede tomar el 8255 están especificadas por los tres puertos que maneja y por el registro de la palabra da control de acuerdo a la siguiente table:

| AO | A1 | OPERACION                                           |  |  |  |  |  |

|----|----|-----------------------------------------------------|--|--|--|--|--|

| 0  | 0  | Escribe o lee en o del<br>Puerto A.                 |  |  |  |  |  |

| 0  | 1  | Escribe o les en o del<br>Puerto B.                 |  |  |  |  |  |

| 1  | 0  | Escribe o les en o del<br>Puerto C.                 |  |  |  |  |  |

| 1  | 1  | Escribe en el registro de<br>la palabra de control. |  |  |  |  |  |

La palabra de control específica los siguientes parametros:

| BIT   | FUNCION                                                              |

|-------|----------------------------------------------------------------------|

| 0     | Especifica mi la parte baja del puerto C em<br>entrada o malida.     |

| 1     | Especifica si el puerto B es entrada o salida.                       |

| 2     | Selección del modo del grupo B.                                      |

| 3     | Especifica ei la parte superior del puerto C<br>es entrada o salida. |

| 4     | Especifica si el puerto A es entrada o salida.                       |

| 5 y 6 | Selección del modo del grupo A.                                      |

| 7     | Bandera de programación. Activo en "1".                              |

| l ,   | , ·                                                                  |

56.0

| PA3/1) (   | 40,574 |

|------------|--------|

| PA2(2) (   | 39)PA5 |

| PA1(3) (   | 38)PA6 |

| PAO(4) (   | 37)PA7 |

| RD(5)      | 36) WR |

| CS(6) (35) | RESET  |

| GHD(7) (   | 34)DO  |

| A1(B) (    | 33)D1  |

| AO(9) (    | 32)D2  |

| PC7(10)    | 31)03  |

| PCG(11)    | 30)04  |

| PC5(12)    | 29)05  |

| PC4(13)    | 28)D6  |

| PCO(14)    | 27)07  |

| PC1(15)    | 26)Vcc |

| PC2(16)    | 25)PB7 |

| PC3(17)    | 24)PB6 |

| PBO(18)    | 23)PB5 |

| PB1(19)    | 22)PB4 |

| PB2(20)    | 21)PB3 |

FIG. 6.1 CONFIGURACION DEL 8255.

Este circuito posee una característica importante y consiste en poder encender o apagar cada uno de los bits del puerto C en forma independiente a la de enviar algún byte por medio de la instrucción de OUT. Esta función es útil cuando se manejan el modo l y 2, debido a que como ya había mencionado antes, algunos de los bits del puerto C representan señales de control. Dicha función es programada dentro del registro de la palabra de control.

El bit 7 de la palabra de control especifica si la palabra que se programó es de modo de operación o de la función de encendido/apagado de los bits del puerto C.

Los bits 6 y 5 especifican el modo de operación del grupo A de acuerdo a la siguiente tabla:

| 6 | 5 | HODO DE OPERACION |

|---|---|-------------------|

| 0 | 0 | Modo 0.           |

| 0 | 1 | Modo 1.           |

| 1 | x | <br>  Modo 2.     |

X = Irrelevante.

Los bits 4, 3, 1 y 0 especifican si el puerto A, parte superior del puerto C, puerto B y la parte inferior del puerto C, respectivamente son salidas si son "0" o entradas si son "1".

El bit 2 específica el modo de operación del grupo B, de tal forma que si es "0", se programa el modo 0, si es "1" se programa el modo 1.

La palabra de programación del modo de encendido/apagado de los bits del puerto C está formada por los siguientes parámetros:

| BIT     | FUNCION                                                                                 |

|---------|-----------------------------------------------------------------------------------------|

| 0       | Encendido o apagado de los bits seleccionados.<br>"1" para encendido. "0" para apagado. |

| 1,2 y 3 | Selecciona el bit del puerto C.                                                         |

| 4,5 y 6 | Irrelevantes.                                                                           |

| 7       | Bandera de la función de encendido/apagado.<br>Activo en "0".                           |

El bit 7 cuando es "0", específica que se trata de la palabra de la función de encendido/apagado de los bits del puerto C.

Los bits 3, 2 y 1 seleccionan los bits del puerto C a encender o apagar, de acuerdo a la siguiente tabla:

|   | 3 | 2 | 1 | SELECCION |

|---|---|---|---|-----------|

|   |   | 1 |   |           |

|   | ٥ | 0 | 0 | Bit 0     |

|   | 0 | 0 | 1 | Bit 1     |

|   | 0 | 1 | a | Bit 2     |

|   | 0 | 1 | 1 | Bit 3     |

|   | 1 | 0 | 0 | Bit 4     |

|   | 1 | 0 | 1 | Bit 5     |

|   | 1 | 1 | 0 | Bit 6     |

|   | 1 | 1 | 1 | Bit 7     |

| į |   | _ |   |           |

Cada uno de los modos de operación está definido como a continuación se menciona:

- Modo 0. Este modo configura cada uno de los puertos como entradas o salidas simples. Las salidas son latchadas, las entradas no.

- Modo 1. Este modo configura los puertos A y B como entradas o malidas, 6 bits del puerto C para señales de control de transferencia de los datos de los puertos A y B y 2 bits del puerto C como entradas o salidas mimples. Las entradas y salidas de los puertos A y B son latchadas. Las señales de control del puerto C, que regulan la transferencia de información de los puertos A y B están definidas de diferente forma, según se programe el puerto como entrada o malida.

Si es entrada se definen como:

STB (Strobe Input). Un "0" en esta entrada carga el latch de entrada. Es el bit 4 del puerto C.

IBF (Input Buffer Full F/F). Un "1" en esta salida indica que el latch de entrada está lleno. Es colocada en "1" cuando STB es "0" y es limplada con la transición positiva de la señal de READ. Es el bit 5 del puerto C.

INTR (Interrupt Request). Esta salida sirve para interruspir al microprocesador cuando este dispositivo está pidiendo servicio. Es "1" cuando STB es "0" e IBF es "1" y es limpiado con la transición positiva de la señal de READ. INTE A es controlado por el bit 4 del puerto C. INTE B es controlado por el bit 2 del puerto C.

#### Si es salida se definen como:

OBF (Output Buffer Full F/F). Cuando esta salida está en "0", indica que el microprocesador ha escrito datos dentro del puerto seleccionado. Es puesta en "1" con la transición positiva de la señal de WRITE y es "0" cuando la entrada de ACK es "0". Es el bit 7 del puerto C.

ACK (Acknowledge Input). Un "0" en esta entrada informa al 8255 que los datos de los puertos A o B han sido aceptados. Es el bit 6 del puerto C.

INTR (Interrupt Request). Cuando esta salida es "l" puede ser usada para interrumpir al microprocesador y dar servicio el 8255. Es puesta en "l" cuando ACK es "l" y OBF es "l". Es limpiada con la transición negativa de la señal de WRITE. INTE A es controlada por el bit 6 del puerto C, INTE B es controlada por el bit 2 del puerto C.

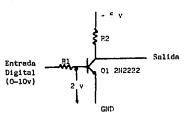

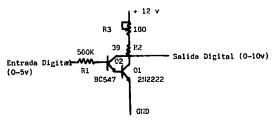

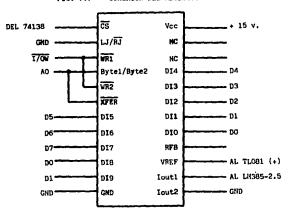

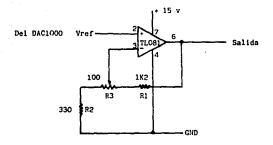

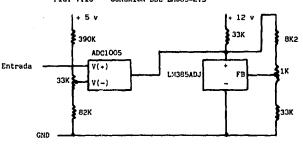

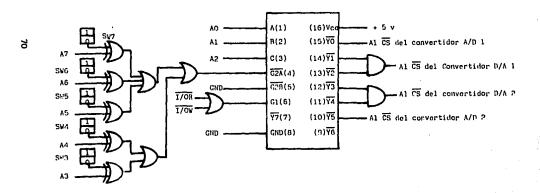

Las señales de INTE se refieren a poder habilitar las señales de INTE de los puertos A y B de las señales de control que entran al 8255, en el caso de ser entradas, se refiere a la señal de STB y en el caso de salidas, a la señal de ACK.