### UNIVERSIDAD NACIONAL AUTONOMA DE MEXICO

FACULTAD DE INGENIERIA

# IMPRESOR DE LLAMADAS TELEFONICAS

TESIS PROFESIONAL

YUKIHIRO MINAMI KOYAMA

D I R E C T O R

ING. RODOLFO PETERS LAMMEL

1984

UNAM – Dirección General de Bibliotecas Tesis Digitales Restricciones de uso

### DERECHOS RESERVADOS © PROHIBIDA SU REPRODUCCIÓN TOTAL O PARCIAL

Todo el material contenido en esta tesis esta protegido por la Ley Federal del Derecho de Autor (LFDA) de los Estados Unidos Mexicanos (México).

El uso de imágenes, fragmentos de videos, y demás material que sea objeto de protección de los derechos de autor, será exclusivamente para fines educativos e informativos y deberá citar la fuente donde la obtuvo mencionando el autor o autores. Cualquier uso distinto como el lucro, reproducción, edición o modificación, será perseguido y sancionado por el respectivo titular de los Derechos de Autor.

### CONTENIDO

| INTRODUCCION                                                               | 1  |

|----------------------------------------------------------------------------|----|

| CAPITULO I                                                                 |    |

| FUNCIONAMIENTO BASICO DE UNA LINEA TELEFONICA INDIVIDUAL                   | 3  |

| I.1 APARATO TELEFONICO DE BATERIA CENTRAL                                  | 4  |

| I.2 BOSQUEJO GENERAL DEL FUNCIONAMIENTO DE UN CUADRO CONMUTADOR AUTOMATICO | 8  |

| CAPITULO II                                                                |    |

| EXPLICACION Y COMPARACION DE ALGUNAS FAMILIAS DE                           |    |

| CIRCUITOS LOGICOS DIGITALES                                                | 11 |

| II.1 LOGICA RTL (RESISTOR TRANSISTOR LOGIC)                                | 12 |

| II.2 LOGICA DTL (DIODE TRANSISTOR LOGIC)                                   | 19 |

| II.3 LOGICA HTL (HIGH THRESHOLD LOGIC)                                     | 22 |

| II.4 LOGICA TTL (TRANSISTOR TRANSISTOR LOGIC)                              | 25 |

| II.5 LOGICA ECL (EMITTER COUPLED LOGIC)                                                  | 31        |

|------------------------------------------------------------------------------------------|-----------|

| II.6 CUADRO COMPARATIVO DE LAS FAMILIAS LOGICAS DIGITALES                                | 34        |

| CAPITULO III                                                                             |           |

| FAMILIAS LOGICAS DIGITALES CON TRANSISTORES DE EFECTO                                    |           |

| DE CAMPO                                                                                 | 35        |

| III.1 GENERALIDADES DEL TRANSISTOR DE EFECTO DE CAMPO                                    | 36        |

| III.2 TRANSISTOR DE EFECTO DE CAMPO DE JUNTURA                                           | 37        |

| III.3 TRANSISTOR DE EFECTO DE CAMPO DE SEMICONDUCTOR                                     |           |

| METALIZADO OXIDADO (MOSFET)                                                              | 41        |

| III.4 LOGICA MOS                                                                         | 45        |

| III.5 LOGICA CMOS (COMPLEMENTARY-SYMMETRY METAL OXIDE SEMICONDUCTOR                      | 50        |

| CAPITULO IV                                                                              |           |

| DISEÑO DE LOS CIRCUITOS NECESARIOS PARA LA IMPLEMENTACION                                |           |

| DEL "IMPRESOR DE LLAMADAS TELEFONICAS"                                                   | 61        |

| IV.1 FUNCIONAMIENTO BASICO DEL IMPRESOR DE UNA                                           |           |

| CALCULADORA DE MESA                                                                      | 63        |

| IV.2 CIRCUITOS DE DETECCION DE LAS PRINCIPALES                                           |           |

| FUNCIONES TELEFONICAS                                                                    | 67        |

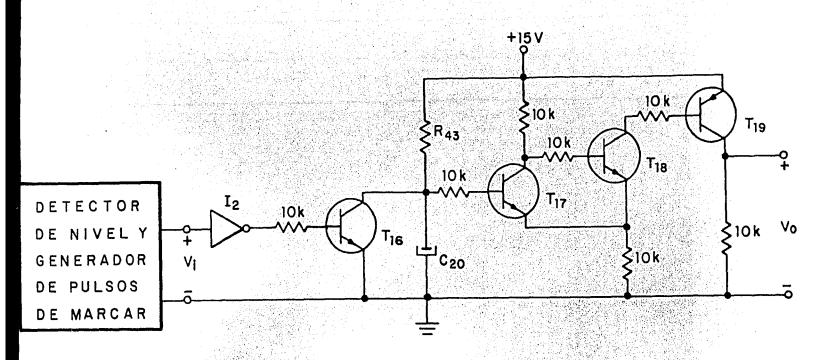

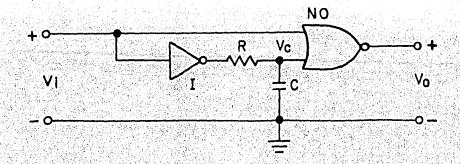

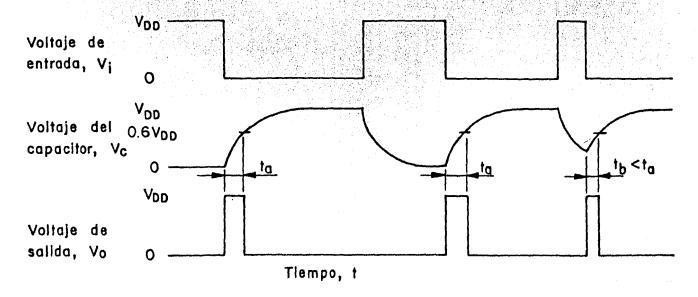

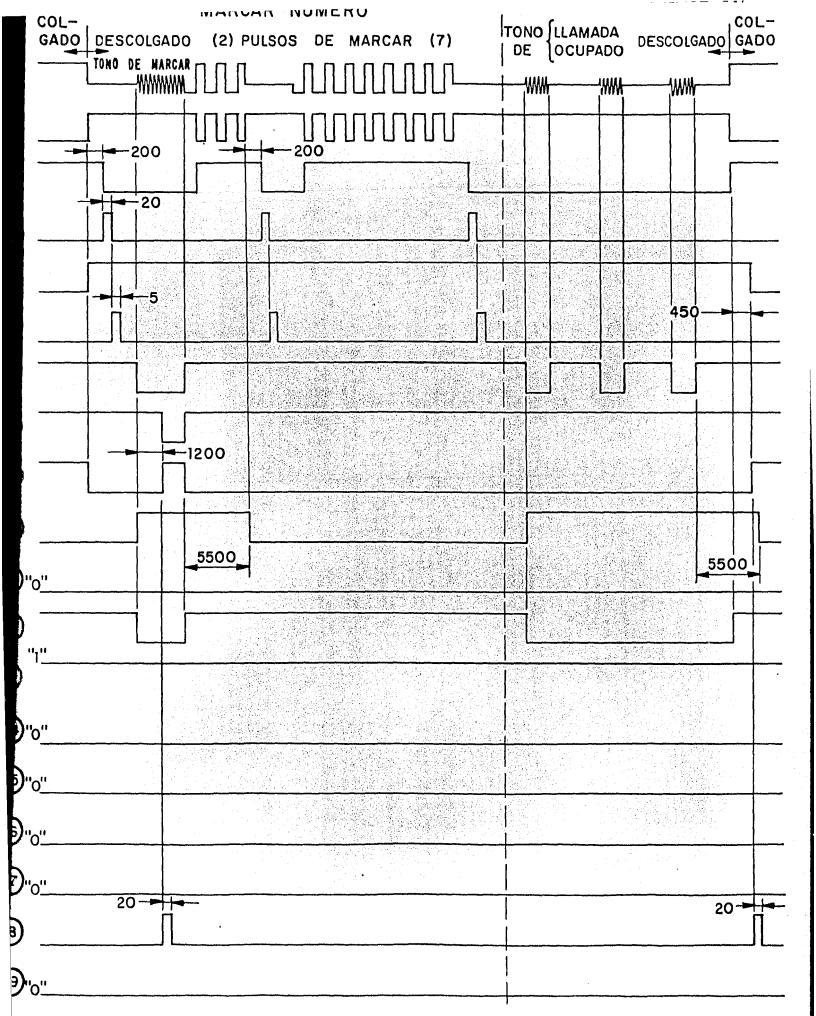

| IV.2.1 DETECTOR DE NIVEL Y GENERADOR DE PULSOS DE MARCAR                                 | 68        |

| IV.2.2 DETECTOR DE TELEFONO COLGADO                                                      | 83        |

| IV.2.3 DETECTOR DE TONO                                                                  | 88        |

| IV.2.4 DETECTOR DE TONO CONTINUO                                                         | 95        |

| IV.2.5 DETECTOR DE TONO DISCONTINUO                                                      | 96        |

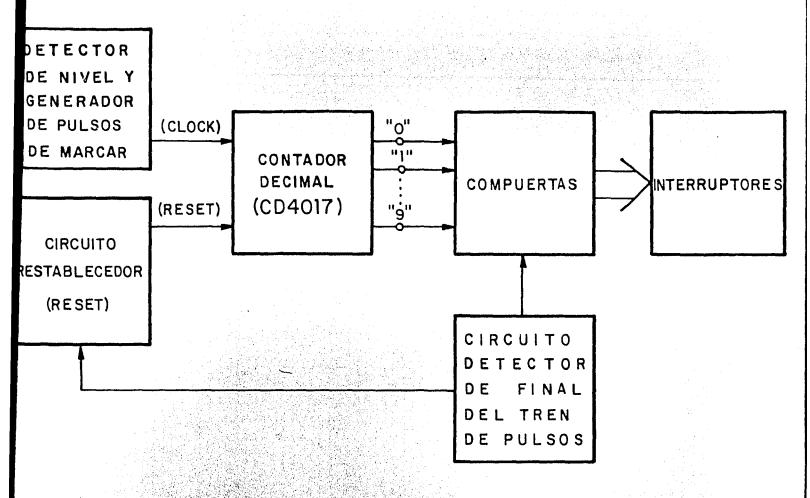

| IV.3 CIRCUITOS DE PROCESAMIENTO DE LOS PULSOS DE MARCAR                                  | 99        |

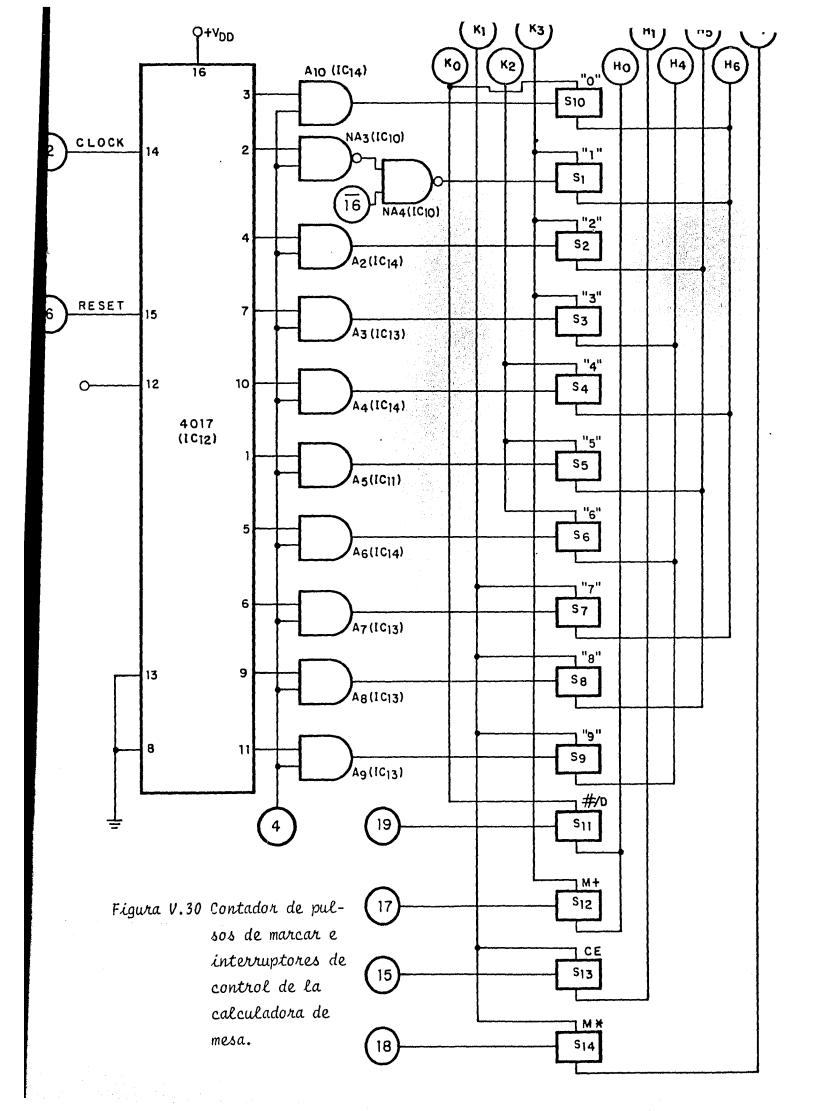

| IV.3.1 CONTADOR DE PULSOS DE MARCAR IV.3.2 CIRCUITO DETECTOR DE FINAL DEL TREN DE PULSOS | 99<br>101 |

|             | IV.3.3 CIRCUITOS DE COMANDO DE COMPUERTAS Y RESTABLECEDOR |     |

|-------------|-----------------------------------------------------------|-----|

|             | DEL CONTADOR                                              | 103 |

|             | 사용 사용 사용 사용 사용 전에 가는 것이 되었다.<br>                          |     |

| IV.4        | CIRCUITOS DE DETECCION DE ENLACE Y DE CONTABILIDA         | )   |

|             | DEL TIEMPO DE LLAMADA                                     | 106 |

|             | IV.4.1 DETECTOR DE ENLACE Y DE TERMINACION DE LLAMADA     | 106 |

|             | IV.4.2 HABILITADOR DEL CIRCUITO "MARCAS DE TIEMPO" Y      |     |

|             | COMANDO DE IMPRESION                                      | 109 |

|             | IV.4.3 CIRCUITO GENERADOR DE "MARCAS DE TIEMPO"           | 110 |

|             | IV.4.4 CIRCUITO CONTABILIZADOR DEL TIEMPO DE LLAMADA      | 113 |

|             | IV.4.5 CIRCUITO IMPRESOR DEL TIEMPO DE LLAMADA            | 115 |

|             |                                                           |     |

| CAPIT       | JLO V                                                     |     |

| APLICA      | ACION DEL PROCESO DE OPTIMACION EN EL DISEÑO FINAL        |     |

| DEL "       | IMPRESOR DE LLAMADAS TELEFONICAS"                         | 120 |

| <b>v.</b> 1 | MODIFICACIONES REALIZADAS A ALGUNOS CIRCUITOS             | 121 |

| V.2         | OPTIMACION DEL NUMERO DE CIRCUITOS INTEGRADOS             |     |

|             | UTILIZADOS                                                | 130 |

| V.3         | SELECCION DE UNA NUEVA CALCULADORA DE MESA                | 134 |

| V.4         | DIAGRAMAS ESQUEMATICOS FINALES Y GRAFICAS DE LAS          |     |

|             | SALIDAS DE LOS CIRCUITOS UTILIZADOS                       | 138 |

| V.5         | ALGUNAS CONSIDERACIONES SOBRE EL ARMADO DEL               |     |

| ۷.)         | "IMPRESOR DE LLAMADAS TELEFONICAS"                        | 149 |

|             |                                                           |     |

| CONCL       | USIONES                                                   | 153 |

| DEGOVE      |                                                           |     |

| RECON       | OCIMIENTO                                                 | 156 |

| BIBLI       | OGRAFIA                                                   | 157 |

#### INTRODUCCION

Una de las necesidades más grandes de la humanidad ha sido siempre la COMUNICACION. A través de los siglos, ésta ha evolucionado para poder realizarse de manera cada vez más rápida y eficiente.

Dentro de los grandes logros alcanzados en este campo está la TELE-FONIA, o sea, el arte de transmitir a distancia la palabra hablada por me dio de una combinación de dispositivos electrónicos y electromecánicos, que se ha desarrollado desde la investigación relacionada con la construcción del primer receptor con el cual Alexander Graham Bell hizo sus experimentos fundamentales en 1876, hasta los actuales aparatos electrónicos altamente eficientes, complejos equipos centrales automáticos, así como redes de comunicación interurbana y sistemas computarizados de control de líneas.

A pesar de que los principios fundamentales de la TELEFONIA han per manecido virtualmente inalterados, se considera actualmente como un complemento esencial para la inmensa mayoría de las actividades humanas, razón por la cual ha tomado tal incremento y penetrado en tantas otras ramas de la tecnología electrónica, que es casi imposible apreciar sus posibilidades en toda su extensión.

Debido a la demanda cada vez mayor de usuarios de líneas telefónicas, así como del radio de acción alcanzado por éstas, se ha hecho necesario el control cada vez más eficiente y automatizado de dichas líneas.

Este trabajo tiene como principal finalidad, proponer un dispositivo de control de llamadas de una línea individual o "IMPRESOR DE LLAMADAS

TELEFONICAS", utilizando elementos electrónicos de fácil adquisición, así

como toda la tecnología digital generada hasta mediados de la década de

los setentas.

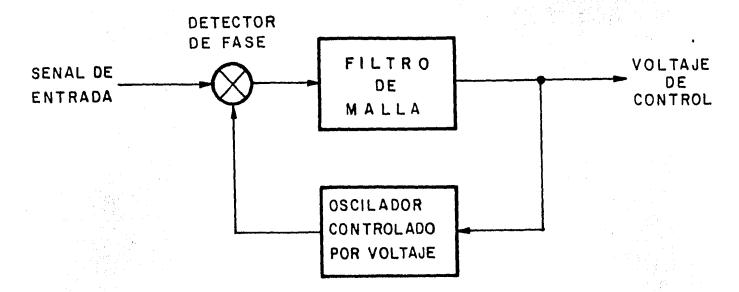

En este "IMPRESOR DE LLAMADAS TELEFONICAS" se han utilizado elementos tales como transistores bipolares de juntura (TBJ), resistencias, capacitores, compuertas elementales digitales (NAND, NOR, AND, NOT o inversor, etcétera) y circuitos integrados de mayor complejidad, como contado res digitales, un circuito de "amarre" de fase o PLL por sus siglas en inglés (Phase-Locked Loop), así como el impresor de una calculadora de mesa.

El "IMPRESOR DE LLAMADAS TELEFONICAS" ha sido diseñado exclusivamen te mediante circuitería electrónica o "HARDWARE", sin utilizar el microprocesador y su consiguiente programación digital o "SOFTWARE".

Se ha tenido en consideración durante todo el desarrollo del diseño, el proceso de optimación, tan importante para todos los campos de la

ingeniería, de manera de reducir al mínimo el número de elementos utiliza

dos, así como la energía necesaria para su funcionamiento.

Por esta última razón, se han utilizado en su mayoría circuitos integrados de la familia CMOS, los cuales consumen menor potencia en comparación con otras tecnologías de circuitos integrados digitales, tales como las familias TTL, RTL, etcétera.

En algunos casos específicos no ha sido posible la utilización de este tipo de circuitos, por ejemplo, cuando se ha requerido de un voltaje de operación mayor o se ha necesitado alguna función diferente de las proporcionadas por los circuitos CMOS, por lo que se ha recurrido a circuitos discretos con base en transistores bipolares de juntura.

A grandes rasgos, éstos son los principales criterios de diseño del "IMPRESOR DE LLAMADAS TELEFONICAS".

#### CAPITULO I

### FUNCIONAMIENTO BASICO DE UNA LINEA TELEFONICA INDIVIDUAL

El "IMPRESOR DE LLAMADAS TELEFONICAS" será diseñado con base en el sistema telefónico de la Ciudad de México, que se le puede catalogar dentro de los sistemas automáticos de batería central.

Este sistema está compuesto principalmente por los aparatos telefónicos de los abonados, la línea telefónica en sí (conductores eléctricos) y el cuadro conmutador automático (central), compuesto por diversos circuitos como el de alimentación de voltaje o fuente de voltaje, los selectores, los generadores de señales, etcétera.

Se denomina a este sistema de batería central, por la característica de que la fuente de alimentación es común para todos los aparatos tele fónicos de los abonados, que están conectados a un cuadro conmutador automático al que se le puede considerar como el centro del sistema.

Existe también el sistema telefónico de batería local, en el que ca da aparato telefónico posee su propia fuente de energía.

### I.1 APARATO TELEFONICO DE BATERIA CENTRAL

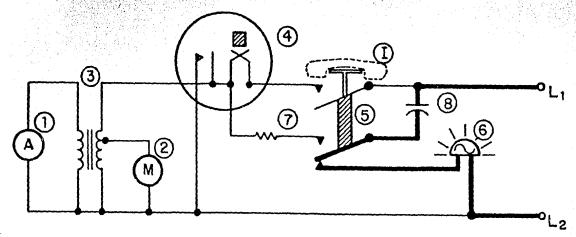

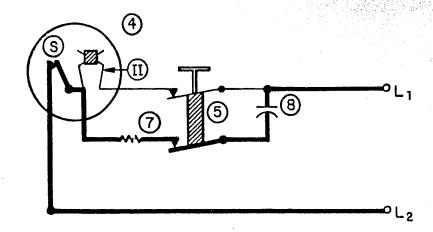

El aparato telefónico de batería central está compuesto básicamente por los siguientes elementos: el microteléfono (I), que comprende tanto al audífono (1) como al microfono (2), el transformador (3), el disco de marcar (4), el conmutador de horquilla (5), el timbre eléctrico (6), una resistencia (7) y, un capacitor (8).

Figura I.1 Diagrama esquemático de un aparato telefónico con el microtelefono colgado.

El diagrama de la figura I.1 representa esquemáticamente al aparato telefónico con el microteléfono puesto en la horquilla o "colgado".

Cuando la línea es excitada por la señal de llamada (corriente alterna), ésta pasa a través del capacitor (8) y el interruptor inferior del conmutador de horquilla (5), accionando al timbre (6) cuyo sonido indica la existencia de una comunicación exterior con el abonado.

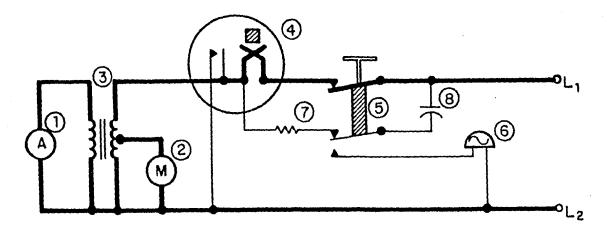

Figura I.2 Diagrama esquemático de un aparato telefónico con el microteléfono descolgado.

Al descolgar el microteléfono (véase figura I.2), el interruptor su perior del conmutador de horquilla conecta la línea con el circuito vocal del aparato telefónico, compuesto por el audífono (1), el micrófono (2) y el transformador (3), a través de los contactos del disco de marcar (4); el interruptor inferior del conmutador de horquilla desconecta la línea del timbre.

Durante la conferencia telefónica, el circuito microfónico (2) se alimenta de la corriente continua de la línea. Las corrientes vocales transmitidas por la línea llegan al audífono (1) a través del embobinado secundario del transformador (3).

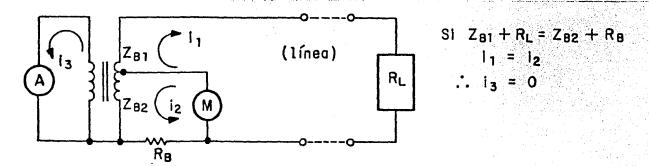

El circuito vocal está diseñado de tal manera que el audífono sea excitado casi exclusivamente por la corriente vocal de la línea, impidien do que la corriente microfónica del mismo aparato predomine en la audición. Esto se logra haciendo que la impedancia compuesta por la parte superior del embobinado primario del transformador (véase figura I.3) más la impedancia de la línea, se iguale a la impedancia de la parte inferior del mismo embobinado.

Figura 1.3 Diagrama esquemático simplificado, mostrando el principio de funcionamiento del circuito ANTI-LOCAL.

De esta manera, las corrientes  $i_1$  e  $i_2$  son iguales, por lo que la suma algebraica de las corrientes del embobinado primario del transformador es igual a cero. Por lo tanto, la corriente vocal que pasa por el audífono debida a la excitación del mismo usuario, se anula.

Al terminar la conferencia, el abonado cuelga su microteléfono, por lo que el conmutador de horquilla vuelve a su posición de reposo.

Cuando el abonado desea realizar una llamada, descuelga su microteléfono, conectando de esta manera su aparato telefónico con la línea, a través de los interruptores del conmutador de horquilla (5), como ya se explicó anteriormente.

Para marcar el número del abonado con el que se desea la comunicación, el abonado utiliza el disco de marcar (4).

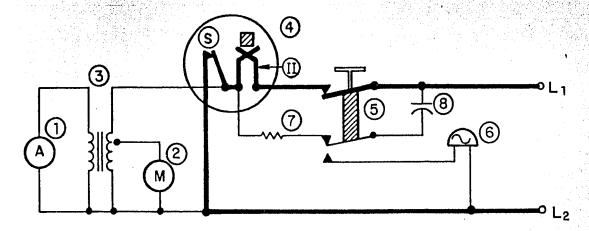

Figura I.4 Diagrama esquemático de un aparato telefónico al iniciar el accionamiento del disco de marcar.

Al comenzar a girar el disco, cierran los contactos del interruptor marcado con S (véase figura I.4), con el cual se cortocircuitan el transformador (3) y el micrófono (2), protegiéndolos de impulsos de corriente producidos durante la generación de los pulsos de marcar.

Al soltar el disco, los contactos del interruptor II abren y cierran un número de veces igual a la cifra marcada en el disco, mediante una rueda de material aislante provista de salientes que penetran entre los contactos del interruptor II.

Figura 1.5 Diagrama esquemático simplificado de un aparato telefónico durante la generación de pulsos de marcar.

Durante todo el proceso de generación de pulsos, el interruptor S permanece cerrado, abriéndose al llegar el disco a su posición de reposo.

La figura I.5 presenta un diagrama simplificado del circuito, al es tar accionando el disco, en el que se omiten todas las partes cortocircuitadas, así como las que quedan afectadas por la generación de los pulsos de marcar.

El corto circuito efectuado por el interruptor S asegura una diferencia máxima de resistencia entre los períodos de cierre y de apertura de los contactos del interruptor II, además de proteger al oído de los choques acústicos causados por la generación de los pulsos, en el audífono.

Como la fuente de alimentación del cuadro conmutador automático se encuentra conectado constantemente a la línea, circulará corriente por és ta al descolgar el microteléfono. Al marcar el número, como resultado del corto circuito la corriente aumentará, siendo interrumpida completamente al abrirse los contactos del interruptor II.

Cada interrupción produce una chispa, que de persistir, causaría corrosión y picaduras a los contactos. Con el fin de suprimir la chispa, un circuito apagador de chispas consistente en una resistencia (7) y un capacitor (8), se conectará entre los contactos del generador de pulsos. De esta manera, se absorbe la energía creadora de la chispa, sofocándola eficazmente.

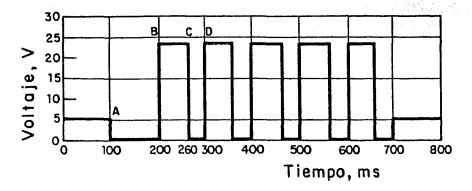

Figura I.6 Gráfica Voltaje-Tiempo durante la generación de los pulsos de marcar.

El diagrama de la figura I.6 muestra las variaciones de voltaje en la línea telefónica durante el periodo de generación de pulsos. En el intervalo previo a la marcación del número (0-A), el voltaje queda en fun-

ción de la resistencia de la línea más la del transformador y la del micrófono.

Al girar el disco de marcar, se cortocircuita la línea, por lo que el voltaje disminuye a cero (A-B). Durante una interrupción, el voltaje crece a su valor máximo por tener la línea abierta (B-C), mientras que en el periodo de cierre que sigue (C-D), el voltaje vuelve a cero.

La frecuencia de generación utilizada en los aparatos de la Ciudad de México, es de diez pulsos por segundo (10 Hz), siendo el ciclo de trabajo del 40%, es decir, que los contactos del interruptor están cerrados durante 40 milisegundos y abiertos 60 milisegundos.

### I.2 BOSQUEJO GENERAL DEL FUNCIONAMIENTO DE UN CUADRO CONMUTADOR AUTOMATICO

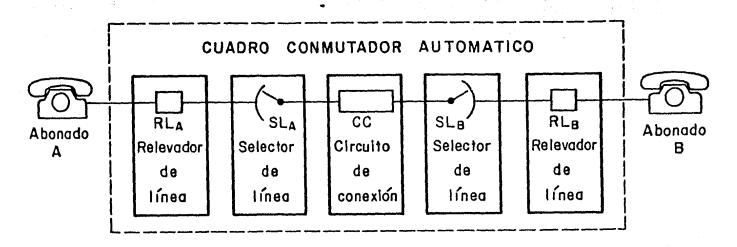

Un cuadro conmutador automático está compuesto principalmente por los siguientes elementos: la fuente de alimentación, relevadores de línea, buscadores de línea o selectores de línea y, el circuito de conexión, en donde están localizados los principales elementos del sistema telefónico.

El diagrama de bloques de la figura I.7 se utilizará para explicar el principio general de funcionamiento.

Figura I.7 Diagrama de bloques de un Cuadro Conmutador Automático de Batería Central.

Cuando El abonado "A" descuelga su microteléfono, se cierra el circuito de línea a través de los contactos del conmutador de horquilla de su aparato. El relevador de línea RLA atrae y cierra un circuito que causa el arranque del selector de línea SLA, el cual busca la línea del abonado en su campo múltiple. Al entrar el selector en contacto con dicha línea previamente señalada por el relevador de línea RLA con un potencial positivo, cierra un interruptor asociado con el circuito de conexión CC, parando la búsqueda del selector.

En seguida, el circuito de conexión emite un zumbido —la señal de marcar— al abonado que llama, para advertirle que la central está en condiciones de recibir el número deseado.

Cuando el abonado "A" marca el número requerido, el selector de línea  ${\rm SL_B}$  avanza, colocándose sobre los contactos correspondientes a la línea del abonado deseado.

A continuación se efecúa la prueba de ocupado y, si se verifica que el abonado "B" está libre, el circuito de conexión envía la señal de llamada a éste, junto con el zumbido de llamada al abonado "A". La señal de llamada se emite en forma intermitente y continúa hasta que haya contesta do el abonado "B". Al contestar éste último, la señal de llamada se suspende y se establece la comunicación.

En el caso de que al efectuar la prueba de ocupado, ésta haya sido positiva, el circuito de conexión envía al abonado "A" el zumbido de ocupado, para indicarle a este abonado el estado de la línea con la que quie re establecer contacto.

La comunicación se deshace al colgar ambos abonados sus microteléfonos. Los selectores de línea  ${\rm SL}_{\rm A}$  y  ${\rm SL}_{\rm B}$  regresan entonces a su posición de reposo.

Los microteléfonos de los abonados quedan alimentados por medio de la fuente de alimentación de la central. Los voltajes utilizados en los sistemas telefónicos de la Ciudad de México, son de 24 y 48 V.

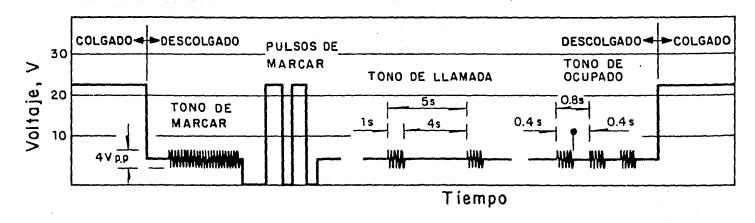

Los zumbidos de llamada, de ocupado y la señal de marcar, tienen una frecuencia de 400 Hz a 600 Hz, con un nivel de voltaje de 4  $V_{p-p}$ . La señal de marcar es un zumbido continuo, mientras que la señal de llamada tiene un periodo de 5 segundos con un ciclo de trabajo del 15% al 20% y, la señal de ocupado tiene un periodo de 0.8 segundos con un ciclo de trabajo del 50%.

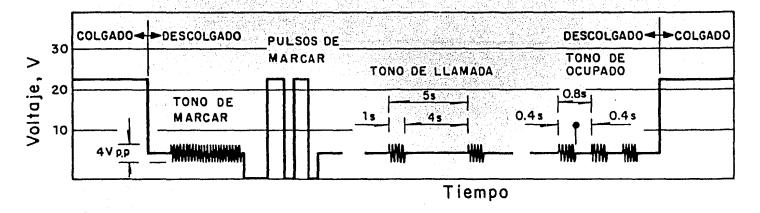

Figura 1.8 Gráfica Voltaje-Tiempo de una línea telefónica individual de 24 V. Se encuentran acotados los valores de interés para el diseño. Los valores de tiempo están fuera de escala.

En la figura I.8 se muestra la gráfica Voltaje-Tiempo de una línea telefónica individual de 24 V. Los valores que están contenidos en esta gráfica tendrán una gran importancia para el diseño del "IMPRESOR DE LLA-MADAS TELEFONICAS".

### CAPITULO II

## EXPLICACION Y COMPARACION DE ALGUNAS FAMILIAS DE CIRCUITOS LOGICOS DIGITALES

El diseño del "IMPRESOR DE LLAMADAS TELEFONICAS" está basado en el procesamiento de datos obtenidos a partir de la línea telefónica individual, de la que se requiere el registro del número marcado y del tiempo que dure la llamada realizada por el abonado.

Actualmente, la forma más adecuada de diseñar cualquier sistema de procesamiento de datos es a través de la tecnología digital, la que utiliza pocas operaciones básicas con las que se pueden desarrollar un gran número de funciones de mayor complejidad, con base en la repetición y combinación múltiple de las primeras.

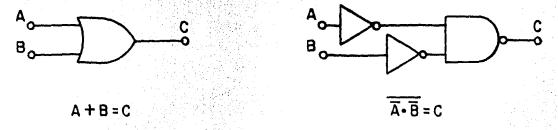

Estas operaciones básicas son implementadas mediante circuitos electrónicos. Los más comúnmente utilizados en los sistemas digitales son conocidos como circuitos OR, AND, NOT o inversor y FLIP FLOP. Estos son los llamados circuitos lógicos o compuertas digitales.

Los circuitos lógicos pueden diseñarse de múltiples maneras: mediante resistencias y transistores bipolares de juntura, agregando capacitores, con resistencias, diodos y transistores, con transistores de efecto de campo (FET), etcétera. Cada una de estas diferentes formas de diseñar

los circuitos, han dado pié a la creación de las diferentes familias o tecnologías de circuitos lógicos digitales.

A continuación se plantearán los principios de diseño y la comparación entre estas familias, para que, con base en esta información, se pue da elegir para este trabajo la que mejor se adapte a las necesidades requeridas.

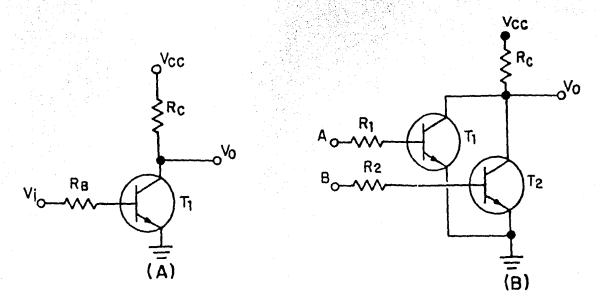

### II.1 LOGICA RTL (RESISTOR TRANSISTOR LOGIC)

En la implementación de circuitos de esta familia lógica, se utilizan únicamente transistores bipolares de juntura y resistencias. Esta fue la primera familia de circuitos lógicos establecida en el mercado de los circuitos integrados.

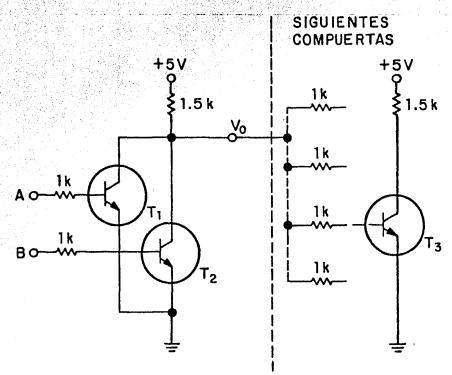

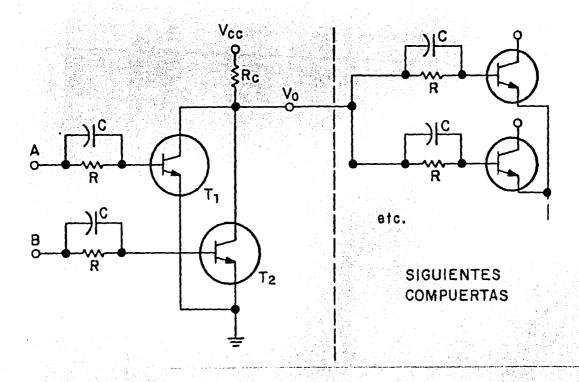

Figura II.1 Circuito básico RTL: compuerta NOR con dos entradas, con abanico de salida de cuatro.

El circuito básico de esta família está mostrado en la figura II.1, el cual representa una compuerta NOR de dos entradas, A y B, cuya salida está conectada a otras cuatro compuertas con entradas similares.

Si alguna de las entradas es "alta", el transistor correspondiente

se satura y por lo tanto la salida será "baja". El voltaje de salida será igual al voltaje de saturación colector-emisor del transistor, o sea, aproximadamente  $V_{\text{CE,sat}} = 0.2 \text{ V}$ .

En caso de que sus dos entradas sean "bajas", todos los transistores de entrada estarán cortados, por lo que la salida será "alta".

De esta manera, se obtiene la tabla de verdad mostrada en la figura II.2, con lo que se puede apreciar que el circuito propuesto opera efectivamente como una compuerta lógica NOR.

| А | В        | Vo |

|---|----------|----|

| 0 | 0        | 1  |

| 0 | <b>1</b> | 0  |

| 1 | 0        | 0  |

| 1 | 1        | 0  |

Figura II.2 Tabla de verdad de la compuerta NOR.

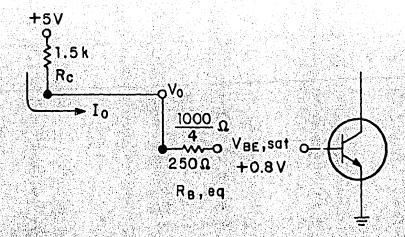

El voltaje de salida, quedará en función del número de entradas a las que esté conectada la compuerta. En este caso, como el número de entradas es de cuatro, entonces la salida estará cargada con cuatro resistencias de 1 k $\Omega$  en paralelo. El equivalente de estas cuatro resistencias de 1 k $\Omega$  será de 250  $\Omega$ , estando conectadas al potencial de saturación base emisor de los transistores de entrada, o sea,  $V_{\rm BE,sat}$  = 0.8 V.

El circuito equivalente está mostrado en la figura II.3. Bajo estas circunstancias, la corriente que circulará por la malla será:

$$I_o = \frac{V_{CC} - V_{BE, sat}}{R_C + R_{B, eq}}$$

;  $I_o = \frac{5 - 0.8}{1.5 + 0.25}$ ;  $I_o = 2.4 \text{ mA}$

Entonces, el voltaje de salida será:

$$V_0 = V_{BE,sat} + R_{B,eq} i$$

;  $V_0 = 0.8 + 0.25 \times 2.4$ ;  $V_0 = 1.4 V_0$

Figura 11.3 Circuito equivalente de la compuerta MOR con salida "alta", cargada con un abanico de salida de cuatro.

Este voltaje debe ser capaz de saturar a los cuatro transistores subsiguientes. La corriente de base en cada uno de ellos será:

$$I_{B} = \frac{V_{O} - V_{BE, sat}}{R_{B}}$$

;  $I_{B} = \frac{1.4 - 0.8}{1}$ ;  $I_{B} = 0.6 \text{ mA}$

y la corriente de colector será:

$$I_{C} = \frac{V_{CC} - V_{CE,sat}}{R_{C}}$$

;  $I_{C} = \frac{5 + 0.2}{1.5}$ ;  $I_{C} = 3.2 \text{ mA}$

por lo tanto, para que el circuito funcione, la ganancia mínima de los transistores β deberá ser:

$$\beta = \frac{I_C}{I_B}$$

;  $\beta = \frac{3.2}{0.6}$ ;  $\beta = 5.33$

Este valor es bastante pequeño que se puede lograr sin ninguna dificultad, tanto en circuitos integrados como en elementos discretos. Si los transistores tienen una ganancia mayor que la anterior, se asegurará que el circuito precedente podrá manejar cuando menos cuatro entradas. Al número máximo de entradas que puede manejar la salida de una compuerta se le denomina "ABANICO DE SALIDA" o FAN OUT. Este depende directamente del voltaje de polarización del circuito, así como de los valores de las re-

sistencias de entrada y de salida en el circuito analizado. El abanico de salida típico para la familia lógica RTL es de cinco.

Otro parámetro de importancia en el diseño de cualquier sistema digital es el "MARGEN DE RUIDO", que se puede definir como el intervalo de voltaje en el que puede variar la entrada sin causar un cambio de nivel en la salida.

En el circuito estudiado, el voltaje de salida "bajo" es de  $V_{\rm O} = 0.2$  V. El voltaje de encendido de los transistores es de  $V_{\gamma} = 0.5$  V, por lo tanto el margen de ruido de este tipo de ciruitos será de 0.3 V. Esto quiere decir que si en la entrada de una compuerta se producen variaciones de voltaje mayores de 0.3 V, el estado de la salida estará expuesto a variaciones. Como se puede apreciar, este valor de margen de ruido es muy pequeño.

La potencia disipada máxima por la compuerta y el tiempo de demora de propagación son otros dos parámetros fundamentales de diseño.

Se define como potencia máxima disipada por la compuerta  $(P_D)$ , a aquella potencia que es disipada por el circuito en el peor de los casos. Para el ejemplo tratado, este caso se presenta cuando las dos entradas son "altas" simultáneamente.

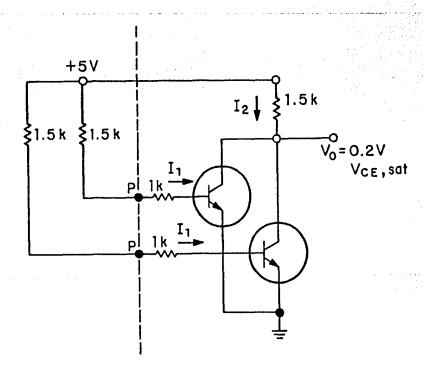

Figura II.4 Circuito simplificado para calcular la potencia máxima disipada por la compuerta.

La figura II.4 muestra el circuito simpoificado para el cálculo de la potencia máxima disipada por la compuerta.

$$I_{1} = \frac{V_{CC} - V_{BE, sat}}{R_{C} + R_{B}}; \quad I_{1} = \frac{5 - 0.8}{1.5 + 1}; \quad I_{1} = 1.68 \text{ mA}$$

$$V_{P} = V_{BE, sat} + R_{B}I_{1}; \quad V_{P} = 0.8 + 1 \times 1.68; \quad V_{P} = 2.48 \text{ V}$$

$$I_{2} = \frac{V_{CC} - V_{CE, sat}}{R_{C}}; \quad I_{2} = \frac{5 - 0.2}{1.5}; \quad I_{2} = 3.2 \text{ mA}$$

$$P_{D} = 2V_{P}I_{1} + V_{CC}I_{2}; \quad P_{D} = 2 \times 2.48 \times 1.68 + 5 \times 3.2;$$

$$P_{D} = 24.33 \text{ mW}$$

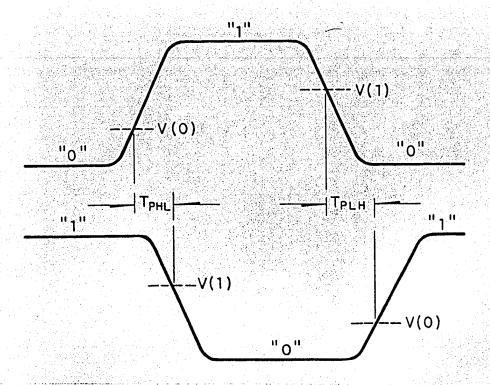

Por último, el tiempo de demora de propagación T<sub>PD</sub> se puede definir de la siguiente manera: considerando que la entrada tiene una cierta constante de tiempo tanto de "subida" (de "0" a "1" lógicos) como de "bajada" (de "1" a "0"), el cambio de estado de la salida queda en función de esta constante de tiempo, así como los voltajes de "encendido" -V(1)- y de apagado -V(0)- de la compuerta, es decir, los niveles de voltaje en los cuales la salida de la compuerta empieza a cambiar de estado, de "0" a "1" o de "1" a "0" respectivamente. En general los valores de estos dos voltajes son diferentes.

Con base en la compuerta NOR explicada en párrafos anteriores, interconectando todas las entradas de la compuerta se podrá obtener la gráfica comparativa de voltajes de entrada y de salida de la compuerta contra el tiempo, mostrada en la figura II.5.

El tiempo de propagación de "encendido" ( $T_{\rm PLH}$  o Low to High Propagation Time) será el tiempo que demora desde que la entrada alcanza el voltaje de "encendido" V(1), hasta que la salida alcanza el voltaje de "apagado" V(0). De la misma manera, el tiempo de propagación de "apagado" ( $T_{\rm PHL}$  o High to Low Propagation Time) se podrá definir como el tiempo que demora desde que la entrada "sube" al voltaje de "apagado" V(0), hasta que la salida llega al voltaje de "encendido" V(1).

En general, los tiempos de propagación de "encendido" y de "apagado" son diferentes, causado por el tiempo de almacenamiento de los portadores minoritarios de los transistores.

Figura II.5 Gráfica de Voltaje de entrada  $(V_i)$  y de Voltaje de salida  $(V_o)$  contra Tiempo para determinar los tiempos de propagación.

Entonces, el Tiempo de Demora de Propagación se define como el promedio de estos dos últimos tiempos:

$$T_{PD} = \frac{1}{2} (T_{PLH} + T_{PHL})$$

Para los circuitos de la familia lógica RTL, el tiempo de demora de propagación tiene un valor típico de 12 ns (nanosegundos), o sea, 12 × 10<sup>-9</sup> segundos, con un abanico de salida de cinco; este valor es un tiempo bastante bajo, por lo que se puede aplicar esta familia lógica en el diseño de sistemas rápidos, lo cual constituye una ventaja de la familia RTL.

Otra ventaja de esta familia lógica es que utiliza un espacio reducido para funciones digitales estándar sobre el cristal de silicio, cuan do es fabricado como circuito integrado, por lo que resulta ser muy económico.

Una familia lógica derivada de la RTL es la familia RCTL (Resistor Capacitor Transistor Logic), en la que a las resistencias de la base de

Figura 11.6 Circuito básico RCTL.

los transistores se les agreça un capacitor de aceleración de carga de la capacitancia parásita de la juntura base-emisor del transistor, conectán-dose en paralelo. La figura II.6 muestra el circuito básico RCTL.

Por la razón mencionada anteriormente, es posible aumentar el valor de las resistencias de entrada, logrando disminuir la potencia disipada con respecto a la familia antecedente, además de disminuir notoriamente el tiempo de demora de propagación.

Pero el hecho de utilizar varios valores de resistencias mayores y capacitores en el circuito integrado hacen que aumente considerablemente el tamaño del cristal de silicio, ya que los capacitores ocupan un área de cinco veces el de un transistor y, el área que ocupa una resistencia es directamente proporcional a su valor óhmico. Se deduce que el costo de los circuitos de esta familia lógica es significativamente mayor que el de la familia RTL.

Las familias lógicas RTL y RCTL fabricadas en circuitos integrados, se dejaron de utilizar a partir de los primeros años de la década de los sesentas y han dejado paso a otras tecnologías más avanzadas en los circuitos lógicos digitales.

### II.2 LOGICA DTL (DIODE TRANSISTOR LOGIC)

El funcionamiento de este circuito es fácilmente comprensible de una manera cualitativa. Como su nombre lo indica, esta familia de circuitos lógicos es implementada con diodos, transistores bipolares de juntura y resistencias.

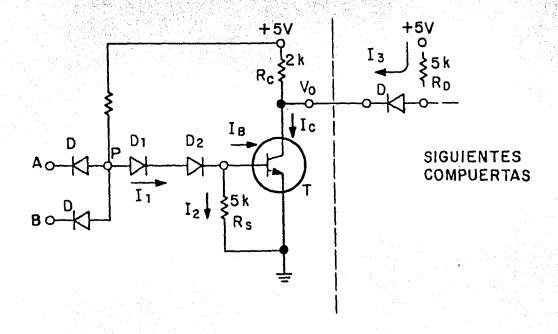

El circuito básico de la familia lógica DTL está mostrado en la figura II.7. Si cuando menos una de las entradas es "baja" ( $V_i = 0.2 \text{ V}$ ), el diodo "D" conectado a dicha entrada conducirá por lo que el voltaje en el punto "P" será  $V_p = 0.9 \text{ V}$ . Este valor de voltaje no es suficiente para poner en funcionamiento al transistor "T" por lo que éste quedará cortado. De esta manera, la salida será "alta", es decir,  $V_i = 5 \text{ V}$ , considerando que no se tiene conectada a la salida ninguna carga.

Figura II.7 Circuito básico DTL: compuerta NAND con dos entradas.

En el caso de que las dos entradas sean "altas", los diodos de entrada quedarán cortados. Entonces circulará corriente a través de la resistencia  $R_D$  y los diodos  $D_1$  y  $D_2$ , a la base del transistor al cual lo saturará, siendo la salida "baja". El voltaje de salida  $V_O$  será igual al voltaje colector-emisor de saturación del transistor, o sea,  $V_O$  = 0.2  $V_O$

En la figura II.8 se presenta la tabla de verdad de este circuito, con la que se comprueba que opera como una compuerta NAND.

| Å | В | Vo |

|---|---|----|

| 0 | 0 |    |

| 0 | 1 |    |

|   | О |    |

| 1 | 1 | 0  |

Figwra II.8 Tabla de verdad de La compuerta NAND.

Para demostrar que el transistor está realmente saturado cuando las dos entradas son "altas", se procederá de la siguiente manera: la corriente  $I_1$  que circula por los diodos  $D_1$  y  $D_2$  quedará determinada como:

$$I_{1} = \frac{V_{CC} - V_{BE, sat} - 2 \times V_{D}}{R_{D}}; \quad I_{1} = \frac{5 - 0.8 - 2 \times 0.7}{5};$$

$$I_{1} = 0.56 \text{ mA}$$

$$I_{2} = \frac{V_{BE, sat}}{R_{S}}; \quad I_{2} = \frac{0.8}{5}; \quad I_{2} = 0.16 \text{ mA}$$

$$I_{B} = I_{1} - I_{2}; \quad I_{B} = 0.56 - 0.16; \quad I_{B} = 0.4 \text{ mA}$$

$$I_{C} = \frac{V_{CC} - V_{CE, sat}}{R_{C}}; \quad I_{C} = \frac{5 - 0.2}{2}; \quad I_{C} = 2.4 \text{ mA}$$

$$\beta = \frac{I_{C}}{I_{B}}; \quad \beta = \frac{2.4}{0.4}; \quad \beta = 6$$

Por lo tanto, si se cuenta con transistores con una ganancia mayor de  $\beta$  = 6, se asegurará la saturación del transistor "T" y por lo tanto el funcionamiento del circuito.

Los diodos D $_1$  y D $_2$  sirven para aumentar el margen de ruido del circuito. Para que "encienda" el transistor "T", es necesario que cuando alguna de las entradas sea "baja", el valor del voltaje  $V_p$  sea:

$$V_{P} = V_{\gamma} + 2 \times V_{D}$$

;  $V_{P} = 0.5 + 2 \times 0.7$ ;  $V_{P} = 1.9 \text{ V}$

Para ello, dicha entrada necesitará tener un valor mínimo de 1.2 V. Por lo tanto, el margen de ruido en este caso será de 1.2 - 0.2 = 1 V. Si se eliminara uno de los diodos, este margen de ruido se reduciría a 1 - 0.7 = 0.3 V. Si las entradas son "altas":

$$V_{P} = V_{CC} - R_{D+1}^{I}$$

;  $V_{P} = 5 - 5 \times 0.56$ ;  $V_{P} = 2.2 \text{ V}$

por lo tanto, los diodos de entrada estarán polarizados inversamente con un valor de voltaje menor de 1.6 V, por lo que en este caso, el margen de ruido sería de 3.4 V.

Para calcular el abanico de salida de este circuito, es necesario considerar el caso de máxima carga del transistor "T". Este caso sucederá cuando la salida sea "baja". Con base en la figura II.7, se puede observar que el transistor tiene que ser capaz de absorber a todas las corrientes I de cada una de las compuertas subsiguientes, si la salida es "baja". Entonces, la corriente total del colector con un abanico de salida "n" será:

$$I_{C,tot} = I_{C} + nI_{3}$$

y por otro lado:

$$I_3 = \frac{V_{CC} - V_D - V_{CE,sat}}{R_D}$$

;  $I_3 = \frac{5 - 0.7 - 0.2}{5}$ ;  $I_3 = 0.82 \text{ mA}$

y si se considera una ganancia mínima del transistor  $\beta$  = 30, el abanico de salida máximo será:

$$n = \frac{I_{C,tot} - I_{C}}{I_{3}}$$

,  $n = \frac{\beta I_{B} - I_{C}}{I_{3}}$ ,  $n = \frac{30 \times 0.4 - 2.4}{0.82}$

$$n = 11.7$$

Entonces, se puede afirmar que este circuito es capaz de manejar a casi 12 compuertas sin problema, suponiendo el valor de ganancia correspondiente.

La potencia disipada con un abanico de salida de doce será:

$$P_D = V_{CC}I_1 + R_CI_2^2 + V_{CE,sat}I_{C,tot};$$

$P_D = 5 \times 0.56 + 2 \times 2.4^2 + 0.2 \times 12.24 ; P_D = 16.77 \text{ mW}$

El tiempo de demora de propagación típico de la familia lógica DTL es de 30 ns, comparativamente mayor con respecto a la tecnología RTL.

### II.3 LOGICA HTL (HIGH THRESHOLD LOGIC)

Esta familia lógica se originó de la necesidad de contar con sistemas digitales que pudieran funcionar con altos niveles de ruido afectándo los, como es el caso de las plantas industriales en que por la presencia de motores, interruptores de alta tensión, circuitos de control de apagado-encendido, generan niveles de ruido muy altos.

Entonces, una de las características más importantes de esta tecnología es que debe de contar con un considerable margen de ruido. Su nombre significa Lógica con Altos Niveles de Voltaje de "apagado-encendido".

Con base en el circuito de la familia DTL anteriormente analizado y realizando algunas modificaciones, se puede lograr la característica deseada, pero afectando significativamente a otros parámetros.

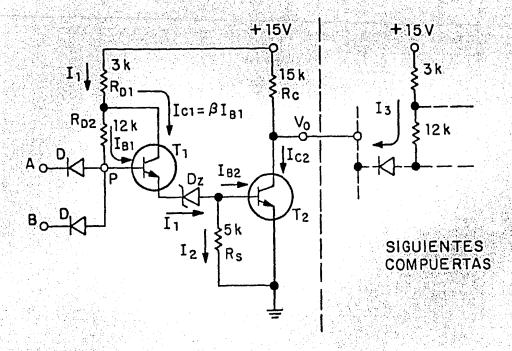

El circuito de la figura II.9 muestra una compuerta NOR, que es la compuerta básica de esta familia lógica. Como se puede apreciar, en lugar deñ diodo  $\mathrm{D}_1$  aparece el transistor  $\mathrm{T}_1$ , con el fin de aumentar el abanico de salida y, en lugar del diodo  $\mathrm{D}_2$ , se le reemplaza por un diodo "zener" de 6.9 V de voltaje de ruptura, para aumentar el margen de ruido. Este reemplazo requerirá aumentar también el voltaje de alimentación y, por lo tanto, la potencia disipada será mayor.

El circuito funciona de una manera similar al de la familia DTL ana

lizada en el inciso anterior.

Figura 11.9 Circuito básico HTL.

Para comprobar que la inclusión del transistor  $T_1$  aumenta el abanico de salida y el zener  $D_Z$  por el diodo  $D_2$  aumenta el margen de ruido, se procederá a continuación como sigue: cuando las dos entradas son "altas", los diodos de entrada "D" quedarán cortados por lo que circulará corriente por los transistores  $T_1$  y  $T_2$ , a través de las resistencias  $R_{D1}$ ,  $R_{D2}$  y el zener  $D_Z$ . Considerando una ganancia mínima de los transistores de  $\beta = 30$ :

$$I_1 = I_{B1} + I_{C1}$$

;  $I_1 = I_{B1}(1 + \beta)$ ;  $I_1 = 31I_{B1}$

el voltaje en el punto "P" será:

$$V_{p} = V_{BE1,act} + V_{z} + V_{BE2,sat}$$

;  $V_{p} = 0.7 + 6.9 + 0.8$ ;  $V_{p} = 8.4 \text{ V}$

entonces:

$$V_{CC} - V_{p} = R_{D1}I_{1} + R_{D2}I_{B2}$$

,  $15 - 8.4 = 3 \times 31I_{B1} + 12 \times I_{B1}$ ;  $105I_{B1} = 6.6$ ,  $IB_{1} = 0.063$  mA,  $I_{1} = 1.95$  mA

$$I_2 = \frac{V_{BE, sat}}{R_S}$$

;  $I_2 = \frac{0.8}{5}$ ;  $I_2 = 0.16 \text{ mA}$

$I_{B2} = I_1 - I_2$ ;  $I_{B2} = 1.95 - 0.16$ ;  $I_{B2} = 1.79 \text{ mA}$

Calculando la corriente I para comprobar la saturación del transistor  $\mathbf{T}_2$ :

$$I_{C2} = \frac{V_{CC} - V_{CE,sat}}{R_{C}}$$

;  $I_{C2} = \frac{15 - 0.2}{15}$ ;  $I_{C2} = 0.987 \text{ mA}$

por lo tanto, el transistor T<sub>2</sub> está saturado.

Procediendo de forma similar al circuito DTL, el abanico de salida máximo será:

$$n = \frac{I_{C2, tot} - I_{C2}}{I_{3}},$$

$$I_{C2,tot} = \beta I_{B2}$$

;  $I_{C2,tot} = 30 \times 1.79$ ;  $I_{C2,tot} = 53.66 \text{ mA}$

$$I_3 = \frac{\frac{V_{CC} - V_{D} - V_{CE,sat}}{R_{D1} + R_{D2}}$$

;  $I_3 = \frac{15 - 0.7 - 0.2}{3 + 12}$ ;  $I_3 = 0.94 \text{ mA}$

por lo tanto:

$$n = \frac{53.66 - 0.987}{0.94}$$

;  $n = 56$

Como se puede apreciar, el abanico de salida aumenta considerablemente al sustituir  $D_1$  por el transistor  $T_1$ .

Siendo el voltaje  $V_p=8.4~V$ , si la entrada es "alta", los diodos "D" estarán polarizados inversamente por un voltaje de 15 - 8.4 = 6.6 V. Por lo tanto, para poder "encender" los diodos, se requerirá un voltaje mínimo de 6.6 + 0.6 = 7.2 V.

En el caso de que alguna de las entradas sea "baja", el voltaje  $V_{

m p}$  será:

$$V_{p} = V_{o} + V_{D}$$

;  $V_{p} = 0.2 + 0.7$ ;  $V_{p} = 0.9 V$

por lo que para poder "encender" al transistor  $T_2$ , se requerirá un voltaje mínimo de:

$$V_{p} = V_{\gamma 1} + V_{z} + V_{\gamma 2}$$

;  $V_{p} = 0.5 + 6.9 + 0.5$ ;  $V_{p} = 7.9 \text{ V}$

por lo tanto, el margen de ruido será cuando menos de 7 V, valor que resulta ser bastante adecuado cuando se opera bajo condiciones extremas de niveles de ruido. La potencia máxima disipada será:

$$P_D = V_{CC}I_1 + R_{C}I_{C2}^2 + V_{CE;sat}I_{C2;tot};$$

$P_D = 15 \times 1.95 + 15 \times 0.987^2 + 0.2 \times 53.66; P_D = 54.58 \text{ mW}$

valor que es significativamente mayor con respecto al circuito DTL analizado anteriormente.

El aumento de potencia es ocasionado principalmente por el valor ma yor de voltaje de polarización y, en menor grado, por el aumento del abanico de salida máximo, como puede apreciarse.

Al mismo tiempo, al utilizar el transistor  $T_1$  y el diodo zener  $D_Z$ , se afecta considerablemente al tiempo de demora de propagación. El valor típico de este parámetro para la familia HTL es de unos 90 ns.

### II.4 LOGICA TTL (TRANSISTOR TRANSISTOR LOGIC)

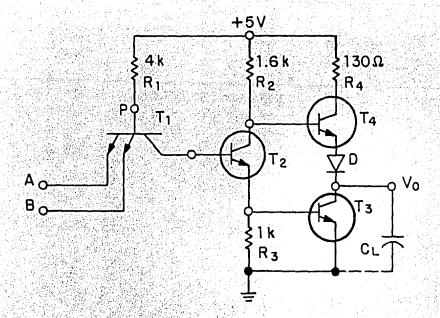

Esta familia lógica también está basada en la topología de los circuitos de la tecnología DTL. El circuito básico que funciona como una compuerta NAND similar al de los circuitos anteriormente presentados (DTL y HTL) está mostrado en la figura II.10.

En lugar de los diodos "D" de entrada, en los circuitos TTL son sus tituidos por las junturas base-emisor de un transistor multiemisor y, reemplazando al diodo  $\mathrm{D}_1$  se tiene la juntura base-colector del mismo transistor. Así mismo, el transistor  $\mathrm{T}_2$  es utilizado en lugar del diodo  $\mathrm{D}_2$  del circuito DTL, teniendo éste al transistor  $\mathrm{T}_2$  en la etapa de salida.

Figura II.10 Circuito básico TTL: compuerta NAND de dos entradas, con etapa de salida tipo "TOTEM POLE".

En los circuitos TTL, la etapa de salida es implementada mediante una configuración conocida como "TOTEM POLE", la cual actúa de tal manera que disminuye la constante de tiempo en los cambios de estado a la salida de la compuerta, acelerando la carga de las capacitancias parásitas de las compuertas subsiguientes.

La explicación del funcionamiento del circuito TTL se presenta a continuación.

Si cuando menos una de las entradas es "baja", V = 0.2 V, entonces:

$$V_{P} = V_{i} + V_{BE,act}$$

;  $V_{P} = 0.2 + 0.7$ ;  $V_{P} = 0.9 \text{ V}$

Para que la juntura base-colector de  $T_1$  esté polarizado directamente así como para el encendido de los transistores  $T_2$  y  $T_3$ , se requiere un nivel de voltaje  $V_p$  alrededor de:

$$V_{p} = V_{CE3,act} + V_{CE2,act} + V_{BC,dir}$$

;  $V_{p} = 0.7 + 0.7 + 0.7$ ;  $V_{p} = 2.1 \text{ V}$

De ésto se deduce que los transistores T2 y T3 están apagados y la

juntura base-colector no conduce. De esta manera, la salida es "alta".

En el caso de que ambas entradas sean "altas", las junturas base-emisor del transistor de entrada estarán inversamente polarizadas, por lo que circulará corriente a través de la resistencia  $\mathbf{R}_1$  y la juntura base-colector de  $\mathbf{T}_1$ , saturando a  $\mathbf{T}_2$  y a  $\mathbf{T}_3$ . La salida por lo tanto, será "baja", con un voltaje  $\mathbf{V}_1$  de:

$$V_{o} = V_{CE3,sat}$$

;  $V_{o} = 0.2 V_{ce3}$

El voltaje en "P" será:

$$V_{p} = V_{BE3,sat} + V_{BE2,sat} + V_{BC,dir}; V_{p} = 0.8 + 0.8 + 0.7;$$

$$V_{p} = 2.3 \text{ V}$$

Aparentemente, el transistor multiemisor T<sub>1</sub> sólamente parece tener las funciones de diodos interconectados y no las de un transistor. Empero, Su funcionamiento como transistor se presenta durante el "apagado" del circuito.

Cuando la salida es "baja", el potencial en la base de  $T_2$  es igual al del colector de  $T_1$ , siendo de 0.8+0.8=1.6 V durante la saturación de  $T_2$  Y  $T_3$ . Si ahora, alguna de las entradas "baja" a  $V_1=0.2$  V, entonces  $V_p=0.9$  V, por lo cual la base de  $T_1$  quedará sujeta a dicho potencial. En este instante, la juntura base-colector de  $T_1$  estará inversamente polarizada, por lo que se deduce que este transistor funcionará dentro de su región activa.

La corriente de colector generada de esta manera en  $T_1$  removerá rápidamente la carga almacenada en  $T_2$  y  $T_3$ . Esta es la característica por la que la familia TTL proporciona la más alta velocidad entre las lógicas basadas en la saturación de los transistores.

El valor típico del tiempo de demora de propagación de esta familia lógica es de 8 ns.

El funcionamiento de la configuración "TOTEM POLE" de la etapa de salida de los circuitos TTL es como sigue. Cuando los transistores  $\mathbf{T}_2$  y  $\mathbf{T}_3$  están saturados, la salida de la compuerta es "baja", como se explicó anteriormente. Por lo tanto, la base del transistor  $\mathbf{T}_4$  quedará a un poten

cial de:

$$V_{B4} = V_{BE3,sat} + V_{CE2,sat}$$

;  $V_{B4} = 0.8 + 0.2$ ;  $V_{B4} = 1.0 \text{ V}$

y el emisor del mismo transistor:

$$V_{E4} = V_{CE3,sat} + V_{D}$$

;  $V_{E4} = 0.2 + 0.7$ ;  $V_{E4} = 0.9$  V

Esto quiere decir que el transistor  $T_4$  estará cortado, por lo que la corriente de colector de  $T_3$  estará en función únicamente del abanico de salida, sin verse aumentada por la corriente propia de esta etapa de salida.

En caso de que se omitiera el diodo "D", el potencial en el emisor de  $T_4$  sería  $V_{E4}=0.2$  V, por lo que este transistor quedaría saturado. Bajo estas condiciones, la corriente de colector que circularía a través de él tendría un valor de:

$$I_{C} = \frac{V_{CC} - V_{CE4, sat} - V_{CE3, sat}}{R_{4}}$$

;  $I_{C} = \frac{5 - 0.2 - 0.2}{0.13}$ ;  $I_{C} = 35.40 \text{ mA}$

el cual sería un valor excesivo e inútil.

Además, la carga capacitiva de la salida al cambiar a estado "bajo" la salida de la compuerta, es rápidamente descargada a través del transistor T<sub>3</sub>.

Ahora, haciendo la consideración de que una de las entradas cambia a un estado "bajo",  ${\rm T_2}$  quedará cortado, lo cual causará que  ${\rm T_3}$  también se corte, ya que el voltaje  ${\rm V_{RE3}}$  se hace cero.

La salida se mantiene momentáneamente con un voltaje  $V_O = 0.2 \text{ V}$ , debido a que el potencial en la carga capacitiva no cambia instantáneamente.

El corte de  ${\bf T}_2$  causará entonces la saturación de  ${\bf T}_4$  en ese momento; la corriente de base instantánea será:

$$I_{B4} = \frac{V_{CC} - V_{BE4, sat} - V_{D} - V_{O}}{R_{2}}$$

,  $I_{B4} = \frac{5 - 0.8 - 0.7 - 0.2}{1.6}$ ,

$$I_{B4} = 2.06 \text{ mA}$$

y la corriente de colector tendrá un valor de:

$$I_{C4} = \frac{\frac{V_{CC} - V_{CE4,sat} - V_{O} - V_{O}}{R_{4}}; \quad T_{C4} = \frac{\frac{5 - 0.2 - 0.7 - 0.2}{0.13}; \quad T_{C4} = \frac{1}{10.13}; \quad T_{C4} = \frac{1}{10.13}$$

For lo tanto, considerando una ganancia mínima de  $\beta$  = 30, se asegura la saturación de  $T_4$ . Este transistor mientras permanezca saturado, estará funcionando como una fuente de corriente cargando las capacitancias parásitas del abanico de salida. El voltaje de salida  $V_0$  crecerá con una constante de tiempo muy pequeña, con un valor:

$$\tau = (R_4 + R_{CE,sat} + R_d)C$$

donde  $R_{CE,sat}$  es la resistencia de saturación entre el colector y el emisor y,  $R_d$  es la resistencia del diodo polarizado en directa.

Al crecer V , la corriente en T disminuye paulatinamente, por lo que finalmente en estado estable, el voltaje de salida tendrá un valor:

$$v_0 = v_{CC} - v_1 - v_{DY}$$

;  $v_0 = 5 - 0.5 - 0.6$ ;  $v_0 = 3.9$   $v_0$

La función de la resistencia  $R_4$  es la de limitar la corriente pico de carga de la capacitancia parásita  $C_{_{\!\!\!T}}$  a un valor:

$$I_{CA} + I_{BA} = 32 \text{ mA}$$

Si no se incluyera esta resistencia, prácticamente se tendría un impulso de corriente  $(I_0^{\to\infty})$ , lo cual generaría ruido en la fuente de alimentación e incrementaría el consumo de potencia, sobre todo al requerir altas frecuencias de operación.

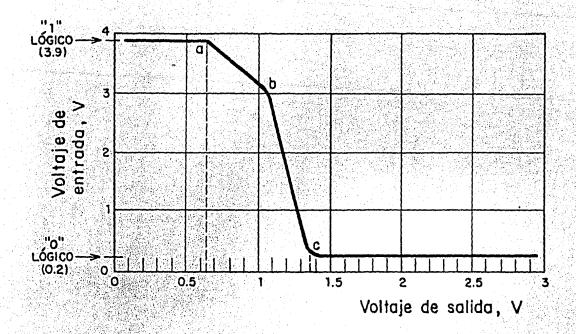

La figura II.11 muestra la gráfica de la función de transferencia voltaje de entrada  $V_i$  contra voltaje de salida  $V_o$ , de una compuerta de la familia TTL.

Figura II.11 Gráfica de la función de transferencia de una compuerta TTL.

Haciendo la consideración que las entradas de la compuerta se encuentran interconectadas entre sí, si el voltaje de entrada  $V_i$  = 0.2 V (estado "bajo"), el voltaje de salida  $V_o$  será  $V_o$  = 3.9 V.

A partir de este estado, al ir incrementando el voltaje de entrada  $V_i$ , la corriente de base de  $T_1$  gradualmente se irá desviando del emisor al colector, causando que el transistor  $T_2$  conduzca. Esta condición ocurre a un valor de  $V_i$  = 0.7 V aproximadamente (punto "a" de la gráfica).

El transistor  $T_2$  funcionará en su región lineal con una ganancia de terminada por la razón  $R_2$  entre  $R_3$ . Como el transistor  $T_4$  permanece encendido, la salida estará comandada por el funcionamiento de  $T_2$ . Entonces, el voltaje de la salida decrecerá con una pendiente:

$$\frac{R_2}{R_3}$$

= 1.6 (del punto "a" al punto "b" de la gráfica)

Cuando  $V_i = V_b$  ( $V_b = 1.1 \text{ V}$ ), la entrada es lo suficientemente alta para causar el encendido del transistor  $T_3$ . Esto origina la disminución drástica de la impedancia del emisor de  $T_2$ , por lo que la ganancia aumenta considerablemente. Esta es la razón por la cual, la curva de transferencia "baja" con una pendiente mucho mayor al anterior, entre los pun-

tos "b" y "c".

Por último, a partir de un valor  $V_i = V_c$  ( $V_c = 1.4$  V), el transistor  $T_4$  se corta, dando como resultado que el estado de la salida sea "0" lógico, con un voltaje  $V_c = 0.2$  V.

Los valores típicos de algunos parámetros importantes de esta familia lógica son: un abanico de salida típica de diez, potencia máxima disipada por compuerta  $P_D$  = 20 mW, margen de ruido en estado "alto" de 2 V y en estado "bajo" de 0.8 V.

La principal desventaja es que la fuente de alimentación tiene un intervalo muy rígido, entre 4.75 y 5.25 V.

La tecnología TTL tuvo una gran difusión y demanda en los primeros años de la década pasada debido principalmente a su economía, gran versatilidad y características muy adecuadas en general.

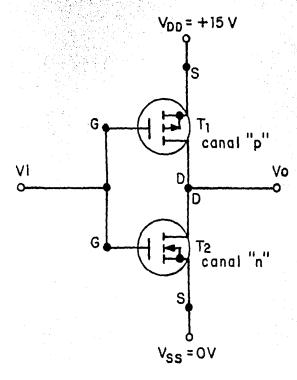

Sin embargo, por la búsqueda constante de tecnologías más avanzadas en las que se obtuvieran mayor economía y mejores características, la familia TTL tuvo que ceder su lugar a la familia lógica CMOS, la cual es una de las más utilizadas en la actualidad.

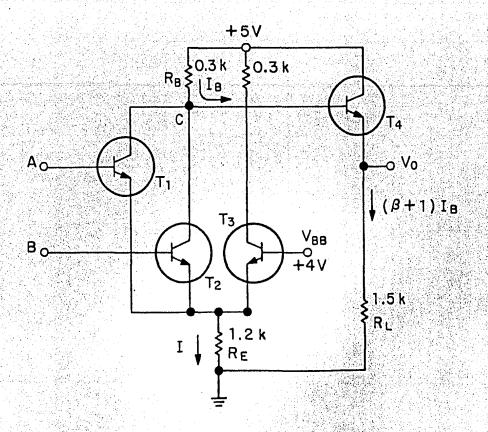

### II.5 LOGICA ECL (EMITTER COUPLED LOGIC)

Esta familia lógica está basada en el funcionamiento del amplificador diferencial, en el que la corriente del emisor permanece prácticamente sin variaciones.

El circuito básico de la tecnología ECL está mostrado en la figura II.12. Los emisores de los transistores  $\mathbf{T}_1$  y  $\mathbf{T}_2$  están interconectados entre sí junto con el emisor del transistor de referencia  $\mathbf{T}_3$ . La resistencia de emisor-común  $\mathbf{R}_{\mathrm{E}}$  hace la función de una fuente de corriente constante, con un valor de corriente de:

$$I = \frac{V_{BB} - V_{BE3,act}}{R_{E}}$$

;  $I = \frac{4 - 0.7}{1.2}$ ;  $I = 2.75 \text{ mA}$

debido a que la base del transistor de referencia  $T_3$  está conectado a un voltaje de referencia  $V_{\rm RR} = 4$  V.

Figura II.12 Circuito básico ECL: compuerta NOR con dos entradas.

El circuito funciona de la siguiente manera: cuando ambas entradas tienen un potencial menor de  $V_i = V_{BB}$ , o sea,  $V_i = 4$  V, los transistores de entrada  $T_1$  y  $T_2$  estarán cortados. Por lo tanto, el transistor  $T_4$  se en cenderá y el voltaje de salida tendrá un valor  $V_0 = R_L I_B(\beta + 1)$ .

Suponiendo una ganancia mínima del transistor de  $\beta$  = 30, el valor del voltaje de salida se podrá calcular de la siguiente manera:

$$I_{B} = \frac{V_{CC} - V_{BE4,act} - V_{O}}{R_{B}}; \quad R_{B}I_{B} = V_{CC} - V_{BE4,act} - V_{O};$$

$$R_{B}I_{B} = V_{CC} - V_{BE4,act} - R_{L}I_{B}(\beta + 1);$$

$$I_{B}[R_{B} + R_{L}(\beta + 1)] = V_{CC} - V_{BE4,act};$$

$$I_{B} = \frac{V_{CC} - V_{BE,act}}{R_{B} + R_{L}(\beta + 1)}; \quad I_{B} = \frac{5 - 0.7}{0.3 + 1.5(30 + 1)};$$

$$I_{B} = 0.092 \text{ mA}$$

por lo tanto:

$$V_{O} = R_{L} I_{B} (\beta + 1)$$

;  $V_{O} = 1.5 \times 0.092 \times 31$ ;  $V_{O} = 4.3 V$

Cuando una de las entradas es mayor del valor  $V_{BB}=4$  V, la corriente circulará a través del transistor correspondiente, causando que el voltaje de salida V taje del colector disminuya, lo que provocará que el voltaje de salida V también decrezca, produciendo una salida "baja". El valor de este voltaje se calculará a continuación, suponiendo un voltaje de entrada  $V_{i}=4.3$  V (estado "alto":

$$I = \frac{V_1 - V_{BE1,act}}{R_E}; \quad I = \frac{4.3 - 0.7}{1.2}; \quad I = 3 \text{ mA}$$

$$V_C = V_{CC} - R_B I; \quad V_C = 5 - 0.3 \times 3; \quad V_C = 4.1 \text{ V}$$

$$V_C = V_C - V_{BE4,act}; \quad V_C = 4.1 - 0.7; \quad V_C = 3.4 \text{ V}$$

La diferencia entre los voltajes de salida de los estados "alto" y "bajo" es de únicamente 0.9 V. Por lo mismo, el margen de ruido que puede esperarse de este tipo de circuito es pequeño, del orden de 0.3 V.

La principal ventaja que ofrece esta familia lógica, es debida a que funciona sin que ninguno de sus transistores componentes llegue a saturarse, por lo que el tiempo de demora de propagación es sumamente baja, con un valor típico de 2 ns. Sin embargo, la potencia disipada máxima es relativamente alta, típicamente de 50 mW.

Esta familia lógica fue utilizada sobre todo en computadoras grandes, donde las desventajas por tiempo de demora de propagación eran mayores a las causadas por el aumento de la potencia de alimentación requerida.

Otra ventaja de la familia ECL es sobre su abanico de salida alto, del orden de 25, obtenido principalmente al contar con una impedancia de salida baja, ya que su etapa de salida es del tipo "seguidor-emisor".

#### II.6 CUADRO COMPARATIVO DE LAS FAMILIAS LOGICAS DIGITALES

Para resumir los conceptos vertidos a lo largo de este capítulo, to mando los resultados teóricos obtenidos y agregando los valores de algunos parámetros de las familias MOS y CMOS que se analizarán en el siguien te capítulo, se muestra en el cuadro de la figura II.13 la comparación de las principales familias lógicas digitales.

| LOGICA                                  | RTL | DTL  | HTŮ  | тт∟       | ECL | MOS     | CMOS |

|-----------------------------------------|-----|------|------|-----------|-----|---------|------|

| PARAMETRO                               |     |      |      | ere ji ti |     |         |      |

| COMPUERTA<br>BASICA                     | NOR | NAND | NAND | NAND      | NOR | NAND    | NAND |

| ABANICO DE SALIDA<br>(FAN OUT)          | 5 · | 10   | 25   | 10        | 25  | 20      | >50  |

| POTENCIA DISIPADA<br>POR COMPUERTA, mW  | 25  | 20   | 55   | 20        | 50  | 0.02~45 | 0.01 |

| MARGEN DE<br>RUIDO, V                   | 0.3 | 0.8  | 7.0  | 0.4       | 0.3 | 1.0     | 1.0  |

| TIEMPO DE DEMORA<br>DE PROPAGACION, n s | 12  | 30   | 90   | 9         | 2   | 300     | 70   |

| FUENTE DE<br>ALIMENTACION, V            | 5   | 5    | 15   | 5         | 5   | 3~15    | 3~15 |

Figura II.13 Cuadro comparativo de las principales familias lógicas digitales.

#### CAPITULO III

## FAMILIAS LOGICAS DIGITALES CON TRANSISTORES DE EFECTO DE CAMPO

Durante los últimos años se han desarrollado varios tipos de líneas de componentes de procesamiento digital de datos.

Algunos de los factores importantes para el diseño de componentes digitales son: los requerimientos de voltaje de alimentación y de potencia, la confiabilidad de operación, la inmunidad al ruido, el costo, la velocidad (frecuencia máxima de operación), la estabilidad térmica, la compatibilidad y, la disponibilidad en el mercado.

Los circuitos de la familia lógica CMOS tienen en la mayoría de los factores anteriores excelentes características. Aunque existen familias lógicas con más altas frecuencias de operación (más rápidas), la mayoría de las nuevas aplicaciones de circuitos digitales no requieren una velocidad que exceda la que puede proporcionar un circuito CMOS (10 MHz). Así mismo, estas nuevas aplicaciones necesitan la optimación de otros factores, tales como alto margen de ruido, buena estabilidad térmica y baja potencia de disipación, los cuales son algunas de las excelentes características ofrecidas por la familia CMOS.

El término genérico CMOS está basado en las letras en inglés, de

las palabras Semiconductor Oxidado y Metalizado con simetría Complementaria (Complementary-symmetry Metal Oxide Semiconductor).

Para comprender el funcionamiento de estos dispositivos, se analiza rá inicialmente el funcionamiento de los transistores de efecto de campo o FET (Field Effect Transistor). Posteriormente se tratarán los principios de diseño de las compuertas básicas de las familias MOS y CMOS, así como sus principales características.

#### III.1 GENERALIDADES DEL TRANSISTOR DE EFECTO DE CAMPO

El transistor de efecto de campo o FET, es un dispositivo semiconductor cuyo funcionamiento está basado en el control de la corriente que circula a través de él mediante un campo eléctrico.

Existen dos tipos principales de transistores de efecto de campo: el de juntura (JFET o JUNCTION FET) y el de compuerta aislada (IGFET o INSULATED GATE FET), más comúnmente conocido como FET de Semiconductor Metalizado Oxidado o MOSFET.

Las principales diferencias entre los transistores de efecto de cam po y los transistores bipolares de juntura son las siguientes:

- La operación de los transistores de efecto de campo depende únicamente del flujo de los portadores mayoritarios. Por lo tanto, es un dispositivo semiconductor unipolar (un solo tipo de portador).

- Resulta ser más sencilla su fabricación y ocupa menos espacio, como parte de un circuito integrado.

- 3. Muestra una impedancia de entrada muy alta, típicamente de varios megohms ( $M\Omega$ ).

- 4. Genera menos ruido y tiene una ganancia relativamente pequeña, con respecto al transistor bipolar de juntura. Esta última característica representa su principal desventaja.

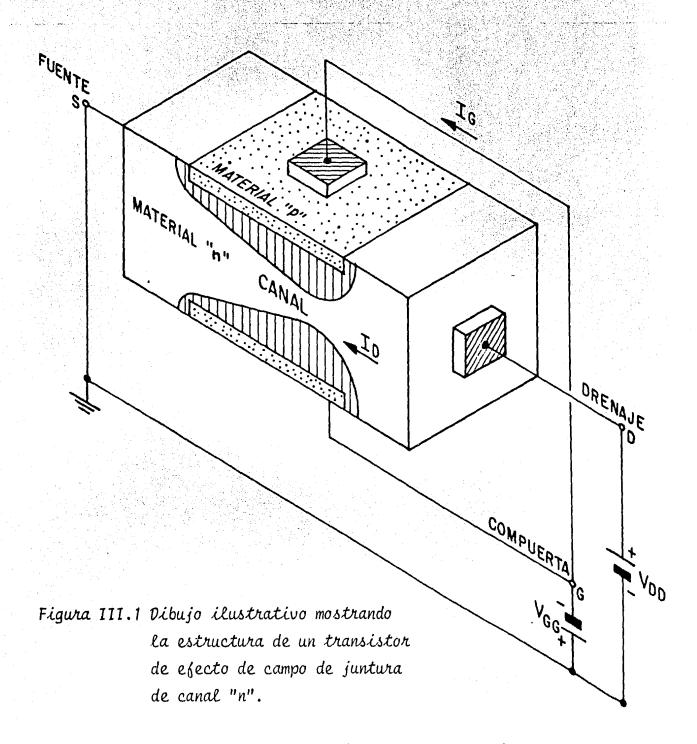

#### III.2 TRANSISTOR DE EFECTO DE CAMPO DE JUNTURA

La estructura teórica de un transistor de efecto de campo de juntura de canal "n" (material semiconductor con exceso de elctrones libres), está mostrada en la figura III.1.

Con base en este dispositivo electrónico, se explicará el principio de funcionamiento y las características de mayor trascendencia de este tipo de transistores.

En los extremos de una barra semiconductora de material "n" se fabrican contactos eléctricos. Debido a la diferencia de potencial provocada por una fuente de voltaje conectada a dichos extremos, se causa un flujo de corriente a través de la barra. Esta corriente consiste en porta dores mayoritarios que en el caso de un FET de juntura de canal "n" son electrones.

Las partes principales y los símbolos convencionales estandarizados de los transistores de efecto de campo de juntura, son las siguientes:

- FUENTE "S" (Source), es la terminal a través de la cual, los por tadores mayoritarios entran a la barra. La corriente convencional que entra a la barra por la fuente se simboliza con I.

- 2. DRENAJE "D" (Drain), es la terminal por la que los portadores ma yoritarios salen de la barra semiconductora. La corriente convencional que entra a la barra por el drenaje es designada con I<sub>D</sub>. Al voltaje entre el drenaje y la fuente se le denomina V<sub>DS</sub> y es positiva si el drenaje es más positivo que la fuente. En la figura III.1 V<sub>DS</sub> = V<sub>DD</sub>, donde V<sub>DD</sub> es el voltaje de alimentación del drenaje.

- 3. COMPUERTA "G" (Gate). Sobre ambos lados de la barra semiconducto ra de material "n", se crean regiones de alta concentración de impurezas receptoras ("p+") mediante aleación, difusión o, por cualquier otro método para la formación de junturas "p-n". Estas regiones de material "p" se les llama COMPUERTA ("G"). Entre la compuerta y la fuente está aplicado un voltaje V<sub>GS</sub> = -V<sub>GG</sub>, de tal manera de polarizar inversamente la juntura "p-n". La corriente convencional que entra a la barra en G se le denomina I<sub>G</sub>.

- 4. CANAL (Channel), es la región comprendida entre las terminales de la compuerta a través de la cual, los portadores mayoritarios fluyen desde la fuente hacia el drenaje.

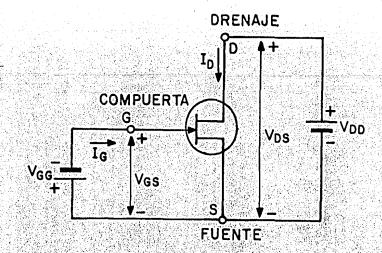

El símbolo gráfico y las polaridades convencionales de un transistor de efecto de campo de juntura con los voltajes de polarización correspondientes, está mostrado en la figura III.2.

El sentido de la cabeza de flecha de la compuerta indica la dirección en que circularía la corriente de compuerta  $\mathbf{I}_{G}$ , cuando la juntura correspondiente estuviera polarizado directamente.

Figura 111.2 Símbolo electrónico de un FET de juntura de canal "n".

La operación de los transistores de efecto de campo de juntura es como sigue: en ambos lados de la juntura "p-n" polarizado inversamente, se forman regiones de carga espaciales. Los portadores de corriente son transferidos de un lado de la juntura al otro, permaneciendo solamente iones positivos en el lado "n" e iones negativos en el lado "p". De esta manera se originan líneas de intensidad de campo eléctrico que van desde los iones positivos hacia los negativos y crean la caída de voltaje a través de la juntura.

Mientras mayor sea la polarización inversa, aumentará proporcionalmente el tamaño de la región de cargas inmóviles. Como la conductividad

de esta región es nominalmente nula debido a la inexistencia de portadores de corriente, la anchura efectiva de operación del canal disminuye

progresivamente con el incremento de la polarización inversa.

De todo ésto se concluye que con un voltaje de drenaje a fuente fijo, la corriente de drenaje  $\mathbf{I}_{\mathrm{D}}$  será una función del voltaje de polarización inversa a través de la juntura de la compuerta.

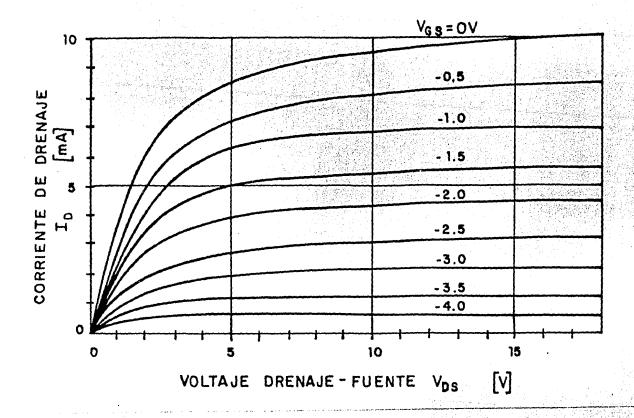

Una gráfica de la corriente de drenaje  $I_D$  en función del voltaje drenaje-fuente  $V_{DS}$ , con el voltaje compuerta-fuente  $V_{GS}$ , como parámetro de un circuito de fuente común, está mostrada en la figura III.3.

Para comprender cualitativamente las características por las que la gráfica adquiere la forma mostrada, considérese el caso en que  $V_{\rm GS}$  = 0 V. Si la corriente  $I_{\rm D}$  = 0 mA, el canal entre las terminales de la compuerta estará completamente abierto.

Figura III.3 Gráfica de corriente de drenaje  $I_{\mathcal{D}}$  contra voltaje drenaje-fuente  $V_{\mathcal{DS}}$ , con el voltaje compuerta-fuente  $V_{\mathcal{GS}}$ , como parámetro de un transitor de efecto de campo de juntura de canal "n".

Para valores pequeños de voltaje  $V_{\rm DS}$  aplicado al FET, la barra semi conductora actúa como una simple resistencia, por lo que la corriente  $I_{\rm D}$  crece proporcionalmente con  $V_{\rm DS}$ .

Pero al incrementarse aún más la corriente  $I_D$ , debido a la caída de potencial producida a lo largo de la barra, hace que la juntura con la compuerta se polarice inversamente, sobre todo en las regiones más cercanas al drenaje. Esta es la causa por la que el canal se empieza a "cerrar", hasta llegar a un valor de voltaje  $V_D$  de "contracción" del canal denominado  $V_D$  (Pinch-off voltage), para el cual la corriente  $I_D$  permanece prácticamente constante con respecto a un incremento mayor de  $V_D$ , ya que en principio, el canal no puede cerrarse completamente.

Ahora, si el voltaje V es aplicado de manera de proporcionar una polarización inversa mayor, el voltaje de "contracción" del canal  ${\rm V_p}$  ocurrirá para valores menores de  ${\rm V_{DS}}$ , por lo que la corriente máxima  ${\rm I_D}$  también resultará ser meñor.

# NSISTOR DE EFECTO DE CAMPO DE SEMICONDUCTOR 'ALIZADO OXIDADO (MOSFET)

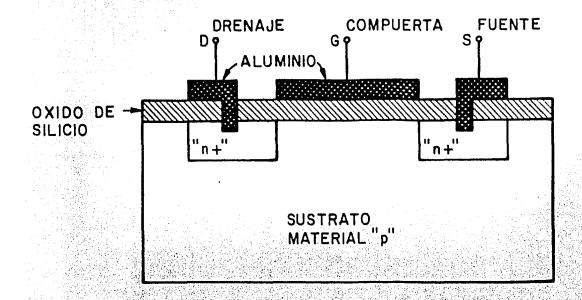

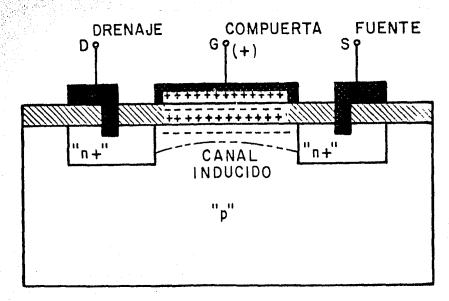

Este tipo de transistor de efecto de campo tiene una importancia comercial mayor con respecto al FET de juntura. A este transistor de efecto de campo de semiconductor metalizado oxidado se le denomina comúnmente como MOS. En la figura III.4 se muestra la estructura teórica de un transistor MOS.

El MOS de canal "n" consiste en un sustrato de baja densidad de por tadores, dentro del cual se difunden dos regiones de alta concentración de material "p". Estas regiones "p" tienen una separación entre ellas de 10 a 20 µm y hacen las funciones del drenaje y de la fuente.

Una delgada capa (0.1 a 0.2  $\mu$ m) de óxido de silicio (Si0<sub>2</sub>) aislante es fabricada sobre la estructura y a través de huecos practicados en ellas, se realizan contactos eléctricos metalizados con el drenaje y con la fuente.

Sobre la zona intermedia entre estas dos últimas partes se forma un área metalizado que tendrá la función de la compuerta. La región debajo de la compuerta, entre el drenaje y la fuente será entonces el canal. El metal utilizado en la fabricación del MOS es generalmente alumnio (Al).

El área que ocupa en el bloque semiconductor de un circuito integra do es de 3,200 µm² (o sea que pueden incluirse 300 transistores MOS en 1 mm²) o menor, el cual es aproximadamente el 5% del área que requiere un transistor bipolar de juntura para su fabricación.

La capa de óxido de silicio aislante entre la compuerta y el resto del MOS es la razón por la que este dispositivo también se le denomina FET de compuerta aislada. Así también, ésta es la causa principal por la que la resistencia de entrada del MOS sea muy alta, del orden de  $10^{10}\ \Omega$ .

Existen dos tipos diferentes de MOS llamados de "adición" (Enhancement) y de "sustracción" (Depletion). La figura III.4 corresponde a un MOS del primer tipo. La principal diferencia que existe entre ellos es que en la fabricación del MOS del tipo "sustracción", el canal se fabrica con material del mismo tipo que el drenaje y la fuente, pero de baja densidad de portadores. Debido a ello, este tipo de MOS es capaz de conducir

# III.3 TRANSISTOR DE EFECTO DE CAMPO DE SEMICONDUCTOR METALIZADO OXIDADO (MOSFET)

Este tipo de transistor de efecto de campo tiene una importancia comercial mayor con respecto al FET de juntura. A este transistor de efecto de campo de semiconductor metalizado oxidado se le denomina comúnmente como MOS. En la figura III.4 se muestra la estructura teórica de un transistor MOS.

El MOS de canal "n" consiste en un sustrato de baja densidad de por tadores, dentro del cual se difunden dos regiones de alta concentración de material "p". Estas regiones "p" tienen una separación entre ellas de 10 a 20 µm y hacen las funciones del drenaje y de la fuente.

Una delgada capa (0.1 a 0.2  $\mu$ m) de óxido de silicio (SiO<sub>2</sub>) aislante es fabricada sobre la estructura y a través de huecos practicados en ellas, se realizan contactos eléctricos metalizados con el drenaje y con la fuente.

Sobre la zona intermedia entre estas dos últimas partes se forma un área metalizado que tendrá la función de la compuerta. La región debajo de la compuerta, entre el drenaje y la fuente será entonces el canal. El metal utilizado en la fabricación del MOS es generalmente alumnio (Al).

El área que ocupa en el bloque semiconductor de un circuito integra do es de 3,200  $\mu\text{m}^2$  (o sea que pueden incluirse 300 transistores MOS en 1 mm²) o menor, el cual es aproximadamente el 5% del área que requiere un transistor bipolar de juntura para su fabricación.

La capa de óxido de silicio aislante entre la compuerta y el resto del MOS es la razón por la que este dispositivo también se le denomina FET de compuerta aislada. Así también, ésta es la causa principal por la que la resistencia de entrada del MOS sea muy alta, del orden de  $10^{10}\ \Omega$ .

Existen dos tipos diferentes de MOS llamados de "adición" (Enhancement) y de "sustracción" (Depletion). La figura III.4 corresponde a un MOS del primer tipo. La principal diferencia que existe entre ellos es que en la fabricación del MOS del tipo "sustracción", el canal se fabrica con material del mismo tipo que el drenaje y la fuente, pero de baja densidad de portadores. Debido a ello, este tipo de MOS es capaz de conducir

Figura III.4 Estructura teórica de un transistor de efecto de campo MOS de canal "n", de tipo "adición" (enhancemente).

una pequeña corriente entre el drenaje y la fuente en ausencia de un voltaje aplicado a la compuerta; en cambio el MOS de tipo "adición" requiere de la aplicación de un voltaje en la compuerta para que circule corriente por el canal.

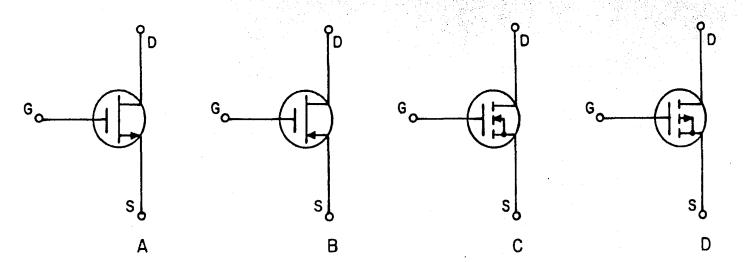

Los símbolos gráficos de los diversos tipos de MOS, están dibujados en la figura III.5.

Figura III.5 Símbolos gráficos de los diferentes tipos de transis tores MOS. Las figuras A y B pueden representar MOS de tipos "adición" o "sustracción". Las figuras C y D representan específicamente MOS de tipo "adición". A y C son de canal "n"; B y D son de canal "p".

Obsérvese que las figuras C y D tienen cuatro terminales. La terminal intermedia del lado derecho representa al sustrato, el cual está internamente conectado con la fuente.

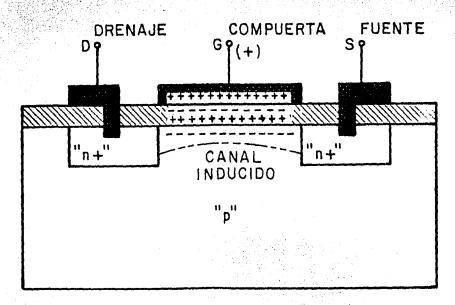

El funcionamiento de un MOS de tipo "adición" está basado en la formación inducida de un canal de conducción debajo de la compuerta.

Considerando un MOS de canal "n" tipo "adición", si se aplica un potencial positivo a la compuerta, se crea un campo eléctrico a través del óxico, que inducirá cargas negativas en la región de semiconductores debajo de la compuerta (Figura III.6).

Figura III.6 Estructura de un transistor MOS de canal "n" de tipo de "adición" donde se muestra la creación de un canal inducido por el campo eléctrico generado por el poten cial positivo en la compuerta.

Estas cargas negativas serán portadores minoritarios en el sustrato de material "p". Al aumentar el voltaje en la terminal de la compuerta, se incrementa el número de portadores minoritarios en el canal induci

do, por lo que la conductividad crece, permitiendo la circulación de corriente a través de este canal, del drenaje a la fuente.

La corriente de drenaje es inyectada o "añadida" por el voltaje positivo en la compuerta, al canal inducido y de ahí a la fuente. Este mecanismo es la razón por la cuál este tipo de dispositivo recibe el nombre de MOS de "adición".

Existe un voltaje mínimo V<sub>GS</sub> a partir del cuál comienza a circular una cantidad sifnificativa de cor 'el drenaje a la fuente. A partir

Obsérvese que las figuras C y D tienen cuatro terminales. La terminal intermedia del lado derecho representa al sustrato, el cual está internamente conectado con la fuente.

El funcionamiento de un MOS de tipo "adición" está basado en la formación inducida de un canal de conducción debajo de la compuerta.

Considerando un MOS de canal "n" tipo "adición", si se aplica un potencial positivo a la compuerta, se crea un campo eléctrico a través del óxico, que inducirá cargas negativas en la región de semiconductores debajo de la compuerta (Figura III.6).

Figura III.6 Estructura de un transistor MOS de canal "n" de tipo de "adición" donde se muestra la creación de un canal inducido por el campo eléctrico generado por el potencial positivo en la compuerta.

Estas cargas negativas serán portadores minoritarios en el sustrato de material "p". Al aumentar el voltaje en la terminal de la compuerta, se incrementa el número de portadores minoritarios en el canal inducido, por lo que la conductividad crece, permitiendo la circulación de corriente a través de este canal, del drenaje a la fuente.

La corriente de drenaje es inyectada o "añadida" por el voltaje positivo en la compuerta, al canal inducido y de ahí a la fuente. Este mecanismo es la razón por la cuál este tipo de dispositivo recibe el nombre de MOS de "adición".

Existe un voltaje mínimo  $V_{\overline{GS}}$  a partir del cuál comienza a circular una cantidad sifnificativa de corriente del drenaje a la fuente. A partir

de este voltaje, se considera que el canal se ha formado. Recibe el nombre de voltaje de "encendido" o  $V_{\mathrm{TH}}$  (threshold voltage).

El valor del voltaje de "encendido" depende de las propiedades electricas del sustrato y del óxico, así como del grosor de éste último. Los valores típicos de  $V_{\mathrm{TH}}$  van de 2 a 4V.

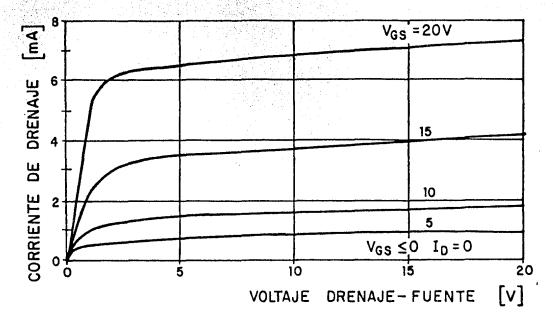

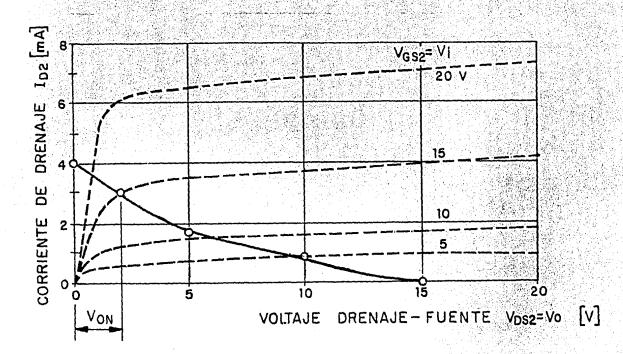

La gráfica de corriente de drenaje  $I_D$  contra voltaje drenaje-fuente  $V_{DS}$  con el volteje compuerta-fuente  $V_{GS}$  como parámetro, de un transistor MOS de canal "n" tipo "adición" está mostrada en la figura III.7.

Figura III.7 Gráfica de corriente de drenaje  $I_{\rm D}$  contra voltaje drenaje-fuente  $V_{\rm DS}$ , con el voltaje compuerta-fuente  $V_{\rm GS}$ , como parámetro de un transistor MOS de canal "n" de tipo "adición".

El MOS tipo "sustracción" tiene un funcionamiento dual. Al aplicarse un potencial negativo en la compuerta, en el canal de material "n" se crea un campo eléctrico similar al explicado para el FET de juntura, por lo que funciona de una manera parecida a éste.

Si el potencial aplicado en la compuerta es positivo, su funcionamiento será similar al MOS de tipo "adición".

#### III.4 LOGICA MOS

Conocidos los fundamentos básicos bajo los cuales funcionan los transistores de efecto de campo MOS, se podrá comprender adecuadamente la operación de los circuitos digitales diseñados con estos dispositivos.

Para la fabricación de compuertas de esta familia lógica, se utilizan preferentemente transistores MOS tipo "adición" por la característica de que requieren de la aplicación de un voltaje en la compuerta del MOS para que circule corriente por el canal.

Debido a las capacitancias parásitas compuerta-drenaje, compuertafuente y compuerta-sustrato, los circuitos MOS son relativamente más lentos que los circuitos diseñados con transistores bipolares de juntura.

Pero su baja potencia de disipación y su alta densidad de fabricación en circuitos integrados, hacen a esta familia MOS sumamente atractiva, sobre todo para aplicaciones de baja velocidad.

El valor típico de tiempo de demora de propagación de esta familia lógica es del orden de 300 ns. Se considera que el abanico de salida que puede manejar es de 20 compuertas.

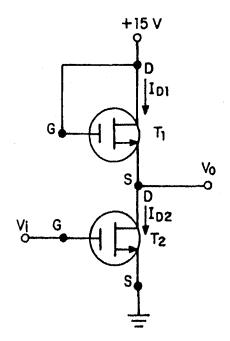

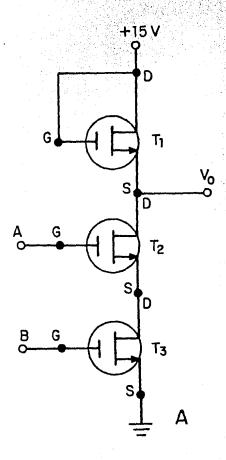

Figura III.8 Circuito inversor MOS.

Está formado únicamente por dos transistores MOS canal "n" de tipo "adición".

Se muestra en la figura III.8 un circuito inversor MOS. Como se puede observar, consiste únicamente de dos transistores MOS interconecta dos entre sí, sin necesidad de resistencias u otros elementos similares.

El transistor superior  $\mathbf{T}_1$ , funciona exclusivamente como una resistencia de carga. El transistor  $\mathbf{T}_2$ , es el elemento activo de la compuerta lógica.

Para comprender el funcionamiento de este circuito, se requiere establecer las siguientes ecuaciones:

$$V_{i} = V_{GS2}$$

;  $V_{o} = V_{DS2}$ ;  $V_{D} = V_{DS1} + V_{o}$ ;  $I_{DS1} = I_{DS2}$

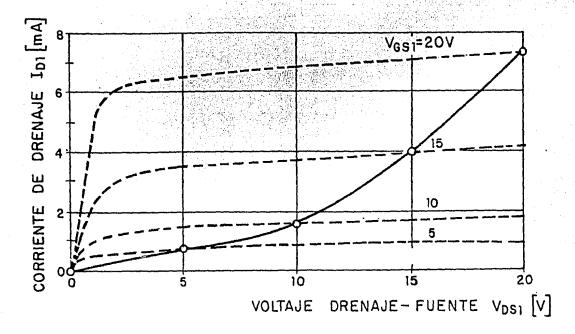

Como el transistor  $T_1$  tiene voltajes compuerta-fuente  $V_{\rm GS1}$  y drenaje fuente  $V_{\rm DS1}$  iguales, el lugar geométrico de los puntos que cumplen con esta condición en la gráfica de corriente de drenaje  $I_{\rm D1}$  contra voltaje drenaje-fuente  $V_{\rm DS1}$  con el voltaje  $V_{\rm GS1}$  como parámetro, se muestra en la figura III.9.

Figura III.9 Gráfica del lugar geométrico donde  $V_{DS1} = V_{GS1}$  del transistor MOS canal "n" tipo "adición".

Este lugar geométrico será la curva de transferencia de corriente de drenaje  $I_{D1}$  contra voltaje  $V_{DS1}$ . Obsérvese que para una  $I_{D1}$  = 0 mA, el voltaje  $V_{DS1}$  es igual a cero.

Conocida esta curva de transferencia, se podrá dibujar la gráfica de corriente de drenaje del transistor  $\mathbf{T}_2$  ( $\mathbf{I}_{D2}$ ) contra voltaje de salida  $\mathbf{V}_0$ , conociendo las ecuaciones:

$$I_{D1} = I_{D2}$$

;  $V_{o} = V_{DD} - V_{DS1}$

La gráfica de transferencia I contra V está mostrada en la figura III.10.

Figura III.10 Gráfica de transferencia de corriente de drenaje  $I_{D2}$  contra voltaje de salida  $V_o$  =  $V_{DS2}$ , con el voltaje de entrada  $V_i$  =  $V_{CS2}$  como parámetro y el voltaje de alimentación  $V_{DD}$  = 15 V.

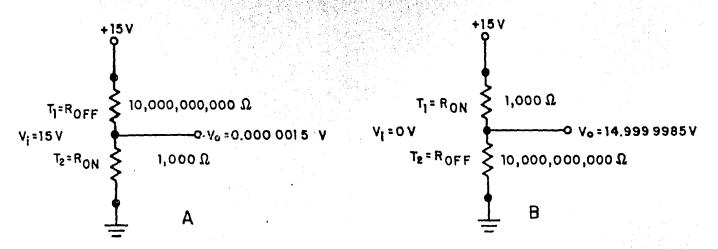

Entonces se puede deducir que si el voltaje de entrada  $V_i$  = 0 V, el voltaje de salida tendrá un valor  $V_O$  =  $V_{DD}$ . Como este voltaje de alimentación  $V_{DD}$  = 15 V,  $V_O$  = 15 V.

Se puede mantener esta misma condición mientras el transistor  $T_2$  permanezca apagado. Considerando un voltaje de encendido  $V_{\mathrm{TH}}=2$  V, se puede inferir un voltaje similar como valor del margen de ruido.

Ahora, si la entrada es alta o sea  $V_i$  = 15  $V_{GS2}$  = 15  $V_{OS2}$ , la salida será baja, con un valor de  $V_i$  = 2  $V_i$ , como se puede apreciar en la gráfica de la figura III.10.

Entonces se puede concluir que el circuito en estudio corresponde a una compuerta NOT o inversor.

A continuación se procederá a calcular la potencia disipada. Cuando  $V_i = 0$  V, la corriente  $I_{D1} = I_{D2}$  es prácticamente nula. En realidad exis-

te un valor sumamente pequeño, si se considera que la resistencia de "apa gado" del MOS es del orden de R  $_{\rm OFF}$  = 10  $^{10}$   $\Omega$  .

Como en este caso  $V_0 = 15 V_1$

$$I_{D} = \frac{V_{O}}{R_{OFF}}$$

;  $I_{D} = \frac{15}{10^{10}}$ ;  $I_{D} = 1.5 \times 10^{-9}$  A;  $I_{D} = 1.5 \text{ nA}$

por lo tanto:

$$P_{D} = V_{DD}I_{D}$$

:  $P_{D} = 15 \times 1.5$ ;  $P_{D} = 22.5$  nW

En este estado la impedancia de salida es alta teniendo aproximadamente el valor de la resistencia drenaje-fuente de  $T_1$ :

Ahora cuando  $V_i = V_{DD}$  y  $V_o = 2$  V, de la figura III.10 se obtiene un valor de  $I_{D2} = 3$  mA. Entonces:

$$P_{D} = V_{DD}I_{D}$$

;  $P_{D} = 15 \times 3$ ;  $P_{D} = 45 \text{ mW}$

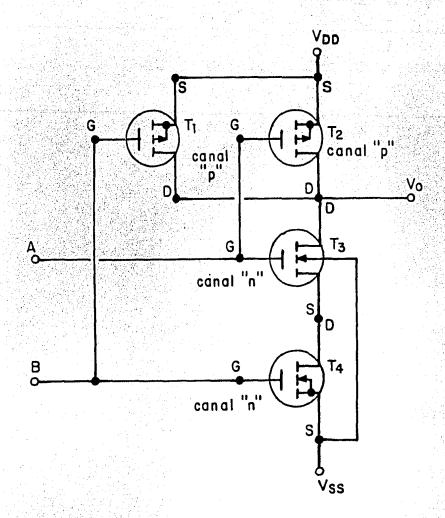

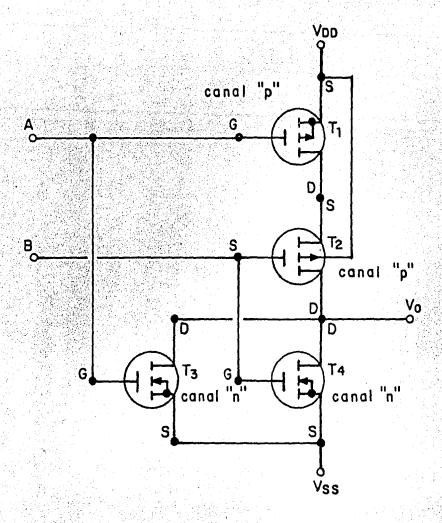

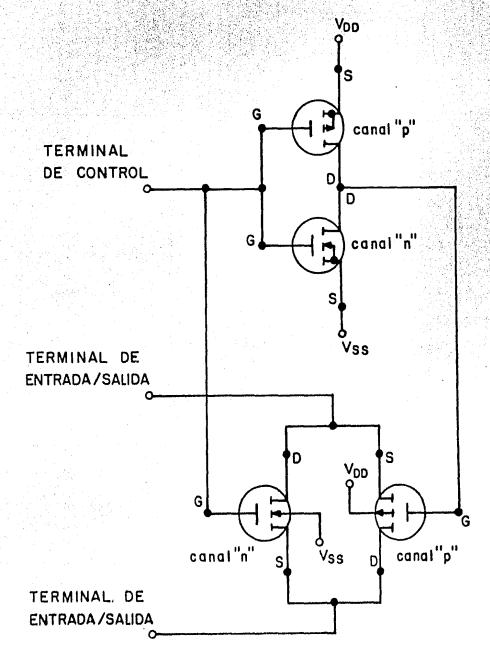

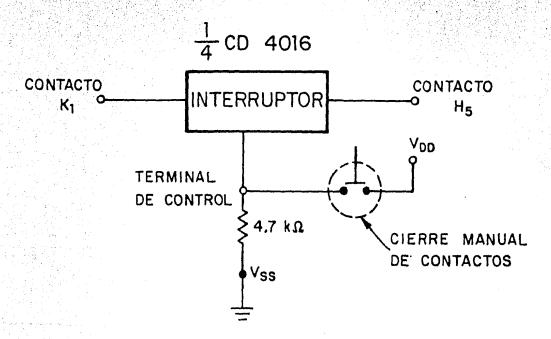

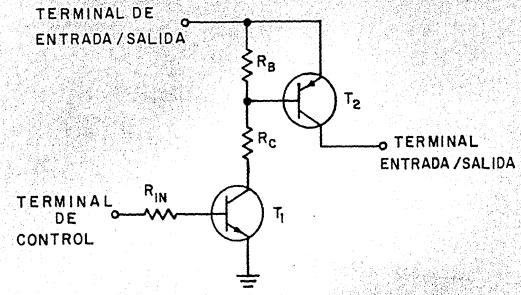

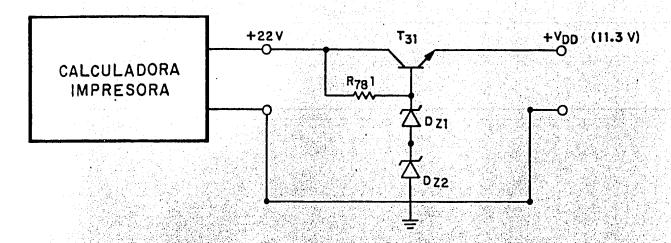

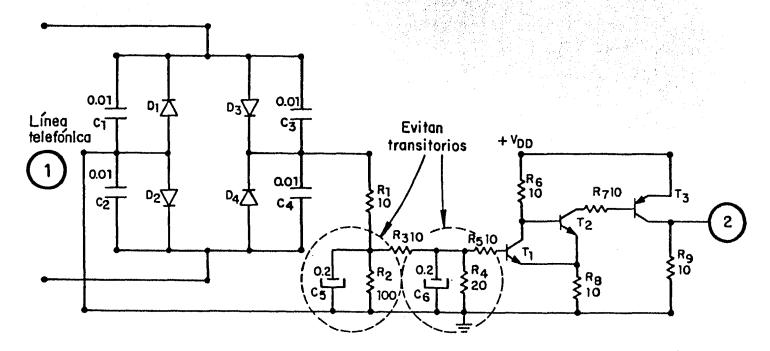

La impedancia de salida tendrá un valor aproximado igual al de la resistencia que presenta el transistor  $\mathbf{T}_2$  "encendido", que es de unos 600  $\Omega$ .