# UNIVERSIDAD NACIONAL AUTONOMA DE MEXICO

FACULTAD DE INGENIERIA

## DISEÑO Y CONSTRUCCION DE UN EGUALIZADOR GRAFICO CONTROLADO DIGITALMENTE

TESIS

QUE PARA OBTENER EL TITULO DE: INGENIERO MECANICO ELECTRICISTA

PRESENTAN:

Boris Escalante Ramírez

Pedro Méndez Colina

Carlos Octavio Vazquez Pérez

DIRECTOR DEL SEMINARIO: ING. ANTONIO SALVA CALLEJA

MEXICO, D. F.

## UNAM – Dirección General de Bibliotecas Tesis Digitales Restricciones de uso

## DERECHOS RESERVADOS © PROHIBIDA SU REPRODUCCIÓN TOTAL O PARCIAL

Todo el material contenido en esta tesis está protegido por la Ley Federal del Derecho de Autor (LFDA) de los Estados Unidos Mexicanos (México).

El uso de imágenes, fragmentos de videos, y demás material que sea objeto de protección de los derechos de autor, será exclusivamente para fines educativos e informativos y deberá citar la fuente donde la obtuvo mencionando el autor o autores. Cualquier uso distinto como el lucro, reproducción, edición o modificación, será perseguido y sancionado por el respectivo titular de los Derechos de Autor.

### INDICE

### INTRODUCCION

|            | •                                                 |    |

|------------|---------------------------------------------------|----|

| CAPITULO 1 | SELECCION DE LA CONFIGURACION DE LA BANDA BASICA  |    |

|            | DEL ECUALIZADOR.                                  | 1  |

|            |                                                   | ٠. |

|            | 1.1 CONFIGURACION CON UN SOLO AMPLIFICADOR        |    |

|            | OPERACIONAL.                                      | 1  |

|            | 1.2 CONFIGURACION CON UN GIRADOR.                 | 9  |

|            | 1.3 ECUALIZADOR PARAMETRICO.                      | 16 |

|            | 1.4 ECUALIZADOR CON ALIMENTACION HACIA ADELANTE Y |    |

|            | RETROALIMENTACION.                                | 20 |

|            |                                                   |    |

| CAPITULO 2 | DISEMO DE UN CAHAL DEL ECUALIZADOR.               | 32 |

|            | 2.1 IMPLEMENTACION DE LA BANDA BASICA.            | 32 |

|            | 2.2 CONJUNCION DE 10 BANDAS BASICAS DE UN CANAL.  | 37 |

|            | 2.3 SELECCION DE LOS PARAMETROS DE LA RED ACTIVA  |    |

|            | PARA LA BANDA BASICA.                             | 41 |

|            | 2.3.1 RELACION DE GANANCIAS.                      | 42 |

|            | 2.3.2 RELACION DE ANCHO DE BANDA.                 | 43 |

|            | 2.4 IMPLEMENTACION FINAL DE UN CANAL DEL          |    |

|            | ECUALIZADOR.                                      | 53 |

|             | BASICA.                                           | 60  |

|-------------|---------------------------------------------------|-----|

| •           |                                                   | 50  |

|             |                                                   |     |

| ,           |                                                   |     |

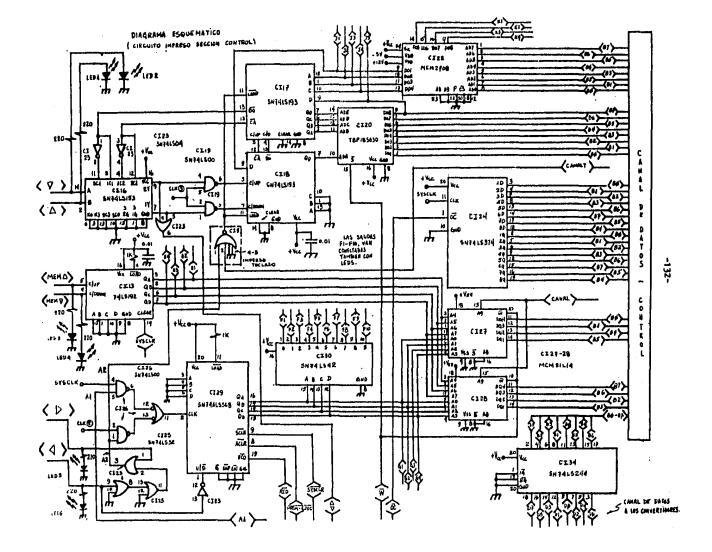

| CAPITULO 4  | CONTROL DIGITAL DEL ECUALIZADOR.                  | 65  |

|             |                                                   | :   |

|             | 4.1 BLOQUE DE CONVERTIDORES DIGITALES-ANALOGICOS. | 67  |

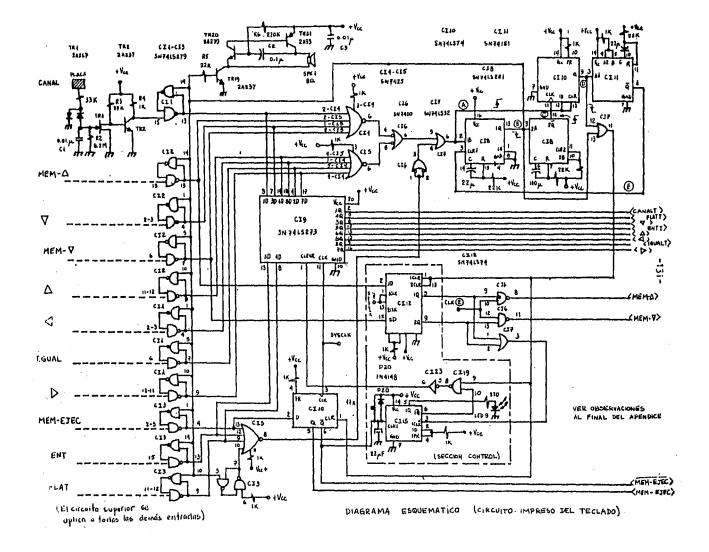

|             | 4.2 BLOQUE TECLADO.                               | 74  |

|             | 4.3 BLOQUE SELECCION DE BANDA.                    | 92  |

|             | 4.4 BLOQUE CONTROL DE GANANCIA.                   | 95  |

|             | 4.5 BLOQUE DE MEMORIA.                            | 105 |

|             | 4.6 BLOQUE DE REGISTRO TEMPORAL.                  | 108 |

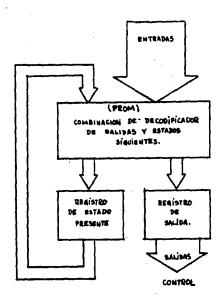

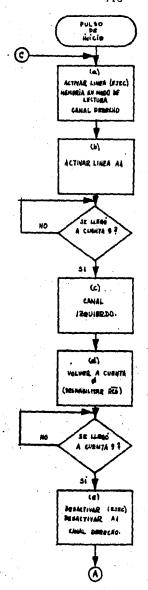

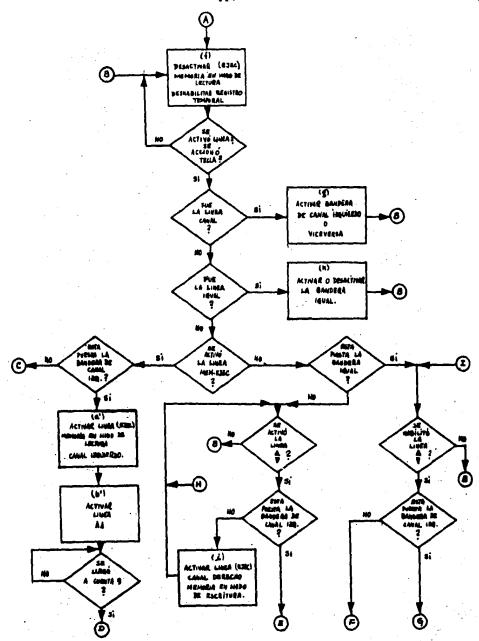

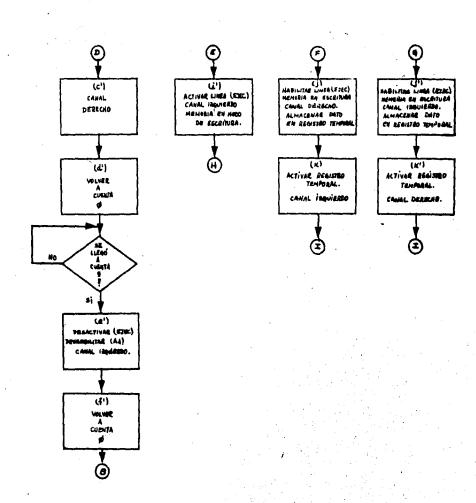

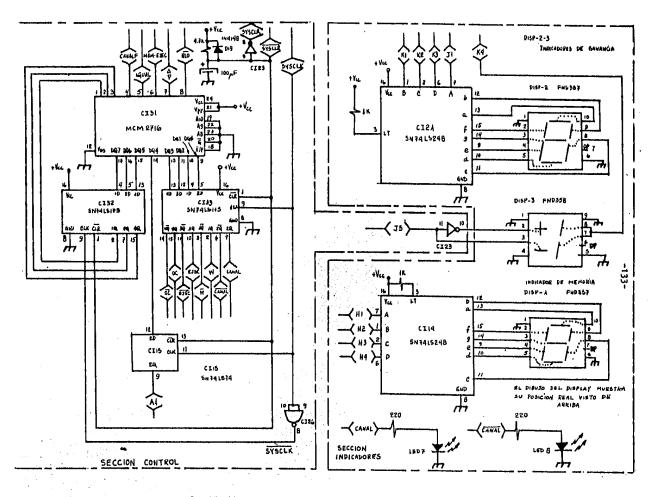

|             | 4.7 BLOQUE SECUENCIADOR.                          | 109 |

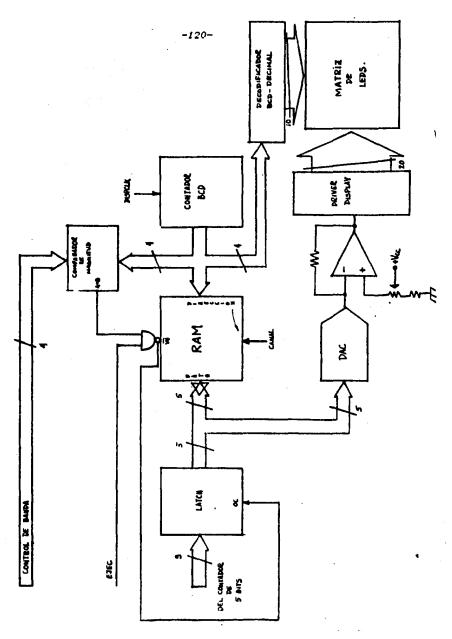

|             | 4.8 BLOQUE DE INDICADOR GRAFICO.                  | 119 |

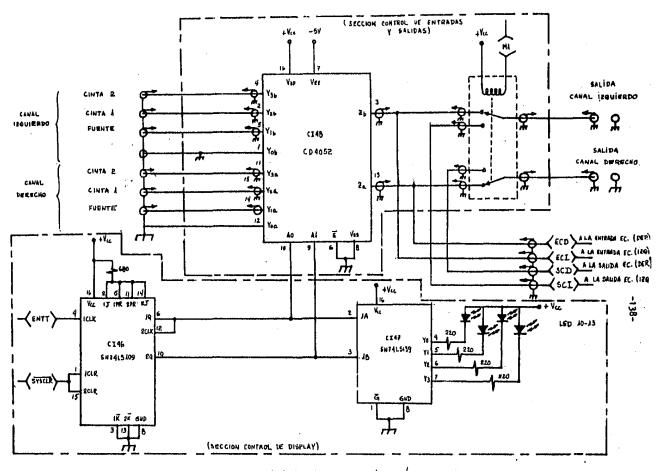

|             | 4.9 BLOQUE DE SELECCION ENTRADAS Y SALIDAS.       | 123 |

|             | 4.10 CIRCUITOS AUXILIARES.                        | 123 |

|             |                                                   |     |

|             |                                                   |     |

| CAPITULO 5  | NUEVAS TECNOLOGIAS EN EL DISENO DE ECUALIZADORES  |     |

| •           | CONTROLADOS DIGITALMENTE.                         | 126 |

|             |                                                   |     |

| CONCLUSIONE | s.                                                | 128 |

|             |                                                   |     |

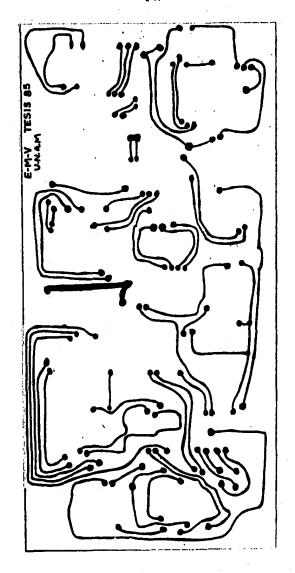

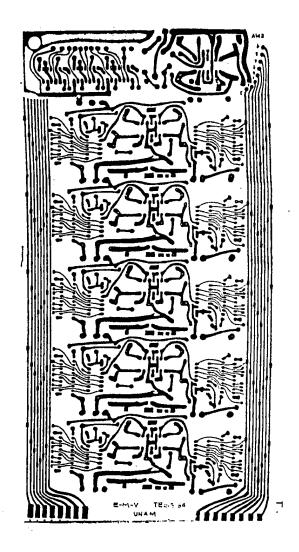

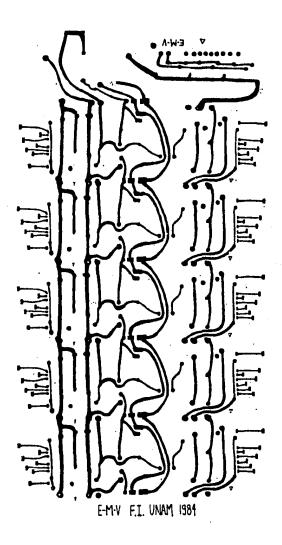

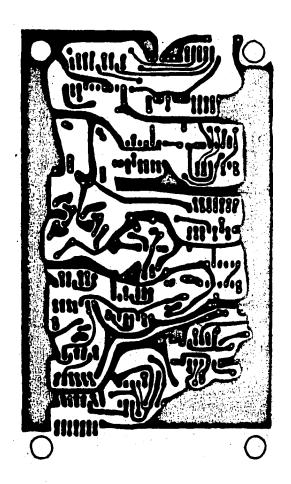

| APENDICE A  | DIAGRAHAS ESQUENATICOS.                           | 130 |

|             |                                                   |     |

| APENDICE B  | LISTA DE PARTES.                                  | 141 |

|             |                                                   |     |

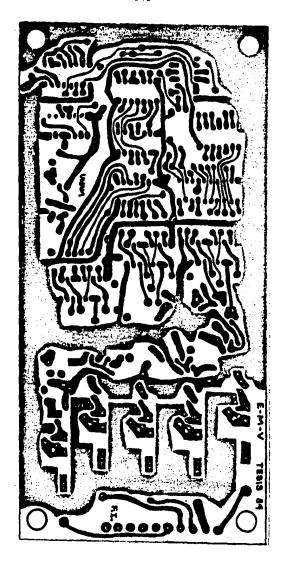

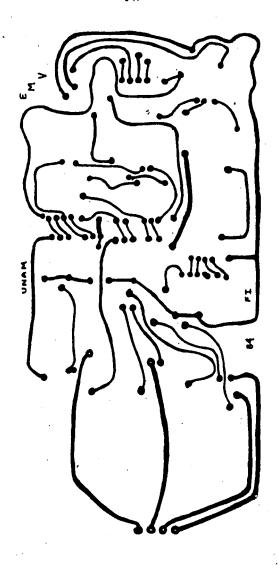

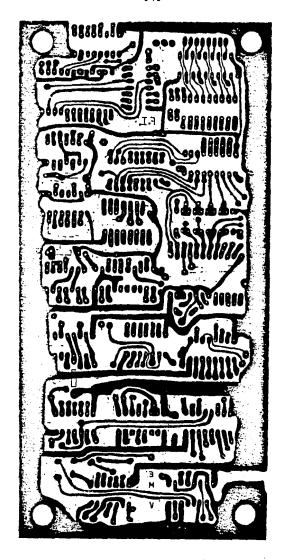

| 405UD 105 0 | CIRCUITOS IMPRESOS.                               | 145 |

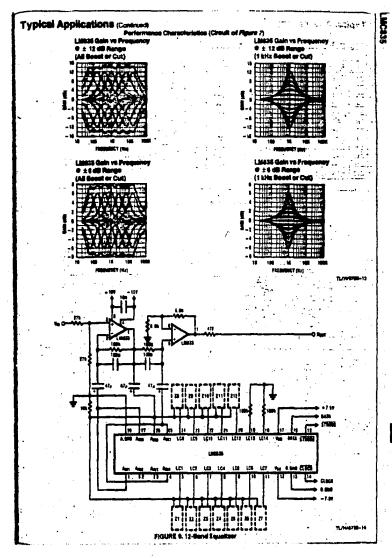

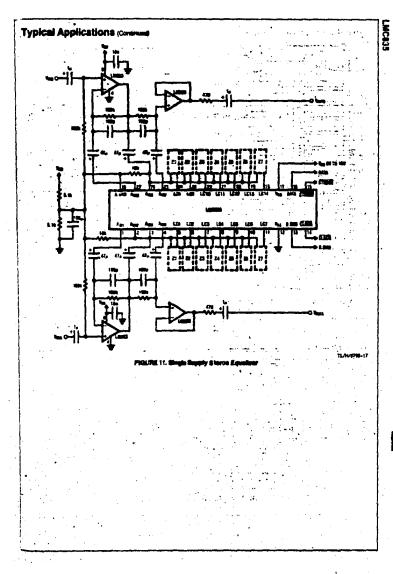

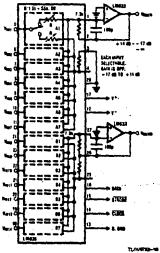

| APENDICE D | ESPECIFICACIONES | DEL LMC835 |

|------------|------------------|------------|

|------------|------------------|------------|

BIBLIOGRAFIA.

#### INTRODUCCION.

Un ecualizador gráfico recibe este nombre porque la posición de los controles deslizantes reproduce gráficamente la modificación de la respuesta en frecuencia. En nuestro caso, los controles deslizantes para cada banda no existen, pero a cambio, un desplegado indica gráficamente la ganancia de cada banda.

Un punto importante en el diseño de un ecualizador, es el número de bandas en las que se va a dividir la gama de frecuencias audibles. El ecualizador ideal tendría un número infinito de bandas para poder tener un control total de cada frecuenci audible. Obviamente, se debe escoger un número limitado de bandas, tal que no sea tan pequeño que no permita tener un control amplio sobre la gama de frecuencias audibles, ni tan grande que no exista una diferencia notable entre la variacion de ganancia de dos frecuencias adyacentes.

Tomando como modelo los ecualizadores comercíales, se decidió diseñar un ecualizador de 10 bandas por canal separadas una octava entre si, empezando con 31.25 Hz para la frecuencia central de la primera banda y terminando con 16 KHz para la última banda.

Al divisir la gama de frecuencias audibles en 10 intervalos de frecuencia, el caso ideal serla que la variación de ganancia de todas las fecuencias comprendidas en cada intervalo fuera la misma, lo cual implica que los filtros usados para la configuración de las bandas tuvieran una respuesta plana en las frecuencias pasantes y una pendiente infinita para la pérdida de ganancia en la frecuencia de

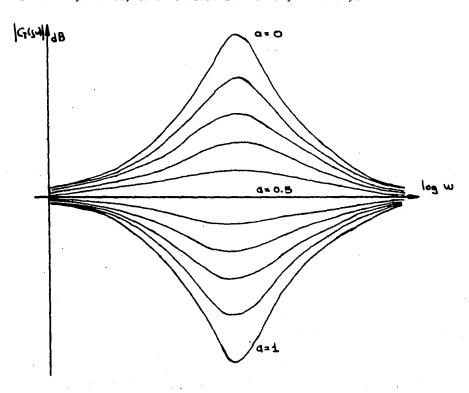

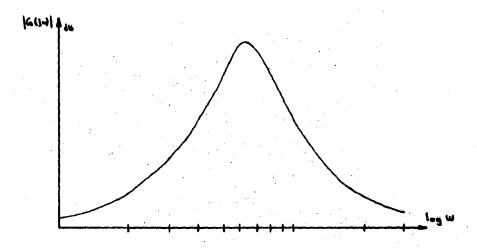

corte, lo cual es imposible. Con filtros de muy alto orden se puede aproximar este comportamiento, pero el beneficio que esto pueda producir no justifica el costo que implica la construcción de filtros de brden alto. Por lo anterior, las bandas de los ecualizadores tienen un comportamiento en magnitud, para distintos valores de ganancia, como se muestra en la siguiente figura.

MAGNITUD DE LA BANDA BASICA DE UN ECUALIZADOR PARA DISTINTAS CONDICIONES DE GANANCIA

Como se verà más adelante estas curvas corresponden a la funcion de transferencia F(S), la cual se presenta a continuación:

$$F(S) = \frac{1 + (1-a) H(S)}{1 + a H(S)}$$

en donde H(S) representa la función de transferencia de un filtro . pasobanda, y O(a(1.

Un ecualizador controlado digitalmente presenta varias ventajas con respecto a los ecualizadores convencionales. Una de ellas es que al tener la información de la ganancia o atenuación de cada banda en una palabra digital, es posible memorizar varias ecualizaciones que satisfagan ciertas necesidades, para posteriormente recuperarlas cuando se presente la ocasión. Otra de la ventajas de este tipo de control es la posibilidad de obtener gran resolución y buena presición en la variación de la ganancia de cada banda. Es decir, si se tiene la posibilidad de controlar toda la gama de ganancias de cada una de éstas, de +15 dB a -15 dB, mediante 8 bits, es factible tener cambios de ganancia tan pequeños como 0.12 dB.

Es importante hacer notar que el hecho de tener una o más palabras digitales que representan tanto la ganancia como la selección de bandas, hace factible llevar a cabo el control del ecualizador mediante un microprocesador, una microcomputadora o un circuito secuencial y combinacional, según lo requiera el grado deseado de versatilidad del ecualizador, y la finalidad del mismo.

El hecho de haber escogido el tema de ecualizadores controlados

digitalmente como tesis, implica que los conocimientos necesarios para desarrollarlo, abarcan las áreas de electronica analógica y digital que posibilitan plasmar de una manera tangible y práctica dichos conocimientos.

#### I SELECCION DE LA CONFIGURACION DE LA BANDA BASICA DEL ECUALIZADOR.

La selección de una adecuada configuración para las bandas del ecualizador implica, entre otras cosas, tomar en cuenta la manera de llevar a cabo el control digital. Así, algunas de las posibles configuraciones para tal efecto se muestran a continuación:

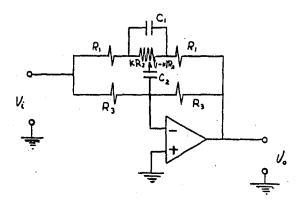

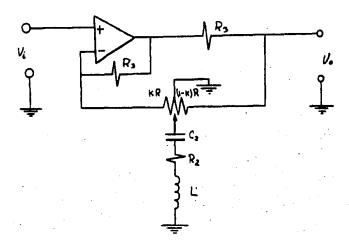

#### 1.1 CONFIGURACION CON UN SQLO AMPLIFICADOR OPERACIONAL.

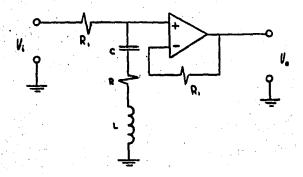

FIGURA 1.1 BANDA DE ECUALIZADOR CON UN SOLO AMP. OF.

La función de transferencia de este circuito se puede obtener de la siguiente forma

Se observa que el potenciometro  $R_2$  junto con el capacitor  $G_2$  forman un circuito delta, factible de transformarse en estrella, lo cual lleva a una simplificación de la red como lo muestra la figura 1.2

FIGURA 1.2 EQUIVALENTE DEL CIRCUITO DE LA FIGURA 1.1

en donde:

$$Z_{2} = R_{z} + \frac{(1 - K) R_{2}}{R_{2} C_{z} S + 1}$$

(1.2.

$$Z_{3} = \frac{1}{S} \frac{K (1 - K) R_{2} C_{4} S}{R_{2} C_{4} S}$$

(1.3)

Considerando las propiedades del amplificador operacional ideal, tales como ganancia infinita, impedancia de entrada infinita, impedancia de salida nula, podemos concluir que:

$$V_{a}/R_{a} + V_{a}/Z_{a} + V_{a}/R_{a} = 0$$

(1.4)

En la ecuación anterior se encuentra implicito el concepto de tierra virtual en la entrada no inversora del amplificador operacional debida a la ganancia infinita del amplificador, lo que provoca que con realimentación negativa se cumpla que:

$$Vb = Vc = 0 \tag{1.5}$$

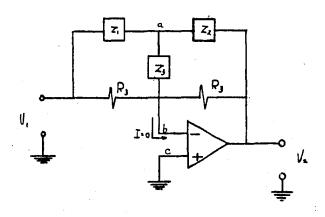

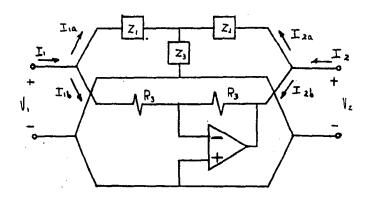

Como consecuencia de esta última aseveración, el circuito se puede plantear nuevamente como se muestra en la figura 1.3, en donde se ve claramente que se trata de dos bipuertos en paralelo, tales como los representados en la figura 1.4

FIGURA 1.3 ESQUENATIZACION DEL CIRCUITO DE LA FIGURA 1.1 COMO DOS BIPUERTOS EN PARALELO.

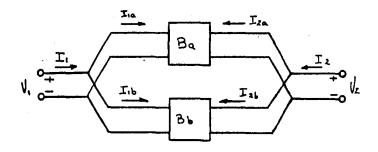

FIGURA 1.4 BIPUERTOS EN PARALELO.

Del circuito de la figura 1.3 se observa que:

$$I_{z}(S) = I_{z=}(S) \neq I_{z=}(S)$$

(1.6)

$$I_{2}(S) = I_{2n}(S) + I_{2n}(S)$$

(1.7)

Si optamos por modelar los bipuertos con parametros Y , se tiene que para el bipuerto A:

$$\begin{bmatrix} I_{x_{2}}(S) \\ I_{x_{2}}(S) \end{bmatrix} = \begin{bmatrix} Y_{xx}(S) & Y_{xx}(S) \\ Y_{xx}(S) & Y_{xx}(S) \end{bmatrix} \begin{bmatrix} V_{x}(S) \\ V_{x}(S) \end{bmatrix}$$

(1.8)

y para el bipuerto B

$$I_{Ab}(S) = V_A(S)/R_B \tag{1.9}$$

$$L(S) = V_2(S)/R_*$$

(1.10)

Sustituyendo las ecuaciones (1.8), (1.9) y (1.10) en las ecuaciones

(1.6) y (1.7), tenemos:

$$I_{a}(S) = Y_{aa}(S) V_{a}(S) + Y_{aa}(S) V_{a}(S) + (1/R_{a})V_{a}(S)$$

(1.11)

$$I_{2}(S) = Y_{22}(S) V_{2}(S) + Y_{22}(S) V_{2}(S) + (1/R_{3})V_{2}(S)$$

(1.12)

De la ecuación (1.4) se tiene que:

$$I_{x}(S) + I_{x}(S) = 0$$

(1.13)

De donde se obtiene:

$$V_{x}(S)$$

$Y_{xx}(S) + Y_{xx}(S) + 1/R_{x}$  (1.14)

$V_{x}(S)$   $Y_{xx}(S) + Y_{xx}(S) + 1/R_{x}$

Ecuación que en función de Zs, Zm, Zm queda como:

Sustituyendo los valores de Zz, Zz y Zz, quedas

$$\frac{V_{2}\left(4\right)}{V_{1}\left(5\right)} = \frac{C.C._{1}R_{1}R_{1}R_{2} + P_{2} + 2R_{2}K\left(1-K\right)\right)S^{2} + \left[2C._{1}R_{1}R_{2} + C._{2}R_{1}\left(R_{1}+R_{2}+R_{3}\right) + C._{2}R_{2}\left(1-K\right)\left(R_{1}K+R_{3}\right)\right]S + 2R_{1}+R_{2}}{C._{1}C._{1}R_{1}R_{1}+R_{3} + 2R_{2}K\left(1-K\right)\right]S^{2} + \left[2C._{1}R_{1}R_{2} + C._{2}R_{1}\left(R_{1}+R_{2}+R_{3}\right) + C._{2}R_{1}\left(R_{1}+R_{2}\right) + C._{3}R_{2}\left(R_{1}+R_{2}\right)\right)S + 2R_{1}+R_{2}}$$

(1.16)

Se puede corroborar el efecto ecualizador de la función de transferencia de la ecuación (1.16) tomando uno de los extremos del potenciómetro. Por ejemplo, si K = O (maxima ganancia)

$$\frac{V_{f}(s)}{V_{f}(s)} = \frac{C.C_{1}R_{1}R_{2}(n,+n_{2})S^{2} + [2CR_{1}R_{2} + C_{2}R_{1}(R_{1}+n_{2}+n_{3}) + C_{2}R_{2}R_{3}]S + 2R_{1} + R_{2}}{C.C_{2}R_{1}R_{2}(n,+n_{3})S^{2} + [2CR_{1}R_{2} + C_{2}R_{1}(R_{1}+R_{2}+n_{3})]S + 2R_{1} + R_{2}}$$

(1.17)

Si igualamos esta ecuación con la correspondiente a la curva de máxima ganancia del ecualizador:

$$\frac{V_{2}(S)}{V_{4}(S)} = 1 + H(S) \qquad (1.18)$$

$$donde \qquad H(S) = \frac{Ho \propto Ho S}{S^{2} + \alpha Mo S + Ho^{2}} \qquad (1.19)$$

$$por tanto \qquad \frac{V_{2}(S)}{V_{4}(S)} = \frac{S^{2} + (1 + Ho) \propto Ho S + Ho^{2}}{S^{2} + \alpha Ho S + Ho^{2}} \qquad (1.20)$$

$$de donde \qquad Ho = \begin{bmatrix} 2R_{1} + R_{2} \\ C_{2} C_{2} R_{1} R_{2} & (R_{1} + R_{3}) \end{bmatrix} \qquad (1.21)$$

$$\alpha = \frac{2C_{1} R_{2} R_{2} + C_{2} R_{1} (R_{1} + R_{2} + R_{3})}{[C_{2} C_{2} R_{1} R_{2} (R_{1} + R_{3}) (2R_{1} + R_{2})]^{(1/2)}} \qquad (1.22)$$

$$C_{2} R_{2} R_{3} \qquad (1.23)$$

Por el contrario, si K = 1 (maxima atenuación):

$$\frac{y_{i}(s)}{y_{i}(s)} = \frac{C_{i}C_{s}R_{i}(R_{i}+R_{s})S^{2} + (2C_{i}R_{i}R_{s}+C_{s}R_{i}(R_{i}+R_{s}+R_{s}))S + 2R_{i}+R_{s}}{C_{i}C_{s}R_{i}R_{i}(R_{i}+R_{s})S^{2} + (2C_{i}R_{i}R_{s}+C_{s}R_{i}(R_{i}+R_{s}+R_{s})+C_{s}R_{s}R_{s})S + 2R_{i}+R_{s}}$$

(1.24)

2 C = R = R = + C = R = (R = + R = + R =)

En este caso:

$$V_{\alpha}(S)$$

1 (1.25)

$V_{A}(S)$  1 + H(S)

De donde necesariamente, se obtienen iguales resultados para lpha, Ho y

Por altimo, si K = 0.5

Que corresponde a la respuesta plana de la banda del ecualizador.

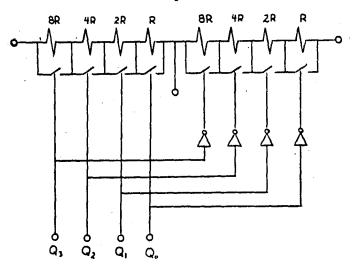

Esta configuración tiene la ventaja de contar solamente con un amplificador operacional, lo cual la hace más barata y compacta. Sin embargo, tiene la desventaja de que la ganancia del ecualizador se controla mediante un potenciómetro no aterrizado. De lo anterior se desprende que la forma de realizar el control digital se puede llevar a cabo mediante interruptores analógicos, como lo muestra la siguiente figuras

FIGURA 1.5 CONTROL DIGITAL DE UN POTENCIONETRO SIMULADO CON DOS REDES R - 2R.

la figura se aprecia la simulación de un potenciómetro mediante dos redes R-2R. Asimismo se muestra la forma de llevar a cabo el control digital del potenciómetro empleando 4 bits unicamente, lo cual solo produce 16 valores distintos de resistencia. Si se desea ecualizador con 8 bits, para así obtener hasta 256 valores diferentes o "posiciones" del potenciometro, se tendrian que utilizar 16 interruptores analógicos y 8 inversores para el control de los interruptores. Otra desventaja que presenta esta configuración es que la relación R-2R de la red de resistencias provoca que para un valor específico del potenciómetro que se pretende simular, el valor de R no sea un valor comercial resistencia. La multiplicación sucesiva del valor de R por 2 daria lugar a otros valores de resistencias no comerciales. Una manera de salvar estas dificultades es emplear resistencias comerciales con el

valor más próximo al deseado. Sin embargo, el error que producirla lo anterior, afectaria tanto a la exactitud de las ganancias o atenuaciones de la banda como a los parámeros propios de la configuración (frecuencia central, factor de calidad, etc.). Otra manera de evitar el uso de valores de resistencias no comerciales, es obtener el valor exacto mediante arreglos de resistencias comerciales. En consecuencia, la voluminosidad de cada banda aumenta considerablemente provocando que las dimensiones del aparato sean mayores.

Por las razones mencionadas, el circuito de la figura 1.ε πο representa una buena solución a la búsqueda de una adecuada configuración.

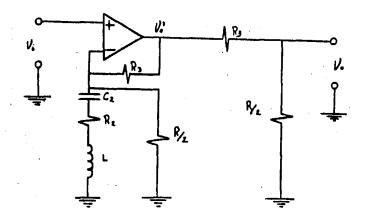

#### 1.2 CONFIGURACION CON UN GIRADOR.

Una segunda opción es utilizar la configuración empleada en algunos ecualizadores comerciales.

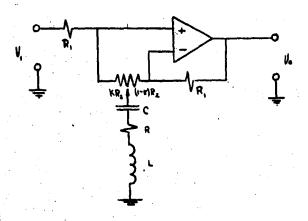

FIGURA 1.6 BANDA DE ECUALIZADOR CON UN GIRADOR

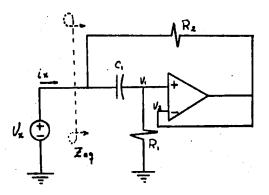

En esta configuración, existe un circuito llamado girador que simula una impedancia compuesta de una resistencia y una inductancia en serie. A continuación se presenta el circuito que realiza esta función, así como las relaciones que rigen el comportamiento del girador.

FIGURA 1.7 GIRADOR

| V. | =   | V <sub>2</sub>                                              | (1.27) |

|----|-----|-------------------------------------------------------------|--------|

| Ix |     | $(V_X - V_B) / R_B + (V_X - V_A) SC_A$                      | (1.28) |

| Ιx |     | $(Vx - V_x) (1 / R_x + SC_x)$                               | (1.29) |

| Ιx |     | $(V_X - V_Z) (R_Z C_Z S + 1) / R_Z$                         | (1.30) |

| v. | . = | Vx R <sub>4</sub> / (R <sub>4</sub> + 1 / SC <sub>4</sub> ) | (1.31) |

| V. | =,  | Vx R, C, S / (R, C, S + 1)                                  | (1.32) |

| Ix | - = | Vx (1 + R2 C2 S) / (R2 R2 C2 S + R2)                        | (1,33) |

| Vx | . , | ' Ix = (R; R; C; S + R;)/(R; C; S + 1)                      | (1.34) |

$$Zeq = (R_x + jH R_x R_x C_x) / (1 + jH R_x C_x)$$

(1.35)

si W Ra Ca (( 1 Entonces :

$$Zeq = R_x + jH R_x R_x C_x = R_x + jH L$$

(1.36)

$$L = R_s R_s C_s \tag{1.37}$$

De lo anterior se desprende que si se cumple la restriccion  $HR_2G_4 <<1$ , entonces el circuito de la figura 1.6 se puede representar como «inue:

FIGURA 1.8 CIRCUITO EQUIVALENTE DE LA FIGURA 1.6.

Para apreciar claramente la operación del ecualizador, se plantea el circuito para k=0, k=0.5 y k=1.

#### a) Para K = O

FIGURA 1.9 EQUIVALENTE DEL CIRCUITO DE LA FIGURA 1.6

PARA K = 0.

$$V_{0}, \qquad R_{3}$$

$$V_{1} \qquad R(LC S^{2} + R_{2} C S + 1)$$

$$= 2(LC S^{2} + R_{3} C S + 1) + RC S$$

$$(1.38)$$

b) Para K = 0.5

FIGURA 1.10 EQUIVALENTE DEL CIRCUITO DE LA FIGURA 1.6 PARA K = 0.5

$$\frac{V_0}{V_1} = \frac{2 R_3}{R} \frac{R}{(1.41)}$$

$$\frac{R}{R} = \frac{2 R_3 + R}{R}$$

(1.41)

$$Vo / Vi = 1 \tag{1.42}$$

#### c) Para K = 1

FIGUPA 1.11 EQUIVALENTE DEL CIRCUITO DE LA FIGURA 1.6 PARA K = 1

$$Vo' / Vi = (R + 2 R_{3}) / R$$

$$R (L C S^{2} + R_{2} C S + 1)$$

$$Vo = 2 (L C S^{2} + R_{2} C S + 1) + R C S$$

$$Vo' = R (L C S^{2} + R_{2} C S + 1) + R C S$$

$$2 (L C S^{2} + R_{2} C S + 1) + R C S$$

$$Vo = 1$$

$$R = 1$$

$$R = 1 + H(S)$$

$$R + 2 R_{3} C S$$

$$(1.43)$$

Para los casos a y c la función H(S) representa un filtro pasobanda, de donde se desprende que las ecuaciones (1.40), (1.42) y (1.45) corresponden al comportamiento característico de un ecualizador.

L C S2 + R2 C S + 1

$$R + 2R_3 \qquad Ho \ (1 \ / \ Q) \ Ho \ S$$

$$H(S) = \frac{1}{L \ C \ S^2 + R_3 \ C \ S + 1} \qquad S^2 + (1 \ / \ Q) \ Ho \ S + Ho^2$$

Esta segunda opción, al igual que la anterior no cubre satisfactoriamente la necesidad de encontrar el circuito ideoneo para la banda del ecuelizador controlado digitalmente.

La razón es que el control de la banda lo realiza un potenciómetro, que aunque se puede separar en dos potenciómetros aterrizados, no implica una simplificación al control, pues el cursor se mueve entre ambos potenciómetros.

Por lo tanto, esta configuración, al igual que la primera opción, no cubre satisfactoriamente la necesidad de simplificar el control digital, ya que requiere de dos potenciómetros aterrizados, o bien, de uno solo con ambos extremos sin aterrizar, con una derivación a tierra en el centro del mismo; encontrándose otra vez el problema presente de un control digital a base de switches analógicos que implican un aumento considerable en el volumen, costo y complejidad de construcción del aparato.

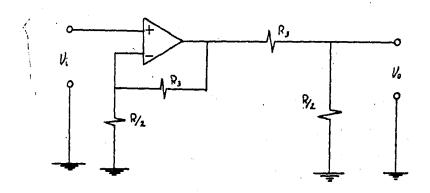

#### 1.3 ECUALIZADOR PARAMETRICO.

Existe un tercer tipo de configuración que lleva a cabo la acción de ecualización, y consiste en utilizar un filtro pasobanda de los denominados filtros en variables de estado.

La configuración es la siguiente:

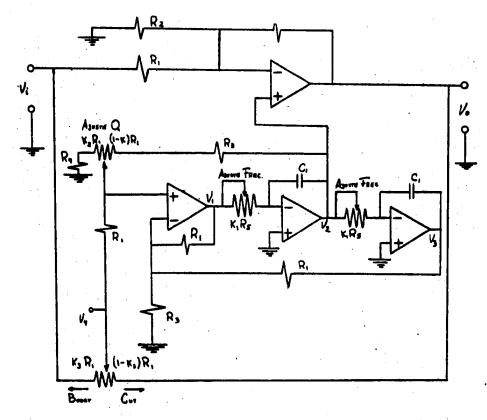

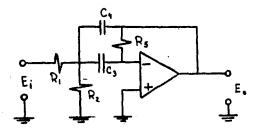

FIGURA 1.12 BANDA DE ECUALIZADOR PARAMETRICO.

En el circuito anterior, se distingue un bloque correspondiente al filtro pasobanda cuya entrada es  $V_{-}$  y la salida es  $V_{-}$ .

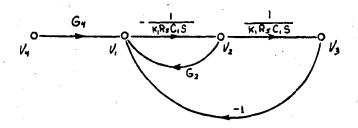

Un reograma correspondiente a dicho bloque es el siguientes

FIGURA 1.13 REOGRAMA CORRESPONDIENTE AL FILTRO PASOBANDA EN VARIABLES DE ESTADO

Si  $R_A = R_A / 2$  y  $R_A = R_A / 15$ , entonces:

$$G_{2} = \frac{4 + 60 \text{ K}_{2}}{25 + 21.5 \text{ K}_{2} - 15 \text{ K}_{2}^{2}}$$

(1.48)

La función de transferencia V2 / V4 es la siguiente:

$$V_{2} = \frac{-0.4}{K_{A} R_{B} C_{A}} = \frac{1}{K_{A}^{2} R_{B}^{2} C_{A}^{2}}$$

$$(1.49)$$

que confirma que el bloque es un filtro pasobanda con los siguientes parámetros:

Para completar el anàlisis de la configuración, se plantea el resto del circuito de la siguiente manera:

FIGURA 1.14 UNIDAD OPERACIONAL DEL ECUALIZADOR PARAMETRICO

Donde  $V_2 = -H(S) V_4$

Del circuito original observamos que  $V_{+}=(1-K_{2})$   $Vi \neq K_{2}$  Vo entonces si  $R_{2}=R_{2}$  / 5

$$Vo = -7 \text{ H(S) } E(1 - K_{3}) \text{ } V_{i} + K_{3} \text{ } V_{0}I - V_{i}$$

$$Vo = \frac{(1 - K_{3}) (7 \text{ H(S)}) + 1}{V_{i}}$$

$$V_{i} = \frac{K_{3} (7 \text{ H(S)}) + 1}{K_{3} (7 \text{ H(S)}) + 1}$$

$$(1.51)$$

La función de transferencia anterior representa claramente la acción de ecualización del circuito.

Esta configuración presenta características muy especiales. La

primera de ellas consiste en que el hecho de estar formada por un filtro en variables de estado, permite variar en forma independiente la frecuencia central del ecualizador, así como el ancho de banda del mismo, sin que el ajuste de uno de los parametros anteriores modifique al otro.

Esto hace que el ecualizador pueda abarcar, con solo dos bandas, el control de toda la gama de frecuencias audibles, pero no al mismo tiempo. Es decir, que en un instante dado solo se controla un cierto rango de frecuencias, restringidas por el ancho de banda seleccionado en ese momento. Si se deseara modificar la ganancia de otro rango distinto de frecuencias, hay que descuidar el rango anterior, a menos que se implementen varias bandas repartidas a lo largo de toda la gama de frecuencias audibles. Sin embargo, esto anula la ventaja del ecualizador de poder seleccionar la frecuencia central de cada banda, además de representar una gran inversión, ya que cada banda necesitaría por lo menos tres amplificadores operacionales y se caería nuevamente en el mismo problema de controlar digitalmente un potenciómetro no aterrizado.

El anàlisis de la configuración anterior no resulta infructuoso como parece, pues da lugar a una idea que puede resolver nuestro problema, y es materia de la próxima sección.

#### 1.4 ECUALIZADOR CON ALIMENTACION HACIA ADELANTE Y RETROALIMENTACION.

Ya desde el año de 1938 Bode desarrolló la idea de un ecualizador variable, la cual sería de gran utilidad para ecualizar cables de

transmision con diferentes longitudes.

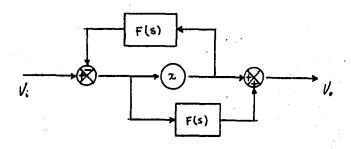

La teoría de un ecualizador del tipo de Bode se expresa matemáticamente con la relación:

en donde L(M) es la curva de ecualización variable en dB, F(M) es la máxima ecualización de la curva en dB y p es el parámetro de control que determina la cantidad y signo de la ecualización.

Bode demostró que la ecuación anterior se puede aproximar a la relación:

En donde

$$x = (1 + p) / (1 - p) - 1 (1.54)$$

V(S) es añora la curva de ecualización variable, x es el parámetro de control que esta en función de p y F(S) es la función de transferencia de la curva de máxima ganancia del ecualizador.

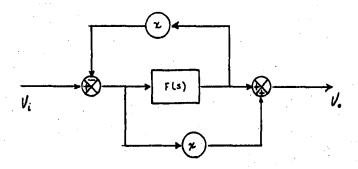

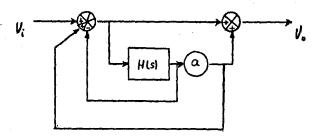

Dos posibles implementaciones de la ecuación (1.53) podrían ser las que se muestran a continuación:

FIGURA 1.15a

FIGURA 1.15b

## FIGURA 1.15 ECUALIZADOR VARIABLE USANDO REALIMENTACION Y TRAYECTORIA DIRECTA

La desventaja de la configuración de la figura 1.15a es que se necesitan dos redes que realicen la función F(S), lo cual significa un aumento en el costo del aparato.

La figura 1.15b salva la desventaja anterior, sin embargo, el hecho de

necesitar dos elementos de control x que trabajen paralelamente sin una terminal común, representa una desventaja.

Además de las contariedades de la implementación física de la ecuación (1.53) señalada en los párrafos anteriores, existe una muy seria restricción en la misma. La ecuación (1.54) muestra que el parámetro de control x no presenta una relación lineal con respecto a p, o sea, a la cantidad de ecualización de la curva V(S).

Lo anterior hace necesario que el elemento de control x sea implementado mediante algun dispositivo con un gran rango de variación para poder alcanzar valores representativos a p=1, es decir x=infinito.

Una forma de resolver el problema anterior es, linealizar la relación de control.

Si sustituimos la ecuación (1.54) en (1.53):

$$V(S) = \frac{C1 + F(S)J - p C1 - F(S)J}{C1 + F(S)J + p C1 - F(S)J}$$

(1.55)

$$V(S) = \frac{1 - \rho G(S)}{1 + \rho G(S)} - 1 < \rho < 1 \qquad (1.57)$$

La ecuación (1.57) es factible de realizarse físicamente, y cuenta con una relación de control líneal de acuerdo a la ecuación (1.52).

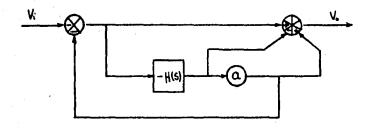

Recordando la fórmula de Mason para reogramas, la ecuación (1.57) se puede implementar bajo el siguiente diagrama:

FIGURA 1.16 ECUALIZADOR VARIABLE DERIVADO DE LA ECUACION (1.57)

La a. erior representa una configuración sencilla con una sola red y un solo parametro de control, el cual es lineal con respecto al grado de ecualización. Sin embargo, la complejidad de la ecuación (1.58) limita el uso de la configuración, pues generaria problemas en la realización de ciertas funciones. Esto dificulta el procedimiento de diseño.

Otra desventaja de esta configuración, es la necesidad de un elemento de control que ofrezca valores proporcionales al intervalo -1(p(1, lo cual implica que dicho elemento no puede estar formado por una simple resistencia variable, sino que debe ser un circuito con ganancia variable entre un valor negativo y otro positivo, o en su defecto, simular una resistencia variable negativa. Ambas soluciones requieren elementos activos para su realización lo cual además de complicar el circuito final, eleva su costo.

A partir de la ecuación (1.55) se puede encontrar otra configuración más sencilla de implementar.

· Sustituyendo (1.59) en (1.55):

Donde H(S) = F(S) - 1

$$V(S) = \frac{1 + F(S) - 2a + 1 + 2a F(S) - F(S)}{1 + F(S) + 2a - 1 - 2a F(S) + F(S)}$$

(1.60)

$$V(S) = \frac{1 + a (F(S) - 1)}{1 + (1-a) (F(S) - 1)}$$

(1.61)

$$V(S) = \frac{1 + a H(S)}{1 + (1-a) H(S)}$$

0 ( a ( 1 (1.62)

(1.63)

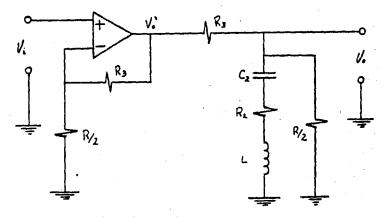

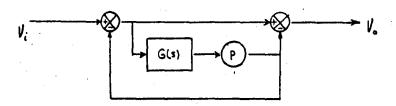

Volviendo a la formula de Mason, la ecuación (1.62) se puede realizar con los arreglos de las siguientes figuras:

FIGURA 1.17a

FIGURA 1.17b

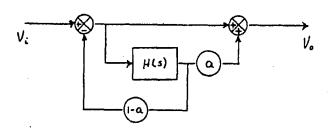

FIGURA 1.17 ECUALIZADOR VARIABLE CON RED ACTIVA UNICA

En ambas realizaciones aparecen los bloques H(S), a, 1-a, sin embargo, la figura 1.17a puede simplificarse agregando una segunda retroalimentación como lo muestra la figura 1.18:

FIGURA 1.18 OPTIMIZACION DEL ECUALIZADOR DE LA FIGURA 1.17

En esta configuración se ha eliminado la existencia del bloque 1-a, por lo que el único elemento de control es el bloque a donde O(a(1, lo que significa que puede ser llevado a cabo mediante un solo atenuador.

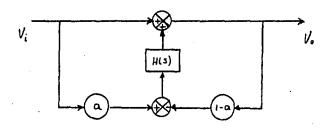

Por su parte, la figura 1.17b puede también simplificarse si observamos que la entrada al bloque H(S) esta dada por la ecuación (1.64):

$$Ve = a Vi - (1 - a) Vo$$

$0 < a < 1$  (1.64)

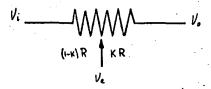

Que es muy parecida a la ecuación de un potenciómetro, como se muestra a continuación:

FIGURA 1.19 POTENCIONETRO

$$Ve = K Vi + (1 - K) Vo$$

$O < K < 1$  (1.65)

La única diferencia entre la ecuación (1.64) y la ecuación (1.65), es el signo del segundo término, lo que se puede arreglar facilmente invirtiendo los signos de la realimentación y una de las trayectorias directas como se plantean en la siguiente figuras

FIGURA 1.20 ALTERNATIVA PARA EL ECUALIZADOR DE LA FIGURA 1.17b

$$Ve = a Vi + (1 - a) Vo$$

(1.66)

$Vo = 1 + a H(S)$  (1.67)

$Vi = 1 + (1 - a) H(S)$

Podemos observar claramente, que esta ultima configuración es la que utiliza el ecualizador paramétrico, en donde el bloque H(S) es

el filtro pasobanda en variables de estado.

Tanto la configuración de la figura 1.18 como la de la figura 1.20, tienen la ventaja de contar con una red H(S) y un solo elemento de control, el cual, además, solo varía entre valores de O a 1. Pero también tiene la gran ventaja de que la relación entre la red H(S) y la función F(S) de máxima ecualización es extremadamente sencilla como se aprecía en la ecuación (1.63).

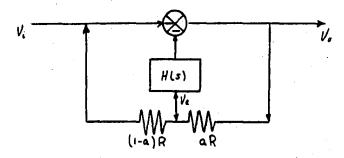

Con la topología de la figura 1.21 se puede realizar cualquier función F(S) a partir de una red H(S).

FIGURA 1.21 CONFIGURACION PARA REALIZAR LA FUNCION H(S).

Para nuestro caso en especial, la topología de la figura 1.20 no resuelve nuestro problema, pues volvemos a la dificultad original del

potenciómetro no aterrizado, sin embargo, la configuración de la figura 1.18 presenta una alternativa que resuelve dicho problema, ya que solo es necesario un atenuador, o bien un potenciómetro aterrizado para el control del ecualizador. Esta caracteristica es tan importante, que es practicamente la que decidirá que la configuración de la figura 1.18 es la óptima para resolver nuestro problema. Lo anterior se deriva del hecho de que el atenuador se puede llevar a cabo a bajo costo y sin gran voluminosidad mediante un convertidor digital-analógico como se verá más adelante.

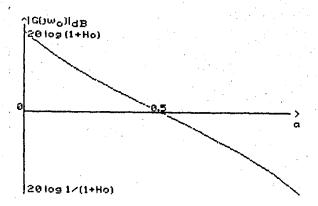

Como ya se menciono antes, los ecualizadores para audio tienen una característica "bump"; de donde la curva de máxima ecualización F(S) es de la forma que muestra la figura 1.22.

FIGURA 1.22 CURVA DE LA HAGNITUD DEL ECUALIZADOR PARA MAXIMA

GANANCIA.

La curva mostrada en la figura 1.22 corresponde a las ecuaciones (1.70) y (1.71).

$$S^{2} + B \text{ Ho } S + \text{Ho }^{2}$$

$F(S) = \frac{B}{\sqrt{3}} + \alpha \text{ Ho } S + \text{Ho }^{2}$

$S^{2} + \alpha \text{ Ho } S + \text{Ho }^{2}$

De donde si  $\beta = \alpha (Ho + 1)$

Al comparar estas ecuaciones con la ecuación (1.63) se concluye que H(S) corresponde a la función de transferencia de un filtro pasobanda, misma que es necesario implementar para construir la configuración de la figura 1.18.

### 2 DISENO DE UN CANAL DEL ECUALIZADOR.

### 2.1 INPLEMENTACION DE LA BANDA BASICA DEL ECUALIZADOR.

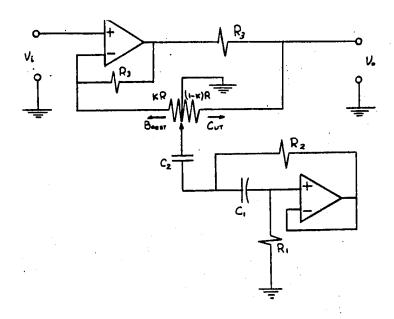

El siguiente paso es diseñar la implementación física del diagrama de bloques de la figura 1.18.

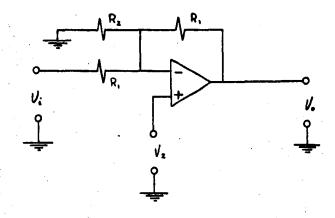

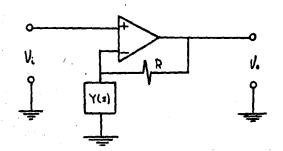

Para llevar a cabo la implementación de los sumadores utilizaremos configuraciones inversoras y no inversoras de amplificadores operacionales.

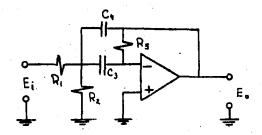

Los filtros pasobanda H(S) los se realizaron mediante la configuración de segundo orden de realimentación múltiple, mostrada en la figura 2.1 cuya función de transferencia se presenta a continuación.

De la ecuación anterior se obtienen los parámetros Ho, Ho y Q como sique:

$$Ho = \frac{1}{R_z} \qquad (2.2)$$

$$\frac{R_z}{R_z} \qquad (1 \neq \frac{C_+}{C_-})$$

$$R_z \qquad C_z \qquad (2.3)$$

$$Ho = [ \frac{1}{R_z} \qquad (-1 \neq \frac{1}{R_z} ) ]^{(2.3)}$$

El procedimiento de diseño se muestra a continuación:

Dados Ho, Q y Ho

Se elige Ca = Ca = C, y se calculan:

$$R_{s} = \frac{Q}{W_{0} + W_{0}}$$

(2.5)

$$R_{2} = \frac{Q}{(2.6)}$$

(2.6)

FIGURA 2.1 FILTRO PASOBANDA. CONFIGURACION REALIMENTACION MULTIPLE.

Es importante mencionar que para los requerimientos de un ecualizador, un filtro pasobanda de segundo orden es suficiente, debido a que la relación costo-beneficio no justifica el uso de filtros de orden superior que multiplican el costo de los circuitos, pues el oido humano no aprecia una gran diferencia entre una pérdida abrupta de ganencia que podría proporcionar un filtro de cuarto o sexto orden, y una pérdida más tenue que proporciona un filtro de segundo orden.

La razón de usar la configuración realimentación multiple es simplemente la sencillez de la misma.

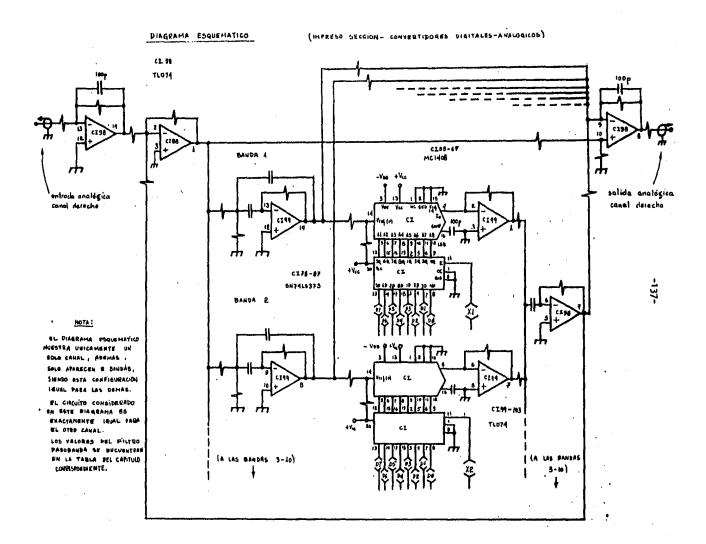

Por otra parte, la manera de llevar a cabo el atenuador "a", es de vital importancia, pues como hemos visto a lo largo de este trabajo, es el factor que más ha influido en la elección de la banda del ecualizador. La importancia de este factor radica en que es el atenuador "a" el acoplamiento entre la sección analógica del ecualizador y el control digital del mismo. Es decir, que lo que se

necesita es un atenuador digital, y la manera más sencilla y barata, es usar un convertidor digital—analogico que en realidad no es mas que un dispositivo que atenúa un voltaje de referencia en base a una palabra digital. Si en lugar de usar un voltaje constante, usamos el voltaje de salida de los filtros como voltaje de referencia, lo que tendremos será un atenuador digital con 256 distintos valores de atenuación que van desde O hasta 255/256.

Es fâcil darse cuenta que la alternativa del convertidor digital analógico ya se vislumbraba desde el principio del presente trabajo, cuando se propuso un potenciometro controlado digitalmente, como el que se muestra en la figura 1.5.

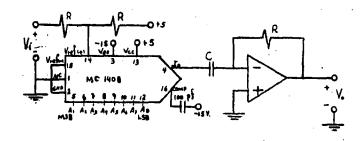

El DAC utilizado es el MC 1408, escogido por su bajo costo, su buena precisión y porque una de sus principales aplicaciones es precisamente la de atenuador digital.

El único obstáculo para usar este DAC como atenuador digital, es que no es bipolar, sino que trabaja unicamente con valores unipolares en el voltaje de referencia, sin embargo, la manera de solucionar el problema, es montar la señal en una componente de voltaje de directa y posteriormente eliminarla mediante un capacitor de tantalio. Hasta aquí no terminan las consideraciones para usar el DAC como atenuador digital, pues este no es un dispositivo cuya salida sea un voltaje, sino que a la salida del DAC existe una corriente proporcional al voltaje atenuado. Para convertir de corriente a voltaje, usaremos un amplificador operacional. La implementación final del atenuador, se muestra en la figura 2.2.

FIGURA 2.2 ATENUADOR DIGITAL.

De la configuración anterior tenemos la relación:

$$V_0 = \frac{K}{----} V_1$$

$K = 0,1, ...255$  (2.8)

Una vez definidos todos los bloques de la configuración de la banda, se pueden reacomodar y tratar de optimizar la configuración para llegar a la que se muestra en la figura 2.3 que es equivalente a la de la figura 1.18.

FIGURA 2.3 CONFIGURACION DEFINITIVA PARA CADA BANDA.

# Del diagrama anterior tenemos que:

Se nota claramente que esta configuración tiene solo dos diferencias con respecto a la de la figura 1.18, que sons para máxima ganancia a = 0 y para máxima atenuación a = 1, y la otra diferencia es que se trata de una configuración inversa.

### 2.2 CONJUNCION DE 10 BANDAS BASICAS DE UN CANAL DEL ECUALIZADOR.

Hasta aquí se ha escogido la configuración idónea para formar cada banda del ecualizador, pero falta encontrar la mejor manera de juntar 10 de estas bandas para formar un canal del ecualizador.

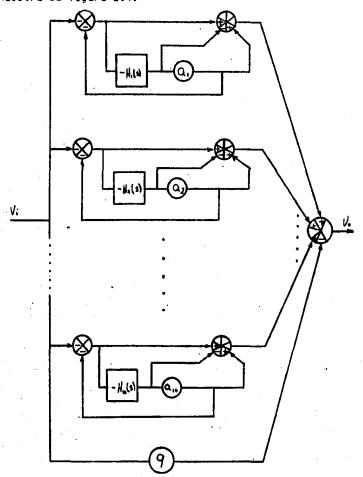

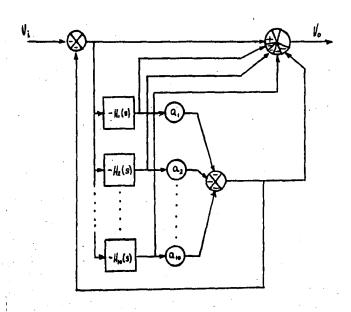

La primera manera que viene a la mente para conjuntar 10 bandas es, conectar las entradas de las 10 bandas en paralelo y sumar sus salidas como lo muestra la figura 2.4.

FIGURA 2.4 PRIMERA OPCION PARA LA CONJUNCION DE 10 BANDAS DE UN CANAL DEL ECUALIZADOR.

En la figura se observa que también existe una trayectoria directa desde la entrada hasta la salida, con valor de -9. Esto se debe a que cuando los controles de las 10 bandas apunten O decibeles, se debe obtener una respuesta plana de ganancia unitaria en la salida del canal, por tanto, como cada banda aporta una función de transferencia unitaria, la ganancia total de las 10 trayectorias sería de 10, lo que hace necesario restar 9 veces la entrada para que la ganancia total sea unitaria.

La función de transferencia total del canal es:

Esta configuración para el canal es lógica, sin embargo considerando que cada banda necesita 4 amplificadores operacionales, sería necesario utilizar 84 de éstos para los dos canales del ecualizador, lo cual resulta en una elevación del costo del aparato.

Además, la curva de magnitud de la función de transferencia de la ecuación (2.11), no es simétrica para a<sub>4</sub>=0 y para a<sub>4</sub>=1, pues para el primer caso:

$$V_0(S)$$

= 0

$V_0(S)$  = 1 -  $V_0(S)$  (2.12)

$V_0(S)$  = 0

y para a.=1

$$Vo(S)$$

= 0 1 (2.13)

$Vi(S)$  = 1 +  $H_4(S)$

Por estas razones, es necesario buscar una configuración más compacta para cada canal como la que se propone en la figura 2.5.

FIGURA 2.5. SEGUNDA OPCION PARA LA CONFIGURACION DE CADA CANAL DEL ECUALIZADOR

La función de transferencia de esta configuración es:

Obviamente el comportamiento de las configuraciones de las figuras 2.4 y 2.5 no es igual, pero si muy parecido, sin embargo, la última tiene ventajas sobre la primera, las cuales consisten en que la configuración de la figura 2.5 si es simétrica para los valores de ai=0 y ai=1 como se muestra a continuación:

para a,=0

$$Vo(S)$$

= -1 -  $\frac{1}{\Sigma}H_{4}(s)$  (2.16)

para a<sub>i</sub>=1

Pero la razón más importante, es que el número total de amplificadores operacionales que se necesitan para los dos canales del ecualizador, usando esta configuración, es 48, casi la mitad que usando la otra configuración.

Por tanto, se concluye que la mejor configuración para usar en cada canal, es la que se muestra en la figura 2.5.

## 2.3 SELECCION DE LOS PARAHETROS DE LA RED ACTIVA PARA LA BANDA BASICA.

Una de las características más importantes de un ecualizador gráfico es el número de bandas del mismo.

Al igual que el número de bandas aumenta, el control que se tiene sobre la gama de frecuencias audibles aumenta también. Sin embargo, por limitaciones de costo y espacio es necesario escoger un número

limitado de bandas. Cada banda tendrá control sobre las frecuencias limitadas por el ancho de banda de la misma.

Claramente se observa que el ancho de banda de la función de máxima ganancia F(S) = H(S) + 1, está en función del ancho de banda del filtro pasobanda H(S). Lo mismo ocurre con la máxima ganancia de la banda y la ganancia del filtro pasobanda H(S).

Por lo anterior, se hace necesario obtener dichas relaciones que nos permitan diseñar los parámetros del filtro pasobanda.

### 2.3.1 RELACION DE GANANCIAS.

Sea la función del ecualizador G(S)

$$G(S) = \frac{1 + (1 - a) H(S)}{1 + a H(S)}$$

(2.18)

donde H(S) representa un filtro pasobanda,

a representa el parametro de control O < a < 1

$$H(S) = \frac{Ho \propto Ho S}{S^2 + \propto Ho S + Ho^2}$$

(2.19)

donde Ho es la ganancia del filtro para H = Ho

c es el inverso del factor de calidad (c = 1 / 9).

Ho es la frecuencia central en la cual ocurre la mayor

ganancia del filtro.

Se sabe que para a = 0 se tiene la ganancia máxima del ecualizador para H = Ho.

Dicha ganancia expresada en decibeles se puede expresar como se muestra a continuación:

$$G_{\text{max}} \text{ dB} = 20 \log / G(j_{\text{No}}) / = 20 \log (1 + Ho)$$

(2.20)

Si se desea construir un ecualizador cuya maxima ganancia y máxima atenuación sean  $\neq$ 15 dB y =15 dB respectivamente entonces:

$$15 = 20 \log (1 + Ho)$$

(2.21).

de donde

$$Ho = 4.6234$$

(2.22)

Este es el valor de Ho con el que se deben diseñar los filtros pasobanda de todas las bandas del ecualizador.

## 2.3.2 RELACION DE ANCHO DE BANDA

Se requiere obtener una relación entre el factor de calidad del filtro pasobanda, y el factor de calidad correspondiente a la banda ecualizante para el caso de máxima ganancia.

Una vez más, para a = O

El factor de calidad del ecualizador al que denotaremos como Qe se puede definir de igual forma que el factor de calidad del filtro Q, es decir:

$$Qa = Ho / (H_2 - H_2)$$

(2.25)

donde  $H_{2}$ - $H_{3}$  representa el ancho de banda, entendiéndose a éste como la gama de frecuencias en la cual el modulo / G(jH) / no se atenua más de 3 dB del máximo, es decir:

$$(1 + Ho) / 2^{(1/2)} \le / 6(jH) / \le 1 + Ho$$

(2.26)

por lo tanto, el primer paso es obtener H<sub>2</sub> y H<sub>2</sub> como se muestra a continuación

$$2 ( Ho^{2} - H^{2})^{2} + 2 (I + Ho)^{2} (\alpha Ho H)^{2} =$$

$$= (I + Ho)^{2} (Ho^{2} - H^{2})^{2} + (I + Ho)^{2} (\alpha Ho H)^{2}$$

$$(2.28)$$

$$(1 + Ho)^2 (\alpha Ho H)^2 = C (1 + Ho)^2 - 2I (Ho^2 - H^2)^2$$

(2.29)

$$(1 + Ho) (\alpha Ho H) = \pm (Ho^2 - H^2) \{ (1 + Ho)^2 - 2 \}^{(1/2)}$$

(2.30)

Optando primero por desarrollar esta ecuación con el signo positivo de la raiz cuadrada, se tiene:

$$H^{2}\{(1 + H_{0})^{2} - 2\}^{(1/2)} + H(1 + H_{0}) \propto H_{0} - H_{0}^{2}\{(1 + H_{0})^{2} - 2\} = 0$$

$$(2.31)$$

$$-(1 + H_{0}) \propto H_{0} + H_{0}\{\alpha^{2}(1 + H_{0})^{2} + 4 E(1 + H_{0})^{2} - 2J\}^{(1/2)}$$

$$H = \frac{2\{(1 + H_{0})^{2} - 2J^{(1/2)}\}}{(2.32)}$$

De esta ecuación se obtienen dos valores correspondientes a la frecuencia en la cual existe una pérdida de 3 dB de la máxima ganancia, uno de ellos positivo y el otro negativo.

Lógicamente, interesa el primero, al que denotaremos N.

$$H_{d} = \frac{-\alpha (1 + H_{0}) + (\alpha^{2}(1 + H_{0})^{2} + 4\Gamma(1 + H_{0})^{2} - 2)^{r_{d}/2}}{2}$$

$$= \frac{2}{((1 + H_{0})^{2} - 2)^{r_{d}/2}}$$

(2.33)

De igual forma, desarrollando la ecuación (2.30) con el signo negativo de la raiz cuadrada, se obtiene el otro valor de W positivo que llamaremos Ma

Ho

$$\propto (1 + Ho) + (\propto ^2(1 + Ho)^2 + 4E(1 + Ho)^2 - 23)^{(4/2)}$$

$$H_2 = --- \{ (1 + Ho)^2 - 23^{(4/2)} \}$$

$$(2.34)$$

El ancho de banda queda definido entonces por Ma - Ma

$$u_{x} - u_{x} = \frac{\alpha (1 + Ho) No}{(2.35)}$$

$$(1 + Ho)^{2} - 2)^{(2/2)}$$

Por consiguiente, el factor de calidad del ecualizador Qe es función tanto de la ganancia Ho, como del factor de calidad Q del filtro pasobanda, como lo afirma la siguiente ecuación:

El punto más importante ahora, es seleccionar un valor adecuado para el factor de calidad del ecualizador.

Para tal efecto es necesario contar con un criterio acerca de la gama de frecuecias que se podrà controlar con una banda, es decir, determinar un límite entre dos bandas adyacentes en el cual se considera que los efectos de cada banda terminan. Consecuentemente, lo anterior puede despertar alguna controversia, ya que el comportamiento real nunca satisface dicha consideración, sin embargo, es indispensable fijar dichos límites para seleccionar el factor de calidad adecuado.

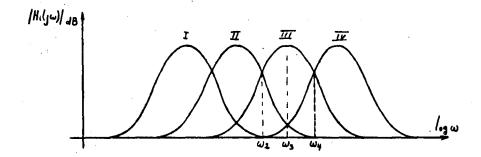

Un criterio adecuado para determinar el valor adecuado del factor de calidad del ecualizador, es considerar la máxima ganancia en todas las bandas de un canal como lo muestra la figura 2.6

FIGURA 2.6 MAXIMA GANANCIA EN TODAS LAS BANDAS

DE UN CANAL DEL ECUALIZADOR.

El comportamiento ideal del canal en estas condiciones, es obtener una curva plana a lo largo de todas las frecuencias audibles.

De la figura 2.6 puede observar que las frecuencias críticas en donde pueden ocurrir máximos y mínimos de la ganancia son las frecuencias centrales de cada banda, y las frecuencias en donde se cruzan dos bandas adyacentes, por ejemplo, Ha y Ma.

El problema de seleccionar el factor de calidad de cada banda se reduce a igualar las ganancias en tales frecuencias.

De acuerdo a la ecuación (2.15) sabemos que para el caso planteado en la figura 2.6 ai=0, por lo tanto:

$$(G(jH))' = f + \frac{10}{1 + 1} H_x(jH) f$$

(2.37)

dondes

$$j \ Ho \propto Ho \ H$$

$H_{a}(j \ H) = \frac{1}{Ho^{2} - H^{2} + j \propto Ho \ H}$

(2.38)

· Se,observa que para Ha

$$G(jH_{a}) = 1 + \sum_{i=1}^{10} H_{i}(jH_{a})$$

(2.39)

Ahora bien, para simplificar los calculos y considerando que sobre la frecuencia  $W_{2}$  solo actúa la banda III, se puede reducir la ecuación (2.39) en:

$$G(jH_{3}) = 1 + H_{0}$$

(2.40)

Por otra parte, si se obtiene la ganancia total en una frecuencia intermedia entre dos frecuencias centrales, tal como  $W_{2}$ , y considerando que sobre esta solo actuan las bandas II y III, que están separadas una octava, podemos obtener una ecuación analoga a la (2.40) como sigue:

Un punto importante en este paso, es darse cuenta que en la ecuación (2.41) se estan sumando números complejos, pero hay que observar

también que los términos segundo y tercero del segundo miembro de dicha ecuación, son números complejos conjugados, es decir, su módulo es el mismo, pero su argumento está conjugado. Por, tanto la suma de ellos es un número real.

De lo anterior se concluye que:

$$2\sqrt{2} \text{ Ho } \alpha$$

$G(jH_2) = 1 + \frac{2\sqrt{2} \text{ Ho } \alpha}{[1 + 2\sqrt{2}]^{(2/2)}}$

$(2.42.$

en donde y representa el argumento de los números conjugados, el cual está en función de o, pero sabemos que está entre O y 90 grados. Para agilizar los cálculos, dicho ángulo lo supondremos alrededor de 30 grados, por lo que cos y = 0.866.

Si se igualan las ecuaciones (2.41) y (2.42), se tiene:

$$1 + H_0 = 1 + \frac{2 \sqrt{2} H_0 \alpha}{\sqrt{1 + 2 \alpha^2}} (0.866) \qquad (2.43)$$

De lo anterior, se obtiene ques

$$4 \alpha^2 = 1$$

(2.44)

$$Q = 2$$

(2.45)

Para corroborar la certeza de este valor, se indagaron los factores de calidad correspondientes a los filtros pasobanda que conforman las bandas básicas de algunos ecualizadores comerciales, tales comno los de las referencias [22] y [25].

La banda bàsica del ecualizador de la referencia [22] es la que se mostro en la figura 1.6.

De la ecuación 1.40 es posible obtener el factor de calidad del filtro pasobanda de la siguiente forma:

$$HO = \frac{1}{(L C)^{(1/2)}}$$

(2.46)

$$\propto Ho = \frac{R_{\pi}}{L} \tag{2.47}$$

Sustituyendo (2.46) en (2.47):

$$Q = \frac{C(4/2)}{R_2 C(4/2)}$$

(2.48)

Valuando en esta ecuación los valores de los elementos de una banda, por ejemplo:

se desprende ques

$$Q = 2.0$$

(2.49)

La banda bàsica del ecualizador de la referencia [25] es muy similar a la anterior, pues también cuenta con un girador.

A continuación se muestra el circuito de esta banda con el circuito del girador.

FIGURA 2.7 BANDA BASICA DEL ECUALIZADOR DE LA REFERENCIA [25].

Si se plantea el circuito anterior para k=0, se simplifica mucho la configuración:

FIGURA 2.8 CIRCUITO DE LA FIGURA ANTERIOR PARA HAXIMA GANANCIA.

Del circuito anterior, se tiene que:

De esta ecuación se desprende que:

Sustituyendo los valores de una banda en la ecuación anterior, como son:

se obtiene:

$$Q = 2.28$$

(2.52)

Los resultados de las ecuaciones (2.49) y (2.52) confirman que el valor obtenido en la ecuación (2.45) bajo nuestro criterio concuerda con los valores del factor de calidad de los ecualizadores comerciales.

# 2.4 IHLPENENTACION FINAL DE UN CANAL DEL ECUALIZADOR.

Con los valores de Ho y Q correspondientes al filtro pasobanda seleccionados en la sección anterior, se procedió a diseñar cada uno de los 10 filtros que conforman el canal del ecualizador.

FIGURA 2.9 FILTRO PASOBANDA.

Para este efecto, se usaron las ecuaciones de diseño (2.5), (2.6) y (2.7). Por supuesto, que los valores nominales emanados de estas ecuaciones, para cada elemento de los filtros, no son valores comerciales, pero tratamos de escoger juegos de elementos en los que cada uno de ellos se acerque lo más posible a algún valor comercial, con el fin de que el valor real de los parâmetros de la red (Ho, Q y fo) no se aleje del ideal.

Este procedimiento, conduce a la tabla 2.1, que muestra los valores seleccionados de los elementos de cada filtro pasobanda y el valor real de cada parámetro que produce el conjunto de los mencionados elementos.

| Frecuencia de | ¢    | R1   | R2   | R5   | Но   | fo       | Q    |

|---------------|------|------|------|------|------|----------|------|

| la banda (Hz) | (nf) | (KD) | (Kg) | (KR) |      | (Hz)     |      |

| 31.25         | 220  | 10   | 12   | 100  | 5    | 30.97    | 2.14 |

| 62.5          | 150  | 6.8  | 10   | 68   | 5    | 63.95    | 2.05 |

| 125           | . 56 | 10   | 12   | 100  | 5    | 121.69   | 2.14 |

| 250           | 27   | 10   | 12   | 100  | 5    | 252.39   | 2.14 |

| 500           | . 11 | 12   | 15   | 120  | 5    | 511.54   | 2.12 |

| 1000          | 6.8  | 10   | 12   | 100  | .5   | 1002.15  | 2.14 |

| 2000          | 3.3  | 10   | 12   | 100  | 5    | 2065.03  | 2.14 |

| 4000          | 1.5  | 10   | 15   | 100  | 5    | 4331.64  | 2.04 |

| 8000          | 0.68 | 12   | 18   | 120  | 5    | 7962.60  | 2.04 |

| 16000         | 0.33 | 13   | 18   | 120  | 4.62 | 16024.65 | 2.00 |

TABLA 2.1

Cabe mencionar que los elementos usados, tanto capacitores como resistencias, tienen una tolerancia de 5% y 10%.

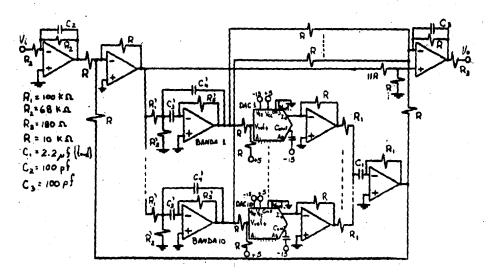

La implementación final del canal del ecualizador, siguiendo el diagrama de bloques de la figura 2.5, se muestra en la figura 2.10.

FIGURA 2.10 IMPLEMENTACION FINAL DEL CANAL DEL ECUALIZADOR

En la figura, se aprecian dos capacitores  $C_2$  y  $C_3$ , destinados a producir un corte en frecuencias altas para evitar el ruido de radiofrecuencia. Se desea que los capacitores introduzcan un polo en la respuesta en frecuancia del canal en 20 KHz.

Existe un método sencillo para el cálculo de los capacitores, el cual consiste en considerar que la ecuación que determina los polos de un circuito; está dada por:

$$1 + b_1 S + b_2 S^2 + \dots + b_n S^n = 0$$

(2.53)

La cual se puede factorizar:

$$(1 + \frac{S}{P_A}) (1 + \frac{S}{P_B}) \dots (1 + \frac{S}{P_n}) = 0$$

(2.54)

Desarrollando la ecuación (2.54) e igualandola con la ecuación (2.53) se obtiene que:

En un circuito electrico con resistencias y capacitores sabemos que el coeficiente bl del termino lineal de la ecuación (2.53) siempre está dado por la ecuación (2.56).

$$b_x = \sum_{i} R_{x,i} C_x \tag{2.56}$$

donde  $R_{4,0}$  es la resistencia que "ve" el capacitor Ci cuando los demás capacitores están en circuito abierto, es decir  $C_{J}=0$ ,  $j \neq i$ .

Igualando (2.55) y (2.56)

Si consideramos que existe un polo dominante Pd=P, que produce el corte en alta frecuencia, se debe cumplir que

$$Pd = P_{x} \langle \langle P_{x}, P_{x}, \dots, P_{n} \rangle \qquad (2.58)$$

Por tanto, una buena aproximación a la ecuación (2.57) es:

$$\sum_{i} R_{i,o} C_{i} = \frac{1}{---}$$

$$Pd$$

(2.59)

Para nuestro caso, en esta sumatoria solo se consideran  $C_2$  y  $C_3$ , pues los capacitores de los filtros forman parte de una red que produce ganancia unitaria en alta frecuencia, y el capacitor  $C_3$  sirve para producir un corte en baja frecuencia.

Entonces, del circuito se tiene que:

$R_{20} = R = 10000 \ \Omega$ .

Ran = 68000 p.

Si Pd = 2 ( 3.1416 ) ( 20000 ) y fijamos C2 = C3, resulta:

Ca = Ca = 102 pf

Este es el valor de los capacitores que produce un corte en 20 KHz.

Notese que tampoco hemos considerado la respuesta en frecuencia de los amplificadores operacionales usados en la implementación del canal. La razón es que se optó por trabajar con el circuito integrado TLO74 que contiene 4 amplificadores operacionales. Estos dispositivos ya están internamente compensados para producir un corte en altas frecuencias. Para nuestro caso, en el que se usaron niveles bajos de voltaje en la salida, así como valores pequeños de ganancia, el polo del amplificador operacional se encuentra alrrededor de 100 KHz, que obviamente está sobrado, pues las frecuencias audibles más altas son del orden de 20 KHz.

Otras razones para haber usado el circuito integrado TLO74 para todas las implementaciones con amplificadores operacionales son: tiene entrada JFET, es de bajo ruido, tiene baja distorsión armónica, está internamente compensado y está protegido contra corto circuitos en las salidas.

El capacitor C4, como ya se menciono, sirve para eliminar la componente de voltaje de directa proveniente de los convertidores digital—analógico. Sin embargo, se debe tener cuidado al escoger el valor del capacitor, pues un valor no apropiado podría producir un polo dentro de la zona de frecuencias audibles.

El procedimiento de selección de  $C_{2}$ , es muy parecido al de  $C_{2}$  y  $C_{2}$ 2

Si la ecuación:

$$S^n + b_2 S^{(n-2)} + ... + b_{n-2} S + b_n = 0$$

(2.60)

contiene a los polos del sistema, entonces se puede factorizar como sique:

$$(S + P_4) (S + P_2) \dots (S + P_{n-4}) (S + P_n) = 0$$

(2.61)

Igualando las dos ecuaciones anteriores, se puede demostrar que:

$$b_x = \sum_{k=0}^{n} P_k \tag{2.62}$$

En los circuitos eléctricos con capacitores y resistencias, el término b<sub>e</sub> está dado por:

$$b_{z} = \sum_{x=x}^{n} \frac{1}{C_{x} R_{x} \text{ intenses}}$$

(2.63)

donde  $R_{s-sin-s+o}$ , es la resistencia "vista" por cada capacitor  $C_s$  cuando los demás capacitores están en corto circuito  $(C_s = infinito)$ ,  $j \neq i$ .

Ahora bien, se considera la existencia de un polo dominante Po= $P_a$  para bajas frecuencias, entonces se debe cumplir que:

$$P_{\alpha} = P_{\perp} \rangle\rangle P_{\alpha}, P_{\beta}, \dots, P_{n}$$

(2.64)

De aqui, una buena aproximación a la ecuación (2.63) es:

$$P_{d} = \sum_{n=1}^{\infty} \frac{1}{C_{n} R_{n} \sin 2n}$$

$$(2.65)$$

Volviendo a nuestro caso, en esta ecuación solo intervienen  $C_2$ , pues  $C_2$  y  $C_3$  son para producir cortes en alta frecuencia y los capacitores de los filtros tampoco representan una impedancia considerable para frecuencias menores a 30 Hz.

For tanto, se desea un corte en 7 Hz, de la figura 2.00 observamos que  $R_{x=xn+inx+n}=R_{x}/10=10000~\Omega$ .

De donde:

C = 2.2 Mf

Finalmente, en la entrada del canal, se agrego una configuración inversora cuya finalidad es eliminar el signo negativo de la función de transferencia de la ecuación (2.15), y proporcionar una impedancia de entrada de 68000 ohms, la cual no es tan baja para producir una caida de voltaje al conectar algún aparato a la entrada del ecualizador, ni tan alta para facilitar la aparición de ruido a la entrada del canal.

### 3 AJUSTE DE LA CURVA GANANCIA-ATENUACION DE LA BANDA BASICA.

En el capítulo 1, sección 4, se habló de que en la ecuación (1.52) se representa una función L(H) en dB que es la curva de ecualización variable en función de un parámetro p y una curva de máxima ecualización F(H) en dB. En dicha función, L(H) es lineal con respecto al parametro p. Sin embargo, al aproximar la ecuación (1.52) a la (1.53) se perdió la proporcionalidad de aquellos parametros.

Si se recuerda que la banda básica elegida para configurar nuestro ecualizador se derivo de la ecuación (1.53), es facil percatarse que subsiste la no linealidad entre aquellos parametros. Lo anterior se hace presente si de la ecuación (2.10) se obtiene el módulo de G(jH) en decibeles para H=Ho.

$$\frac{1 + (1 - a) H_0}{(G(jN)/dB} = 20 \log \frac{1}{-----}$$

$$\frac{1 + a H_0}{(3:1)}$$

Al graficar  $(G(jHo))/_{dB}$  contra a, se llega a la grafica de la figura 3.1

FIGURA 3.1 CURVA GANANCIA-ATENUACION DE LA BANDA BASICA.

En esta figura claramente se manifiesta la no linealidad entre la ganancia en dB de la banda y el parametro de control "a" ó atenuador "a".

Ahora bien, se decidió dividir la gama de ganancias de +15 dB a -15 dB de cada banda en 32 pasos, es decir que, la minima variación posible en la ganancia es de 1 dB. Se pensó así, porque consideramos que para el oldo humano no es perceptible un cambio menor a 1 dB. Lo anterior sugiere que el control digital debe hacer uso de un contador de 5 bits que maneje a los atenuadores digitales.

Sin embargo, surge un problema grave al dividir en 32 valores el parametro "a" de atenuación que va de 0 a 1 , y verificar la gamancia real que dichos valores proporcionan a la banda básica.

## Este problema se manifiesta claramente en la tabla 3.1

| Palabra<br>digital | Valor del parametro " | a" Ganancia   | deseada<br>dB | Ganancia real<br>dB |

|--------------------|-----------------------|---------------|---------------|---------------------|

| 00000              | 0.0000                |               | 15            | 15.00               |

| 00001              | 0.0313                |               | 14'           | 13,60               |

| 00010              | 0.0625                |               | 1.3           | 12.34               |

| 00011              | 0.0938                |               | 12            | 11.18               |

| 00100              | 0.1250                |               | 11            | 10.10               |

| 00101              | 0.1563                |               | 10            | 9.08                |

| 00110              | 0.1875                |               | 9             | 8.12                |

| 00111              | 0.2188                |               | 8             | 7.21                |

| 01000              | 0.2500                |               | 7             | 6,33                |

| 01001              | 0.2813                |               | 6             | 5.48                |

| 01010              | 0.3125                |               | 5             | 4.66                |

| 01011              | 0.3438                | 4.00          | 4             | 3.85                |

| 01100              | 0.3750                |               | 3 -           | 3.06                |

| 01101              | 0.4063                |               | 2             | 2.29                |

| 0 1 1 1 0          | 0.4375                |               | . 1           | 1.52                |

| 01111              | 0.4688                |               | <b>O</b> .    | 0.76                |

| 10000              | 0.5000                |               | -0            | -0.00               |

| 10001              | 0.5313                | •             | -1            | -0.76               |

| 10010              | 0.5625                |               | -2            | -1.52               |

| 10011              | 0.5938                |               | -3            | -2.29               |

| 10100              | 0.6250                |               | -4            | -3.06               |

| 10101              | 0.6563                |               | -5            | -3.85               |

| 10110              | 0.6875                |               | -6            | -4.66               |

| 10111              | 0.7188                | ,             | -7            | -5.48               |

| 11000              | 0.7500                |               | -8            | -6.33               |

| 11001              | 0.7813                |               | -9            | -7.21               |

| 11010              | 0.8125                | · -           | -10           | -8.12               |

| 11011              | 0.8438                | -             | -11           | -9.08               |

| 11100              | 0.8750                | -             | -12           | -10.10              |

| 11101              | 0.9063                |               | -13           | -11.18              |

| 11110              | 0.9375                | -             | -14           | -12.34              |

| 1 1 1 1 1          | 0.9688                | · · · · · · · | -15           | -13.60              |

### TABLA 3.1

En la tabla anterior, se observa una diferencia grande entre los valores de ganancia deseados y los valores reales. Esto se debe por una parte a que la curva ganancia-atenuación mostrada en la figura 3.1, no es lineal, y por otra parte a que la cuenta binaria máxima equivale al número 31 decimal, por lo tanto, el valor máximo que

se puede obtener en el atenuador, es de 0.9688 lo que implica que no se alcanzará el valor de -15 dB de ganancia en cada banda. Esto último es una consecuencia de que la interfase entre la palabra digital y el valor del atenuador, es un convertidor digital-analógico.

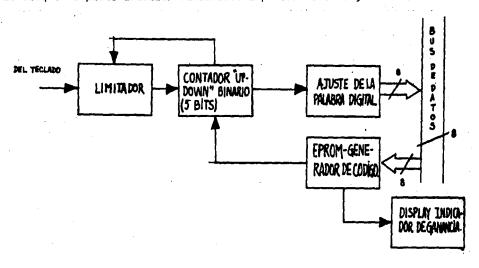

Por tanto, si se quiere diseñar un aparato, del cual una de sus ventajas es la precisión, se debe forzosamente dar un remedio a este problema. La solución es utilizar la máxima resolución que nos permite el convertidor, y que es de 256 bits, pues el convertidor es de 8 bits.

Para este efecto, despejamos de la ecuación (3.1) el parametro "a":

$$(1 + H_0) = 10^{-0/20}$$

$$A = \frac{1}{H_0} (1 + 10^{-0/20})$$

(3.2)

donde G= /G(jNo)/am

A partir de esta ecuación, se puede construir una tabla en la que una palabra digital de 5 bits, va a direccionar a otra de 8 bits, la cual aproxima al valor más cercano del parámetro "a" de atenuación necesario para producir el valor exacto de ganancia deseada en cada banda básica. Esta tabla se presenta a continuacións

| Ganancia<br>deseada dB | Valor del atenuador "a"<br>necesario | Palabra digital Palabra digital<br>8 bits 5 bits |

|------------------------|--------------------------------------|--------------------------------------------------|

| 15<br>14               | 0.000                                | 00000000 00000 00000                             |

| 13                     | 0.046                                | 00001100 00010                                   |

| 12                     | 0.071                                | 00010010 00011                                   |

| 11                     | 0.099                                | 00011001 00100                                   |

| 10                     | 0.128                                | 00100001 00101                                   |

| 9                      | 0.159                                | 00101001 00110                                   |

| 8                      | 0.192                                | 00110001 00111                                   |

| 7                      | 0.226                                | 00111010 01000                                   |

| 6                      | 0.262                                | 01000011 01001                                   |

| 5                      | 0.299                                | 01001100 01010                                   |

| 4                      | 0.338                                | 01010110 01011                                   |

| ż                      | 0.378                                | 01100000 01100                                   |

| 4<br>3<br>2            | 0.418                                | 01101011 01101                                   |

| 1                      | 0.459                                | 01110101 01110                                   |

| . 0                    | 0.500                                | 01111111 01111                                   |

| -0                     | 0.500                                | 10000000 10000                                   |

| -1                     | 0.541                                | 10001010 10001                                   |

| -2                     | 0.582                                | 10010100 10010                                   |

| -3                     | 0.622                                | 10011111 10011                                   |

| -4                     | 0.662                                | 10101001 10100                                   |

| -5                     | 0.701                                | 10110011 10101                                   |

| -6                     | 0.738                                | 10111100 10110                                   |

| <del>-</del> 7         | 0.774                                | 11000101 10111                                   |

| -8                     | 0.808                                | 11001110 11000                                   |

| -9                     | 0.841                                | 11010110 11001                                   |

| -10                    | 0.872                                | 11011110 11010                                   |

| -11                    | 0.901                                | 11100110 11011                                   |

| -12                    | 0.929                                | 11101101 11100                                   |

| -13                    | 0.954                                | 11110011 11101                                   |

| -14                    | 0.978                                | 11111001 11110                                   |

| -15                    | 1.000                                |                                                  |

### TABLA 3.2

La tabla anterior sugiere que un contador de 5 bits sea la entrada a un circuito combinacional o a una memoria, cuya salida debe ser la palabra digital de 8 bits de la tabla anterior, la cual va a manejar al convertidor digital-analógico. Esto es tema del capítulo 4.

Es importante hacer notar que con este proceso, conjuntado en la tabla 3.2, se ha configurado una relación lineal entre la ganancia de cada banda y la palabra digital de 5 bits.

## 4. CONTROL DIGITAL DEL ECUALIZADOR

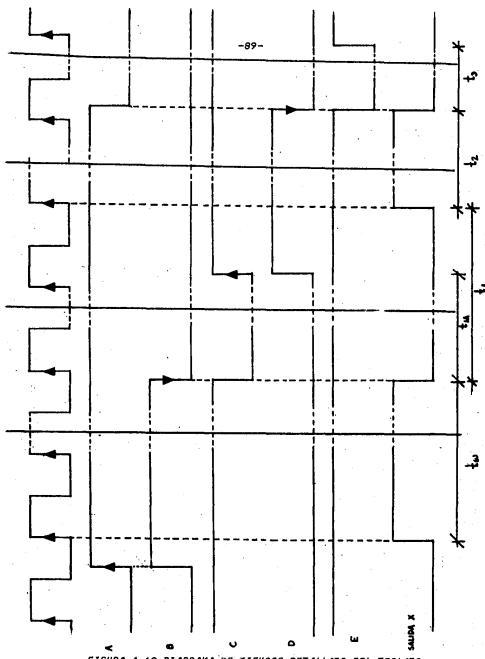

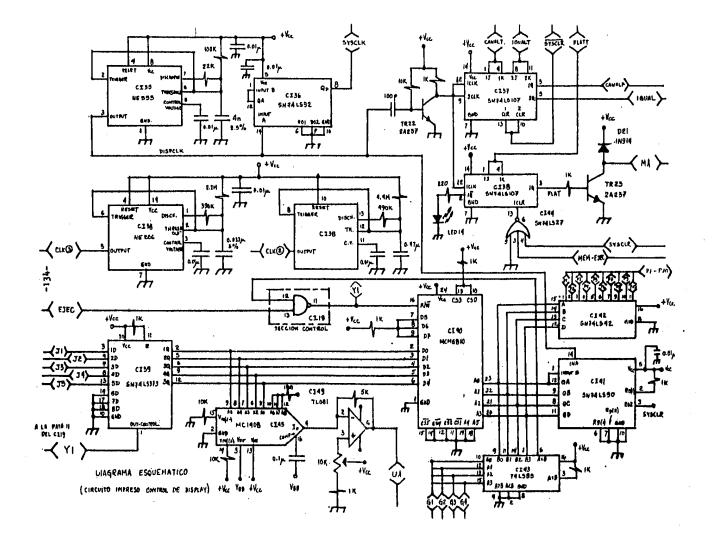

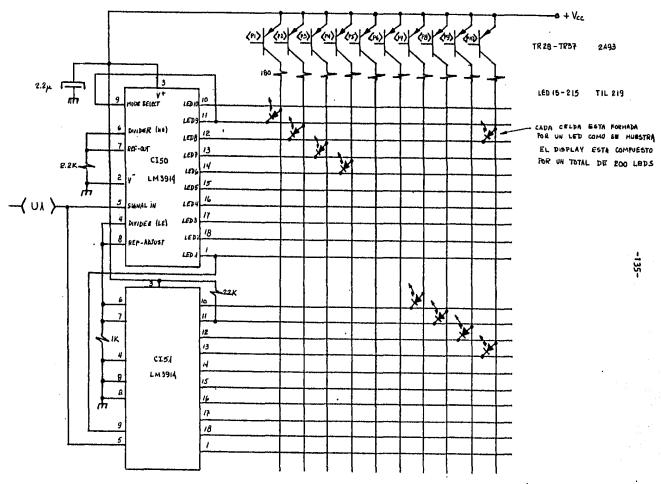

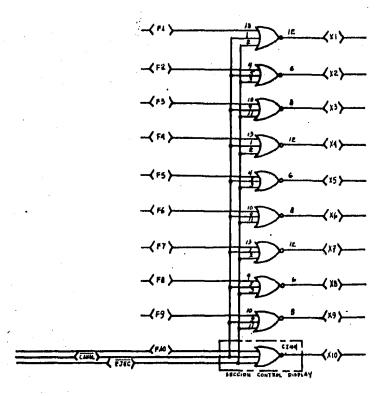

El presente capítulo comprende una expircación detallada sobre el funcionamiento del control digital para el sistema ecualizador, mostrando con diagramas de bloques, figuras y esquemas de alambrado la composición del mismo.

Todo este capítulo se complementa con los diagramas esquemáticos que se encuentran en el Apendice A. Para una mayor información sobre el funcionamiento de cada bloque, favor de referirse al diagrama correspondiente.

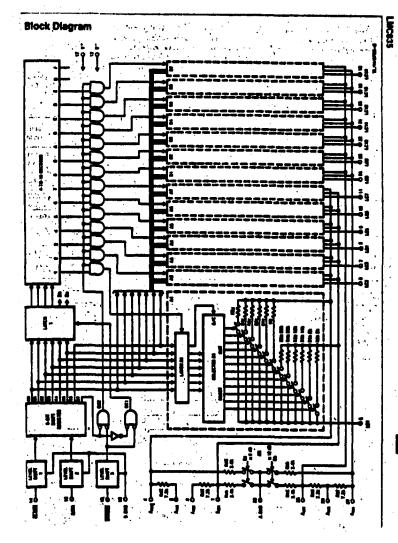

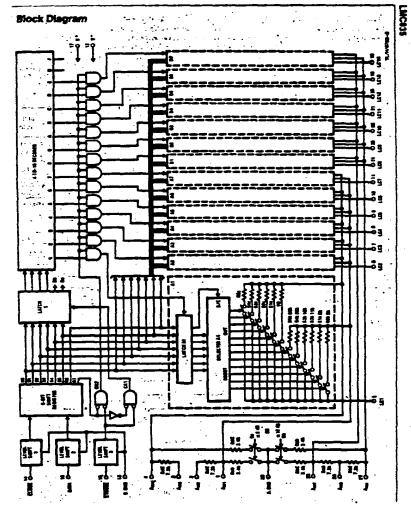

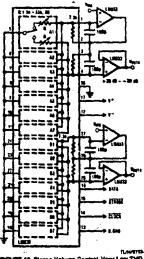

Con el proposito de entender mejor el funcionamiento de la circuitería del control digital, se ha dividido al sistema, en varios bloques de circuitos con funciones especiales cada uno. En la figura 4.1 se pueden observar los diversos circuitos que componen al sistema.

-66-

Como es lógico, algunos de estos bloques estan relacionados entre si.

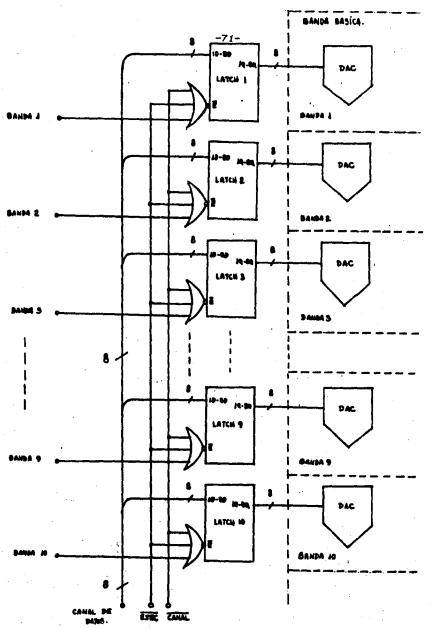

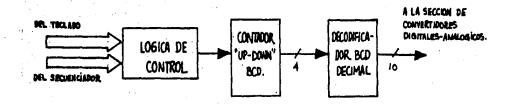

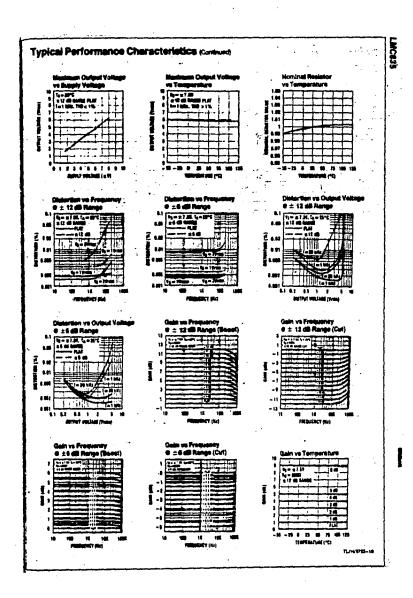

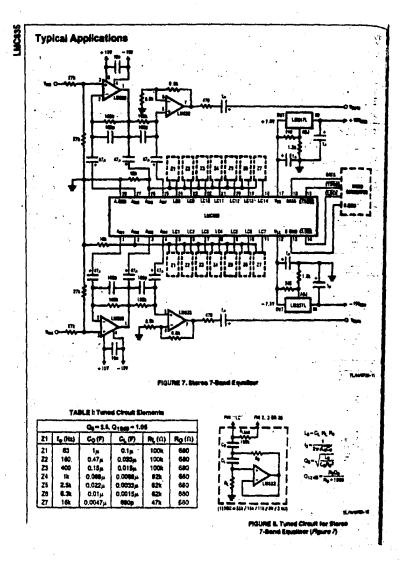

#### 4.1 BLOQUE DE CONVERTIDORES DIGITALES-ANALOGICOS.

Como se vibanteriormente en cada uno de los circuitos que realizan las bandas del ecualizador, se usan convertidores digital-analógico para implementar un atenuador controlado digitalmente. Esta sección se dedicará exclusivamente a detallar los circuitos digitales que alimentan a los DACS, para llevar acabo el ajuste de ganancia o atenuación de cada una de las bandas que forman el ecualizador.

Cada banda posee una ganancia de +15 dB y una atenuación de -15 dB, el ajuste de la ganancia puede hacerse para cada banda por separado, a través de una palabra de 8 bits. Asimismo se tienen además 13 líneas de control. El circuito se diseño de tal manera que pudiese ser compatible con un microcomputador o cualquier otro sistema digital, sin tener que utilizar el control integrado al sistema.

Como se menciono anteriormente, la ganancia o atenuación de cada banda, puede variarse mediante una palabra digital de 8 bits. Con esta palabra es posible tener 256 pasos de ganancia disponible, que pueden darse en un rango de -15 a +15 dB. Para aplicaciones futuras mediante microcomputador, el hecho de poseer esa cantidad de pasos implica un ajuste preciso para cada banda, en caso de que así se requiriera.

Por lo que se refiere al control digital integrado, este utilizara,

32 pasos de ganancia, de los 256 mencionados anteriormente. Para los sistemas de audio convencionales, no es primordial que exista una gran cantidad de pasos para cada banda, lo que si es importante aquí, es que se tenga precisión en cada paso que se da, al variar la ganancia de la banda, es decir, la diferencia entre las ganancias que corresponden a dos palabras digitales adyacentes debe ser, en términos absolutos de un dB. El ajuste correspondiente se debe hacer mediante un circuito digital, que veremos más adelante.

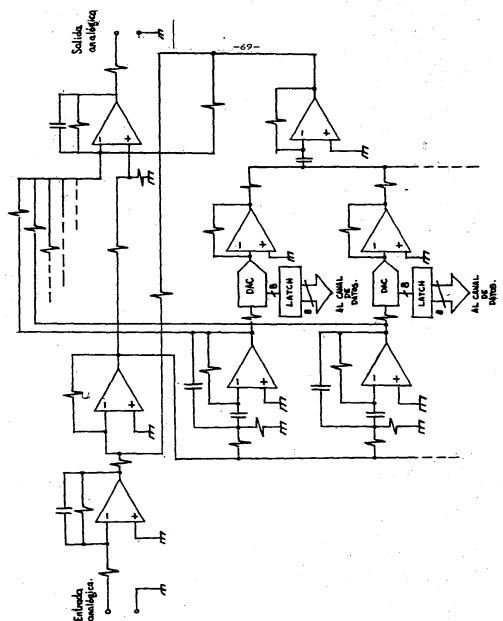

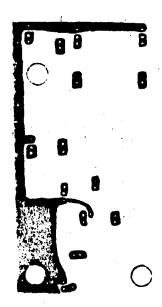

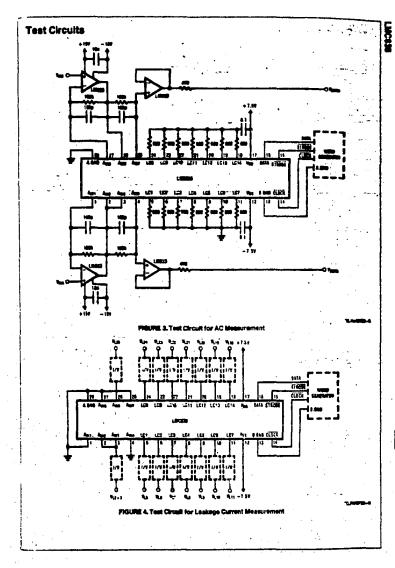

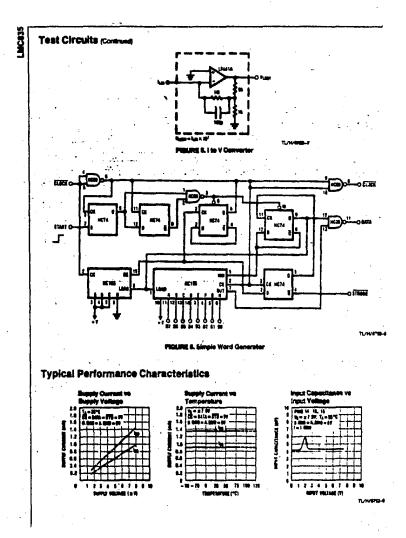

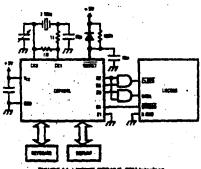

A continuación, en la figura 4.2 se observa la configuración de este bloque. Cada canal está alambrado en un circuito impreso, que contiene una pequeña parte del circuito para el control digital.

FIGURA 4.2 CONFIGURACION DEL BLOQUE DE CONVERTIDORES DIGITALES—ANALOGICOS.

FIGURA 4.2 CONFIGURACION DEL BLOQUE DE CONVERTIDORES DIGITALES-ANALOGICOS.

Para simplificar el esquema, se muestran únicamente dos bandas de un canal, de tal forma, que se ilustre la manera en que se encuentra configurada la sección digital analógica. Por otro lado, en la figura 4.3 se observa en forma más detallada ésta sección.

. IGURA 4.3 CONFIGURACION GENERAL DEL BLOQUE DE CONVERTIDORES DIGITALES-ANALOGICOS.

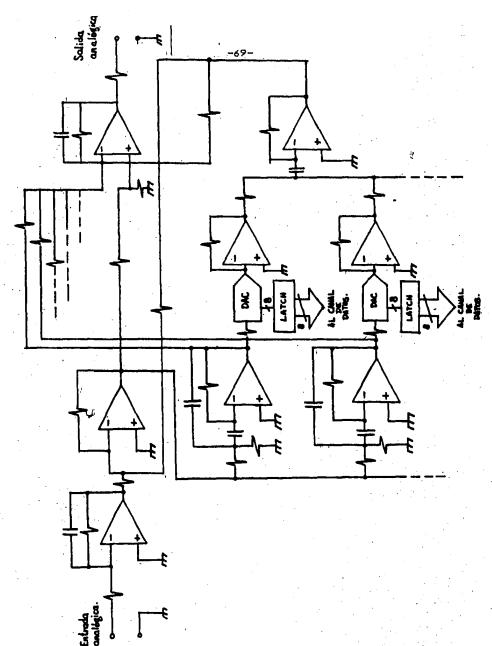

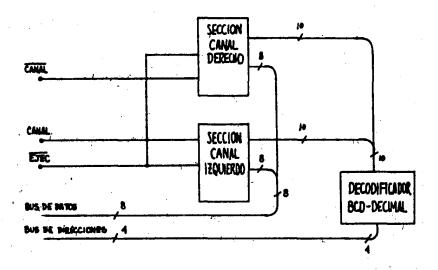

En el circuito se usan "latches". TTL- (SN74L\$373) de 8-bits, que tienen la finalidad de retener la información de la banda correspondiente. La entrada de habilitación (E) para el latch (pata 11) está conectada a la salida de una compuerta NOR de tres entradas, lo anterior se hace con el propósito de tener acceso a tres lineas de control. La primera linea, "CANAL", es una linea de habilitación para el canal correspondiente, posee verificación baja, o sea, que mientras permanezca en cero, estará habilitada. La segunda linea "EJEC", es la de ejecución, y la tercera linea sirve como direccionamiento de la banda en turno. Una determinada banda se seleccionará cuando las tres lineas tengan un nivel bajo. Como el latch es del tipo "transparente", la información que en ese momento esté pasando por el canal de datos de 8 bits, será aquella que modificarà el valor de la corriente de salida del DAC direccionado. La figura 4.3 muestra el circuito para un solo canal, siendo por tantoigual al otro, a excepción de que unicamente un canal funciona a la vez, esto se logra por medio de un inversor colocado en el lugar adecuado como lo muestra la figura 4.4. En realidad, se tienen disponibles 2 lineas de "CANAL", una verificada alta, y la otra baja, provenientes del circuito secuencial.

FIGURA 4.4 DIRECCIONAMIENTO DE LOS CANALES.

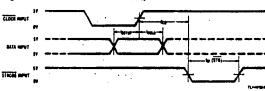

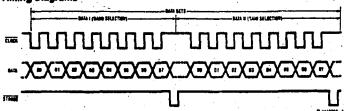

El canal de datos para ambos canales es común, así como también el de direcciones. En la misma figura 4.4 se ilustra además un degodificador BCD-DECIHAL TTL (SH74LS42). Este circuito integrado tiene como función el de reducir el número de lineas de control de dirección, el circuito es parte del bloque de control de banda. Aquí se ha querido poner en claro, que es posible efectuar el control digital mediante una microcomputadora, microprocesador, etc., con sólo tener acceso a estas catorce líneas. Existe otra posibilidad de reducir el número de líneas para el control del ecualizador, mandando la información en serie. El diseño de un circuito en serie no resulta muy complicado, ya que se pueden utilizar registros de corrimiento serie-paralelo, que estuvieran sincronizados con un reloj. Para el sistema mencionado se tendrían entonces tres

lineas, la primera seria la de datos, la segunda el reloj, la tercera "STROBE", está última indica la presencia de un bloque completo de datos, que ha sido cargado en los registros. Debido a que el circuito en serie mencionado, no llegó a implementarse, por no considerarlo necesario, sólo se menciona aqui como posible alternativa para el control externo. Por ahora esta sección sólo se dedicará a detallar el control digital que tiene integrado el sistema.

El diagrama esquematico del bloque de convertidores digitales-analógicos puede verse en el Apéndice A.

### 4.2 BLOQUE TECLADO.

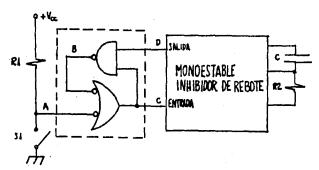

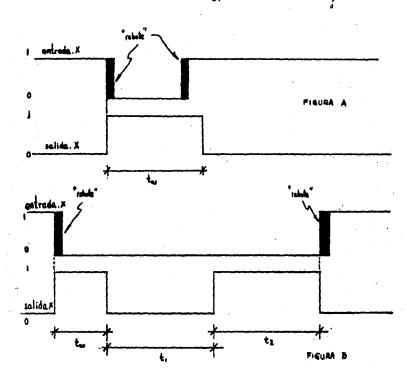

- El teclado del ecualizador ha sido diseñado con las siguientes características:

- \* Sensible al tacto, es decir, cualquier tecla se acciona con el simple toque del dedo sobre una placa metàlica.

- \* Insensible a "rebotes" ya sean electronicos o mecánicos, con el objeto de no provocar falsas instrucciones al sistema digital.

- \* Inmunidad a errores ocasionados, por el accionamiento de una tecla por un tiempo mayor del debido.

- \* Repetición automática del teclado, esto es: si la tecla permanece más tiempo apretada, aún después de haberse producido

el primer pulso, se espera un cierto intervalo de tiempo, sin que se genere una nueva señal, y cuando éste lapso termine, si aun persiste la acción de la tecla, se manda de nuevo la señal, que durará mientras la tecla se mantenga presionada. Esto es útil sobretodo en los comandos de ganancia para cada banda, así como también, para el circuito que direcciona a cada una de éstas, debido a que no será necesario presionar continuamente la tecla, si se requiere que la función siga activa. Por ejemplo, podemos lograr lo siguiente; al presionar sólo un instante la tecla que controla la ganancia en forma ascendente, nos moveremos sólo un paso, en este caso 1 dB. Si se mantuviese apretada la tecla, después de medio segundo aproximadamente, en forma automática la ganancia variará. Lo anterior se logra haciendo funcionar un contador, circuito que veremos más adelante. El contador seguirá funcionado hasta que la tecla deje de oprimirse.

# El teclado posee circuitos que inutilizan parte del mismo, en el caso de que una determinada secuencia se ejecute. Lo anterior es necesario cuando se accionan las teclas MEN ▲ y MEN ▼ (memoria ascendente o memoria descendente) para evitar que la información de otras memorias se altere, sin que previamente se pase por completo la información hacia los latches y como consecuencia a los convertidores digitales—analógicos que forman parte de cada banda.

<sup>\*</sup> Cada vez que se acciona una tecla se produce una oscilación audible. Este sonido, de corta duración, sólo se presentará la primera vez que se accione cualquiera de las teclas.

Para comprender mejor el funcionamiento del bloque de teclado, en la figura 4.5 se muestra una disposición de bloques auxiliares que componen al circuito:

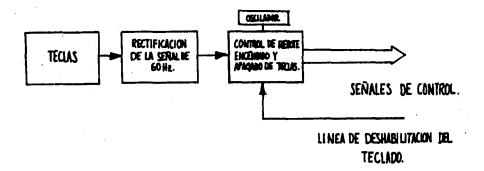

FIGURA 4.5 BLOQUES AUXILIARES DEL TECLADO.

La primera parte del bloque de teclado esta formado por un total de 11 teclas de entrada, que conforman los comandos principales del ecualizador, estos son:

- ; control de ganancia (ascendente).

- 🕶 🦈 : control de ganancia (descendente).

- : selección de banda (descendente).

- s selección de banda (ascendente).

- HEM-▲ : comando de selección de memoria (ascendente).

- HEM-- : comando de selección de memoria (descendente).

- IGUAL : control para colocar la misma información en

- TOTAL NE PRO- COLORS LE MODEL INIVINITATION CI

- ambos canales.

- CANAL .: selección de canal izquierdo o derecho.

MEM-EJEC : vacia el contenido de la memoria direccionada.

FLAT s pone al sistema ecualizador en "flat" (O dB de

ganancia).

ENT : escoge la entrada de señal analógica deseada.

Existen entradas adicionales para futuras funciones o modificaciones en lo que se refiere al control del equalizador,

Las 11 teclas mencionadas anteriormente estan formadas por una serie de láminas, cada una de éstas láminas se conecta con un circuito independiente uno de otro, que condiciona la señal producida por el efecto que tiene el cuerpo humano de funcionar como una antena. Con ésta peculiaridad es posible prescindir de un teclado convencional de tipo mecánico. En el diagrama a bloques de la figura 4.5, se ve que la sección está constituida por dos etapas, la de rectificación y la de conmutación.

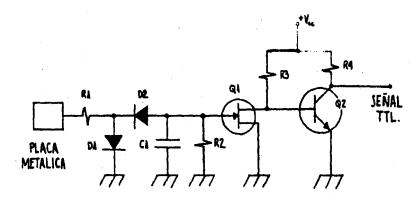

En la figura 4.6 se observa el circuito.

FIGURA 4.6 CIRCUITO DE RECTIFICACION Y MANEJO DE LA SENAL DE 60HZ

Para escoger el circuito se partib del siguiente hecho: una seffal captada por el cuerpo humano, puede llegar a detectarse por medio de un circuito electrónico, pero éste debe tener una impedancia muy alta a la entrada para poder detectar un cambio al contacto del dedo con una placa metálica. Al efectuar varias pruebas, bajo diferentes condiciones, se observo, que en una habitación normal, en la que exista alguna linea de alimentación de 120 V y 60 Hz, la forma de onda generada por el cuerpo humano al contacto de una placa metálica, tiene la misma frecuencia que la linea de alimentación, y con una magnitud pico a pico que varia de 5 a 10 voltios aproximadamente. Como es lógico, la señal se presenta en forma distorsionada. Se penso que la magnitud del voltaje pico a pico podria ser suficiente para hacer funcionar un circuito. Es evidente que la corriente que genera el cuerpo humano es muy pequeña. Para tal efecto se utiliza un transistor FET, con éste tipo de dispositivo electrónico, se logran las condiciones

necesarias de entrada para condicionar la señal.

La semal de radiación de 60 Hz. debe rectificarse, de tal forma que al presionar la lamina, la corriente Id del FET sea casi nula, haciendo que el transistor HPN (Q2) conduzca y se produzca en el colector un nivel bajo de voltaje que se tomará como un "O" lógico para las entradas TTL que siguen en la otra sección del circuito. Aqui se puede hacer notar que Q1 y Q2 funcionarán como interruptores electrónicos. Guando se presiona la lámina, se provoca una caida de potencial en Vgs, éste voltaje se produce a partir del ruido que se genera del exterior, y que es captado por el circuito. El orden de magnitud de ese ruido es tal que hará que entre en funcionamiento el circuito.

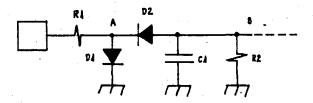

El circuito rectificador estará calculado de manera que cada vez que se oprima la làmina, el voltaje Vgs sobrepase el valor de Vp (voltaje compuerta-fuente de estrangulamiento, "pinch off"). En el caso del FET 2A267 éste voltaje tienen un valor de -3 V aproximadamente. Si se sobrepasara ésta cantidad, Id prácticamente será nula. La señal rectificada que llega a la compuerta del FET debe alcanzar un valor, digamos de -4 o -5 volts, para que en Ql la=0. Vemos el circuito de rectificación en la figura 4.7:

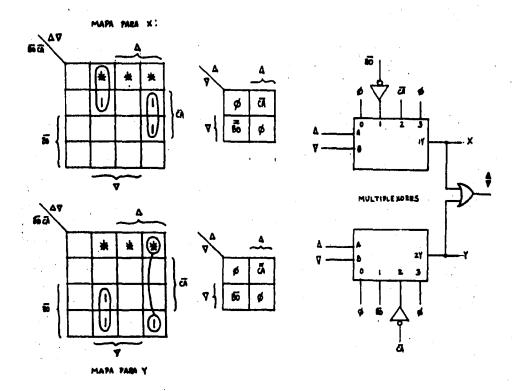

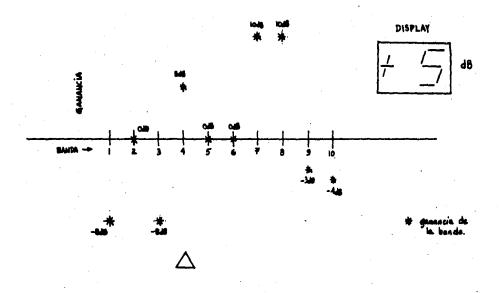

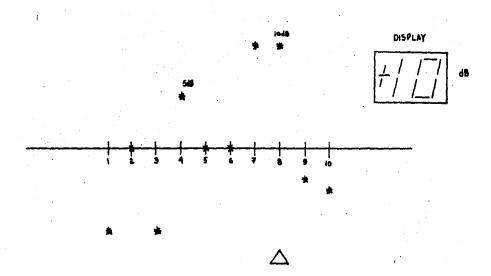

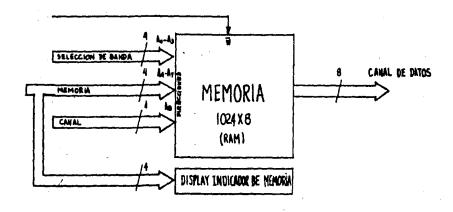

FIGURA 4.7 CIRCUITO DE RECTIFICACION.